One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106 • 781/329-4700 • World Wide Web Site: http://www.analog.com

## A Geophone/Hydrophone acquisition reference design based on the AD1555/AD1556 chipset

by Alain Guery

### INTRODUCTION

This application note describes a reference design based on the 24 Bit sigma-delta high dynamic range AD1555/AD1556 chipset. This chip-set allows direct acquisition of high dynamic sensors like geophones or hydrophones. Acquisition of other high dynamic range low frequency range ( up to few kHz ) sensors can also be done.

The intent of this note is to provide the detailed description of this design. These guidelines can be used to ease the design using the AD1555/AD1556 chip-set. The main goal of this design is to give a baseline design that can be customized at user convenience rather than a design which covers all acquisition needs.

This design is very dense ( less than 1 inch by 2 inches per channel ), can be easily extended to do a multichannel acquisition system, and demonstrates the specific high accuracy performances of the chip-set. Performance of 120dB dynamic range in 408Hz bandwidth, equivalent input noise of 80nVrms in 101 Hz bandwidth and distortion of -120 dB with a total power dissipation lower than 90mW per channel typically can be achieved.

The AD1555 is a complete sigma-delta modulator, combined with a programmable gain amplifier intended for low frequency, high dynamic range measurement applications. The AD1555 outputs a ones-density bit stream proportional to the analog input. When used in conjunction with the AD1556 digital filter/decimator, a high performance ADC is realized.

A full description of the AD1555/AD1556 is available in the AD1555/AD1556 data sheet and should be consulted when utilizing this application note. The data sheet provides detailed information on the functionality of the AD1555/AD1556 chipset and will be referenced often in this application note.

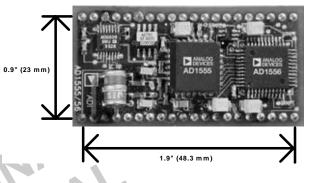

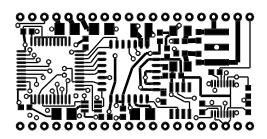

Figure 1. Implementation of the reference design.

## GENERAL DISCUSSION

The implementation of this one channel acquisition AD1555/ AD1556 reference design occupies less than one 1 inch by 2 inches per channel on a one side board and is shown in figure 1. In multichannel applications, some components can be shared to further reduce the estate per channel. This reference design includes many functionalities like EMI/RFI filtering, lightning protection, sensor and acquisition system build-in testability, calibration, reference voltage and easy to use serial digital interface. The schematic of the reference design is shown in figure 2.

### **Input Filtering**

Some filtering of the input signal coming from the sensor is usually required before acquisition. Depending on the application, the requirements of this filter can vary among EMI/RFI filtering to prevent high frequency noise coming in and being detected by the acquisition system, common mode filtering and polarization when the sensor is floating, lightning protection when sensors such as geophone are connected through long cables and are exposed to the elements. It is difficult to cover all the specific requirements of each application with the same filter. The filter implemented in the reference design answers some of these requirements and can be customized according to each specific application.

# AN-566AN Preliminary Technical Data Preliminary Technical Data

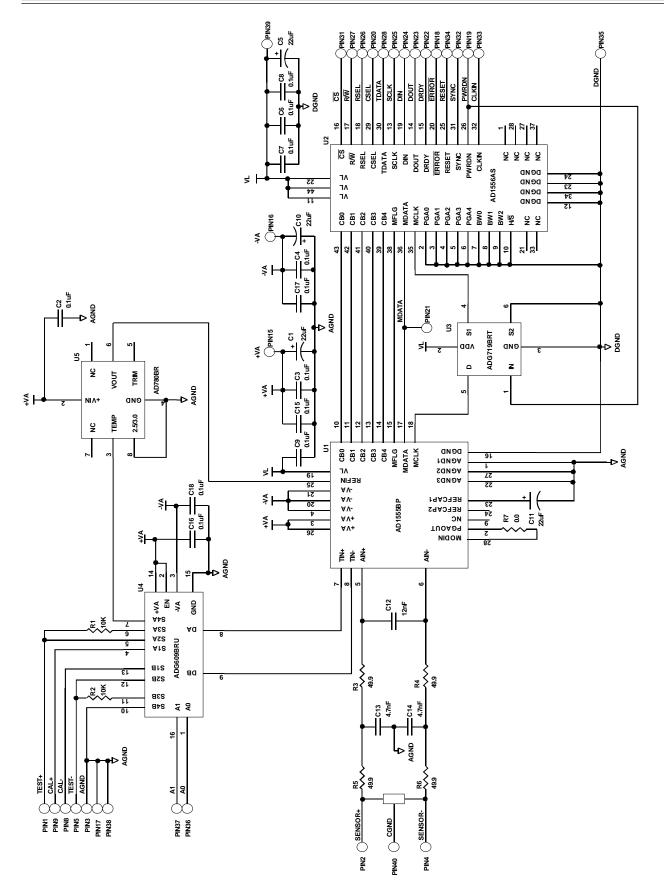

Figure 2. Schematic.

The filter implemented on the reference design consists of a low pass common mode filter made by R5, C13, C14 and R6 followed by a differential mode low pass filter made by R3, C12 and R4. The cutoff frequency of the differential filter is set below the sampling frequency of the sigma-delta modulator of the AD1555 and therefore this filter can served as the antialiaising filtering. Because of the architecture of the AD1555, there is usually no need for another anti-aliaising filter. The common mode and differential filter cut off frequencies on the reference design are set respectively at 675 kHz and 66kHz. The differential filter cutoff frequency is chosen deliberately significantly lower than the common mode filter cutoff frequency to remove differential signals generated by any mismatch which could be present in the common mode filter.

The serial resistors R3, R4, R5 and R6 must be kept low to reduce their noise contribution which could reduce the dynamic range mainly at the highest gain settings. With the values chosen in the reference design, the dynamic range loss  $\Delta_{dynamic}$  is close to 0.2dB for the gain setting of 34 at the sampling rate of 4ms (250 Hz).

$\Delta_{dynamic} \approx 20.LOG_{10}[(({n_R}^2 + {n_{ADC}}^2)^{1/2}\!/{n_{ADC}}]$

Where :

$n_{ADC}$  is the equivalent input noise of the AD1555.

$n_{ADC}$  is 80nVrms for the gain setting of 34 at F0 = 250Hz (see Table I of the data sheet).

n<sub>R</sub> is the thermal noise of the serial resistors :

$n_R^2 \approx 4kT.4.R.(BW_{-3dB})$

R = R3 = R4 = R5 = R6

$BW_{-3dB}$  is a good approximation of the noise bandwidth due to the steep digital filter response (see Table II of the data sheet).

Note that C12, C13 and C14 are on the signal path and, therefore, should have a very good linearity as an NPO ceramic capacitor or a polypropylene type.

If desired, the cutoff frequencies can be lowered by increasing the serial resistors or the capacitors which will result in a tradeoff between the dynamic range loss at high gain and the size of the capacitors.

#### Lightning protection

The reference design is designed to handle severe stresses which could likely happen because it is directly connected to remote sensors. For instance, in seismic land based systems where geophones are used, lightning could eventually propagate through the geophone cable to the acquisition system. The voltage spikes induced by lightning is first clamped by the surface mount dual gas arrestor Z1 from Joslyn, part number 2036-90-A, to about 100V. The signals on AD1555 AIN inputs are also clamped to the analog supply rails  $+V_A$  and  $-V_A$  by robust clamping diodes integrated in the AD1555. Thus, the serial resistors R3, R4, R5 and R6 limit the pulsed current which flows in the AIN inputs to about 1A. The AD1555 AIN inputs are designed to handle 1.5A pulsed current during  $2\mu s$  without experiencing any destructive damage or latch-up whether the AD1555 is powered on or off. Meanwhile, enough time should be left between each spike to avoid excessive power dissipation. When the stress pulses are longer than  $2\mu s$ , the current limitation should be reduced by increasing the values of R3, R4, R5 or R6. The power supplies +VA and -VA should be able to handle a high pulsed current which returns through them. A tranzorb on each supply, common to all channels in a multichannel configuration, could be enough to achieve the desired protection. Meanwhile, the power supply design should take in consideration this requirement.

#### **Calibration process**

The AD1555 is intended to be used with a calibration process to achieve high precision absolute accuracies. This calibration process can be done easily by acquiring ground and full-scale references for each gain setting.

The offset for each gain setting can be known by using the AD1555 internal multiplexer in the mode "Ground input" which shorts the inputs to ground. It is recommended to calibrate the offset for each gain setting due to potential offset mismatch. Then, each gain setting can be calibrated accurately by applying known voltage references close to full-scale between CAL+ and CAL- inputs of the module. When the channel S1 of the multiplexer U4 is selected and the AD1555 internal multiplexer uses the mode "Test input", these reference voltages can be measured through the AD1555 with the corresponding gain setting. Use of the lowest bandwidth ( $F_0 =$ 250Hz) filter of the AD1556 and averaging will reduce the noise of the calibration measurements. The high input impedance of the AD1555, 140M $\Omega$  typical, minimizes errors due to source impedance of the reference voltages which can be generated directly from a precision resistive network.

Moreover, although gain and offset temperature drift of the AD1555 are low, the calibration accuracy over temperature can be further improved by monitoring the ambient temperature. The reference design offers a cheap way to do that using the AD780 Temperature output pin (TEMP) feature. The voltage of the temperature pin TEMP of the AD780 is proportional to the absolute temperature with a temperature sensitivity of +1.9mV/°C typical. By acquiring this temperature dependant voltage through the channel S4 of the multiplexer U4, temperature change can be detected and the user can decide to launch a new calibration process at the actual ambient temperature.

Only one calibration circuitry consisting of the reference voltages and the multiplexer U4 can be used for all channels in multichannel system.

#### Self-test circuitry

The AD1555/AD1556 reference circuit is designed to ease the testability of both the acquisition system and the sensor. As described in chapter Programming the AD1555 of the data

# AN-566AN Preliminary Technical Data Preliminary Technical Data

sheet, a signal on TIN inputs can be applied on the sensor through the AD1555 internal multiplexer and the sensor response can be measured simultaneously with the AD1555.

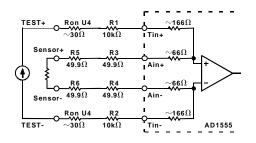

For instance, that allows the measurement of the impedance of the sensor and its cable which helps to localize any potential failures ( open or short-circuit ). A voltage source applied between TEST+ and TEST- will force, through the 10k $\Omega$  resistors R1 and R2, a current into the sensor when the multiplexer U4 is on channel S3 and the internal multiplexer of the AD1555 on "Sensor Test1" configuration. The figure 3 shows a simplified schematic of this configuration.

Figure 3. Sensor impedance measurement schematic.

The accuracy of the measurement is slightly affected by the serial resistance of the AD1555 inputs and the on resistance of the multiplexer U4. By using the typical values shown on figure 2, impedance measurement accuracy of a few percent is possible. To further improve this accuracy, these serial resistances which can deviate at ambient temperature by  $\pm -20\%$  from the typical value, can be determined in factory by measuring known impedances in place of the sensor. The remaining error due to these serial resistances is their temperature variation which can vary by +/-20% over -55°C to +85°C temperature range. Notice that this measurement can be either done with DC or with a low frequency source. With the multiplexer U4 on channel S2 and the internal AD1555 multiplexer on "Test input", the amplitude of the source applied to the inputs of the module can be measured accurately and therefore doesn't affect the impedance measurement accuracy.

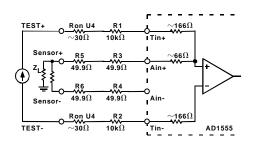

The impedance between the sensor and the ground which allows the detection of leak and isolation issues in the sensor cable can be done by a similar manner. By selecting the AD1555 internal multiplexer in "Sensor Test2" configuration which forces the source signal on only one side of the sensor, isolation impedance between the sensor and the ground is measured. Figure 4 shows a simplified schematic of this configuration. The low side input of the AD1555 is always at the same voltage (TEST-) while a possible leakage impedance  $Z_L$ on the sensor forms a voltage divider with resistor R1 and the other serial resistors. The output, AIN+, will depend on the leakage impedance  $Z_L$ . When  $Z_L$  is high, the AIN+ voltage is close to the TIN+ voltage.

Figure 4. Sensor leakage measurement schematic.

Like the sensor, the acquisition system can be also verified easily.

Noise level and dynamic range performance can be checked using the AD1555 internal multiplexer in "Ground input" configuration. In this mode, the AD1555 PGA inputs are shorted by an internal accurate  $1k\Omega$  resistor. Noise level and dynamic range can be checked for each gain setting with the expected values defined in table I of the data sheet. The values in this table do not include the noise of the internal 1  $k\Omega$  resistor and should be added as follows :

$$n_{\rm T} \approx (n_{\rm ADC}^2 + 16.10^{-18}.{\rm BW}_{-3dB})^{1/2}$$

Where :

$n_{\rm T}$  is the expected equivalent input noise in "Ground input" configuration.

$n_{ADC}$  is the equivalent input noise of the AD1555. It is given in table I.

$BW_{-3dB}$  is a good approximation of the noise bandwidth due to the steep digital filter response (see Table II of the data sheet).

Similarly, performance of the acquisition system in the presence of signal like linearity and intermodulation or impulse response can be verified by applying an AC or two tone reference source between either TEST+ and TEST- or CAL+ and CAL- inputs.

### AD1555 circuit

The AD1555 is a fully integrated acquisition solution which requires only few external passive devices.

The PGA output PGAOUT is usually connected to the modulator input MODIN by a short-circuit (resistor R7). If desired, this resistor R7 can be used to slightly change the voltage ranges. In fact, the AD1555 PGA still behaves well with output range up to +/-3.5V. Resistor R7 and the input impedance of the modulator,  $20k\Omega$  typical, will reduce this swing to get the modulator range of +/-2.25V. Also R7 can be replaced by a capacitor to have a high pass filter.

#### Power supply

The reference design is intended to be used with separate digital and analog supplies : a dual analog supply +/-5V (+VA, -VA) and a +5V digital supply. The necessary decoupling components are on board. There is no connection between the analog and digital ground planes on the reference design board and, thus, this connection can be made at an optimal location in the system. This optimal location depends a lot on the system architecture and is usually determined by experiment. It was found that a short connection between pin 38 (AGND) and pin 35 (DGND) is a good location when the reference design is used in a stand alone application.

This design can be used also with a 3V digital supply with the following modifications :

- The AD1555 digital supply (pin 19) is connected through a 15 $\Omega$  resistor to the +5V analog supply +VA. Thus, the AD1555 remains supplied with 5V without any need of an additional supply.

- 10k $\Omega$  resistors should be inserted on MDATA and MFLG lines between the AD1555 and the AD1556 to protect the AD1556 against the AD1555 5V logic. The delay introduced by the time constant of the 10k $\Omega$  resistor and the AD1556 input capacitance is compatible with the AD1556 timing.

The AD1555 and the AD1556 can be shutdown by bringing PWRDN high (pin 19) or by using the software programmable AD1556 configuration register. Also, the shutdown consumption of the AD1555 is slightly lower when MCLK is low. To take benefit of this additional power saving, a switch U3 can be added. The switch U3 forces MCLK low when PWRDN is high.

#### Implementation and Layout

The reference design is implemented on a 4 layer board:

- The top layer is shown in figure 5.

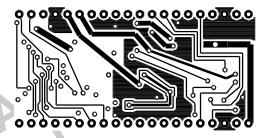

- The layer below called "shield" is shown in figure 6.

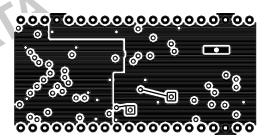

- The next layer is used for both digital and analog ground planes and shown in figure 7.

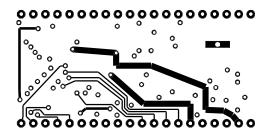

- The fourth layer is shown in figure 8.

One of the most critical line is the return ground connection of the pin AGND3 of the AD1555 (pin 22). From this pin, it is routed first to the low side of the reference decoupling capacitor C11, then to the reference voltage ground (pin 4) and finally returns to the analog ground plane at the pin AGND1 of the AD1555 (pin 1).

The bill of material is listed in Table I.

Figure 5. Top Layer (Not to scale).

Figure 6. Shield Layer (Not to scale ).

Figure 7. Ground Layer (Not to scale).

Figure 8. Bottom Layer (Not to scale).

## **AN-566AN Preliminary Technical Data Preliminary Technical Data**

### Table I. Bill of material.

#### **Integrated Circuits**

| U1 | AD1555BP.              |

|----|------------------------|

| U2 | AD1556AS.              |

| U3 | switch ADG719BRT.      |

| U4 | multiplexer ADG609BRU. |

| U5 | reference AD780BR.     |

#### Capacitors

| C2-C4,C6-C9,C15-C18<br>C1,C5,C10,C11<br>C12<br>C13,C14 | 100nF X7R Ceramic<br>22μF 6.3V Tantalum B size<br>12nF NPO 50V 1210 size Ceramic<br>4.7nF NPO 100V 1206 size Ceramic | Kemet T494B226K006<br>Kemet C1210C123K5G<br>Kemet C1206C472K5G |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Resistors                                              |                                                                                                                      |                                                                |

| R1,R2<br>R3-R6                                         | 10k $\Omega$ Resistor.<br>49.9 $\Omega$ Resistor.                                                                    |                                                                |

| R1,R2 |  |

|-------|--|

| R3-R6 |  |

#### Protection

**Z**1

PRE-CHARA gas discharge tube Joslyn 2036-90-A