# Single Supply Bridge Transducer Amplifier

AD22055\*

#### **FEATURES**

Gain of 400. Alterable from 40 to 1000 Output Span 20 mV to ( $V_S$ –0.25) V 1 Pole Low-Pass Filtering Available Offset Capability Differential Input Resistance 230 k $\Omega$  Drives 1 k $\Omega$  Load to +4 V Using  $V_S$  = +5 V Supply Voltage: +3 V to +36 V

Transient Spike Protection and RFI Filters Included

Peak Input Voltage (40 ms): 60 V Revexed Supply Protection: -34 V

Operating Temperature Range: -40°C to +125°C

APPL/CA/TIONS

Interface for Pressure Transducers, Position Indicator, Strain Gages, and Other Low Level Signal

Sources

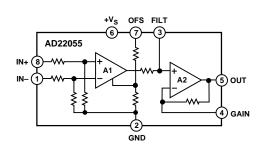

## FUNCTIONAL BLOCK DIAGRAM

# **GENERAL DESCRIPTION**

The AD22055 accepts a differential signal from a bridge transducer whose common-mode signal can be anywhere between the power supplies.

The extended temperature range allows for local signal conditioning for oil and hydraulic pressure sensors as well as other automotive sensors.

\*Patents pending.

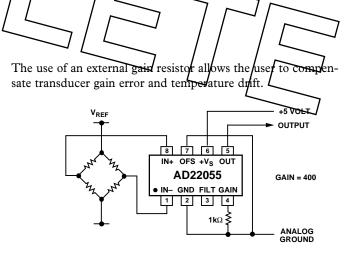

Figure 1. Typical Application Circuit for a Pressure Sensor Interface

#

| Parameter                                                                                                                             | Comments                                                                                                                                                           | <b>Test Conditions</b>                                                               | Min                    | Тур                                  | Max                  | Units                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------|--------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| INPUTS (PINS 1 AND 8)  V <sub>CM</sub> CMRR <sub>LF</sub> CMRR <sub>HF</sub> R <sub>INCM</sub> R <sub>MATCH</sub> R <sub>INDIFF</sub> | Common-Mode Range Common-Mode Rejection Ratio Common-Mode Rejection Ratio Common-Mode Input Resistance Matching of Input Resistances Differential Input Resistance | $f \le 10 \text{ Hz}$<br>f = 10  kHz<br>Pin 1 or Pin 8 to Pin 2<br>Pin 1 to Pin 8    | 0<br>-80<br>-60<br>180 | -90<br>-75<br>230<br>±05<br>230      | 5                    | V<br>dB<br>dB<br>kΩ<br>%                                                                                                  |

| PREAMPLIFIER  G <sub>CL</sub> V <sub>O</sub> R <sub>O</sub>                                                                           | Closed-Loop Gain <sup>1</sup> Output Voltage Range (Pin 3) Output Resistance <sup>2</sup>                                                                          |                                                                                      | +0.02<br>77.6          | 40<br>80                             | +4.75<br><b>82.4</b> | V/V<br>V<br>kΩ                                                                                                            |

| OUTPUT BUFFER  GCI VG RO                                                                                                              | Closed-Loop Gain <sup>1</sup> Output Voltage Range Output Resistance (Pin 5)                                                                                       | $R_{LOAD} \ge 10 \text{ k}\Omega$ $V_O \ge 0.1 \text{ V dc}$                         | 9.95<br>+0.02          | 10<br>2.0                            | 10.05<br>+4.75       | V/V<br>V<br>Ω                                                                                                             |

| Verall system  Vos                                                                                                                    | Gain 1 Gain Drift Gair Dhift Initial Offset Voltage Offset Drift                                                                                                   | V <sub>0</sub> ≥ 0.1 V dc<br>-40°C to +1725°C<br>-125°C/to +150°C<br>-40°C/to +125°C | 398                    | 400<br>-60<br>-500<br>0.05           | <b>402</b>           | V/V<br>ppm/°C<br>ppm/°C<br>mV<br>μV/°C                                                                                    |

| $I_{ m OSC} \ BW_{-3~{ m dB}} \ SR \ N_{ m SD}$                                                                                       | Offset Drift Input Resistance Short-Circuit Output Current  -3 dB Bandwidth Slew Rate Noise Spectral Density <sup>3</sup>                                          | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                               | 2.5<br>7<br>20         | -10<br>3.0<br>11<br>30<br>0.2<br>0.2 | 25                   | $\begin{array}{c} \mu V / C \\ \mu V / ^{\circ} C \\ k \Omega \\ \eta A \\ k Hz \\ \hline \psi V / \sqrt{Hz} \end{array}$ |

| $\overline{\begin{array}{c} \text{POWER SUPPLY} \\ V_S \\ I_S \end{array}}$                                                           | Operating Range Quiescent Supply Current <sup>4</sup>                                                                                                              | $T_A = T_{MIN}$ to $T_{MAX}$                                                         | 3                      | 5<br>200                             | 36<br>500            | V<br>µA                                                                                                                   |

|                                                                                                                                       | Operating Temperature Range                                                                                                                                        |                                                                                      | -40                    |                                      | +125                 | °C                                                                                                                        |

| PACKAGE                                                                                                                               | Plastic SOIC (R-8)                                                                                                                                                 |                                                                                      | A.                     | D22055R                              |                      |                                                                                                                           |

### NOTES

All min and max specifications are guaranteed, although only those marked in boldface are tested on all production units at final test.

Specifications subject to change without notice.

-2- REV. 0

$<sup>^1</sup>$ A2 gain is trimmed to  $\pm 0.5\%$  with a 0.01% 1 k $\Omega$  resistor to ground from Pin 4. The overall gain is trimmed to a gain of 400  $\pm 0.5\%$  with the same 1 k $\Omega$  resistor. The gain of A1 (the ratio of overall gain to A2 gain) is used to adjust the overall gain and, therefore, is not trimmed explicitly to 40. Note that the actual gain to a particular application can be modified by the use of an external resistor at Pin 4.

<sup>&</sup>lt;sup>2</sup>The actual output resistance of A1 is only a few ohms, but access to this output, via Pin 3, is always through an 80 kΩ resistor, which is trimmed to  $\pm 3\%$ . <sup>3</sup>Referred to the input (Pins 1 and 8).

<sup>&</sup>lt;sup>4</sup>With V<sub>DM</sub> = 0 V. Differential mode signals are referred to as V<sub>DM</sub>, while V<sub>CM</sub> refers to common-mode voltages.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage +3 V to +36 V                |

|---------------------------------------------|

| Peak Input Voltage (40 ms)                  |

| Reversed Continuous Supply Voltage34 V      |

| Operating Temperature40°C to +125°C         |

| Storage Temperature65°C to +150°C           |

| Output Short Circuit Duration Indefinite    |

| Lead Temperature (Soldering, 60 sec) +300°C |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; the functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

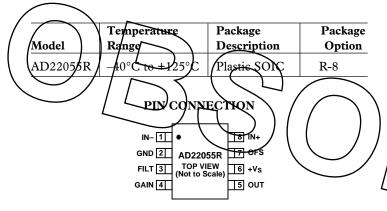

## **ORDERING GUIDE**

### PIN DESCRIPTION

| 8-Pin SOIC |          |  |  |

|------------|----------|--|--|

| Pin        | Function |  |  |

| 1          | IN-      |  |  |

| 2          | Ground   |  |  |

| 3          | Filter   |  |  |

| 4          | Gain     |  |  |

| 5          | Out      |  |  |

| 6          | Out      |  |  |

| 6          | $+V_S$   |  |  |

| 7          | OFS      |  |  |

| 8          | IN+      |  |  |

#### PRODUCT DESCRIPTION

The AD22055 is a single supply difference amplifier consisting of a precision balanced attenuator, a very low drift preamplifier and an output buffer amplifier (A1 and A2, respectively in the functional block diagram. It has been designed so that small differential signals  $V_{\rm DM}$  can be accurately amplified and filtered in the presence of large common–mode voltages  $V_{\rm CM}$  without the use of any other active components.

The common-mode range resistors in this network are trimmed to match better than one part in 10,000. The resistive attenuator network is situated at the input to the AD22055 (Pins 1 and 8) allowing the common-mode voltage at Pins 1 and 8 to be two times greater than that which can be tolerated by the actual input of A1. As a result, the input common-mode range extends from ground to the power supply voltage.

Two small filter capacitors (not shown) have been included at the inputs to Al to minimize the effects of any spurious RF signals present in the signal.

Internal feedback around A1 sets the closed-loop gain of the preamplifier to 40 V/V from the input pins, and the output of A) is connected to Pin 3 via a 80 k $\Omega$  resistor which is trimmed to  $\pm 3\%$ , to facilitate the low-pass filtering of the signal. The output buffer A2 has a gain of 10 V/V (using a precise 1 k $\Omega$  resistor from Pin 4 to ground) setting the precalibrated, overall gain of the AD22055, to 400 mV. This gain is easily user-configurable.

Overall gain is programmed using the following equation  $Gain = 40 + \frac{9k\Omega}{R_{\rm SUN}} V/V$

The dynamic properties of the AD22055 arc optimized for interfacing to transducers, in particular those with a Wheatstone Bridge configuration. Its rejection of large, high frequency, common-mode signals makes it superior to that of many alternative approaches. This is due to the very careful design of the input attenuator and the dose integration of this highly balanced, high impedance system with the preamplifier.

## CAUTION -

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD22057 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 –3–

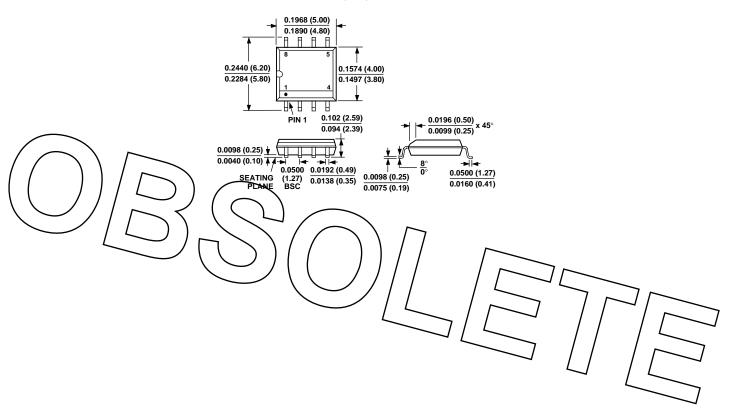

# **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

# Plastic SOIC Package (R-8)

-4-

REV. 0