# EVAL-AD2428WD1BZ A <sup>2</sup>B Evaluation Board Manual

Revision 1.1, October 2019

Part Number 82-000983-01

Analog Devices, Inc. One Technology Way Norwood, MA 02062-9106

# **Copyright Information**

© 2019 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

#### Disclaimer

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

#### Trademark and Service Mark Notice

The Analog Devices logo, Blackfin, SHARC, A<sup>2</sup>B, SigmaDSP, SigmaStudio and EngineerZone are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

# Contents

#### Preface

| Purpose of This Manual       |     |

|------------------------------|-----|

| Manual Contents              | 1–2 |

| Technical Support            | 1–2 |

| Supported Integrated Circuit | 1–2 |

| Supported Tools              | 1–2 |

| Product Information          | 1–2 |

| Analog Devices Website       | 1–3 |

| EngineerZone                 | 1–3 |

#### Using the Board

| Product Overview                                                                      | 2–1 |

|---------------------------------------------------------------------------------------|-----|

| Package Contents                                                                      | 2–2 |

| Default Configuration                                                                 | 2–2 |

| Reference Design Information                                                          | 2–3 |

| 24AA512T - 512K I <sup>2</sup> C Serial EEPROM                                        | 2–4 |

| AD2428 - Automotive Audio Bus A <sup>2</sup> B Transceiver                            | 2–4 |

| ADAU1452 - SigmaDSP Digital Audio Processor                                           | 2–4 |

| ADAU1761 - SigmaDSP Stereo, Low Power, 96 kHz, 24-Bit Audio Codec with Integrated PLL | 2–5 |

| LT8609 - 2A/3A Peak Synchronous Step-Down Regulator with 2.5µA Quiescent Current      | 2–6 |

| LT8620 - 65V, 2A Synchronous Step-Down Regulator with 2.5µA Quiescent Current         | 2–6 |

| LTC3121 - 1.5A Synchronous Step-Up DC/DC Converter                                    | 2–6 |

| LTC3621 -1A Synchronous Step-Down Regulator                                           | 2–7 |

| LTC4040 - 2.5A Battery Backup Power Manager                                           | 2–7 |

| Using the Software                                                                    | 2–7 |

| Setting up Hardware for an A <sup>2</sup> B System                                    | 2–7 |

| Setting up Software                                                                   | 2–8 |

#### Hardware Reference

| System Architecture               |

|-----------------------------------|

| Switches                          |

| Reset Pushbutton ( SW1 )          |

| Connectors                        |

| SPDIF Input ( J1 )                |

| SPDIF Output ( J2 )               |

| Audio Input/Output ( J3 and J4 )  |

| SDP (J5)                          |

| SigmaStudio ( P1 )                |

| $A^2B$ ( P2 and P3 )              |

| Power Plug ( P4 )                 |

| Power Terminal ( P5 )             |

| Battery ( P6 )                    |

| Jumpers                           |

| A <sup>2</sup> B Power ( JP1 )    |

| Hybrid/Local Power ( JP2 )        |

| Hybrid Power ( JP3 )              |

| Boot (JP4)                        |

| BCLK(JP5)                         |

| SYNC(JP6)                         |

| DRX0(JP7)                         |

| DRX1 (JP8)                        |

| DTX1(JP9)                         |

| DTX0(JP10)                        |

| ADP621 CLK (JP11)                 |

| NTC(JP12)                         |

| A <sup>2</sup> B REG ( JP13 )     |

| A <sup>2</sup> B Voltage ( JP14 ) |

| ADAU1761 MCLK Select ( JP19 )       |  |

|-------------------------------------|--|

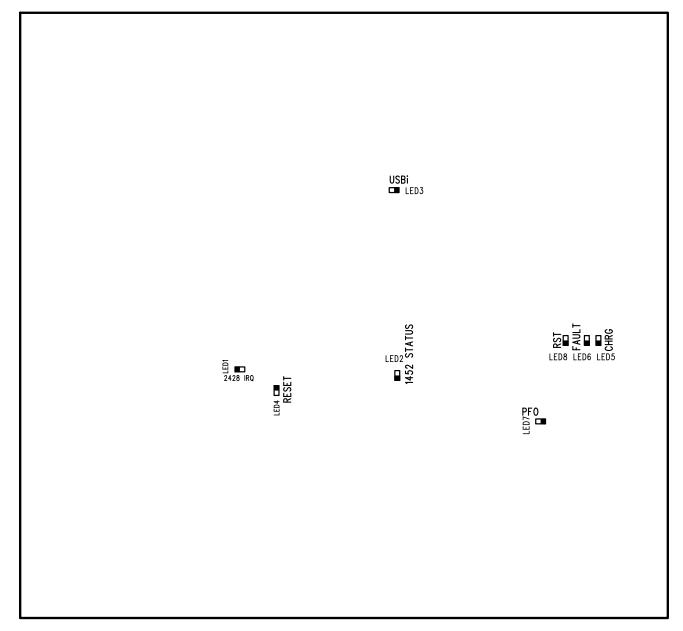

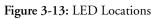

| LEDs                                |  |

| A <sup>2</sup> B Interrupt ( LED1 ) |  |

| ADAU1452 Status ( LED2 )            |  |

| USBi(led)                           |  |

| Reset ( LED4 )                      |  |

| LTC4040 Charge ( LED5 )             |  |

| LTC4040 Fault ( LED6 )              |  |

| LTC4040 PFO ( LED7 )                |  |

| LTC4040 Reset ( LED8 )              |  |

# 1 Preface

Thank you for purchasing the Analog Devices, Inc. EVAL-AD2428WD1BZ evaluation system.

In the default configuration (master mode), this evaluation board provides A<sup>2</sup>B master node functionality for an A<sup>2</sup>B network. A PC host controls the AD2428 A<sup>2</sup>B master transceiver I2C signals over the EVAL-ADUSB2EB USB-to-I2C bridge. This allows the PC to directly discover and control an A<sup>2</sup>B network, as well as to read back registers and monitor performance. Alternatively, the AD2428 master transceiver is controllable over the EI3 connector through an external uController/DSP host device like the Blackfin ADSP-BF527 processor. In the master mode, AD2428 digital audio signals interface directly to the ADAU1452 SigmaDSP<sup>®</sup>, which provides the clock and frame sync signals to the A<sup>2</sup>B network.

The evaluation board also supports local-powered slave mode with different jumper settings, where AD2428 digital audio signals could interface directly to the ADAU1761 audio codec or three microphones, without the ADAU1452 SigmaDSP sitting in the middle of the signal chain. In the slave mode, the AD2428 transceiver drives clock and frame sync signals to the ADAU1761 SigmaDSP for transmitting or receiving data. Three digital MEMS microphones with PDM output feed the A<sup>2</sup>B bus slots in the slave mode.

The SigmaStudio<sup>®</sup> graphical development tool is the programming, development, and tuning software for the SigmaDSP, A<sup>2</sup>B and Sharc processors. Familiar audio processing blocks can be wired together as in a schematic, and the compiler generates DSP-ready code and a control surface for setting and tuning parameters. This tool allows engineers with no DSP code writing experience to easily implement a DSP into their design and yet is still powerful enough to satisfy the demands of experienced DSP designers. SigmaStudio links with both Analog Devices evaluation boards and production designs to provide full in-circuit real-time IC control.

SigmaStudio includes an extensive library of algorithms to perform audio processing such as filtering, mixing, and dynamics processing, as well as basic low-level DSP functions and control blocks. Advanced record-side processing algorithms such as Enhanced Stereo Capture and wind noise detection are included in the standard libraries. Plug-in algorithms from Analog Devices and 3rd party partners can be added to SigmaStudio's drag-and-drop library.

Along with its graphical DSP signal flow development, SigmaStudio also includes other features to speed up the design cycle from product concept to release. SigmaStudio includes tools for intuitively setting control registers, calculating tables of filter coefficients, visualizing filter magnitude and phase responses, generating C header files, and sequencing a series of controls to ease your transition from SigmaStudio to system implementation on your micro-controller.

# **Purpose of This Manual**

This manual provides instructions for installing the product hardware (board). This manual describes operation and configuration of the board components and provides guidelines for running code on the board.

# **Manual Contents**

The manual consists of:

• Using the board

Provides basic board information.

• Hardware Reference

Provides information about the hardware aspects of the board.

• Bill of Materials

A companion file in PDF format that lists all of the components used on the board is available on the website at http://www.analog.com/EVAL-AD2428WD1BZ.

Please contact Analog Devices Field Application Team for documentation that is not available on website.

• Schematic

A companion file in PDF format documenting all of the circuits used on the board is available on the website at http://www.analog.com/EVAL-AD2428WD1BZ.

Please contact Analog Devices Field Application Team for documentation that is not available on website.

# **Technical Support**

Contact your Analog Devices sales office or authorized distributor. Locate one at: http://www.analog.com/adi-sales

# **Supported Integrated Circuit**

This evaluation system supports the Analog Devices AD2428 IC.

# **Supported Tools**

Information about SigmaStudio and the A<sup>2</sup>B software plug-in for the *EVAL-AD2428WD1BZ* evaluation board is available at: www.analog.com/SigmaStudio.

# **Product Information**

Information about the AD2428 product family is available at: www.analog.com/A2B

#### **Analog Devices Website**

The Analog Devices website, http://www.analog.com, provides information about a broad range of products - analog integrated circuits, amplifiers, converters, transceivers, and digital signal processors.

Also note, MyAnalog.com is a free feature of the Analog Devices website that allows customization of a web page to display only the latest information about products you are interested in. You can choose to receive weekly e-mail notifications containing updates to the web pages that meet your interests, including documentation errata against all manuals. MyAnalog.com provides access to books, application notes, data sheets, code examples, and more.

Visit MyAnalog.com to sign up. If you are a registered user, just log on. Your user name is your e-mail address.

#### EngineerZone

EngineerZone is a technical support forum from Analog Devices, Inc. It allows you direct access to ADI technical support engineers. You can search FAQs and technical information to get quick answers to your embedded processing and DSP design questions.

Use EngineerZone to connect with other DSP developers who face similar design challenges. You can also use this open forum to share knowledge and collaborate with the ADI support team and your peers. Visit http://ez.analog.com to sign up.

# 2 Using the Board

This chapter provides information on the major components and peripherals on the board, along with instructions for installing and setting up the emulation software.

## **Product Overview**

The board features:

- Analog Devices AD2428 Automotive Audio Bus A<sup>2</sup>B Transceiver

- Audio

- Analog Devices ADAU1452 SigmaDSP Digital Audio Processor

- Analog Devices ADAU1761 SigmaDSP Stereo, Low Power, 96 kHz, 24-Bit Audio Codec with Integrated PLL

- Two 3.5mm audio jacks

- Two optical SPDIF connectors

- A<sup>2</sup>B

- Two DuraClik<sup>TM</sup> connectors

- LEDs

- Eight LEDs: one board reset (red) and seven status (yellow)

- Pushbuttons

- One pushbutton: Reset

- External power supply

- CE compliant

- 12V @1.5 Amps

# Package Contents

Your EVAL-AD2428WD1BZ package contains the following items.

- EVAL-AD2428WD1BZ evaluation board

- EVAL-ADUSB2EBZ dongle

- Universal 12V DC power supply

- 1.8m twisted-pair CAT5e-rated cable with DuraClik connectors

Contact the vendor where you purchased your *EVAL-AD2428WD1BZ* evaluation board or contact Analog Devices, Inc. if any item is missing.

# **Default Configuration**

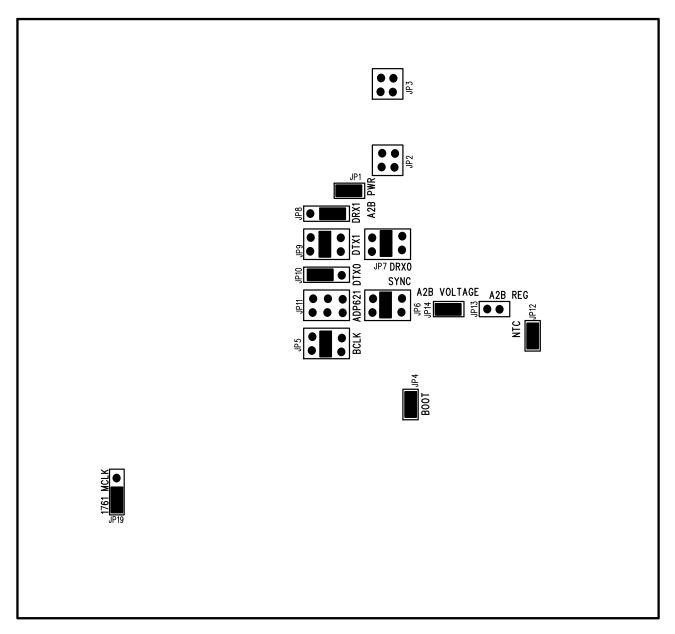

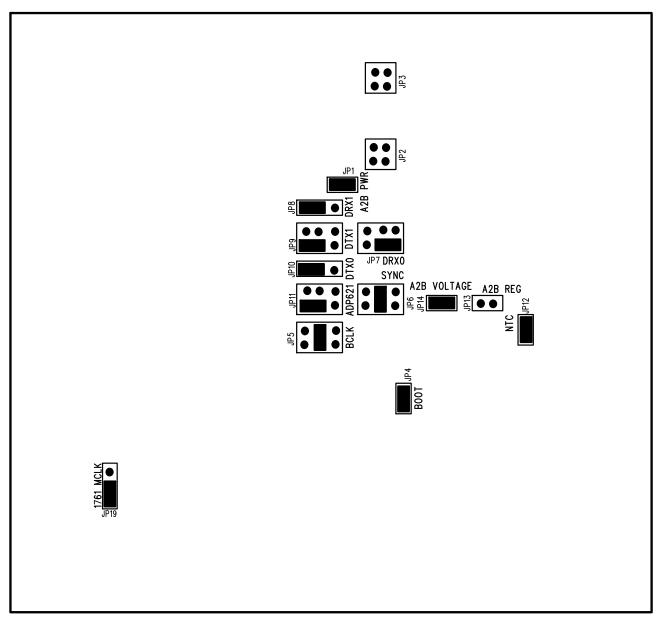

The EVAL-AD2428WD1BZ board is designed to run as a standalone unit.

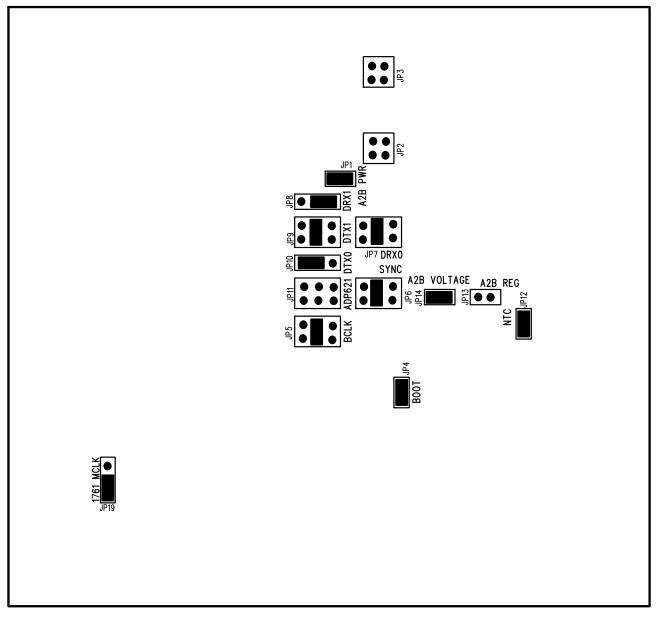

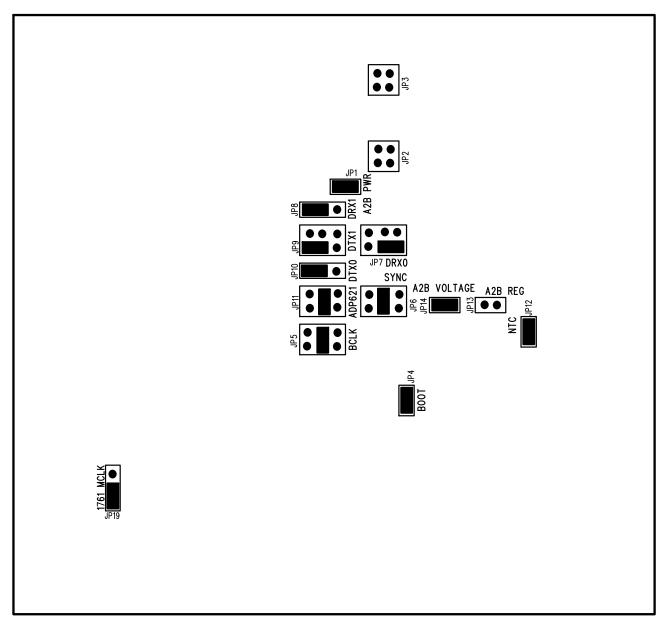

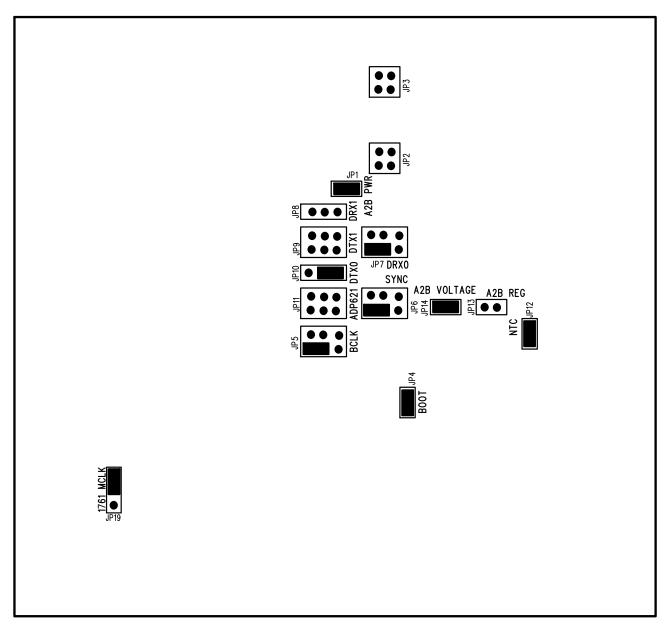

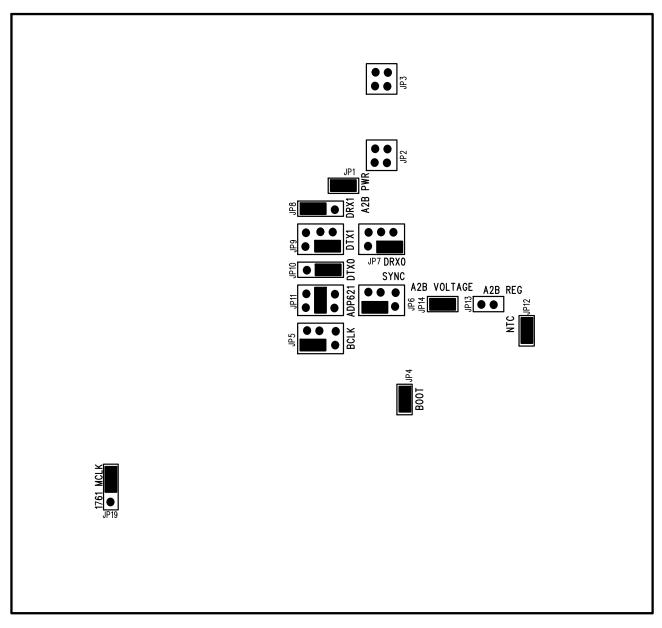

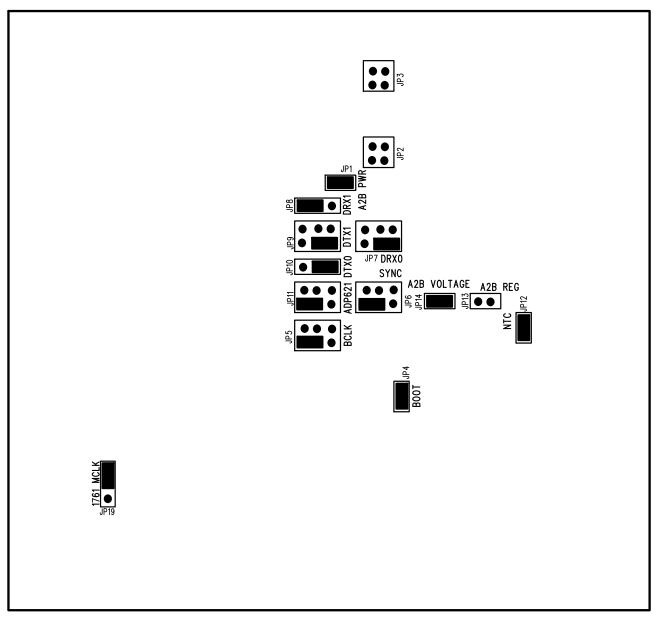

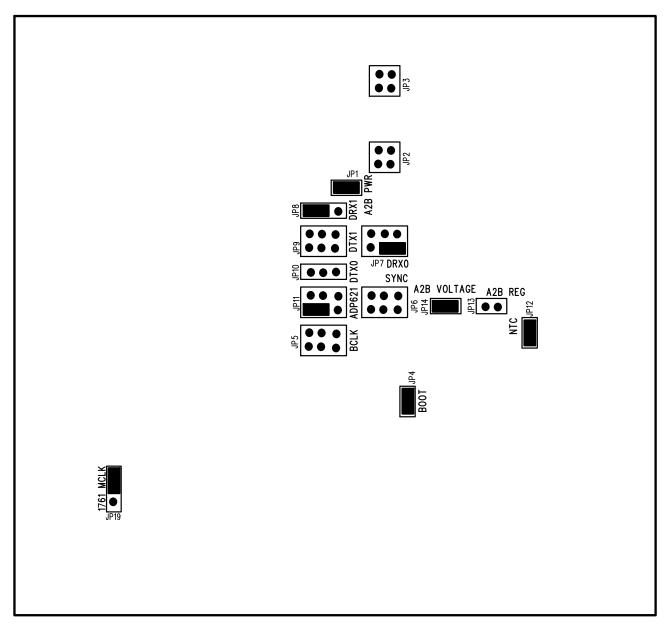

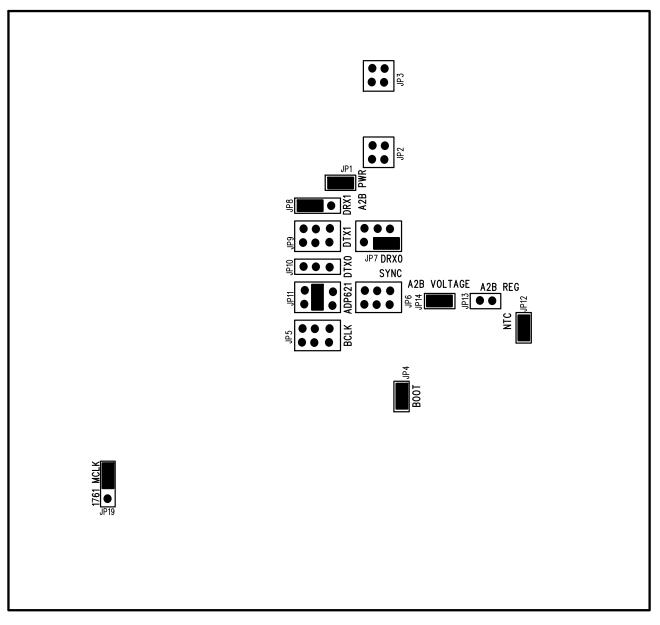

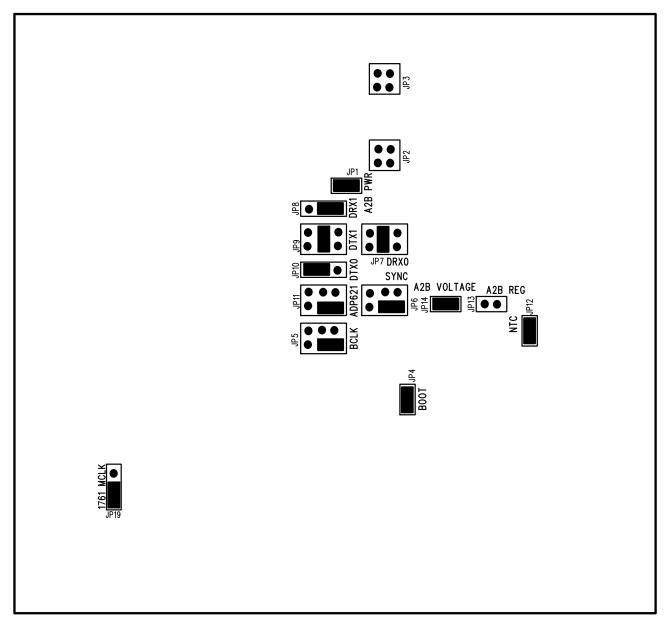

The *Default Hardware Setup* figure shows the default settings for jumpers and switches and the location of the jumpers, switches, connectors, and LEDs. Confirm that your board is in the default configuration before using the board.

Default Config

Figure 2-1: Default Hardware Setup

NOTE: Connectors on the back of the board are noted with dotted lines if applicable.

# **Reference Design Information**

A reference design info package is available for download on the Analog Devices Web site. The package provides information on the schematic design, layout, fabrication, and assembly of the board.

The information can be found at:

```

http://www.analog.com/EVAL-AD2428WD1BZ

```

# 24AA512T - 512K I<sup>2</sup>C Serial EEPROM

The Microchip Technology Inc. 24AA512 is a 512Kb (64K x 8) Serial Electrically Erasable PROM (EEPROM), capable of operation across a broad voltage range (1.7V to 5.5V). It has been developed for advanced, low-power applications such as personal communications and data acquisition. This device also has a page write capability of up to 128 bytes of data. This device is capable of both random and sequential reads up to the 512K boundary. Functional address lines allow up to eight devices on the same bus, for up to 4 Mbit address space. This device is available in the standard 8-pin plastic DIP, SOIJ and DFN packages.

# AD2428 - Automotive Audio Bus A<sup>2</sup>B Transceiver

The Automotive Audio Bus (A<sup>2</sup>B<sup>®</sup>) provides a multichannel, I2S/TDM link over distances of up to 15 m between nodes. It embeds bidirectional synchronous pulse-code modulation (PCM) data (for example, digital audio), clock, and synchronization signals onto a single differential wire pair. A<sup>2</sup>B supports a direct point to point connection and allows multiple, daisy-chained nodes at different locations to contribute and/or consume time division multiplexed channel content.

A<sup>2</sup>B is a single-master, multiple-slave system where the transceiver chip at the host controller is the master. The master generates clock, synchronization, and framing for all slave nodes. The master A<sup>2</sup>B chip is programmable over a control bus (I<sup>2</sup>C) for configuration and read back. An extension of this control bus is embedded in the A<sup>2</sup>B data stream, which grants direct access of registers and status information on slave transceivers as well as I<sup>2</sup>C to I<sup>2</sup>C communication over distance.

The transceiver can connect directly to general-purpose digital signal processors (DSPs), field-programmable gate arrays (FPGAs), application specific integrated circuits (ASICs), microphones, analog-to-digital converters (ADCs), digital-toanalog converters (DACs), and codecs through a multichannel I<sup>2</sup>S/TDM interface. It also provides a pulse density modulation (PDM) interface for direct connection of up to four PDM digital microphones.

Finally, the transceiver also supports an A<sup>2</sup>B bus powering feature, where the master node supplies voltage and current to the slave nodes over the same daisy-chained, twisted pair wire cable as used for the communication link.

# ADAU1452 - SigmaDSP Digital Audio Processor

The ADAU1452 is a automotive qualified audio processors that far exceed the digital signal processing capabilities of earlier SigmaDSP<sup>®</sup> devices. The restructured hardware architecture is optimized for efficient audio processing. The audio processing algorithms are realized in sample-by-sample and block-by-block paradigms that can both be executed simultaneously in a signal processing flow created using the graphical programming tool, SigmaStudio<sup>®</sup>. The restructured digital signal processor (DSP) core architecture enables some types of audio processing algorithms to be executed using significantly fewer instructions than were required on previous SigmaDSP generations, leading to vastly improved code efficiency.

The 1.2 V, 32-bit DSP core can run at frequencies of up to 294.912 MHz and execute up to 6144 instructions per sample at the standard sample rate of 48 kHz. However, in addition to industry standard rates, a wide range of sample rates are available. The integer PLL and flexible clock generator hardware can generate up to 15 audio sample rates simultaneously. These clock generators, along with the on board asynchronous sample rate converters (ASRCs) and a flexible hardware audio routing matrix, make the ADAU1452 ideal audio hubs that greatly simplify the design of complex multirate audio systems.

The ADAU1452 interfaces with a wide range of ADCs, DACs, digital audio devices, amplifiers, and control circuitry, due to their highly configurable serial ports, S/PDIF interfaces, and multipurpose input/output pins. They can also directly interface with PDM output MEMS microphones, thanks to integrated decimation filters specifically designed for that purpose.

Independent slave and master I2C/SPI control ports allow the ADAU1452 not only to be programmed and configured by an external master device, but also to act as masters that can program and configure external slave devices directly. This flexibility, combined with self boot functionality, enables the design of standalone systems that do not require any external input to operate.

The power efficient DSP core executes full programs while consuming only a few hundred milliwatts (mW) of power and can run at a maximum program load while consuming less than a watt, even in worst case temperatures exceeding 100°C. This relatively low power consumption and small footprint make the ADAU1452 ideal replacements for large, general-purpose DSPs that consume more power at the same processing load.

# ADAU1761 - SigmaDSP Stereo, Low Power, 96 kHz, 24-Bit Audio Codec with Integrated PLL

The ADAU1761 is a low power, stereo audio codec with integrated digital audio processing that supports stereo 48 kHz record and playback at 14 mW from a 1.8 V analog supply. The stereo audio ADCs and DACs support sample rates from 8 kHz to 96 kHz as well as a digital volume control.

The SigmaDSP core features 28-bit processing (56-bit double precision). The processor allows system designers to compensate for the real-world limitations of microphones, speakers, amplifiers, and listening environments, resulting in a dramatic improvement in the perceived audio quality through equalization, multiband compression, limiting, and third-party branded algorithms.

The SigmaStudio<sup>®</sup> graphical development tool is used to program the ADAU1761. This software includes audio processing blocks such as filters, dynamics processors, mixers, and low level DSP functions for fast development of custom signal flows.

The record path includes an integrated microphone bias circuit and six inputs. The inputs can be mixed and muxed before the ADC, or they can be configured to bypass the ADC. The ADAU1761 includes a stereo digital microphone input.

The ADAU1761 includes five high power output drivers (two differential and three single-ended), supporting stereo head-phones, an earpiece, or other output transducer. AC-coupled or capless configurations are supported. Individual fine level controls are supported on all analog outputs. The output mixer stage allows for flexible routing of audio.

# LT8609 - 2A/3A Peak Synchronous Step-Down Regulator with 2.5µA Quiescent Current

The LT8609 is a compact, high efficiency, high speed synchronous monolithic step-down switching regulator that consumes only 1.7µA of non switching quiescent current. The LT8609 can deliver 2A of continuous current with peak loads of 3A (<1sec). Burst Mode operation enables high efficiency down to very low output currents while keeping the output ripple below 10mVP-P. A SYNC pin allows synchronization to an external clock, or spread spectrum modulation for low EMI operation. Internal compensation with peak current mode topology allows the use of small inductors and results in fast transient response and good loop stability. The EN/UV pin has an accurate 1V threshold and can be used to program VIN UVLO or to shut down the part. A capacitor on the TR/SS pin programs the output voltage ramp rate during start-up while the PG flag signals when VOUT is within ±8.5% of the programmed output voltage as well as fault conditions.

# LT8620 - 65V, 2A Synchronous Step-Down Regulator with 2.5 $\mu A$ Quiescent Current

The LT8620 is a compact, high efficiency, high speed synchronous monolithic step-down switching regulator that accepts a wide input voltage range up to 65V, and consumes only 2.5 $\mu$ A of quiescent current. Top and bottom power switches are included with all necessary circuitry to minimize the need for external components. Low ripple Burst Mode operation enables high efficiency down to very low output currents while keeping the output ripple below  $10mV_{P-P}$ . A SYNC pin allows synchronization to an external clock. Internal compensation with peak current mode topology allows the use of small inductors and results in fast transient response and good loop stability. The EN/UV pin has an accurate 1V threshold and can be used to program  $V_{IN}$  undervoltage lockout or to shut down the LT8620 reducing the input supply current to  $1\mu$ A. A capacitor on the TR/SS pin programs the output voltage ramp rate during start-up. The PG flag signals when  $V_{OUT}$  is within ±9% of the programmed output voltage as well as fault conditions. The LT8620 is available in small 16-Lead MSOP and 3mm × 5mm QFN packages with exposed pads for low thermal resistance.

# LTC3121 - 1.5A Synchronous Step-Up DC/DC Converter

The The LTC3121 is a synchronous step-up DC/DC converter with true output disconnect and inrush current limiting. The 1.5A current limit along with the ability to program output voltages up to 15V makes the LTC3121 well suited for a variety of demanding applications. Once started, operation will continue with inputs down to 500mV, extending run time in many applications.

The LTC3121 features output disconnect in shutdown, dramatically reducing input power drain and enabling VOUT to completely discharge. Adjustable PWM switching from 100kHz to 3MHz optimizes applications for highest efficiency or smallest solution footprint. The oscillator can also be synchronized to an external clock for noise sensitive applications. Selectable Burst Mode operation reduces quiescent current to 25µA, ensuring high efficiency across the entire load range. An internal soft-start limits inrush current during start-up.

Other features include a <1µA shutdown current and robust protection under short-circuit, thermal overload, and output overvoltage conditions.

# LTC3621 -1A Synchronous Step-Down Regulator

The The LTC3621 is a high efficiency 17V, 1A synchronous monolithic step-down regulator. The switching frequency is fixed to 1MHz or 2.25MHz with a  $\pm$ 40% synchronizing range. The regulator features ultralow quiescent current and high efficiencies over a wide VOUT range.

The step-down regulator operates from an input voltage range of 2.7V to 17V and provides an adjustable output range from 0.6V to VIN while delivering up to 1A of output current. A user-selectable mode input is provided to allow the user to trade off ripple noise for light load efficiency; Burst Mode operation provides the highest efficiency at light loads, while pulse-skipping mode provides the lowest voltage ripple. The MODE pin can also be used to allow the user to sync the switching frequency to an external clock.

# LTC4040 - 2.5A Battery Backup Power Manager

The LTC4040 is a complete 3.5V to 5.5V supply rail battery backup system. It contains a high current step-up DC/DC regulator to back up the supply from a single-cell Li-Ion or LiFePO4 battery. When external power is available, the step-up regulator operates in reverse as a stepdown battery charger.

The LTC4040's adjustable input current limit function reduces charge current to protect the main supply from overload while an external disconnect switch isolates the external supply during backup. When the input supply drops below the adjustable PFI threshold, the 2.5A boost regulator delivers power from the battery to the system output.

An optional input overvoltage protection (OVP) circuit protects the LTC4040 from high voltage damage at the VIN pin. One logic input selects either the Li-Ion or the LiFePO4 battery option, and two other logic inputs program the battery charge voltage to one of four levels suitable for backup applications.

# Using the Software

The *EVAL-AD2428WD1BZ* evaluation board is intended to serve as the master node hosting an A<sup>2</sup>B system. It can also function as either a local or bus-powered slave node on the A<sup>2</sup>B bus. A host processor on the master node interfaces directly with the A<sup>2</sup>B master transceiver through which it programs and reads the register spaces of all discovered slave transceivers. This configuration allows a full system initialization at start-up and status monitoring during operation. The examples furnished with the *EVAL-AD2428WD1BZ* A<sup>2</sup>B master evaluation board assume a connection to specific slave boards, as noted in the following sections.

#### Setting up Hardware for an A<sup>2</sup>B System

Use the following sequence to set up the hardware for a three node A<sup>2</sup>B system.

- 1. Assemble the example A<sup>2</sup>B system by connecting the indicated A<sup>2</sup>B evaluation boards as follows:

- Master (EVAL-AD2428WD1BZ) Connect the B-side (P2) to the A-side on the slave0 board (J7)

- Slave0 (EVAL-AD2428WC1BZ) Connect the B-side (J8) to the A-side on the slave1 board (J7)

- Slave1 (EVAL-AD2428WB1BZ)

- 2. Connect the PC over a USB cable and using the EVAL-ADUSB2EBZ USBi I<sup>2</sup>C programmer to the SigmaStudio header (P1) on the master board.

- 3. Connect an audio source to the stereo line input of the slave1 board (J2).

- 4. Connect headphones to the audio output of the master board (J4).

- 5. Plug the wall-mount 12V power supply (1.5 A) into an outlet and connect it to the power jack on the master board (P4).

#### Setting up Software

Use the following programming sequence to set up and operate the A<sup>2</sup>B Software.

- 1. Install the SigmaStudio (Rev. 4.4 or later) and A<sup>2</sup>B Software for Windows/Baremetal (Rev 19.3.0 or later) software from the EVAL-AD2428WD1BZ product page.

- 2. Copy the A2B.dll and A2Bstack.dll driver files from the installation directory (default) C:\Analog Devices\ADI\_A2B\_Software-Rel19.3.0\GUI\x86\_x64) into the SigmaStudio installation ((default) C:\Program Files\Analog Devices\SigmaStudio 4.4). Start SigmaStudio and verify that the A2B.dll file is selected under Tools→AddInsBrowser. Save before exiting.

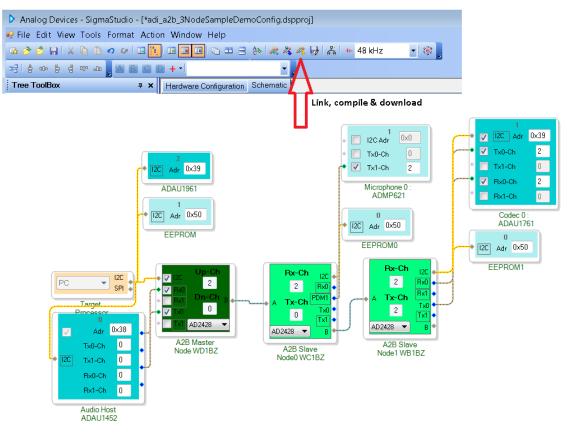

- 3. Open the adi\_a2b\_3NodeSampleDemo.dspproj example project, which is located in the (default) C:\Analog Devices\ADI\_A2B\_Software-Rel19.3.0\Schematics\BF \A2BSchematics directory. Click the Link-Compile-Download icon, as shown in the Software Schematic for adi\_a2b\_3NodeSampleDemoConfig.dspproj A<sup>2</sup>B Example Project figure.

$Figure \ 2-2: Software \ Schematic \ for \ \texttt{adi}\_\texttt{a2b}\_\texttt{3NodeSampleDemoConfig.dspproj} \ A^2B \ Example \ Project$

- 4. Before running the demo, follow the Setting up Hardware for an A<sup>2</sup>B System for a three node A<sup>2</sup>B system guidance. The sample demo configuration appears as shown in the Software Schematic for adi\_a2b\_3Node-SampleDemoConfig.dspproj A<sup>2</sup>B Example Project figure. The audio source connected to the slave1 EVAL-AD2428WB1BZ board plays out of the headphones connected to the master EVAL-AD2428WD1BZ board. The microphone audio from the slave0 EVAL-AD2428WC1BZ board plays out of the slave1 EVAL-AD2428WB1BZ board.

- 5. Use the configuration settings shown in the EVAL-AD2428WB1BZ Evaluation Board Example Slot Assignments figure to properly interface the codec with the A<sup>2</sup>B transceiver. The EVAL-AD2428WB1BZ Evaluation Board Example Slot Assignments figure shows an example of a downstream data configuration where two slots are consumed from the A<sup>2</sup>B bus and sent to the local DAC while two additional slots are contributed by the transceiver taking data from the local ADC.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 🔏 A2B Slave Node1 WB1BZ Properties 📃 🔳 🎫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General View Register View Stream View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | General View Register View Stream View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Slave Config<br>I2C Interface Frequency 400 kHz<br>Super Frame Rate 48.0 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Upstream         Slots to Consume           Slots Received at Port B         0         8         16         24           1         9         17         25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Node Response Cycles 0x68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Slots Passed Up from Port B         0         2         10         18         26           3         11         19         27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Slots Contributed (Local)         2         4         12         20         28           5         13         21         29         6         14         22         30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Spread Spectrum Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Receive Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Mode     No Spread <ul> <li>Frequency</li> <li>4x</li> <li>4x</li> <li>Example 1</li> <li>Example 2</li> <li>Frequency</li> <li>Frequen</li></ul> | Slots Transmitted at Port A 2 No. of Slots 0 Max 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Downstream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Enable Consume/Contribute 🔽 Slots to Consume                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Image: Slots Received at Port A         Image: Slots R |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Slots Passed Down from Port A         0         3         11         19         27           5         13         21         28         5         13         21         29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Slots Contributed (Local)         0         6         14         22         30           7         15         23         31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Config and Control Slot Config   Audio Config   Rate and ClkOut   Interrupt Config   Pin Config   ()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Receive Offset 0 🗭 No. of Slots 2 Max 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Master Address 0x68 Bus Address 0x69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Slots Transmitted at Port B 0 Broadcast Downstream Slots 0 🚖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A-Side Cable Length (m) 4.0 🖶 🔲 Use Configuration from EEPRDM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Enable Manual Slot Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Figure 2-3: EVAL-AD2428WB1BZ Evaluation Board Example Slot Assignments

- 6. The ADAU1452 SigmaDSP on the master EVAL-AD2428WD1BZ board supplies the clock (SYNC) to the AD2428W transceiver. For development of customized ADAU1452 audio flows, disable the automatic programming of the ADAU1452 SigmaDSP during discovery. Right-click the ADAU1452 block and select Peripheral Properties in the A<sup>2</sup>B software schematics.

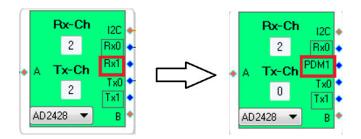

- 7. To test the PDM microphones on the slave1 EVAL-AD2428WB1BZ board, make the connections shown in the Software Schematic for adi\_a2b\_3NodeSampleDemoConfig.dspproj A<sup>2</sup>B Example Project figure. Click RX1 in the A<sup>2</sup>B cell to change the input to PDM, as shown in the Changing AD2428W Pin Function from DRX1 to PDM1 figure.

The headphones connected to the master EVAL-AD2428WD1BZ board can be used to listen to the microphone data coming from the slave1 EVAL-AD2428WB1BZ board.

Figure 2-4: Changing AD2428W Pin Function from DRX1 to PDM1

8. Use the *Stream Config* tab (right-click on *Target Processor* → *Device Properties* → *Stream Config*) to define audio streams across the nodes. (See the *Stream Configuration* figure). The stream assignments configure the upstream and downstream slot settings across the nodes.

| rocessor | Device Properties                                      | A2B Stream Configuration            |                                    |

|----------|--------------------------------------------------------|-------------------------------------|------------------------------------|

|          | Stream Config                                          |                                     | e (                                |

|          | Import Bus Config File                                 | Stream Definition Stream Assignment |                                    |

|          | Export System Config Files<br>Save Schematic in EEPROM |                                     | + - 🗶 1 .                          |

|          | Delete                                                 | Stream Stream Name                  | Fs (kHz) Data No.                  |

|          | Cut                                                    | 0 Mic                               | 48 24 2                            |

|          | Сору                                                   | 1 Stereo                            | 48 24 2                            |

|          | Paste                                                  |                                     |                                    |

|          | ZoomToSelection                                        | A2B Stream Configuration            |                                    |

|          | Disable This Control                                   | Stream Definition Stream Assignment | G.                                 |

|          |                                                        | Auto Slot Calculate View By Name    | <- Stream Destination -            |

|          |                                                        | Stream Name                         | Stream Source Master Slave 0 Slave |

|          |                                                        | Mic                                 | Slave 1 🔽 🗌                        |

|          |                                                        | Stereo                              | Slave 0 🔻 🗖 🔽                      |

Figure 2-5: Stream Configuration

# **3 Hardware Reference**

This chapter describes the hardware design of the EVAL-AD2428WD1BZ evaluation board.

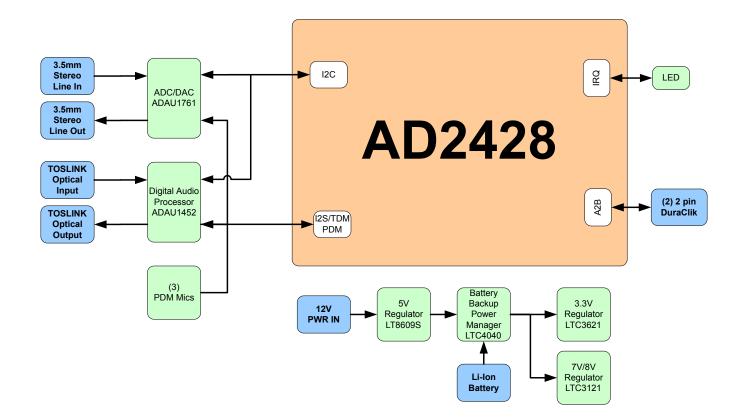

# System Architecture

The board's configuration is shown in the *Block Diagram* figure.

Figure 3-1: Block Diagram

## Switches

This section describes operation of the switches. The switch locations are shown in the Switch Locations figure.

Figure 3-2: Switch Locations

#### Reset Pushbutton ( SW1 )

The reset pushbutton resets the ADAU1452 SigmaDSP. Reset (  $\tt LED4$  ) is used to indicate when the board is in reset.

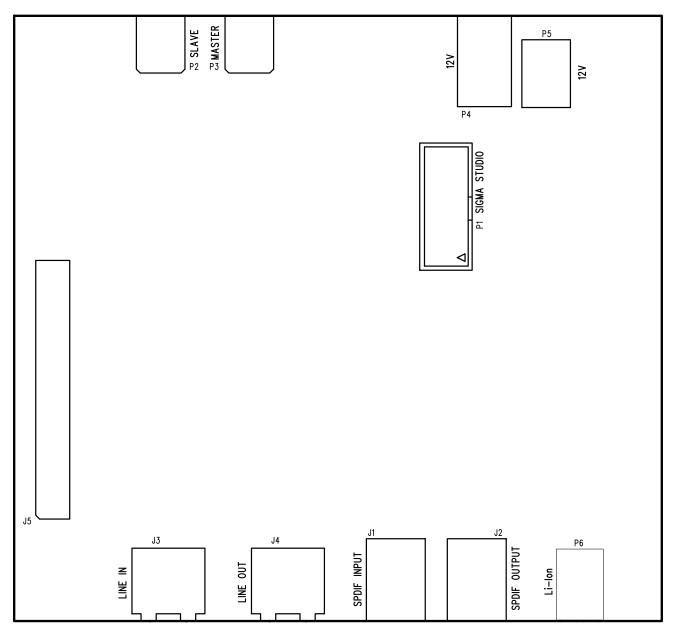

# Connectors

This section describes connector functionality and provides information about mating connectors. The connector locations are shown in the *Connector Locations* figure.