## Low Cost 10-Bit Monolithic D/A Converter

AD561

#### **SCOPE** 1.0

This specification documents the detailed requirements for Analog Devices space qualified die including die qualification as described for Class K in MIL-PRF-38534, Appendix C, Table C-II except as modified herein.

The manufacturing flow described in the STANDARD DIE PRODUCTS PROGRAM brochure at http://www.analog.com/aerospace is to be considered a part of this specification.

This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at www.analog.com/AD561

2.0 Part Number. The complete part number(s) of this specification follow:

> Part Number Description

AD561-000C Low Cost 10-Bit Monolithic D/A Converter

#### 3.0 Die Information

### 3.1 Die Dimensions

| Die Size          | Die Thickness  | Bond Pad Metalization |

|-------------------|----------------|-----------------------|

| 106 mil x 153 mil | 19 mil ± 2 mil | Al/Cu                 |

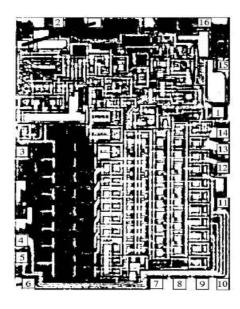

#### 3.2 **Die Picture**

- 1. GND

- 2. BPOS

- 3. -Vs

- 4. LSB

- 5. BIT 9

- 6. BIT 8

- 7. BIT 7

- 8. BIT 6

- 9. BIT 5

- 10. BIT 4

- 11. BIT 3

- 12. BIT 2

- 13. MSB

- 14. + Vs

- 15.  $I_{OUT}$

- 16. RFB

ASD0012515 Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

## **AD561**

## 3.3 Absolute Maximum Ratings 1/2/

| Digital Input Voltage (V <sub>IN</sub> )      | V <sub>CC</sub> to Ground |

|-----------------------------------------------|---------------------------|

| Output Voltage Compliance (V <sub>OUT</sub> ) | -2V to +10V               |

| 10V Span Resistor to Ground                   | $V_{CC}$ to $V_{EE}$      |

| Bipolar Offset Resistor To Ground             | $V_{CC}$ to $V_{EE}$      |

| Operating Temperature Range                   | -55°C to +125°C           |

| Storage Temperature Range                     | -65°C to +150°C           |

| Supply Voltage                                | ±16.5V                    |

| Junction Temperature (T <sub>J</sub> )        | 175°C                     |

### **Absolute Maximum Ratings Notes**

- 1/  $T_A = 25$ °C, unless otherwise noted.

- Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

### 4.0 <u>Die Qualification</u>

In accordance with class-K version of MIL-PRF-38534, Appendix C, Table C-II, except as modified herein.

- (a) Qual Sample Size and Qual Acceptance Criteria 25/2

- (b) Qual Sample Package Sidebrazed DIP

- (c) Pre-screen electrical test over temperature performed post-assembly prior to die qualification.

| Table I - Dice Electrical Characteristics |                  |                                                                          |     |              |         |  |  |

|-------------------------------------------|------------------|--------------------------------------------------------------------------|-----|--------------|---------|--|--|

| Parameter                                 | Symbol           | Conditions Lir<br>1/ M                                                   |     | Limit<br>Max | Units   |  |  |

| Relative Accuracy                         | RA               |                                                                          |     | ±0.5         | LSB     |  |  |

| Differential Nonlinearity                 | DNL              | Major carry transitions                                                  |     | ±1           | LSB     |  |  |

| Gain Error <u>2</u> /                     | A <sub>E</sub>   | With fixed 25Ω resistor                                                  |     | ±0.5         | % of FS |  |  |

| Unipolar Offset Error <u>2</u> /          | Vos              |                                                                          |     | ±0.05        | % of FS |  |  |

| Bipolar Zero Error                        | B <sub>PZE</sub> | With 10Ω resistor                                                        |     | ±3.5         | LSB     |  |  |

| Output Current                            | Іоит             | Digital inputs at logic "1"                                              | 1.5 | 2.4          | mA      |  |  |

| Power Supply Gain Sensitivity             | P <sub>SS1</sub> | Vcc, +4.5V to +5.5V<br>Vcc, +13.5V to +16.5V                             |     | ±10          | PPM of  |  |  |

|                                           | P <sub>SS2</sub> | V <sub>EE</sub> , -10.8V to -13.2V<br>V <sub>EE</sub> , -13.2V to -16.5V |     | ±25          | FS/%    |  |  |

| Table I - Dice Electrical Characteristics (continued) |                 |                                    |              |              |       |  |

|-------------------------------------------------------|-----------------|------------------------------------|--------------|--------------|-------|--|

| Parameter                                             | Symbol          | Conditions<br><u>1</u> /           | Limit<br>Min | Limit<br>Max | Units |  |

| Power Supply Current <u>2</u> /                       | Icc             | V <sub>CC</sub> , +4.5V to +16.5V  | -            | 10           | Α     |  |

|                                                       | I <sub>EE</sub> | V <sub>EE</sub> , -10.8V to -16.5V |              | 16           | mA    |  |

| Power Dissipation                                     | P <sub>D</sub>  |                                    |              | 500          | mW    |  |

| Digital Input High Voltage                            | V <sub>IH</sub> |                                    | 2.0          |              | V     |  |

| Digital Input Low Voltage                             | VIL             |                                    |              | 0.8          | V     |  |

| Digital Input High Current                            | Ін              | Digital "1" = 15V                  |              | ±100         | nA    |  |

| Digital Input Low Current                             | I <sub>IL</sub> | Digital "0" = 0V                   |              | ±25          | μΑ    |  |

### Table I Notes:

$<sup>\</sup>begin{array}{ll} \underline{1/} & V_{CC} = +5 \text{V, } V_{EE} = -15 \text{V, } T_A = 25^{\circ}\text{C, unless otherwise specified.} \\ \underline{2/} & \text{Also tested in CMOS mode. } V_{CC} = +15 \text{V, } V_{EE} = -15 \text{V, } V_{IH} = 10.5 \text{V, } V_{IL} = 4.5 \text{V.} \\ \end{array}$

# **AD561**

| Table II - Electrical Characteristics for Qual Samples |                                       |                                                                          |                |              |              |              |  |  |

|--------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------|----------------|--------------|--------------|--------------|--|--|

| Parameter                                              | Parameter Symbol Conditions Subgroups |                                                                          | Sub-<br>groups | Limit<br>Min | Limit<br>Max | Units        |  |  |

| Relative Accuracy                                      | RA                                    |                                                                          | 1              |              | ±0.5         | LSB          |  |  |

| Differential Nonlinearity                              | DNL                                   | Major carry transitions                                                  | 1, 2, 3        |              | ±1           | LSB          |  |  |

| Gain Error <u>2</u> /                                  | AE                                    | With fixed $25\Omega$ resistor                                           | 1              |              | ±0.5         | % of FS      |  |  |

| Gain Error Temperature Coefficient                     | TCA <sub>E</sub>                      |                                                                          | 2, 3           |              | ±60          | ppm of FS/°C |  |  |

| Unipolar Offset Error <u>2</u> /                       | Vos                                   |                                                                          | 1              |              | ±0.05        | % of FS      |  |  |

| Unipolar Error Temperature<br>Coefficient              | TCVos                                 |                                                                          | 2, 3           |              | ±10          | ppm of FS/°C |  |  |

| Bipolar Zero Error                                     | B <sub>PZE</sub>                      | With 10Ω resistor                                                        | 1              |              | ±3.5         | LSB          |  |  |

| Bipolar Zero Error Temperature<br>Coefficient          | TCB <sub>PZE</sub>                    |                                                                          | 2, 3           |              | ±20          | ppm of FS/°C |  |  |

| Output Current                                         | I <sub>OUT</sub>                      | Digital inputs<br>at logic "1"                                           | 1              | 1.5          | 2.4          | mA           |  |  |

|                                                        | P <sub>SS1</sub>                      | V <sub>CC</sub> , +4.5V to +5.5V<br>V <sub>CC</sub> , +13.5V to +16.5V   |                |              | ±10          | PPM of FS/%  |  |  |

| Power Supply Gain Sensitivity                          | P <sub>SS2</sub>                      | V <sub>EE</sub> , -10.8V to -13.2V<br>V <sub>EE</sub> , -13.2V to -16.5V | 1              |              | ±25          |              |  |  |

|                                                        | lcc                                   | V <sub>CC</sub> , +4.5V to +16.5V                                        |                |              | 10           |              |  |  |

| Power Supply Current <u>2</u> /                        | I <sub>EE</sub>                       | V <sub>EE</sub> , -10.8V to -16.5V                                       | 1              |              | 16           | mA           |  |  |

| Power Dissipation                                      | P <sub>D</sub>                        |                                                                          | 1              |              | 500          | mW           |  |  |

| Digital Input High Voltage                             | V <sub>IH</sub>                       |                                                                          | 1              | 2.0          |              | V            |  |  |

| Digital Input Low Voltage                              | VIL                                   |                                                                          | 1              |              | 0.8          | V            |  |  |

| Digital Input High Current                             | Ін                                    | Digital "1" = 15V                                                        | 1              |              | ±100         | nA           |  |  |

| Digital Input Low Current                              | I <sub>IL</sub>                       | Digital "0" = 0V                                                         | 1              |              | ±25          | μА           |  |  |

## Table II Notes:

$V_{CC} = +5V, \ V_{EE} = -15V, \ unless \ otherwise \ specified.$  Also tested in CMOS mode.  $V_{CC} = +15V, \ V_{EE} = -15V, \ V_{IH} = 10.5V, \ V_{IL} = 4.5V.$

| Table III - Life Test Endpoint and Delta Parameter |                                                                               |                |                    |     |                      |     |              |       |

|----------------------------------------------------|-------------------------------------------------------------------------------|----------------|--------------------|-----|----------------------|-----|--------------|-------|

| (Product is tes                                    | (Product is tested in accordance with Table II with the following exceptions) |                |                    |     |                      |     |              |       |

| Parameter                                          | Symbol                                                                        | Sub-<br>groups | Post Burn In Limit |     | Post Life Test Limit |     | Life<br>Test | Units |

|                                                    |                                                                               | groups         | Min                | Max | Min                  | Max | Delta        |       |

| Power Supply Current                               | <b>I</b> cc                                                                   | 1              |                    | 10  |                      | 13  | ±3           | mA    |

| rower supply current                               | I <sub>EE</sub>                                                               | 1              |                    | 16  |                      | 19  | H            | IIIA  |

| Output Current                                     | louт                                                                          | 1              | 1.5                | 2.4 | 1.4                  | 2.5 | ±5           | mA    |

#### 5.0 **Life Test/Burn-In Information**

- 5.1

- HTRB is not applicable for this drawing.

Burn-in is per MIL-STD-883 Method 1015 test condition B or C.

Steady state life test is per MIL-STD-883 Method 1005. 5.2

- 5.3

# **AD561**

| Rev | Description of Change                                                           | Date           |

|-----|---------------------------------------------------------------------------------|----------------|

| Α   | Initiate                                                                        | 4-Nov-111      |

| В   | Update web address                                                              | Jan. 25, 2002  |

| С   | Update web address. Change IOUT delta from 5 to 0.5.                            | Aug. 14, 2003  |

| D   | Update header/footer and add to 1.0 Scope description.                          | Feb. 26, 2008  |

| E   | Add Junction Temperature (T <sub>J</sub> )175°C to 3.3 Absolute Max. Ratings    | March 28, 2008 |

| F   | Updated Section 4.0c note to indicated pre-screen temp testing being performed. | June 6 2009    |

| G   | Updated Fonts and Sizes to ADI Standards                                        | 22-Sept-2011   |

|     |                                                                                 |                |

|     |                                                                                 |                |