## ADC Architectures IV: Sigma-Delta ADC Advanced Concepts and Applications

## by Walt Kester

### INTRODUCTION

<u>Tutorial MT-022</u> discussed the basics of  $\Sigma$ - $\Delta$  ADCs. In this tutorial, we will look at some of the more advanced concepts including idle tones, multi-bit  $\Sigma$ - $\Delta$ , MASH, bandpass  $\Sigma$ - $\Delta$ , as well as some example applications.

#### **IDLE TONE CONSIDERATIONS**

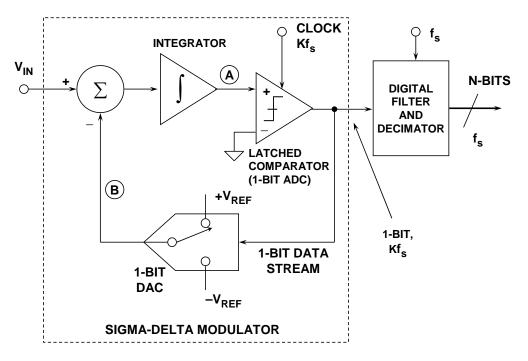

In our discussion of  $\Sigma$ - $\Delta$  ADCs up to this point, we have made the assumption that the quantization noise produced by the  $\Sigma$ - $\Delta$  modulator (see Figure 1) is random and uncorrelated with the input signal. Unfortunately, this is not entirely the case, especially for the first-order modulator. Consider the case where we are averaging 16 samples of the modulator output in a 4-bit  $\Sigma$ - $\Delta$  ADC.

Figure 1: First-Order Sigma-Delta ADC

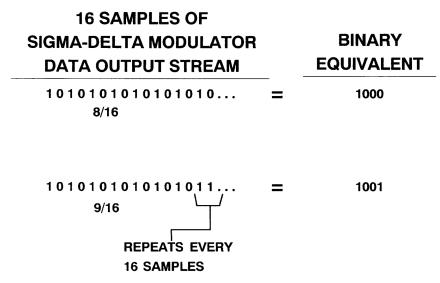

Figure 2 shows the bit pattern for two input signal conditions: an input signal having the value 8/16, and an input signal having the value 9/16. In the case of the 9/16 signal, the modulator output bit pattern has an extra "1" every 16th output. This will produce energy at Kf<sub>s</sub>/16, which translates into an unwanted tone. If the oversampling ratio (K) is less than 8, this tone will fall

into the passband. In audio, the idle tones can be heard just above the noise floor as the input changes from negative to positive fullscale.

Figure 2: Repetitive Bit Pattern in Sigma-Delta Modulator Output

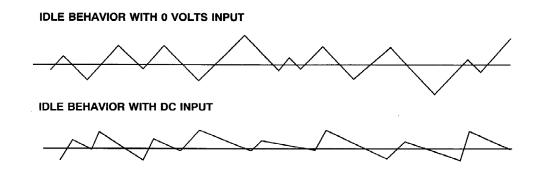

Figure 3 shows the correlated idling pattern behavior for a first order  $\Sigma$ - $\Delta$  modulator, and Figure 4 shows the relatively uncorrelated pattern for a second-order modulator. For this reason, virtually all  $\Sigma$ - $\Delta$  ADCs contain at least a second-order modulator loop, and some use up to fifth-order loops.

IDLE BEHAVIOR WITH 0 VOLTS INPUT

IDLE BEHAVIOR WITH DC INPUT SHOWING CORRELATED IDLING PATTERN

Figure 3: Idling Patterns for First-Order Sigma-Delta Modulator (Integrator Output)

Figure 4: Idling Patterns for Second-Order Sigma-Delta Modulator (Integrator Output)

### HIGHER ORDER LOOP CONSIDERATIONS

In order to achieve wide dynamic range,  $\Sigma$ - $\Delta$  modulator loops greater than second-order are necessary, but present real design challenges. First of all, the simple linear models previously discussed are no longer fully accurate. Loops of order greater than two are generally not guaranteed to be stable under all input conditions. The instability arises because the comparator is a nonlinear element whose effective "gain" varies inversely with the input level. This mechanism for instability causes the following behavior: if the loop is operating normally, and a large signal is applied to the input that overloads the loop, the average gain of the comparator is reduced. The reduction in comparator gain in the linear model causes loop instability. This causes instability even when the signal that caused it is removed.

In actual practice, such a circuit would normally oscillate on power-up due to initial conditions caused by turn-on transients. The <u>AD1879</u> dual audio ADC released in 1994 by Analog Devices used a 5<sup>th</sup> order loop. Extensive nonlinear stabilization techniques were required in this and similar higher-order loop designs (References 1-5).

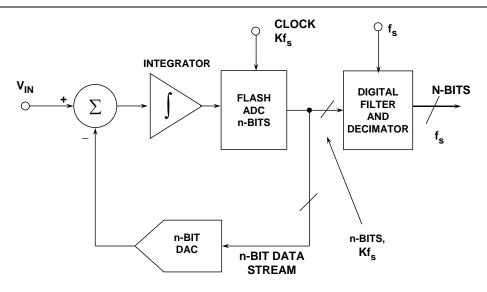

#### MULTI-BIT SIGMA-DELTA CONVERTERS

So far we have considered only  $\Sigma$ - $\Delta$  converters which contain a single-bit ADC (comparator) and a single-bit DAC (switch). The block diagram of Figure 5 shows a multi-bit  $\Sigma$ - $\Delta$  ADC which uses an n-bit flash ADC and an n-bit DAC. Obviously, this architecture will give a higher dynamic range for a given oversampling ratio and order of loop filter. Stabilization is easier, since second-order loops can generally be used. Idling patterns tend to be more random thereby minimizing tonal effects.

## MT-023

Figure 5: Multi-Bit Sigma-Delta ADC

The real disadvantage of this technique is that the linearity depends on the DAC linearity, and thin film laser trimming is required to approach 16-bit performance levels. This makes the multi-bit architecture extremely impractical to implement on mixed-signal ICs using traditional binary DAC techniques.

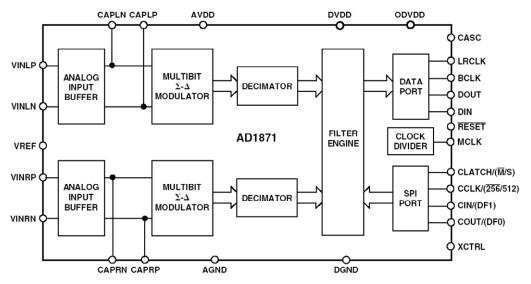

However, fully decoded thermometer DACs (see <u>Tutorial MT-014</u>) coupled with proprietary data scrambling techniques as used in a number of Analog Devices' audio ADCs and DACs, including the 24-bit stereo <u>AD1871</u> (see References 6 and 7) can achieve high SNR and low distortion using the multi-bit architecture. The multi-bit data scrambling technique both minimizes idle tones and ensures better differential linearity. A simplified block diagram of the AD1871 ADC is shown in Figure 6.

Figure 6: <u>AD1871</u> 24-Bit 96-kSPS Stereo Audio Multi-Bit Sigma-Delta ADC

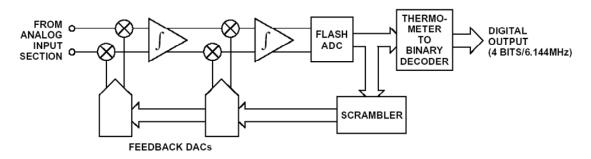

The AD1871's analog  $\Sigma$ - $\Delta$  modulator section comprises a second order multi-bit implementation using Analog Device's proprietary technology for best performance. As shown in Figure 7, the two analog integrator blocks are followed by a flash ADC section that generates the multi-bit samples.

The output of the flash ADC, which is thermometer encoded, is decoded to binary for output to the filter sections and is scrambled for feedback to the two integrator stages. The modulator is optimized for operation at a sampling rate of 6.144 MHz (which is  $128 \times f_s$  at 48-kHz sampling and  $64 \times f_s$  at 96-kHz sampling). The A-weighted dynamic range of the AD1871 is typically 105 dB.

Figure 7: Details of the AD1871 Second-Order Modulator and Data Scrambler

## DIGITAL FILTER IMPLICATIONS ON MULTIPLEXED APPLICATIONS

The digital filter is an integral part of all  $\Sigma$ - $\Delta$  ADCs—there is no way to remove it. The settling time of this filter affects certain applications especially when using  $\Sigma$ - $\Delta$  ADCs in multiplexed applications. The output of a multiplexer can present a step function input to an ADC if there are different input voltages on adjacent channels. In fact, the multiplexer output can represent a fullscale step voltage to the  $\Sigma$ - $\Delta$  ADC when channels are switched. Adequate filter settling time must be allowed, therefore, in such applications. This does not mean that  $\Sigma$ - $\Delta$  ADCs shouldn't be used in multiplexed applications, just that the settling time of the digital filter must be considered. Some newer  $\Sigma$ - $\Delta$  ADCs such are actually optimized for use in multiplexed applications.

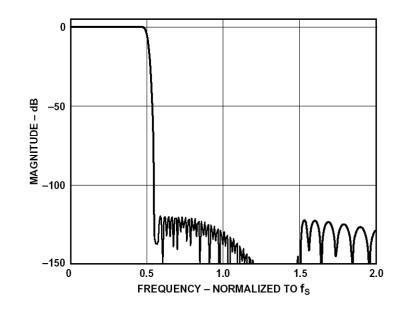

For example, the group delay through the AD1871 digital filter is 910  $\mu$ s (sampling at 48 kSPS) and 460  $\mu$ s (sampling at 96 kSPS)—this represents the time it takes for a step function input to propagate through one-half the number of taps in the digital filter. The total settling time is therefore approximately twice the group delay time. The input oversampling frequency is 6.144 MSPS for both conditions. The frequency response of the digital filter in the AD1871 ADC is shown in Figure 8. This filter uses a finite impulse response (FIR) design, and therefore has linear phase over the audio passband. Duplicating this performance using an analog filter would require considerable design effort as well as rather costly components.

In other applications, such as low frequency, high resolution 24-bit measurement  $\Sigma$ - $\Delta$  ADCs (such as the AD77xx-series), other types of digital filters may be used. For instance, the SINC<sup>3</sup> response is popular because it has zeros at multiples of the throughput rate. A 10-Hz throughput rate produces zeros at 50 Hz and 60 Hz which aids in ac power line rejection.

Regardless of the type of digital filter,  $\Sigma$ - $\Delta$  ADCs require that sufficient settling time is allowed after the application of a step function input.

## MULTISTAGE NOISE SHAPING (MASH) SIGMA-DELTA CONVERTERS

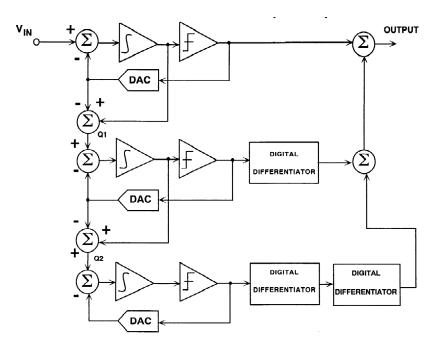

As has been discussed, nonlinear stabilization techniques can be difficult for 3<sup>rd</sup> order loops or higher. In many cases, the multi-bit architecture is preferable. An alternative approach to either of these, called multistage noise shaping (MASH), utilizes cascaded stable first-order loops (see References 8 and 9). Figure 9 shows a block diagram of a three-stage MASH ADC. The output of the first integrator is subtracted from the first DAC output to yield the first stage quantization noise, Q1. Q1 is then quantized by the second stage. The output of the second integrator is subtracted from the second stage quantization noise which is in turn quantized by the third stage.

The output of the first stage is summed with a single digital differentiation of the second stage output and a double differentiation of the third stage output to yield the final output. The result is that the quantization noise Q1 is suppressed by the second stage, and the quantization noise Q2 is suppressed by the third stage yielding the same suppression as a third-order loop. Since this result is obtained using three first-order loops, stable operation is assured.

Figure 9: Multi-Stage Noise Shaping Sigma-Delta ADC (MASH)

## HIGH RESOLUTION MEASUREMENT SIGMA-DELTA ADCS

While older integrating architectures such as dual-slope are still used in digital voltmeters, CMOS  $\Sigma$ - $\Delta$  ADCs are the dominant converter for today's industrial measurement applications. These converters offer excellent 50-Hz/60-Hz power line common-mode rejection and resolutions up to 24 bits with various digital features, such as on-chip calibration. Many have programmable gain amplifiers (PGAs) which allow the direct digitization of small signals from bridge and thermocouple transducers without the need for additional external signal conditioning circuits.

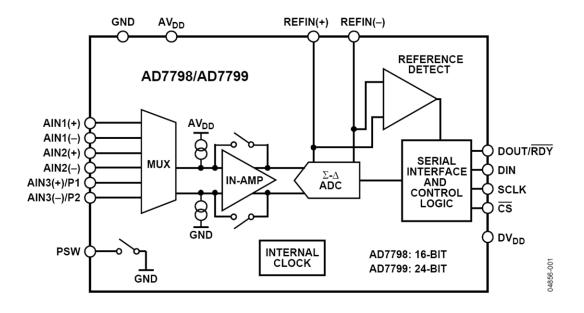

In order to better understand the capability of  $\Sigma$ - $\Delta$  measurement ADCs and the power of the technique, a modern example, the 24-bit <u>AD7799</u>, will be examined in detail. The AD7799 is a member of the AD77xx family and is shown in Figure 10. This ADC was specifically designed to interface directly to low-level sensor outputs such as bridges in weigh scale applications. The device accepts low-level signals directly from a bridge and outputs a serial digital word. There are three multiplexed and buffered differential inputs which drive an internal instrumentation amplifier. The in-amp can be programmed for eight different gains: 1, 2, 4, 8, 16, 32, 64, and 128.

# MT-023

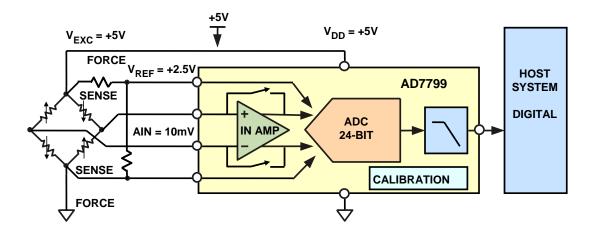

Figure 10: <u>AD7799</u> Sigma-Delta Single-Supply Bridge ADC

Figure 11 shows a direct connection between a bridge-based load cell and a high resolution  $\Sigma$ - $\Delta$  ADC, the AD7799. The fullscale bridge output of 10 mV is digitized to approximately 16 noise-free bits by the ADC at a throughput rate of 4.17 Hz. Ratiometric operation eliminates the need for a precision voltage reference. The AD7799 can be operated at throughput rates from 4.17 Hz to 500 Hz. The part operates with a power supply from 2.7 V to 5.25 V and consumes 380  $\mu$ A typical.

Figure 11: Load Cell Conditioning Using a High Resolution Sigma-Delta ADC

# MT-023

### **BANDPASS SIGMA-DELTA CONVERTERS**

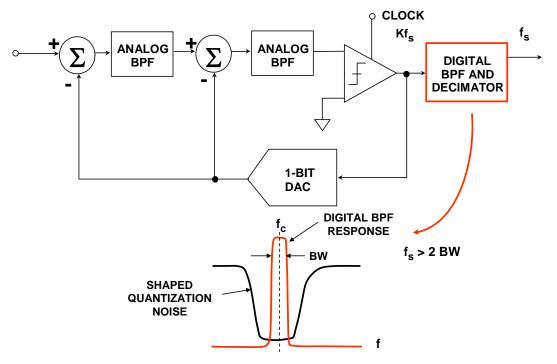

The  $\Sigma$ - $\Delta$  ADCs that we have described so far contain integrators, which are low pass filters, whose passband extends from dc. Thus, their quantization noise is pushed up in frequency. At present, most commercially available  $\Sigma$ - $\Delta$  ADCs are of this type (although some which are intended for use in audio or telecommunications applications contain bandpass rather than lowpass digital filters to eliminate any system dc offsets). But there is no particular reason why the filters of the  $\Sigma$ - $\Delta$  modulator should be LPFs, except that traditionally ADCs have been thought of as being baseband devices, and that integrators are somewhat easier to construct than bandpass filters. If we replace the integrators in a  $\Sigma$ - $\Delta$  ADC with bandpass filters (BPFs) as shown in Figure 12, the quantization noise is moved up and down in frequency to leave a virtually noise-free region in the pass-band (see References 10, 11, and 12). If the digital filter is then programmed to have its pass-band in this region, we have a  $\Sigma$ - $\Delta$  ADC with a bandpass, rather than a lowpass characteristic. Such devices would appear to be useful in direct IF-to-digital conversion, digital radios, ultrasound, and other undersampling applications. However, the modulator and the digital BPF must be designed for the specific set of frequencies required by the system application, thereby somewhat limiting the flexibility of this approach.

Figure 12: Replacing Integrators with Resonators Gives a Bandpass Sigma-Delta ADC

In an undersampling application of a bandpass  $\Sigma$ - $\Delta$  ADC, the minimum sampling frequency must be at least twice the signal bandwidth, BW. The signal is centered around a carrier frequency, f<sub>c</sub>. A typical digital radio application using a 455-kHz center frequency and a signal bandwidth of 10 kHz is described in Reference 11. An oversampling frequency Kf<sub>s</sub> = 2 MSPS and an output rate f<sub>s</sub> = 20 kSPS yielded a dynamic range of 70 dB within the signal bandwidth. An early example of a bandpass  $\Sigma$ - $\Delta$  ADC is the <u>AD9870</u> IF Digitizing Subsystem having a nominal oversampling frequency of 18 MSPS, a center frequency of 2.25 MHz, and a bandwidth of 10 kHz to 150 kHz (see details in Reference 12).

The <u>AD9874</u> and <u>AD9864</u> are general purpose IF subsystems that digitize low level 10-300 MHz IF signals with bandwidths up to 270 kHz (see details in Reference 13). The signal chain contains a low noise amplifier, mixer, bandpass  $\Sigma$ - $\Delta$  ADC and a decimation filter with programmable decimation factor. An AGC circuit provides 12 dB of continuous gain adjustment.

#### SUMMARY

Sigma-delta ADCs and DACs have proliferated into many modern applications including measurement, voiceband, audio, etc. The technique takes full advantage of low cost CMOS processes and therefore makes integration with highly digital functions such as DSPs practical. Modern techniques such as the multi-bit data scrambled architecture minimize problems with idle tones which plagued early  $\Sigma$ - $\Delta$  products. Resolutions up to 24-bits are currently available, and the requirements on analog antialiasing/anti-imaging filters are greatly relaxed due to oversampling. The internal digital filter in audio  $\Sigma$ - $\Delta$  ADCs can be designed for linear phase, which is a major requirement in those applications. For high resolution  $\Sigma$ - $\Delta$  ADCs designed for measurement applications, the digital filter is generally designed so that zeros occur at the mains frequencies of 50 Hz and 60 Hz.

Many  $\Sigma$ - $\Delta$  converters offer a high level of user programmability with respect to output data rate, digital filter characteristics, and self-calibration modes. Multi-channel  $\Sigma$ - $\Delta$  ADCs are now available for data acquisition systems, and most users are well-educated with respect to the settling time requirements of the internal digital filter in these applications.

#### REFERENCES

- 1. W.L. Lee and C.G. Sodini, "A Topology for Higher-Order Interpolative Coders," *ISCAS PROC*. 1987.

- P.F. Ferguson, Jr., A. Ganesan and R. W. Adams, "One-Bit Higher Order Sigma-Delta A/D Converters," *ISCAS PROC*. 1990, Vol. 2, pp. 890-893.

- 3. Wai Laing Lee, A Novel Higher Order Interpolative Modulator Topology for High Resolution Oversampling A/D Converters, MIT Masters Thesis, June 1987.

- 4. R. W. Adams, "Design and Implementation of an Audio 18-Bit Analog-to-Digital Converter Using Oversampling Techniques," *J. Audio Engineering Society*, Vol. 34, March 1986, pp. 153-166.

- 5. P. Ferguson, Jr., A. Ganesan, R. Adams, et. al., "An 18-Bit 20-kHz Dual Sigma-Delta A/D Converter," *ISSCC Digest of Technical Papers*, February 1991.

- 6. Robert Adams, Khiem Nguyen, and Karl Sweetland, "A 113 dB SNR Oversampling DAC with Segmented Noise-Shaped Scrambling," *ISSCC Digest of Technical Papers*, vol. 41, 1998, pp. 62, 63, 413. (describes a segmented audio DAC with data scrambling).

- 7. Robert W. Adams and Tom W. Kwan, "Data-directed Scrambler for Multi-bit Noise-shaping D/A Converters," U.S. Patent 5,404,142, filed August 5, 1993, issued April 4, 1995. (describes a segmented audio DAC with data scrambling).

- 8. Y. Matsuya, et. al., "A 16-Bit Oversampling A/D Conversion Technology Using Triple-Integration Noise Shaping," *IEEE Journal of Solid-State Circuits*, Vol. SC-22, No. 6, December 1987, pp. 921-929.

- 9. Y. Matsuya, et. al., "A 17-Bit Oversampling D/A Conversion Technology Using Multistage Noise Shaping," *IEEE Journal of Solid-State Circuits*, Vol. 24, No. 4, August 1989, pp. 969-975.

- 10. Paul H. Gailus, William J. Turney, and Francis R. Yester, Jr., "Method and Arrangement for a Sigma Delta Converter for Bandpass Signals," U.S. Patent 4,857,928, filed January 28, 1988, issued August 15, 1989.

- 11. S.A. Jantzi, M. Snelgrove, and P.F. Ferguson Jr., "A 4<sup>th</sup>-Order Bandpass Sigma-Delta Modulator," *IEEE Journal of Solid State Circuits*, Vol. 38, No. 3, March 1993, pp. 282-291.

- 12. Paul Hendriks, Richard Schreier, Joe DiPilato, "<u>High Performance Narrowband Receiver Design Simplified by</u> <u>IF Digitizing Subsystem in LQFP</u>," *Analog Dialogue*, Vol. 35-3, June-July 2001. Available at http://www.analog.com (describes an IF subsystem with a bandpass sigma-delta ADC having a nominal oversampling frequency of 18MSPS, a center frequency of 2.25MHz, and a bandwidth of 10kHz - 150kHz).

- Richard Schreier, J. Lloyd, L. Singer, D. Paterson, M. Timko, M. Hensley, G. Patterson, K Behel, and J. Zhou, "A 10-300 MHz IF-Digitizing IC with 90-105 dB Dynamic Range and 15-333 kHz Bandwidth, *IEEE Journal of Solid State Circuits*, Vol. 37, No. 12, December 2002, pp. 1636-1644.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.