Another feature of the AD7882 is a power-down mode which reduces power dissipation from its normal operating value of 200 mW to 0.5 mW.

clock may be used.

The AD7882 operates from  $\pm 5$  V supplies. Analog input ranges can be unipolar, 0 to 2.5 V or bipolar,  $\pm 2.5$  V. The analog input bandwidth is 200 kHz.

In addition to traditional dc accuracy specifications such as linearity, the AD7882 is also fully specified for dynamic performance parameters including harmonic distortion and signal-to-noise ratio (SNR).

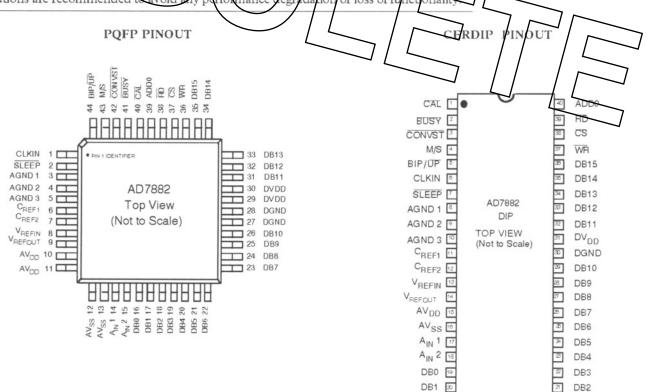

The AD7882 is fabricated in Analog Devices' Linear Compatible CMOS (LC<sup>2</sup>MOS), an advanced, mixed technology process that combines precision bipolar circuits with low-power high-speed CMOS logic. The part is available in a 44-pin plastic quad flat pack (PQFP) and 40-pin cerdip.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

- Self-calibration Achieves High Accuracy A Self-calibrating algorithm minimizes linearity, offset and gain errors. The calibration procedure can also include external offset and gain errors.

- 3. Dynamic Specifications for DSP users. In addition to traditional dc specifications, the AD7882 is specified for ac parameters including signal-to-noise ratio and harmonic distortion. These parameters along with important timing parameters are tested on every device.

- Fast, Versatile Microprocessor Interface. Fast bus access times and standard control signals make the AD7882 easy to interface to microprocessors.

- Low Power. Low power monolithic solution allows ease of application. The AD7882 also has a power down facility

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703 Prelim.F 3/95

Z

# $\label{eq:AD7882} \textbf{AD7882} - \textbf{SPECIFICATIONS}_{(AV_{DD} = 5V \pm 5\%, DV_{DD} = 5V \pm 5\%, AV_{SS} = -5V \pm 5\%, V_{REFIN} = 2.5V, \\ \textbf{AGND} = DGND = 0V, \ \textbf{f}_{CLKIN} = 10 \ \textbf{MHz}, \ \textbf{f}_{SAMPLE} = 300 \ \textbf{kHz}. \ \textbf{All specifications T}_{MIN} \ \textbf{to T}_{MAX} \ \textbf{unless otherwise noted.}$

|                                                           |                              | T <sub>MAX</sub> unless      | otherwise noted.) |                                                                                                     |

|-----------------------------------------------------------|------------------------------|------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|

| Parameter                                                 | A, S<br>Version <sup>1</sup> | B, T<br>Version <sup>1</sup> | Units             | Test Conditions/Comments                                                                            |

|                                                           | version                      | version                      | Cints             | Test Conditions/Comments                                                                            |

| DYNAMIC PERFORMANCE <sup>2</sup>                          | 00                           | 0.0                          | ID min            | A = 10  bHz Turical SNP = 0.2 dP                                                                    |

| Signal to(Noise+Distortion Ratio)                         | 90                           | 90                           | dB min<br>dB min  | $A_{IN} = 10 \text{ kHz}$ , Typical SNR = 92 dB<br>$A_{IN} = 100 \text{ kHz}$ , Typical SNR = 87 dB |

| TUD                                                       | 85                           | 85                           |                   |                                                                                                     |

| THD                                                       | -95                          | -95                          | dB max            | $A_{IN} = 10 \text{ kHz}$ , Typical THD = -100 dB                                                   |

|                                                           | -88                          | -88                          | dB max            | $A_{IN} = 100 \text{ kHz}$ , Typical THD = -90 dB                                                   |

| Peak Harmonic or Spurious Noise                           |                              | -98                          | dB max            | $A_{IN} = 10 \text{ kHz}$ , Typical Peak Har. = -100 dH                                             |

| Luci D'acci                                               | -90                          | -90                          | dB max            | $A_{IN} = 100 \text{ kHz}$ , Typical Peak Har. = -92 dH                                             |

| Intermodulation Distortion<br>2 <sup>ND</sup> Order Terms | 0.0                          | 0.0                          | 1D                | f = 00 bHz $f = 100$ bHz                                                                            |

| 3 <sup>RD</sup> Order Terms                               | -88                          | -88                          | dB max            | $f_A = 98 \text{ kHz}, f_B = 100 \text{ kHz}$                                                       |

|                                                           | -88                          | -88                          | dB max            |                                                                                                     |

| Throughput Time                                           | 3.3                          | 3.3                          | µs max            |                                                                                                     |

| Aperture delay                                            | 10                           | 10                           | ns typ            |                                                                                                     |

| Aperturs Jitter                                           | 20                           | 20                           | ps typ            |                                                                                                     |

| Noise                                                     | 70                           | 70                           | μV rms typ        |                                                                                                     |

| DC ACCURACY2                                              |                              |                              |                   |                                                                                                     |

| Resolution /                                              | 16                           | 16                           | Bits              |                                                                                                     |

| Minimum Resolution for which                              | $\bigcirc$                   | $\frown$                     |                   |                                                                                                     |

| No Missing Codes Guaranteed                               | 16                           | 16                           | Bits              |                                                                                                     |

| Integral Nonlinearity                                     | ±1/2                         | ± 1/2                        | LSE typ           |                                                                                                     |

| Integral Nonlinearity                                     | $\sum 1$                     | ± 1.0                        | LSB max           | $\sim$                                                                                              |

| Differential Nonlinearity                                 | ±0.9                         | ±0.5                         | LSB max           |                                                                                                     |

| Unipolar Offset Error                                     | +2                           | ±2                           | LSB max           |                                                                                                     |

| Unipolar Gain Error                                       | ±2                           | ±2                           | ISBmax            |                                                                                                     |

| Bipolar Zero Error                                        | ±2                           | 12                           | LSB max           |                                                                                                     |

| Bipolar Positive Gain Error                               | ±2                           | ±2                           | LSBmax            |                                                                                                     |

| Bipolar Negative Gain Error                               | ±2                           | ±2                           | LSB max           |                                                                                                     |

| POWER SUPPLY REJECTION                                    |                              |                              |                   |                                                                                                     |

|                                                           | 0.4                          | 0.4                          | dD ture           |                                                                                                     |

| AV <sub>DD</sub> only                                     | 84                           | 84                           | dB typ            |                                                                                                     |

| AV <sub>SS</sub> only                                     | 84                           | 84                           | dB typ            |                                                                                                     |

| ANALOG I/P                                                |                              |                              |                   | 1                                                                                                   |

| Input current                                             | ±1                           | ±1                           | μA max            | Input Range = $0 - 2.5$ V or $\pm 2.5$ V                                                            |

| Input capacitance <sup>3</sup>                            | 20                           | 20                           | pF max            |                                                                                                     |

| REFERENCE OUTPUT                                          |                              |                              |                   |                                                                                                     |

| V <sub>REFOUT</sub> @ 25°C                                | 2.5                          | 2.5                          | Volts nominal     | ±1%                                                                                                 |

| V <sub>REFOUT</sub> Tempco                                | 20                           | 20                           | ppm/°C typ        |                                                                                                     |

| REFERENCE INPUT                                           |                              |                              | PP                |                                                                                                     |

|                                                           | 0.5                          | 2.5                          | Vales             | +00/                                                                                                |

| V <sub>REFIN</sub> Range                                  | 2.5                          | 2.5                          | Volts             | ±2%                                                                                                 |

| V <sub>REFIN</sub> Current                                | ±1                           | ±1                           | µA max            |                                                                                                     |

| LOGIC INPUTS                                              |                              |                              |                   |                                                                                                     |

| Input High Voltage, V <sub>INH</sub>                      | 2.4                          | 2.4                          | Volts min         |                                                                                                     |

| Input Low Voltage, V <sub>INL</sub>                       | 0.8                          | 0.8                          | Volts max         |                                                                                                     |

| Input Current                                             | ±10                          | ±10                          | µA max            |                                                                                                     |

| Input Capacitance <sup>3</sup>                            | 10                           | 10                           | pF max            |                                                                                                     |

| SLEEP INPUT                                               |                              |                              | -                 |                                                                                                     |

| Input High Voltage, V <sub>INH</sub>                      | V <sub>DD</sub> - 0.2        | V <sub>DD</sub> - 0.2        | Volts min         |                                                                                                     |

| Input Low Voltage, V <sub>INL</sub>                       | 0.2                          | 0.2                          | Volts max         |                                                                                                     |

| CLKIN INPUT                                               | 0.2                          | 0.2                          | vons max          |                                                                                                     |

| Negative Trigger Level                                    | -2                           | -2                           | Volts min         | This is the trigger level for choosing                                                              |

|                                                           |                              |                              |                   | internal clock operation of the device                                                              |

NOTES

<sup>1</sup> Temperature Ranges are as Follows: A, B Version -40°C to 85°C S, T Version -55°C to 125°C

<sup>2</sup> Specifications Apply After Calibration.

<sup>3</sup> Sample Tested at 25°C to Ensure Compliance.

Specifications Subject to Change Without Notice.

3

**Preliminary Technical Data**

# AD7882

# $\label{eq:AD7882} \textbf{AD7882} - \textbf{SPECIFICATIONS}_{\text{AGND}} \stackrel{(\text{AV}_{\text{DD}} = 5\text{ V} \pm 5\ \%, \ \text{DV}_{\text{DD}} = 5\text{ V} \pm 5\ \%, \ \text{AV}_{\text{SS}} = -5\text{ V} \pm 5\ \%, \ \text{V}_{\text{REFIN}} = 2.5\text{ V}, \\ \text{AGND} = \text{DGND} = 0\text{ V}, \ f_{\text{CLKIN}} = 10\ \text{MHz}, \ f_{\text{SAMPLE}} = 300\ \text{kHz}. \ \text{All specifications } T_{\text{MIN}} \ \text{to}$ T<sub>MAX</sub> unless otherwise noted.)

4

| Parameter                                                | A, S<br>Version <sup>1</sup> | B, T<br>Version <sup>1</sup> | Units            | Test Conditions/Comments                                                                                                       |

|----------------------------------------------------------|------------------------------|------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS                                            |                              |                              |                  |                                                                                                                                |

| Output High Voltage, V <sub>OH</sub>                     | 2.4                          | 2.4                          | Volts min        | $I_{SOURCE} = 200 \ \mu A$                                                                                                     |

| Output Low Voltage, V <sub>OL</sub><br>DB15 - DB0        | 0.4                          | 0.4                          | Volts max        | $I_{SINK} = 1.6 \text{ mA}$                                                                                                    |

| Tri-State Leakage Current                                | ±10                          | ±10                          | μA max           |                                                                                                                                |

| Tri -State Output Capacitance <sup>3</sup>               | 20                           | 20                           | pF max           |                                                                                                                                |

| POWER REQUIREMENTS                                       |                              |                              |                  |                                                                                                                                |

| DV <sub>DD</sub>                                         | +5                           | +5                           | Volts            | ±5 %                                                                                                                           |

| AVDD                                                     | +5                           | +5                           | Volts            | ±5 %                                                                                                                           |

| AV <sub>ss</sub><br>Normal Mode                          | -5                           | -5                           | Volts            | ±5 %                                                                                                                           |

|                                                          | 1                            | 1                            | mA max           |                                                                                                                                |

|                                                          | 29                           | 29                           | mA max           |                                                                                                                                |

| Alss<br>Power dissipation                                | 27                           | 27<br>300                    | mA max<br>mW max | Typically 200 mW. CLKIN Not Runni                                                                                              |

| Sleep Mode<br>DI <sub>DD</sub>                           |                              | 40                           | µA max           |                                                                                                                                |

| AI <sub>DD</sub><br>AIss                                 | 40                           | 50<br>40                     | µA max<br>µA max |                                                                                                                                |

| Power dissipation                                        |                              |                              | mW max           | Typically 500 W Input Logic Levels of<br>0.2V and V <sub>DD</sub> - 0.2V. CLKIN not runn<br>Typically 1.5mW with CLKIN running |

|                                                          |                              |                              |                  |                                                                                                                                |

| NOTES                                                    |                              |                              |                  |                                                                                                                                |

| NOTES<br><sup>1</sup> Temperature Ranges are as Follows: |                              |                              |                  |                                                                                                                                |

| A, B Version -40°C to 85°C                               |                              |                              |                  |                                                                                                                                |

<sup>2</sup> Specifications Apply After Calibration.

<sup>3</sup> Sample Tested at 25°C to Ensure Compliance. Specifications Subject to Change Without Notice.

|                                          | Limit @ 25°C                   | $Limit @ T_{min}, T_{max} \\$     | Limit @ T <sub>min</sub> , T <sub>max</sub> |                  |                                                |

|------------------------------------------|--------------------------------|-----------------------------------|---------------------------------------------|------------------|------------------------------------------------|

| Parameter                                | (All Versions)                 | (A,B Versions)                    | (S,T Versions)                              | Units            | Conditions/Comments                            |

| t <sub>1</sub>                           | 10                             | 15                                | 20                                          | ns min           | ADD0 to WR Setup Time                          |

| t <sub>2</sub>                           | 5                              | 5                                 | 10                                          | ns min           | ADD0 to WR Hold Time                           |

| t <sub>3</sub>                           | 10                             | 15                                | 20                                          | ns min           | CS to WR Setup Time                            |

| t <sub>4</sub>                           | 5                              | 5                                 | 10                                          | ns min           | CS to WR Hold Time                             |

| t <sub>5</sub>                           | 30                             | 40                                | 50                                          | ns min           | WR Pulse Width                                 |

| t <sub>6</sub>                           | 30                             | 40                                | 50                                          | ns min           | Data Setup Time                                |

| t <sub>7</sub>                           | 5                              | 5                                 | 10                                          | ns min           | Data Hold Time                                 |

| <b>L</b> CONVERT                         | 30T <sub>CLKIN</sub>           | 30T <sub>CLKIN</sub>              | 30T <sub>CLKIN</sub>                        |                  | Conversion Time: Synchronous Operation         |

|                                          | 3.0                            | 3.0                               | 3.0                                         | µs max           | Conversion Time: Internal Clock Operation      |

| t <sub>SAMPLE</sub>                      | 33T <sub>CLKIN</sub>           | 33T <sub>CLKIN</sub>              | 33T <sub>CLKIN</sub>                        |                  | Time Between Samples: Synchronous Operation    |

|                                          | 3.3                            | 3.3                               | 3.3                                         | µs max           | Time Between Samples: Internal Clock Operation |

| 18                                       | 30                             | 40                                | 50                                          | ns min           | CONVST Pulse Width                             |

| t <sub>9</sub>                           | 20                             | 30                                | 40                                          | ns max           | CONVST High to BUSY Low Delay                  |

| t <sub>10</sub>                          | 0/( )                          | 0                                 | 0                                           | ns min           | CS to RD Setup Time                            |

| t <sub>11</sub>                          | $q \sim 1$                     | $0 \longrightarrow 10$            | 0                                           | ns min           | CS to RD Hold Time                             |

| tre /                                    | $A^0 \longrightarrow \langle $ | 50                                | 60                                          | ns min           | RD Pulse Width                                 |

| t13                                      | 40                             | 50                                |                                             | ns max           | RD Low to Data Valid Delay (Data Access Time)  |

| t <sub>14</sub>                          |                                | $[$ <sup>He</sup> $\setminus ) /$ | $\begin{pmatrix} 10 \end{pmatrix}$          | ns min           | Data Hold Time After RD (Bus Relinquish Time)  |

|                                          | 75                             |                                   | 75                                          | ns max           |                                                |

| t <sub>15</sub>                          | 10                             |                                   | 20                                          | ns min           | ADD0 to RD Setup Time                          |

| t <sub>16</sub>                          | 5                              | 5                                 |                                             | ns min           | ADD0 to RD Hold Time                           |

| t <sub>17</sub>                          | 40                             | 40                                | 50                                          | ns min           | New Data Valid before Rising Eage of BUSY      |

| t <sub>18</sub>                          | 20                             | 30                                | 40                                          | ns max           | CLKIN Felling Edge to BUSY Low Delay           |

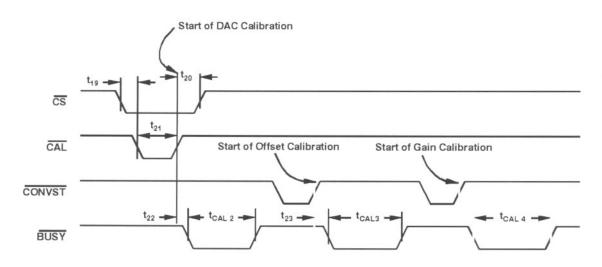

| t <sub>19</sub>                          | 10<br>0                        | 20<br>0                           | 30<br>0                                     | ns min           | CS to CAL Setup Time                           |

| t <sub>20</sub>                          | 30                             | 40                                | 50                                          | ns min           | CAL Pulse Width                                |

| t <sub>21</sub>                          | 20                             | 30                                |                                             | ns min<br>ns max | CAL High to BUSY Low Delay                     |

| t <sub>22</sub>                          | 20                             | 30                                | 40                                          | ns max           | CONVST High to BUSY Low Delay: System          |

| t <sub>23</sub>                          | 20                             | 50                                | 10                                          | no max           | CAL Mode                                       |

| terr                                     | 9276744 T <sub>CLKIN</sub>     |                                   |                                             |                  | Device Calibration Time: Device CAL Mode       |

| t <sub>CAL 1</sub>                       | 6359324 T <sub>CLKIN</sub>     |                                   |                                             |                  | DAC Calibration Time: System CAL Mode          |

| t <sub>CAL 2</sub>                       | 1475104 T <sub>CLKIN</sub>     |                                   |                                             |                  | Offset Calibration Time: System CAL Mode       |

| t <sub>CAL 3</sub><br>t <sub>CAL 4</sub> | 1442324 T <sub>CLKIN</sub>     |                                   |                                             |                  | Gain Calibration Time: System CAL Mode         |

| "CAL 4                                   |                                |                                   |                                             |                  | Sam Sanoration Third. System Star Mode         |

### NOTES

<sup>1</sup>All input signals are specified with tr= tf= 5ns (10% to 90% of 5V) and timed from a voltage level of 1.6V.

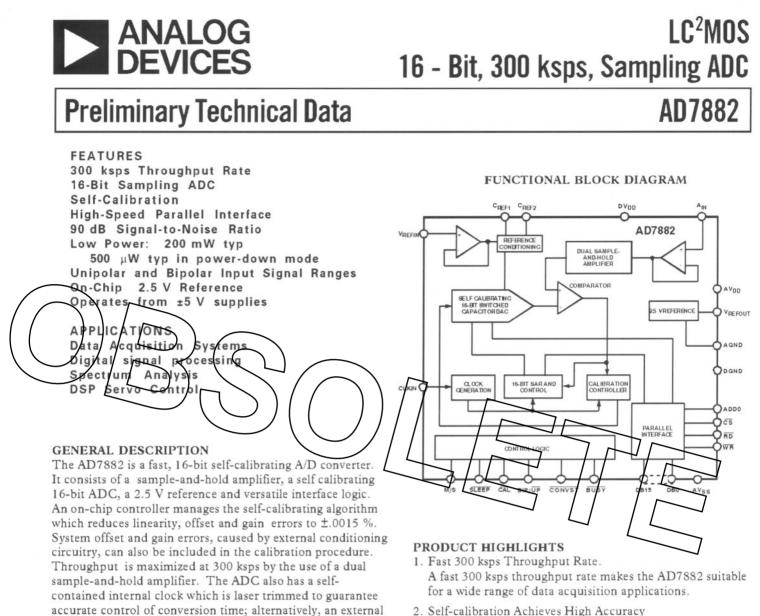

All input signals are specified with the load circuit of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V.  $t_{13}$  is derived from the measured time taken by the data outputs to change 0.5V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 100pF capacitor. This means that the time,  $t_{14}$ , quoted in the Timing Specifications is the true bus relinquish time of the part and as such is independent of external bus loading capacitances.

Specifications subject to change without notice

### **AD7882 ORDERING GUIDE**

| Model    | Temperature<br>Range | Integral Nonlinearity<br>(LSB's) | Package<br>Option <sup>1</sup> |  |

|----------|----------------------|----------------------------------|--------------------------------|--|

| AD7882SQ | -55°C to +125°C      | ±0.5 typ                         | Q-40                           |  |

| AD7882TQ | -55°C to +125°C      | ±1 max                           | Q-40                           |  |

| AD7882AS | -40°C to +85°C       | ±0.5 typ                         | S-44                           |  |

| AD7882BS | -40°C to +85°C       | ±1 max                           | S-44                           |  |

$^{1}$  Q = CERDIP S = PQFP

### ANALOG DEVICES FAX-ON-DEMAND HOTLINE

6

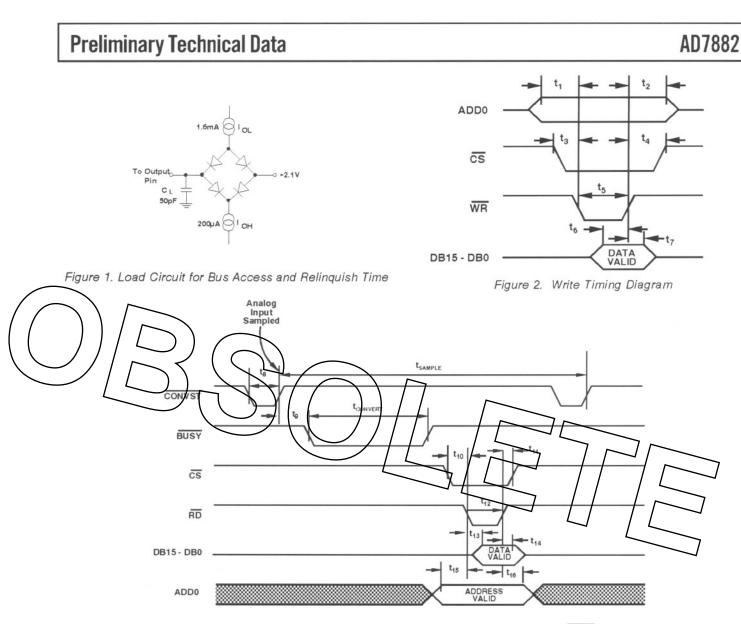

Figure 3. Read Timing Diagram, Asynchronous Operation (M/S = Low; CAL = High)

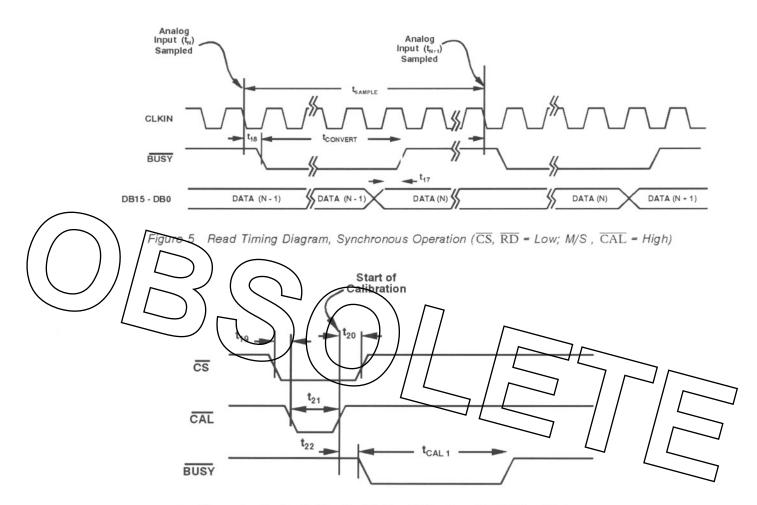

Figure 6. Device Calibration Timing (M/S = Low; RD, WR = High)

Figure 7 System Calibration Timing (M/S = High; RD, WR = High)

- 6 -

# **Preliminary Technical Data**

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| AV <sub>DD</sub> to AGND                      | 0.3V to +7V                         |

|-----------------------------------------------|-------------------------------------|

| AV <sub>SS</sub> to AGND                      | +0.3V to -7V                        |

| AGND to DGND                                  | 0.3V to 0.3V                        |

| AV <sub>DD</sub> to DV <sub>DD</sub>          | 0.3V to + 0.3V                      |

| Analog Inputs to AGNDAV                       | ss- 0.3V to AV <sub>DD</sub> + 0.3V |

| Reference Inputs to AGNDAV                    | ss- 0.3V to AV <sub>DD</sub> + 0.3V |

| Digital Inputs to DGND                        | 0.3V to DV <sub>DD</sub> +0.3V      |

| Digital Outputs to DGND                       | 0.3V to DV <sub>DD</sub> +0.3V      |

| Operating Temperature Range                   |                                     |

| Commercial Plastic (A, B Versions)            | 40°C to +85°C                       |

| Extended Hermetic (S,T Versions)              |                                     |

| Storage Temperature Range                     |                                     |

| Junction Temperature                          | 150°C                               |

| Lead Temperature (Soldering, 10 secs)         | +300°C                              |

| Cerdip Package Power Dissipation              | 1000mW                              |

| θ <sub>JA</sub> Thermal Impedance             |                                     |

|                                               |                                     |

| CAUTION                                       |                                     |

| ESD (Electro-Static Discharge) sensitiv       | e device. Electrostatic ch          |

| readily accumulate on the human body a        | and on test equipment, ca           |

| Although devices feature proprietary ES       |                                     |

| cur on these devices if they are subjected to |                                     |

| precautions are recommended to avoid a        | any performance degrada             |

|                                               |                                     |

# AD7882

| LeadTemperature,Soldering         |        |

|-----------------------------------|--------|

| VaporPhase(60 secs)               | +215°C |

| Infrared(15 secs)                 | +220°C |

| PQFP Package, Power Dissipation   | 875mW  |

| θ <sub>IA</sub> Thermal Impedance | 75°C/W |

| Lead Temperature, Soldering       |        |

| Vapor Phase (60 secs)             | +215°C |

| Infrare(15 secs)                  | +220°C |

#### NOTES

8

1. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. 2. Transient currents of up to 100mA will not cause SCR latch-up.

harges as high as 4000V, which an discharge without detection. ermanent damage may still ocdischarges. Therefore, prop or loss of functionality ion

DB3

DB2

DB0 19

DB1 🗷

### TERMINOLOGY

### Integral Nonlinearity

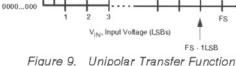

This is the maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are Zero-Scale (not to be confused with Bipolar Zero), a point 0.5 LSB below the first code transition (000.....000 to 000......001) and Full-Scale, a point 0.5 LSB above the last code transition (111....110 to 111......111). The error is expressed in LSB's.

### Differential Nonlinearity/No Missed Codes

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC. Differential Linearity Error is expressed in LSB's. A differential linearity error of  $\pm 0.9$  LSB or less guarantees no missed codes to the full resolution of the device. Thus, the AD7882 has no missed codes guaranteed to 16 bits.

### Unipolar Offset Error

When the device is operating in the 0 to +V<sub>REFIN</sub> range, the deviation of the first code transition from the ideal (+0.5 LSB) is the Unpolar Offset Error. It is expressed in LSB's.

### Unipolar Gain Error

This is the deviation of the last code transition (01.....110 to 01.....111) from the ideal (V<sub>REFIN</sub> 1.5 LSB) after Bipola Zero Error has been adjusted out.

### Bipolar Zero Error

This is the deviation of the mid-scale transition (all 0's to all 1's) from the ideal (AGND).

#### Positive Gain Error

This is the deviation of the last code transition (01....110 to 01....111) from the ideal  $(V_{\text{REFIN}} - 1.5 \text{ LSB})$  after Bipolar Zero Error has been adjusted out.

### Negative Gain Error

This is the deviation of the first code transition (10....000 to 10....001) from the ideal ( $-V_{REFIN} + 0.5 LSB$ ) after Bioplar Zero Error has been adjusted out.

### Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_s/$ 2), excluding dc. The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise +distortion) ratio for an ideal N-bit converter with a sine wave input is given by:

Signal to (Noise + Distortion) = (6.02N + 1.76) dB

Thus for a 16-bit converter, this is 98dB.

#### **Total Harmonic Distortion**

Total harmonic distortion (THD) is the ratio of the rms sum

THD(dB) = 20 log

$$\frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

of harmonics to the fundamental. For the AD7882, it is defined as :

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  and  $V_6$  are the rms amplitudes of the second through the sixth harmonics.

#### Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to  $f_2/2$  and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for parts where the harmonics are buried in the noise floor, it will be a noise peak.

# Intermodulation Distortion

With inputs consisting of sine waves e with nonlinearities and fb, any active devic rtion products at sum and difference frequencies of mfa ± nfb where = 0, 1, 2, 3,etc. Intermodulation terms are equal to those for which neither m or n are ze example, the second order terms and (fa nclude (fa fb), while the third order terms include (2 - fb), (fa + 2fb) and (fa - 2fb).

The AD7882 is tested using the CCIF standard where two input frequencies near the top end of the input bandwidth are used. In this case, the second and third order terms are of different significance. The second order terms are usually distanced in frequency from the original sine waves while the third order terms are usually at a frequency close to the input frequencies. As a result, the second and third order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification where it is the ratio of the rms sum of the individual distortion products to the rms amplitude of the fundamental expressed in dB's.

#### Power Supply Rejection Ratio

This is the ratio, in dB's, of the change in positive gain error to the change in  $AV_{DD}$ ,  $DV_{DD}$  or  $AV_{SS}$ . It is a dc measurement.

|        |              | $\sum (\alpha)$                                                                                                                                                                                                                      |  |  |  |  |  |  |

|--------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ANAL.  | DE DEVICES   | FAX-ON-DEMAND HOTLINE 10                                                                                                                                                                                                             |  |  |  |  |  |  |

| THE HE |              |                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|        |              |                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|        | CS           | Chip select, active low logic input. The device is selected when this input is active.                                                                                                                                               |  |  |  |  |  |  |

|        | ADD0         | Address Input. This control input determines whether the word placed on the output data bus during a read                                                                                                                            |  |  |  |  |  |  |

|        |              | operation is an ADC conversion result or the contents of the control register. A logic low accesses a conver                                                                                                                         |  |  |  |  |  |  |

|        |              | sion result while a logic high accesses the control register. When writing, if ADD0 is high, the control register                                                                                                                    |  |  |  |  |  |  |

|        | WTD          | is the destination. If ADD0 is low, the calibration data memory is the destination.                                                                                                                                                  |  |  |  |  |  |  |

|        | WR           | Write, active low logic input. This input is used in conjunction with CS and ADD0 to write data to the                                                                                                                               |  |  |  |  |  |  |

|        | DB15-DB0     | AD7882.                                                                                                                                                                                                                              |  |  |  |  |  |  |

|        | DBI3-DB0     | Three-state data outputs which are controlled by $\overline{\text{CS}}$ and $\overline{\text{RD}}$ . Data output coding is 2's complement binary.                                                                                    |  |  |  |  |  |  |

|        | Timing and ( | Control                                                                                                                                                                                                                              |  |  |  |  |  |  |

|        | CLKIN        | Clock input, an external TTL-compatible clock may be applied to this input pin. Alternatively, tying this pin                                                                                                                        |  |  |  |  |  |  |

|        |              | to AV <sub>ss</sub> enables the internal clock oscillator.                                                                                                                                                                           |  |  |  |  |  |  |

|        | BUSY         | This output indicates converter status. BUSY is low during conversion and calibration.                                                                                                                                               |  |  |  |  |  |  |

|        | CONVST       | Conversion start. A low to high transition on this logic input pin, when the AD7882 is configured for                                                                                                                                |  |  |  |  |  |  |

|        |              | asynchronous operation, places the Sample-and-Hold amplifier in the hold mode and starts conversion.                                                                                                                                 |  |  |  |  |  |  |

|        | BIP/UP       | Bipolar/Unipolar select logic input. A logic high selects the bipolar input range, $(A_{IN} Range = \pm V_{REFIN})$ and a                                                                                                            |  |  |  |  |  |  |

|        | OL EED       | logic low selects the unipolar range, $(A_{IN} Range = 0 \text{ to } V_{REFIN})$ .                                                                                                                                                   |  |  |  |  |  |  |

|        | SLEEP        | Sleep function, active low logic input. Once asserted, the AD7882 enters the low-power mode. All internal                                                                                                                            |  |  |  |  |  |  |

|        | CAL          | circuitry including the internal voltage reference is powered down. Calibration data is retained.                                                                                                                                    |  |  |  |  |  |  |

|        | CAL          | Active low logic input. A logic low on this input resets all internal logic and initiates a calibration. Initiating a calibration overrides all other internal operations and if a conversion is in progress, it will be terminated. |  |  |  |  |  |  |

|        | M/S          | Mode/Sync logic input. This is a dual function pin. When the device is in the CAL mode (CAL input low), it                                                                                                                           |  |  |  |  |  |  |

|        | 142.0        | determines the calibration mode. When the device is in the normal operating mode, it determines whether                                                                                                                              |  |  |  |  |  |  |

|        |              | conversion is synchronous or asynchronous. Synchronous operation means that the device continuously                                                                                                                                  |  |  |  |  |  |  |

|        |              | converts the input in synchronism with the clock. Asynchronous operation means that the device converts the                                                                                                                          |  |  |  |  |  |  |

|        |              | analog input in response to the application of a CONVST signal. See Table I for the CAL, M/S Truth Table.                                                                                                                            |  |  |  |  |  |  |

|        |              | Note that the control register can be used to disable this input pin. See Control Register Section.                                                                                                                                  |  |  |  |  |  |  |

|        |              |                                                                                                                                                                                                                                      |  |  |  |  |  |  |

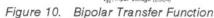

### Table I. AD7882 Operating Modes

| CAL | M/S | Function               |

|-----|-----|------------------------|

| 1   | 0   | Asynchronous Operation |

| 1   | 1   | Synchronous Operation  |

| 0   | σ   | Device Calibration     |

| 0   | 1   | System Calibration     |

### CIRCUIT DESCRIPTION

#### Analog Input

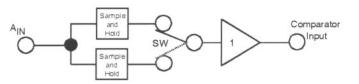

The analog input circuitry includes two SHAs in a ping-pong configuration as in Figure 8. The SHAs alternatively acquire the analog input and hold the output constant for the ADC conversions. During conversion, one of the SHAs is in the hold mode while the other is in the sample mode. The sample

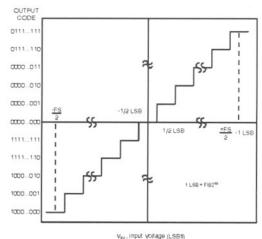

states are then switched after every conversion. The nd hold benefit of this configuration is to eliminate the need for acquiime between conversions sition t The throughput time is now effecti vely equal to ersion time which is 3.0 µs. The con put either unipolar or bipolar depend rar can b s of the BI P/IIP ing on the statu The transfer functio input. for the unipolar range ile the transfer binary wh function for the bipolar inpu 2s comple ment. These ar is shown in Figures 9 and 10. OUTPUT CODE 1111...111 1111...110 1111...101 1111...100 0000...011 1 LSB = FS/26 0000...010 0000...001

#### Calibration

The AD7882 conversion procedure is based on the successive approximation algorithm. Accuracy of the individual components, such as the DAC and comparator, is critical to achieve 16-bit performance. The comparator uses an auto-zero technique to null both internal and external offsets. Another advantage of this scheme is that it nulls 1/f noise. The auto-zero switching occurs well above the 1/f roll-off frequency, thus the noise appears as a dc offset which gets cancelled.

The internal DAC uses binary weighted capacitors instead of the traditional R-2 R ladder type. This allows the AD7882 to employ a calibration routine which nulls the errors of the individual DAC segments along with offset and gain errors. Each segment of the capacitor DAC contains multiple capacitors which are used to trim for absolute accuracy. During a calibration routine, the DAC segments are compared against other segments and trimmed to 1/4 LSB accuracy. Offset and gain errors are then calibrated either against the device AGND and  $V_{\text{REFLN}}$  inputs or external reference voltages that are applied at the  $A_{\text{IN}}$  input.

#### Calibration Routine

The AD7882 is capable of two calibration methods; system calibration and device calibration. Both modes calibrate the internal DAC inearity along with offset and gain errors. A system calibration is where the device calibrates its full scale and offset voltages against externally applied roltages. For a device calibration full scale and offset are calibrated against the  $V_{REFIK}$  and AGND inputs. Note that a calibration must always be initiated after power on to meet the device performance specifications.

Calibration may be initiated in hardware by asserting the CAL pin or in software by writing the appropriate word to the control register. The AD7882 will always perform a full calibration if initiated in hardware. However, under software control, partial calibration options including only offset and gain, can be performed. These options are shown in Table III.

### **Device** Calibration

Device calibration is initiated by pulsing  $\overline{CAL}$  low; see Figure 6. Offset and gain are calibrated against the AGND and  $V_{REFIN}$  inputs respectively. This calibration procedure takes 928 ms, when using a 10 MHz clock.

#### System Calibration

System calibration is initiated by a positive edge on  $\overline{CAL}$  as shown in Figure 7. BUSY goes low three times during the calibration procedure corresponding to the DAC, offset and gain calibrations respectively. The rising edge of the first BUSY pulse indicates that the DAC calibration is complete and the AD7882 is now ready to calibrate the offset. This is achieved by applying an external 0 V input at the A<sub>IN</sub> input and asserting the CONVST input. Note, the external 0 V input must be within  $\pm 1.5$  % of AGND. The rising edge of the second BUSY pulse indicates that the part is ready to calibrate full scale. This time, the full scale input voltage must be applied to the analog input and CONVST must be

# **Preliminary Technical Data**

asserted once again. The full-scale input voltage must be within  $\pm 1.5$  % of the reference input voltage. Complete calibration time is 928 ms plus the width of the two CONVST start pulses, when using a 10 MHz clock for the device.

### Configuring the M/S Input

The  $\overline{M/S}$  input with conjunction with the  $\overline{CAL}$  input determines the type of calibration iniated when  $\overline{CAL}$  is taken low. It also determines whether the conversion is asynchronous (controlled by the  $\overline{CONVST}$  input) or synchronous (with CLKIN). In all, they can be configured in four different ways as shown in Figure 11. The  $\overline{CAL}$  input is

Firure 11. M/S Input Configuration

asserted by a positive edge, when calibration is required. Then, for example if synchronous operation and device calibration is required, M/S is tied to  $\overline{CAL}$ . Note, an inverter can be used between the  $\overline{CAL}$  and the M/S inputs when asynchronous operation and system calibration is required.

If  $\overline{CAL}$  is high, then the user can start a Calibration from the Control Register.

### Timing and Control

Data communication with the AD7882 is controlled by four control inputs; CS, RD, WR and ADD0. The data transfer consists of reading and writing to the control register or coefficients register and reading the conversion result from the output data register.

### Conversion Control and Data Reads

Conversion can be controlled in hardware by asserting the CONVST input (Asynchronous Mode) or the device can be set up for continuous "back-to-back" conversions (Synchronous Mode). The M/S input controls these as outlined above. In Synchronous Mode, a Power-Up, CAL or

# AD7882

CONVST will initiate operation.

12

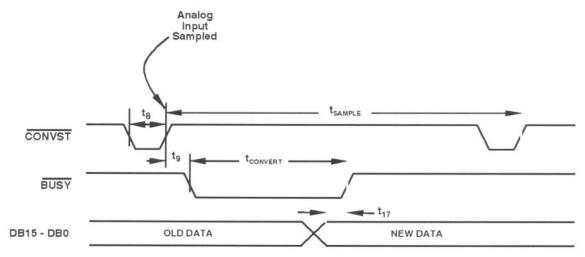

The data outputs are controlled by the  $\overline{CS}$  and  $\overline{RD}$  inputs. The possible timing configurations are shown in Figures 3, 4 and 5. If  $\overline{CS}$  and  $\overline{RD}$  are tied permanently low then the data bus will always be active. However, it will change state at the end of conversion to reflect the most recent result. Reading the data bus must be avoided at this time.

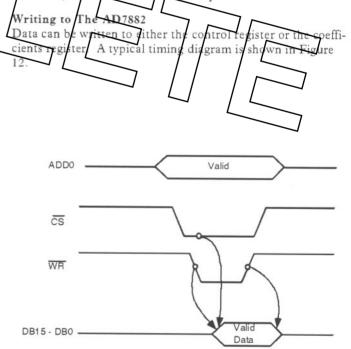

### **Control Register**

The control register serves the dual function of providing control and monitoring the status of the AD7882. This register is directly accessible through the data bus with a read or write operation while ADD0 is high. One of the option settings in the control register is to set up the coefficients register for reading or writing. The coefficient registers contain the calibration coefficients. Loading the coefficients to the register consists of writing 40, 16-bit words. This activity is considerably shorter for almost any processor than performing a calibration. Thus, a typical application might read all the coefficients after calibration, store them in the backup memory and rewrite them to the AD7882 in future power-up initialization routines. Reading the calibration coefficients confists of 40 read cycles to the AD7882. This will return 40, 16-bit words to the microprocessor.

Figure 12. Typical Write Timing

### Table II. Control Register Bit Functions

|                  | Bit Location | I/O Option | Power-Up<br>Default | Function                                                                                                                                                                                                                                                                                                                              |

|------------------|--------------|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | CR0          | Read Only  | 0                   | Conversion status. This bit is high during conversion.                                                                                                                                                                                                                                                                                |

|                  | CR1          | Read Only  | 0                   | Calibration status. This bit is high during calibration.                                                                                                                                                                                                                                                                              |

|                  | CR2          | Read/Write | BIP/UP              | BIP/UP Select. Unipolar operation is selected when CR2 is 0; bipolar operation is selected when CR2 is 1. This assumes that CR3 is 1. When CR3 is 0, CR2 reflects the BIP/UP input.                                                                                                                                                   |

|                  | CR3          | Read/Write | 0                   | If CR3 = 1 then Control Register bits CR2, CR9 and CR10 have priority.<br>Otherwise external pins, $\overline{SLEEP}$ and $\overline{BIP}/\overline{UP}$ have priority.                                                                                                                                                               |

|                  | CR4          | Read/Write | 0                   | CR4 to CR7 determine the calibration function, see Table III.                                                                                                                                                                                                                                                                         |

|                  | CR5          | Read/Write | 1                   | Calibration function, See CR4.                                                                                                                                                                                                                                                                                                        |

|                  | CR6          | Read/Write | 1                   | Calibration function, See CR4.                                                                                                                                                                                                                                                                                                        |

|                  | CR7          | Read/Write | 1                   | Calibration function, See CR4.                                                                                                                                                                                                                                                                                                        |

|                  | CR8          |            |                     | Not Used                                                                                                                                                                                                                                                                                                                              |

| $\left  \right $ | CR9          | Read/Write | SLEEP               | Sleep Control Bit. When CR3 is 1, setting CR9 to 0 powers down all circuitry                                                                                                                                                                                                                                                          |

|                  |              | Read Write | SIREP               | except the reference. When CR3 is 0, CR9 reflects the state of the SLEEP input.<br>Reference power down. When CR3 is 1, reference is powered by writing a 0 to CR10. When CR3 is 0, CR10 reflects the state of the SLEEP input.                                                                                                       |

|                  |              | Read )     |                     | A 1 in this location indicats an overflow on $A_{IN}$ in the last conversion and a gain adjust is required to bring the input back within range.                                                                                                                                                                                      |

|                  | CR12         | Read       | ○))((               | A 1 in this location indicats an underflow on $A_{IN}$ in the last conversion and a gain adjust is required to bring the input back within range.                                                                                                                                                                                     |

|                  | CR13         |            | $\sim$              | Not Used                                                                                                                                                                                                                                                                                                                              |

|                  | CR14         | Read/Write | 0                   | Status Bit If this is 1, it means that the calibration is halted. Calibration can be continued by writing a 0 to this location.                                                                                                                                                                                                       |

|                  | CR15         | Read/Write | 1                   | Reset Bit. All memory and logic is reset when a 0 is writter to this location.<br>Reset happens on the rising edge of WR. If there is a subsequent control<br>register read all bits except CR15 will have Power Up Default setting.<br>Therefore, to restart after a software reset, it is necessary to write a 1 back into<br>CR15. |

|                  |              |            |                     | GRID.                                                                                                                                                                                                                                                                                                                                 |

### Table III. Calibration Options Using the Control Register.

| CR7 | CR6 | CR5 | CR4 | Function                                        |

|-----|-----|-----|-----|-------------------------------------------------|

| 0   | 0   | 0   | 0   | Normal Conversion, No Calibration               |

| 0   | 0   | 0   | 1   | Normal Conversion, No Calibration               |

| 0   | 0   | 1   | 0   | Gain Error only - Device Calibration            |

| 0   | 0   | 1   | 1   | Gain Error only - System Calibration            |

| 0   | 1   | 0   | 0   | Offset Error only - Device Calibration          |

| 0   | 1   | 0   | 1   | Offset Error only - System Calibration          |

| 0   | 1   | 1   | 0   | Offset and Gain Error only - Device Calibration |

| 0   | 1   | 1   | 1   | Offset and Gain Error only - System Calibration |

| 1   | 0   | 0   | 0   | Read All Calibration Coefficients               |

| 1   | 0   | 0   | 1   | Write All Calibration Coefficients              |

| 1   | 0   | 1   | 0   | Read Gain Calibration Coefficients only         |

| 1   | 0   | 1   | 1   | Write Gain Calibration Coefficients only        |

| 1   | 1   | 0   | 0   | Read Offset Calibration Coefficients only       |

| 1   | 1   | 0   | 1   | Write Offset Calibration Coefficients only      |

| 1   | 1   | 1   | 0   | Full Device Calibration                         |

| 1   | 1   | 1   | 1   | Full System Calibration                         |