# Integrated LCD Grayscale Generator

# ADD8502

#### FEATURES

Two Mask Programmable Sets of Five Reference Levels Dual 10-Bit DACs for Flicker Offset and Range Adjustment Integrated  $V_{COM}$  Switching Single-Supply Operation: 5.0 V Low Supply Current: 300  $\mu$ A Global Power Save Mode: 1  $\mu$ A Max Fast Settling Time for Load Change: 20  $\mu$ s Stable with 20 nF/100  $\Omega$  Loads CMOS/TTL Input Levels

APPLICATIONS Color TFT Cell Phones Color TFT PDAs

#### **GENERAL DESCRIPTION**

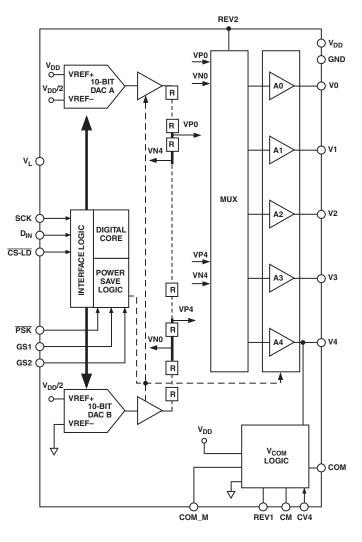

The ADD8502 is an integrated, high accuracy, programmable grayscale generator. Two sets of five output reference voltages are mask programmed to 0.2% resolution. The outputs switch between the two sets of five levels. The reference levels are selected from a 512 tap resistor network using a via mask.

ADD8502 includes two serially addressable, 10-bit digital-toanalog converters (DACs) and five fast, low current buffers. The dual DACs set the endpoint voltages applied to the resistor network to adjust for flicker and range. The two power save modes can reduce the total current to less than 1  $\mu$ A and feature fast recovery time from Shutdown/Sleep Mode. The ADD8502 accepts CMOS or TTL inputs for all controls, including the common drive circuit levels.

ADD8502 operates over the industrial temperature range from  $-40^{\circ}$ C to  $+85^{\circ}$ C and is available in a space-saving 24-lead 4 mm  $\times$  4 mm frame chip scale package.

#### FUNCTIONAL BLOCK DIAGRAM

#### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2002

# $\label{eq:added_bar} ADD8502 \\ -SPECIFICATIONS \ (@v_{DD} = 5.0 \ v, \ -40^\circ C \leq T_A \leq +85^\circ C, \ unless \ otherwise \ noted.)$

| Parameter                                                                                                                                                                                                                             | Symbol                                                                             | Conditions                                                                                                                                                                                                                 | Min               | Тур                                             | Max                                                            | Unit                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|--|

| $\begin{array}{c} \text{SYSTEM ACCURACY} \\ \text{V}_{\text{OUT}} \text{ Error} \\ \text{Swing Error}^1 \\ \text{Mean Error}^2 \\ \text{Mean Error between Adjacent Channels}^3 \\ \text{Mean Error between V0 and V4}^4 \end{array}$ |                                                                                    | $\begin{array}{l} (V_{Pn}-V_{Nn})-(V_{Pi}-V_{Ni}) \\ (V_{Pn}+V_{Nn})/2-(V_{Pi}+V_{Ni})/2) \end{array}$                                                                                                                     |                   | 3<br>1<br>3<br>3<br>3                           | 20<br>17<br>21<br>21<br>25                                     | mV<br>mV<br>mV<br>mV<br>mV                            |  |

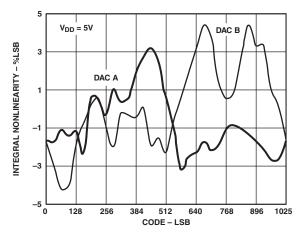

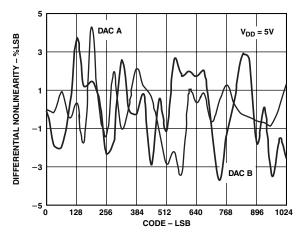

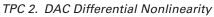

| DAC ACCURACY<br>Resolution<br>Differential Nonlinearity<br>Integral Nonlinearity <sup>5</sup><br>Offset Error<br>Gain Error                                                                                                           | DNL<br>INL                                                                         |                                                                                                                                                                                                                            |                   | $10 \pm 0.25 \pm 0.5 \pm 0.4 \pm 0.15$          |                                                                | Bits<br>LSB<br>LSB<br>% of FSR<br>% of FSR            |  |

| OUTPUT CHARACTERISTICS<br>Output Current<br>Short Circuit Current<br>Output Leakage Current in High-Z Mode<br>Slew Rate<br>Settling Time to 1%<br>Slew Rate <sup>5</sup><br>Settling Time to 1% <sup>5</sup><br>Phase Margin          | $I_{OUT} \\ I_{SC} \\ I_{LEAKAGE} \\ SR \\ t_{S} \\ SR \\ t_{S} \\ t_{S} \\ \phio$ | $\begin{array}{l} (V_{DD}-1 \ V) \\ \text{Short to Ground} \\ \text{High-Z Mode} \\ R_L = 100 \ k\Omega \\ \text{V0 to V4 Step Size} \\ L_D = 100 \ \Omega \ \text{Series 16 nF} \\ \text{V0 to V4 Step Size} \end{array}$ |                   | 25<br>60<br>0.01<br>1.25<br>8<br>0.7<br>8<br>67 | 1.0<br>12<br>12                                                | mA<br>mA<br>μA<br>V/μs<br>μs<br>V/μs<br>μs<br>Degrees |  |

|                                                                                                                                                                                                                                       | Z<br>Z<br>Z<br>Z                                                                   | See Table IV<br>I = 20 mA                                                                                                                                                                                                  |                   | 25<br>25<br>25<br>25                            | 50<br>50<br>50<br>50                                           | Ω<br>Ω<br>Ω<br>Ω                                      |  |

| MASK PROGRAMMABLE<br>RESISTOR CHAIN<br>Resistor Matching                                                                                                                                                                              | R <sub>MATCH</sub>                                                                 | Any Two Segments between<br>512 Resistor String                                                                                                                                                                            |                   | 1                                               |                                                                | %                                                     |  |

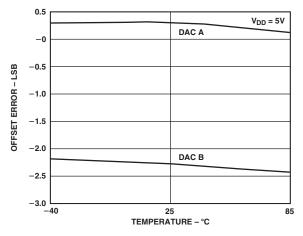

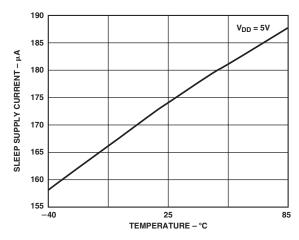

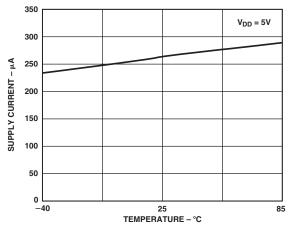

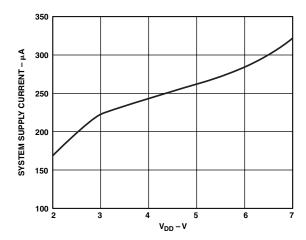

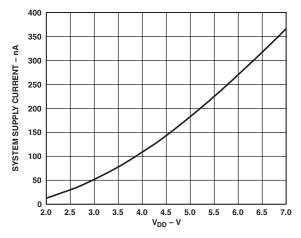

| POWER SUPPLY<br>Supply Voltage<br>Supply Current<br>Shutdown Supply Current<br>Sleep Supply Current<br>Shutdown Recovery Time<br>Sleep Recovery Time                                                                                  | V <sub>DD</sub><br>I <sub>SY</sub><br>I <sub>SY-GLB</sub><br>I <sub>SY-GS1-3</sub> | V <sub>DD</sub> = 5 V; No Load<br>Full Shutdown Mode<br>Mid 3 Buffers Shutdown<br>Global PD to 1%<br>V1–V3 Off to 1%                                                                                                       | 4.5<br>190<br>140 | 5<br>270<br>0.2<br>175<br>23<br>10              | 5.5<br>400<br>1<br>210<br>30<br>15                             | V<br>μΑ<br>μΑ<br>μα<br>μs<br>μs                       |  |

| LOGIC SUPPLY<br>Logic Input Voltage Level<br>Logic Input Current                                                                                                                                                                      | $V_{\rm L}$ $I_{\rm VL}$                                                           |                                                                                                                                                                                                                            | 2.3               | 3.3<br>0.01                                     | 5.5<br>1                                                       | V<br>μA                                               |  |

| DIGITAL I/O<br>Digital Input High Voltage<br>Digital Input Low Voltage<br>Digital Input Current<br>Digital Input Capacitance                                                                                                          | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IN</sub><br>C <sub>IN</sub>           | $GND \le V_{IN} \le 5.5 \text{ V}$                                                                                                                                                                                         | $V_L \times 0.$   | 7                                               | $\begin{array}{c} V_L \times \ 0.3 \\ \pm 1 \\ 10 \end{array}$ | V<br>V<br>μA<br>pF                                    |  |

NOTES

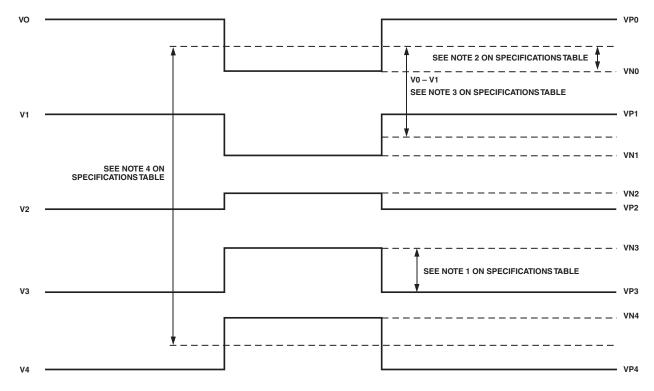

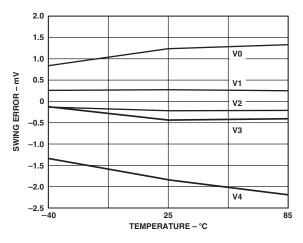

<sup>1</sup>Swing error is a comparison of measured V<sub>OUT</sub> step versus theoretical V<sub>OUT</sub> step. Theoretical values can be found on the Mask Tap Point Option sheet.

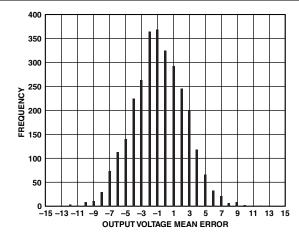

<sup>2</sup>Mean error is measured  $V_{OUT}$  mean versus theoretical  $V_{OUT}$  mean (see Figure 3).

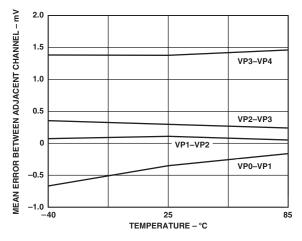

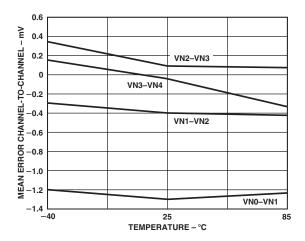

<sup>3</sup>Mean errors between two adjacent channels versus theoretical (see Figure 3).

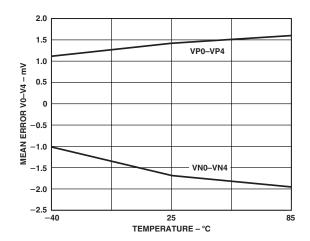

$^{4}$ Mean errors between V0 and V4 versus theoretical (see Figure 3).

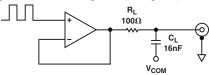

<sup>5</sup>Slew rate and settling time are measured between the output resistor and the capacitor (see Figure 1).

Specifications subject to change without notice.

Figure 1. Slew Rate Diagram

|                                                         | 1               |     |     |     | 1    |

|---------------------------------------------------------|-----------------|-----|-----|-----|------|

| Parameter                                               | Symbol          | Min | Тур | Max | Unit |

| SCK Cycle Time                                          | t <sub>1</sub>  | 100 |     |     | ns   |

| SCK High Time                                           | t <sub>2</sub>  | 45  |     |     | ns   |

| SCK Low Time                                            | t <sub>3</sub>  | 45  |     |     | ns   |

| CS-LD Setup Time                                        | t <sub>4</sub>  | 20  |     |     | ns   |

| Data Setup Time                                         | t <sub>5</sub>  | 5   |     |     | ns   |

| Data Hold Time                                          | t <sub>6</sub>  | 5   |     |     | ns   |

| LSB SCK High to CS-LD High                              | t <sub>7</sub>  | 5   |     |     | ns   |

| Minimum CS-LD High Time                                 | t <sub>8</sub>  | 10  |     |     | ns   |

| SCK to $\overline{\text{CS-LD}}$ Active Edge Setup Time | t <sub>9</sub>  | 5   |     |     | ns   |

| CS-LD High to SCK Positive Edge                         | t <sub>10</sub> | 10  |     |     | ns   |

| SCK Frequency (Square Wave)                             |                 |     |     | 10  | MHz  |

| Table I. | Serial Data | Timing | Characteristics |

|----------|-------------|--------|-----------------|

|----------|-------------|--------|-----------------|

NOTES

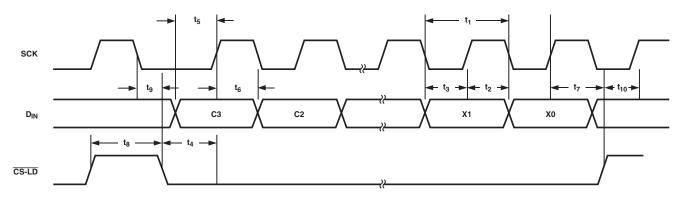

<sup>1</sup>All input signals are specified with rise/fall time –5 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_S + V_{IH}$ )/2. <sup>2</sup>See Figure 2.

Figure 3. Output Wave Form Diagram

#### **ABSOLUTE MAXIMUM RATINGS\***

| V <sub>DD</sub> to GND                     | –0.3 V to +7 V            |

|--------------------------------------------|---------------------------|

| V <sub>L</sub> to GND                      | –0.3 V to +7 V            |

| Digital Input Voltage to GND               | –0.3 V to +7 V            |

| V <sub>OUT</sub> to GND0.3 V               | to V <sub>DD</sub> +0.3 V |

| V <sub>COM</sub> to GND0.3 V               | to $V_{DD}$ +0.3 V        |

| Storage Temperature Range                  | 5°C to +150°C             |

| Lead Temperature Range (Soldering, 10 sec) |                           |

| Vapor Phase (60 sec)                       | 300°C                     |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Package Type        | $\theta_{JA}{}^1$ | $\Psi_{JB}^{2}$ | Unit |

|---------------------|-------------------|-----------------|------|

| 24-Lead LFCSP (ACP) | 34.8              | 13              | °C/W |

NOTES

${}^1\theta_{JA}$  is specified for worst-case conditions, i.e.,  $\theta_{JA}$  is specified for device soldered in circuit board for surface-mount packages.

$^2\psi_{JB}$  is applied for calculating the junction temperature by reference to the board temperature.

#### **ORDERING GUIDE**

| Model      | Temperature<br>Range               |               | Package<br>Option |

|------------|------------------------------------|---------------|-------------------|

| ADD8502ACP | $-40^{\circ}$ C to $+85^{\circ}$ C | 24-Lead LFCSP | CP-24             |

Available in 7" reel only.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADD8502 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

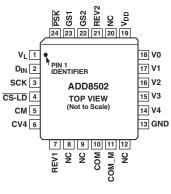

#### PIN CONFIGURATION

NC = NO CONNECT

#### **PIN FUNCTION DESCRIPTIONS**

| Pin No. | Mnemonic        | Name                                    | I/O | Description                                                                                                                                                                                                            |

|---------|-----------------|-----------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VL              | Logic Select Pin                        | Ι   | Logic Supply Voltage. Connect to supply used for system logic. Can accept 2.7 V to V <sub>DD</sub> .                                                                                                                   |

| 2       | D <sub>IN</sub> | Serial Data Input                       | Ι   | When CS is LOW, the input on this pin is shifted into the internal shift register on the rising edge of SCK.                                                                                                           |

| 3       | SCK             | Serial Clock                            | Ι   | Accepts up to 10 MHz input. The rising edge on this clock will shift the data on $D_{IN}$ Pin into the internal shift registers.                                                                                       |

| 4       | CS-LD           | Load                                    | Ι   | When $\overline{\text{CS-LD}}$ is LOW, SCK is enabled for shifting data on the D <sub>IN</sub> input into the internal shift register on the rising edge of SCK. Data is loaded MSB first.                             |

| 5       | СМ              | Logic Control 2<br>for V <sub>COM</sub> | Ι   | When CM is LOW, COM will output the voltage level input on COM_M.<br>When CM is HIGH, COM levels will be determined by the input on REV1.                                                                              |

| 6       | CV4             | Logic Control V4                        | Ι   | If CV4 is HIGH, V4 output is the output of the op amp A4. If CV4 is LOW, V4 is connected to COM and op amp A4 is shut down. Refer to Table II.                                                                         |

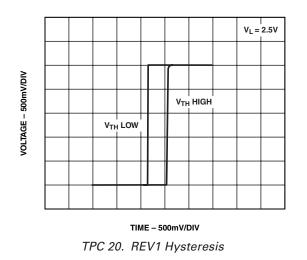

| 7       | REV1            | Logic Control 1 for $V_{COM}$           | Ι   | With CM HIGH, a HIGH on REV1 will cause COM to output the voltage level input at $V_{DD}$ . A LOW on REV1 will cause COM to output the voltage level input at GND.                                                     |

| 8       | NC              | No Connect                              |     | Unused Pin                                                                                                                                                                                                             |

| 9       | NC              | No Connect                              |     | Unused Pin                                                                                                                                                                                                             |

| 10      | СОМ             | Common Output                           | 0   | If CM is LOW, COM will output the voltage input at COM_M. If CM is HIGH, COM will output the voltage input at $V_{DD}$ when REV1 is HIGH and will output the voltage input at GND when REV1 is LOW. Refer to Table II. |

| 11      | COM_M           | Common System<br>V <sub>REF</sub>       | Ι   | COM_M is a system voltage reference input between 2.5 V and 3.5 V. This may be the system 3.3 V supply.                                                                                                                |

| 12      | NC              | No Connect                              |     | Unused Pin                                                                                                                                                                                                             |

| 13      | GND             | Ground                                  | Ι   | Ground. Nominally 0 V.                                                                                                                                                                                                 |

| 14      | V4              | Output                                  | 0   | Buffers are rail-to-rail buffers that can drive high capacitive loads (>16.5 nF). When $\overline{PSK}$ is LOW, these outputs will be Hi-Z.                                                                            |

| 15      | V3              | Output                                  | 0   | Buffers are rail-to-rail buffers that can drive high capacitive loads (>16.5 nF). When $\overline{PSK}$ is LOW or GS1 and GS2 = HIGH, these outputs will be Hi-Z.                                                      |

| 16      | V2              | Output                                  | 0   | Buffers are rail-to-rail buffers that can drive high capacitive loads (>16.5 nF). When $\overline{PSK}$ is LOW or GS1 and GS2 = HIGH, these outputs will be Hi-Z.                                                      |

| 17      | V1              | Output                                  | 0   | Buffers are rail-to-rail buffers that can drive high capacitive loads (>16.5 nF). When $\overline{PSK}$ is LOW or GS1 and GS2 = HIGH, these outputs will be Hi-Z.                                                      |

| 18      | V0              | Output                                  | 0   | Buffers are rail-to-rail buffers that can drive high capacitive loads (>16.5 nF).<br>When PSK is LOW, these outputs will be Hi-Z.                                                                                      |

| 19      | V <sub>DD</sub> | Supply                                  | Ι   | Supply Voltage. Nominally 5 V.                                                                                                                                                                                         |

| 20      | NC              | No Connect                              |     | Unused Pin                                                                                                                                                                                                             |

| Pin No. | Mnemonic | Name                       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------|----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21      | REV2     | Reference Output<br>Select | Ι   | When $\overline{\text{PSK}}$ is HIGH and GS1 or GS2 is LOW, then INVERT selects the output<br>levels on V0 to V4. If INVERT is HIGH, outputs V0 to V4 are connected to<br>reference levels VP0 to VP4, respectively. If INVERT is LOW, outputs V0 to V4<br>are connected to reference levels VN0 to VN4, respectively. When $\overline{\text{PSK}}$ is HIGH<br>and GS1 and GS2 are HIGH, V1–V3 are, Hi-Z state, but V0 and V4 are still<br>connected to reference levels VP0 and VP4 when INVERT is HIGH. Outputs V0<br>and V4 switch to VN0 and VN4 when REV is LOW. |

| 22      | GS2      | Sleep Mode<br>Select       | Ι   | When GS1 and GS2 are HIGH, the middle three output buffers are shut down<br>and V1, V2, and V3 are put into Hi-Z states. Other combinations of GS1 and GS2<br>leave the outputs of A1 to A3 fully active.                                                                                                                                                                                                                                                                                                                                                             |

| 23      | GS1      | Sleep Mode<br>Select       | I   | When GS1 and GS2 are HIGH, the middle three output buffers are shut down<br>and V1, V2, and V3 are Hi-Z. Other combinations of GS1 and GS2 leave the<br>outputs of A1 to A3 fully active.                                                                                                                                                                                                                                                                                                                                                                             |

| 24      | PSK      | Global Power<br>Shutdown   | I   | When $\overline{\text{PSK}}$ is pulled LOW, the chip will be put into the full Power-Down Mode.<br>The DACs, resistor ladder network preamps, and output buffers will all be shut<br>down, and A0 to A4 will be in Hi-Z states. Recovery from full power-down to<br>normal operation is within 30 $\mu$ s.                                                                                                                                                                                                                                                            |

All digital inputs accept CMOS or TTL logic levels.

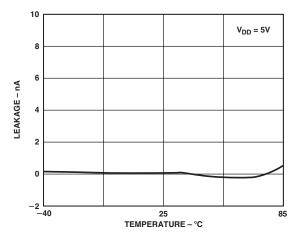

# **Typical Performance Characteristics-ADD8502**

TPC 3. Offset Error vs. Temperature

TPC 4. Shutdown Current vs. Temperature

TPC 5. Sleep Supply Current vs. Temperature

TPC 6. Supply Current vs. Temperature

TPC 7. System Supply Current at Full Power

TPC 8. System Supply Current at Shutdown

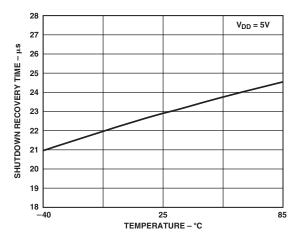

TPC 9. Shutdown Recovery Time vs. Temperature

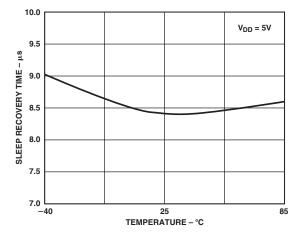

TPC 10. Sleep Recovery Time vs. Temperature

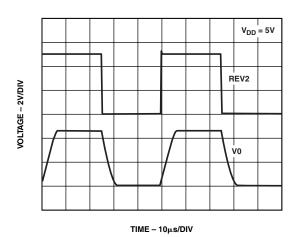

TPC 12. V0 Output Swing Response to REV2

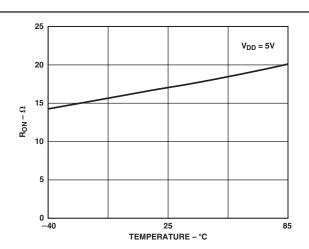

TPC 13. V<sub>COM</sub> Switch-On-Resistance vs. Temperature

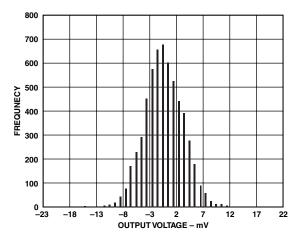

TPC 14. V<sub>OUT</sub> Error Distribution

TPC 15. Swing Error vs. Temperature

TPC 16. V<sub>OUT</sub> Swing Mean vs. Distribution

TPC 17. Mean Error between Adjacent Channel vs. Temperature

TPC 18. Mean Error between Adjacent Channel vs. Temperature

TPC 19. Mean Error between V0 and V4 vs. Temperature

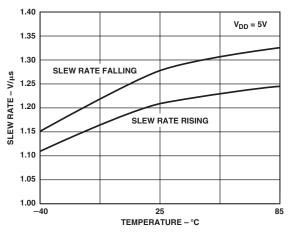

TPC 21. Slew Rate vs. Temperature

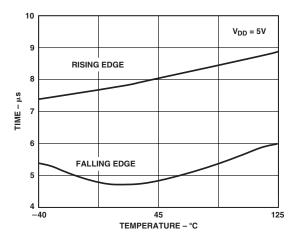

TPC 22. Settling Time at V<sub>OUT</sub> vs. Temperature

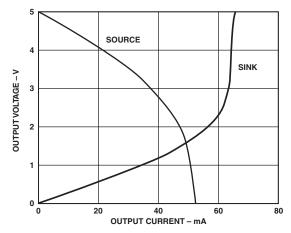

TPC 23. Output Current Source and Sink

#### **OPERATION**

#### **Transfer Function**

The transfer function for the ADD8502 is given in the following equations:

1. Digital-to-analog transfer function for DAC A. An output can be derived from Equation 1 as:

$$V_{OUTA} = \left(\frac{V_{DD}}{2}\right) \left(1 + \frac{D_A}{1024}\right) \tag{1}$$

2. Digital-to-analog transfer function for DAC B. An output can be derived from Equation 2 as:

$$V_{OUTB} = \left(\frac{D_B}{1024}\right) \left(\frac{V_{DD}}{2}\right) \tag{2}$$

Where  $D_A$  and  $D_B$  are decimal equivalents of the binary codes that are loaded to the DAC Register from 0 to 1023.

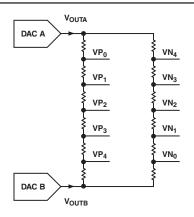

3. Using any programmed tap point from the 512 resistor string, the system output can be derived from Equation 3:

$$V_{TX} = (V_{OUTA} - V_{OUTB}) \left(\frac{T_X}{512}\right) + V_{OUTB}$$

(3)

Where  $T_X$  is any tap point of the 512 resistor string. It is mask programmable.  $V_{TX}$  is the voltage output at any output (VO, ... V4) and will switch between two voltages depending on the mask programmed tap points.

Example:  $V_{DD} = 5$  V,  $D_A = 1,000$ ,  $D_B = 100$ , and  $T_X = 500$ .

$V_{OUTA} = 4.941 \text{ V}$  $V_{OUTB} = 0.244 \text{ V}$  $V_{TX} = 4.831 \text{ V}$

Equations 1–3 will provide a theoretical calculation of the outputs. The actual will vary with load, process, and architecture. See Specifications table.

#### SERIAL INTERFACE

The ADD8502 has a 3-wire serial interface ( $\overline{\text{CS-LD}}$ , SCK, and  $D_{\text{IN}}$ ). The writing sequence begins by bringing the  $\overline{\text{CS-LD}}$  line LOW. Data on the  $D_{\text{IN}}$  line is clocked into the 16-bit shift register on the rising edge of SCK. The serial clock frequency can be as high as 10 MHz. When the last data bit is clocked in,  $\overline{\text{CS-LD}}$  line needs to be brought HIGH to load the DAC registers and the operation mode is dependent upon the control bits.

#### **Input Shift Register**

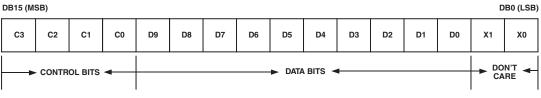

The input shift register is 16 bits wide (see Figure 4). The first four control bits (C3, C2, C1, and C0) are used to set the different operating modes of the device. The next 10 bits are the data bits and the last two bits are "Don't Cares." This composes a full word that is transferred to the DAC register on the rising edge of  $\overline{CS}$ -LD.

In a normal write sequence, the  $\overline{\text{CS-LD}}$  line is kept LOW for at least 16 rising edges of SCK and then it is brought HIGH to update the DACs. However, if  $\overline{\text{CS-LD}}$  is brought HIGH before the 16<sup>th</sup> rising edge, this acts as an interrupt to the write sequence. The shift register is reset and the write sequence is seen as invalid. Neither an update of the DAC register contents nor a change in the operation mode occurs.

Figure 4. Input Register Contents

| Con<br>C3             | trol<br>C2            |                       | le<br>C0              | Status                                     | Input Register<br>Status                                 | DAC Register<br>(Sleep/Wake) | Power-Down Status<br>Comments                                                                                                                                    |

|-----------------------|-----------------------|-----------------------|-----------------------|--------------------------------------------|----------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                     | 0                     | 0                     | 0                     | No Change                                  | No Update                                                | No Change                    | No operation; power-down status unchanged (part stays in Wake or Sleep Mode).                                                                                    |

| 0                     | 0                     | 0                     | 1                     | Load DAC A                                 | No Update                                                | No Change                    | Load input Register A with data. DAC outputs unchanged. Power-down status unchanged.                                                                             |

| 0                     | 0                     | 1                     | 0                     | Load DAC B                                 | No Update                                                | No Change                    | Load input Register B with data. DAC outputs unchanged. Power-down status unchanged.                                                                             |

| 0<br>0<br>0<br>0<br>0 | 0<br>1<br>1<br>1<br>1 | 1<br>0<br>0<br>1<br>1 | 1<br>0<br>1<br>0<br>1 |                                            | Not Used<br>Not Used<br>Not Used<br>Not Used<br>Not Used |                              |                                                                                                                                                                  |

| 1                     | 0                     | 0                     | 0                     | No Change                                  | Update Outputs                                           | Wake                         | Load both DAC registers with existing contents<br>of input registers. Update DAC outputs. Part<br>wakes up.                                                      |

| 1                     | 0                     | 0                     | 1                     | Load DAC A                                 | Update Outputs                                           | Wake                         | Load input Register A. Load DAC registers with<br>new contents of input register A and existing<br>contents of Register B. Update DAC outputs.<br>Part wakes up. |

| 1                     | 0                     | 1                     | 0                     | Load DAC B                                 | Update Outputs                                           | Wake                         | Load input Register B. Load DAC registers with<br>new contents of input Register B and existing<br>contents of Register A. Update DAC outputs.<br>Part wakes up. |

| 1<br>1                | 0<br>1                | 1<br>0                | 1<br>0                |                                            | Not Used<br>Not Used                                     |                              |                                                                                                                                                                  |

| 1                     | 1                     | 0                     | 1                     | No Change                                  | No Update                                                | Wake                         | Part wakes up. Input and DAC registers<br>unchanged. DAC outputs reflect existing<br>contents of DAC registers.                                                  |

| 1                     | 1                     | 1                     | 0                     | No Change                                  | No Update                                                | Sleep                        | Power down the IC, put in into Sleep Mode.                                                                                                                       |

| 1                     | 1                     | 1                     | 1                     | Load DACs<br>A, B with Same<br>10-Bit Code | Update<br>Outputs                                        | Wake                         | Load both input registers. Load both DAC<br>registers with new contents of input registers.<br>Update DAC outputs. Part wakes up.                                |

#### Table II. DAC Control Function

#### **Modes of Operation**

The ADD8502 has various modes of operation, such as updating both DACs simultaneously or changing the power-down status (Sleep/Wake). These are selected by writing the appropriate 4-bit control code (C0–C3). The details for each mode are summarized in Table II.

#### Low Power Serial Interface

To reduce the power consumption of the device ever further, the interface only powers up fully when the device is being written to. As soon as the 16-bit control word has been written to the part, the SCK and  $D_{IN}$  input buffers are powered down. They only power up again following a falling edge of  $\overline{CS-LD}$ .

#### **Double-Buffered Interface**

The ADD8502 has double-buffered interfaces consisting of two banks of registers: input and DAC. The input register is connected directly to the input shift register, and the digital code is transferred to the relevant input register on completion of a valid write sequence. The DAC register contains the digital code used by the resistor string. Access to the DAC register is controlled by the control codes, C0 to C3. The user can update both DACs simultaneously as well as individually. It depends on the selected control codes to update individual output or both outputs simultaneously.

#### **Initial Power-Up Condition**

The ADD8502 has preset DAC conditions when its initially powered on. The DACs are loaded with 1110 1011 11 for the upper DAC and 0000 1010 00 for the lower DAC. The part is powered up in a normal operation mode (Wake Status).

#### **Power-Down Modes**

The ADD8502 has two shutdown modes. One mode is to fully shut down the device using  $\overline{PSK}$  or the digital serial control code, and the other mode is to shut down V1 to V3 buffers using GS1 and GS2. See Table III for the priority of the shutdown control functions.

The ADD8502 will have a quiescent current less than 1  $\mu$ A when it is fully shut down and all output buffers are switched to a high impedance state. The only active circuitries are the digital logics and the latches for the serial control. When the device is brought back from Sleep Mode to normal operation, it will use the last serial word to update the DACs or a new control code or data if any was loaded when the part was in Sleep Mode; i.e., the contents of the input register, DAC register, and power-down status shown in Table II is retained as long as V<sub>DD</sub> and V<sub>L</sub> are on.

The second power save mode (mid 3 buffers are shut down) is using GS1 and GS2. In a condition where both GS1 and GS2 logics are HIGH, the output buffers (V1, V2, and V3) are shut down and switched into a high impedance state.

| PSK | Serial<br>Control | GS1 | GS2 | Operation<br>Mode          |

|-----|-------------------|-----|-----|----------------------------|

| Н   | Wake              | L   | L   | Normal Operation           |

| Н   | Wake              | L   | Н   | Normal Operation           |

| Н   | Wake              | H   | L   | Normal Operation           |

| Н   | Wake              | Н   | Н   | Mid 3 Buffers are Shutdown |

| Н   | Sleep             | X   | Х   | Full Shutdown              |

| L   | X                 | X   | Х   | Full Shutdown              |

#### Table III. Shutdown Control Function

X = Don't Care

#### V<sub>COM</sub> Logic

$V_{COM}$  operation is described in Table IV. The  $V_{COM}$  logic is always active and its logic inputs are CM, REV1, and CV4. When CM is LOW, COM is connected to COM\_M. When CM is HIGH, COM is determined by the logic input of REV1. If REV1 is HIGH, COM is connected to  $V_{DD}$ . When REV1 is LOW, COM is connected to GND.

CV4 controls the V4 output. If CV4 goes LOW, V4 is connected to COM and A4 is shut down with its output in a Hi-Z state. When CV4 is HIGH, the switch connecting V4 to COM is open and A4 is in normal operation mode.

| Table | IV. | V <sub>COM</sub> | Logic | Control |

|-------|-----|------------------|-------|---------|

|-------|-----|------------------|-------|---------|

| Inputs | Outputs |     |                  |     |  |

|--------|---------|-----|------------------|-----|--|

| СМ     | REV1    | CV4 | V <sub>COM</sub> | V4  |  |

| L      | X       | L   | COM_M            | COM |  |

| L      | X       | Н   | COM_M            | A4  |  |

| Н      | L       | L   | GND              | COM |  |

| Н      | Н       | L   | V <sub>DD</sub>  | COM |  |

| Н      | L       | Н   | GND              | A4  |  |

| Н      | Н       | Н   | V <sub>DD</sub>  | A4  |  |

X = Don't Care

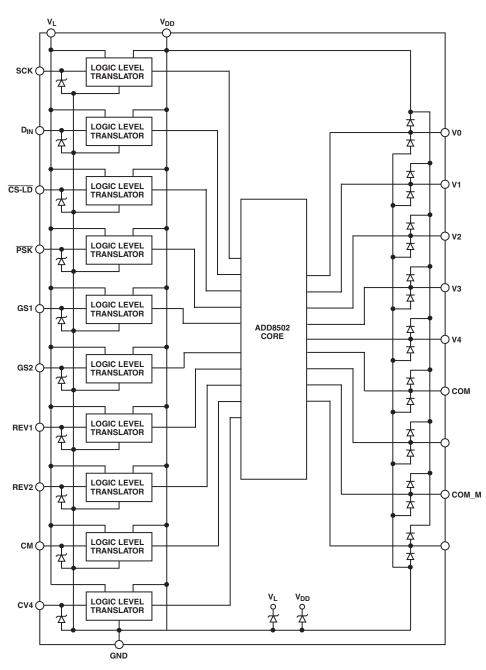

Figure 5. CST ESD and Logic Level Translation Scheme

#### ADD8502 Description

- The ADD8502 uses logic level translators to convert external logic levels to levels suitable for use in the ADD8502 core.

- The logic level translators are intended to be powered from the same supply voltage as is used to power the external logic driving the ADD8502.

- $V_{DD}$  may be powered down while normal voltages are present on the  $V_L$  and logic input pins.

- $V_{DD}$  and  $V_L$  are independent and can be in the range 0 V to 5.5 V.

- No damage to the digital inputs will occur with applied voltages up to 7 V (see Absolute Maximum Ratings section of data sheet).

- No current will flow between V<sub>DD</sub> and V<sub>L</sub> under normal operating conditions.

- Logic voltages can be present on the logic input pins even if  $V_L$  is powered down. Inputs are limited by max supply rating of 7 V.

- Digital input pins have ESD protection connected to GND.

- All other input and output pins have ESD protection connected to GND and  $V_{\text{DD}.}$

#### ADD8502-000 MASK OPTION

Table V. Default Power-Up Conditions

| DAC  | Setpoints | (0 < D < 1) | 023) |

|------|-----------|-------------|------|

| DING | ociponits |             | 0431 |

|           | Decimal Code | Voltage | Unit |

|-----------|--------------|---------|------|

| Upper DAC | 943          | 4.8022  | V    |

| Lower DAC | 40           | 0.0977  | V    |

**Resistor Tap Points (** $0 \le X \le 512$ **)**

|     | Tap Point | Voltage | Unit |

|-----|-----------|---------|------|

| VP0 | 450       | 4.2325  | V    |

| VP1 | 271       | 2.5878  | V    |

| VP2 | 203       | 1.9630  | V    |

| VP3 | 137       | 1.3565  | V    |

| VP4 | 3         | 0.1252  | V    |

| VN0 | 31        | 0.3825  | V    |

| VN1 | 215       | 2.0732  | V    |

| VN2 | 290       | 2.7624  | V    |

| VN3 | 367       | 3.4699  | V    |

| VN4 | 509       | 4.7747  | V    |

|     |           | 1       |      |

Supply voltage = 5 V

Tap point voltages can be derived from the following equation:

$$Vx = V_{OUTB} + \frac{X}{512} \left[ V_{OUTA} - V_{OUTB} \right]$$

Where  $V_{OUTA}$  and  $V_{OUTB}$  can be derived from the transfer functions under the Operation Section of the datasheet.

The ADD8502 uses a single resistor string consisting of 512 individual elements. Both sets of reference voltages ( $V_{P0}-V_{P4}$ ,  $V_{N0}-V_{N4}$ ) are generated from this single string. Two separate resistor networks are shown to demonstrate the tap points, which are changeable by mask option and completely independent of each other.

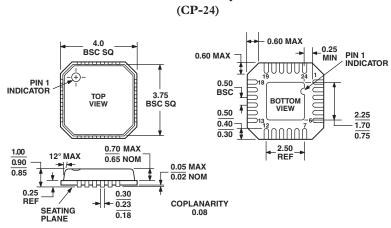

#### **OUTLINE DIMENSIONS**

#### 24-Lead Frame Chip Scale Package [LFCSP] 4x4 mm Body (CP-24)

COMPLIANT TO JEDEC STANDARDS MO-220-VGGD-2