# 3.8 Ω On-Resistance, SPDT Switch

#### **FEATURES**

- 3.8 Ω on resistance

- Specified at

- ▶ V<sub>DD</sub> = +5 V ± 10%

- ▶ V<sub>SS</sub> = -4.5 V to -8.8 V

- ► No V<sub>1</sub> supply required

- ▶ 3 V logic-compatible inputs

- ▶ Up to 310 mA continuous current

- ▶ Rail-to-rail operation

- ▶ 8-lead, 2 mm × 3 mm LFCSP

#### **APPLICATIONS**

- ▶ LDMOS power amplifier gate drive

- GAN power amplifier gate drive

- Communication systems

- Automatic test equipment

- Data acquisition systems

- Sample-and-hold systems

#### **GENERAL DESCRIPTION**

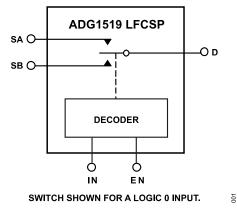

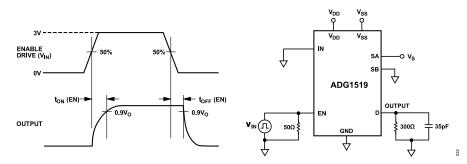

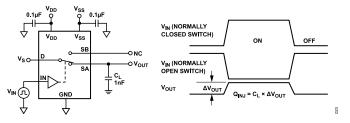

The ADG1519 is a single-pole, double throw (SPDT) switch. An EN input on the lead frame chip scale package (LFCSP) is used to enable or disable the device. When disabled, the switch terminals (SA, SB, and D) are high impedance.

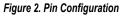

The ADG1519 is fully specified at  $V_{DD}$  = +5 V ± 10% and  $V_{SS}$  = -4.5 V to -8.8 V for applications that require asymmetrical supplies. The ADG1519 on-resistance profile is flat over the full analog input range, ensuring excellent linearity and low distortion when switching audio signals. The construction ensures ultra low power dissipation, making the device ideally suited for portable and battery-powered instruments.

The switch conducts equally well in both directions when on and has an input signal range that extends to the supplies. In the off condition, signal levels up to the supplies are blocked. The ADG1519 exhibits break-before-make switching action for use in multiplexer applications.

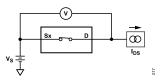

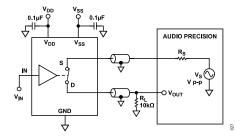

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

#### **PRODUCT HIGHLIGHTS**

- **1.** 5.2  $\Omega$  maximum on resistance at 25°C.

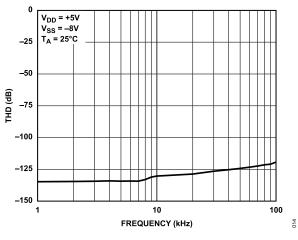

- 2. -135 dB THD.

- 3 V logic-compatible digital inputs: V<sub>INH</sub> = 2.0 V minimum and V<sub>INL</sub> = 0.8 V maximum.

- 4. No logic power supply voltage (V<sub>L</sub>) required.

- 8-lead, 2 mm × 3 mm LFCSP (see the Outline Dimensions section).

Rev. 0

DOCUMENT FEEDBACK

TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | .1 |

| Functional Block Diagram                    | .1 |

| Product Highlights                          | 1  |

| Specifications                              | 3  |

| Dual Supply                                 | 3  |

| Continuous Current Per Channel, Sx or D     | 4  |

| Absolute Maximum Ratings                    | 5  |

| Thermal Resistance                          | 5  |

| ESD Caution                                 | .5 |

| Pin Configuration and Function Descriptions | 6  |

# **REVISION HISTORY**

1/2022—Revision 0: Initial Version

| Typical Performance Characteristics | 7  |

|-------------------------------------|----|

| Test Circuits                       | 10 |

| Terminology                         | 12 |

| THD                                 | 12 |

| Applications Information            | 14 |

| Power Amplifier Gate Drive          | 14 |

| Power Supply Rails                  | 14 |

| Power Supply Recommendations        |    |

| Outline Dimensions                  | 15 |

| Ordering Guide                      | 15 |

| Evaluation Boards                   |    |

# SPECIFICATIONS

# DUAL SUPPLY

$V_{DD}$  = +5 V  $\pm$  10%,  $V_{SS}$  = –4.5 V to –8.8 V, and GND = 0 V, unless otherwise noted.

Table 1.

| Parameter                                                                      | 25°C  | –40°C to +85°C | -40°C to +125°C                    | Unit   | Test Conditions/Comments                                                                                                                                  |

|--------------------------------------------------------------------------------|-------|----------------|------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                                                  |       |                |                                    |        | V <sub>DD</sub> = +4.5 V, V <sub>SS</sub> = -7.2 V                                                                                                        |

| Analog Signal Range                                                            |       |                | V <sub>DD</sub> to V <sub>SS</sub> | V      |                                                                                                                                                           |

| On Resistance, R <sub>ON</sub>                                                 | 3.8   |                |                                    | Ω typ  | $V_{S} = V_{SS}$ to $V_{DD}$ , $I_{S} = -10$ mA, and see Figure 18 <sup>1</sup>                                                                           |

|                                                                                | 5.2   | 6.2            | 7                                  | Ωmax   |                                                                                                                                                           |

| On-Resistance Match Between                                                    | 0.1   | 0.2            | '                                  | Ω typ  | $V_{\rm S} = V_{\rm SS}$ to $V_{\rm DD}$ , $I_{\rm S} = -10 \text{ mA}^{1}$                                                                               |

| Channels, $\Delta R_{ON}$                                                      |       |                |                                    |        | v5 - v55 to vDD, i5 - 10 mint                                                                                                                             |

|                                                                                | 0.3   | 0.35           | 0.4                                | Ω max  |                                                                                                                                                           |

| On-Resistance Flatness, $R_{FLAT (ON)}$                                        | 1.15  |                |                                    | Ω typ  | $V_{\rm S} = V_{\rm SS}$ to $V_{\rm DD}$ , $I_{\rm S} = -10$ mA <sup>1</sup>                                                                              |

|                                                                                | 1.6   | 1.85           | 2                                  | Ωmax   |                                                                                                                                                           |

| LEAKAGE CURRENTS                                                               |       |                |                                    |        | $V_{DD}$ = +5.5 V, $V_{SS}$ = -8.8 V                                                                                                                      |

| Source Off Leakage, $I_S$ (Off)                                                | ±0.1  |                |                                    | nA typ | $V_S$ and $V_D = V_{DD} - 1$ V to $V_{SS} + 1$ V, see Figure 19 <sup>1, 2</sup>                                                                           |

|                                                                                | ±10   | ±12            | ±100                               | nA max |                                                                                                                                                           |

| Drain Off Leakage, $I_D$ (Off)                                                 | ±0.1  |                |                                    | nA typ | $V_S$ and $V_D = V_{DD} - 1$ V to $V_{SS} + 1$ V, see Figure 19 <sup>1, 2</sup>                                                                           |

|                                                                                | ±10   | ±13            | ±140                               | nA max |                                                                                                                                                           |

| Channel On Leakage, $\mathrm{I}_\mathrm{D},\mathrm{I}_\mathrm{S}(\mathrm{On})$ | ±0.1  |                |                                    | nA typ | $V_{\rm S}$ = $V_{\rm D}$ = $V_{\rm DD}$ – 1 V to $V_{\rm SS}$ + 1 V, see<br>Figure 20 <sup>1, 2</sup>                                                    |

|                                                                                | ±10   | ±13            | ±110                               | nA max |                                                                                                                                                           |

| DIGITAL INPUTS                                                                 | - 10  | 10             | 110                                |        |                                                                                                                                                           |

| Input High Voltage, V <sub>INH</sub>                                           |       |                | 2.0                                | V min  |                                                                                                                                                           |

| Input Low Voltage, V <sub>INL</sub>                                            |       |                | 0.8                                | V max  |                                                                                                                                                           |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>                            | 0.001 |                | 0.0                                | µA typ | $V_{IN} = V_{GND}$ or $V_{DD}^3$                                                                                                                          |

| input Guirent, INL of INH                                                      | 0.001 |                | ±0.1                               | μA max | VIN - VGND OI VDD                                                                                                                                         |

| Digital Input Capacitance, C <sub>IN</sub>                                     | 4     |                | ±0.1                               | pF typ |                                                                                                                                                           |

| DYNAMIC CHARACTERISTICS                                                        | 4     |                |                                    | ргтур  | V <sub>DD</sub> = +5 V, V <sub>SS</sub> = -8 V                                                                                                            |

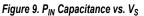

|                                                                                | 240   |                |                                    | no tun | $v_{DD} = +300, v_{SS} = -300$<br>$R_1 = 300 \Omega, C_1 = 35 \text{ pF}^4$                                                                               |

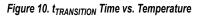

| Transition Time, t <sub>TRANSITION</sub>                                       |       | 265            | 400                                | ns typ | $V_{\rm S} = 3 \text{ V}$ , see Figure 21 <sup>1</sup>                                                                                                    |

|                                                                                | 305   | 365            | 400                                | ns max |                                                                                                                                                           |

| t <sub>ON</sub> (EN)                                                           | 215   | 205            | 000                                | ns typ | $R_L = 300 \Omega, C_L = 35 pF^4$                                                                                                                         |

|                                                                                | 275   | 325            | 360                                | ns max | $V_{\rm S} = 3 V$ , see Figure 23 <sup>1</sup>                                                                                                            |

| t <sub>OFF</sub> (EN)                                                          | 265   |                | 445                                | ns typ | $R_L = 300 \Omega, C_L = 35 pF^4$                                                                                                                         |

|                                                                                | 335   | 380            | 415                                | ns max | $V_{\rm S} = 3 \text{ V}$ , see Figure 23 <sup>1</sup>                                                                                                    |

| Break-Before-Make Time Delay, t <sub>D</sub>                                   | 65    |                |                                    | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF^4$<br>V <sub>SA</sub> = V <sub>SB</sub> = 3 V, see Figure 22 <sup>5</sup>                                               |

|                                                                                |       |                | 38                                 | ns min |                                                                                                                                                           |

| Charge Injection                                                               | 12    |                |                                    | pC typ | $V_{S} = 0 V, R_{S} = 0 \Omega, C_{L} = 1 nF$ , see Figure 24 <sup>1, 4</sup> ,                                                                           |

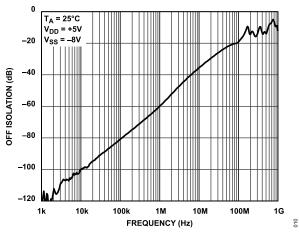

| Off Isolation                                                                  | -60   |                |                                    | dB typ | $\label{eq:RL} \begin{split} R_L &= 50 \; \Omega, \; C_L = 5 \; p\text{F}, \; \text{frequency} = 1 \; \text{MHz}, \\ \text{see Figure } 25^4 \end{split}$ |

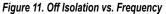

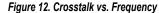

| Channel-to-Channel Crosstalk                                                   | -60   |                |                                    | dB typ | R <sub>L</sub> = 50 Ω, C <sub>L</sub> = 5 pF, frequency = 1 MHz,<br>see Figure 26 <sup>4</sup>                                                            |

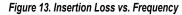

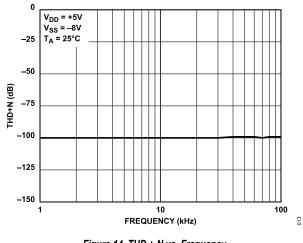

| Total Harmonic Distortion Plus Noise,<br>THD + N                               | 0.001 |                |                                    | % typ  | $R_L$ = 10 kΩ, 5 V p-p, frequency = 20 Hz to<br>20 kHz, see Figure 28 <sup>4</sup>                                                                        |

|                                                                                | -100  |                |                                    | dB typ |                                                                                                                                                           |

| Total Harmonic Distortion, THD                                                 | -135  |                |                                    | dB typ | $R_L = 10 \text{ k}\Omega$ , 5 V p-p, frequency = 1 kHz <sup>4</sup>                                                                                      |

| ,                                                                              | -128  |                |                                    | dB typ | $R_L = 10 \text{ k}\Omega, 5 \text{ V p-p}, \text{ frequency} = 20 \text{ kHz}^4$                                                                         |

|                                                                                | -120  |                |                                    | dB typ | $R_L = 10 \text{ k}\Omega$ , 5 V p-p, frequency = 20 kHz <sup>4</sup>                                                                                     |

|                                                                                | -120  |                |                                    |        | 10  = 10002, 0.000  p-p, 10000000  - 1000012                                                                                                              |

# **SPECIFICATIONS**

#### Table 1.

| Parameter                                | 25°C  | –40°C to +85°C | -40°C to +125°C | Unit    | Test Conditions/Comments                                                            |

|------------------------------------------|-------|----------------|-----------------|---------|-------------------------------------------------------------------------------------|

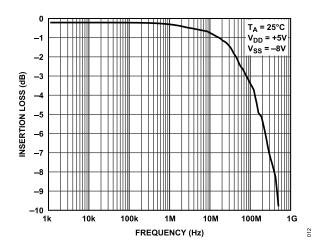

| −3 dB Bandwidth                          | 95    |                |                 | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 27 <sup>4</sup>                       |

| Insertion Loss                           | 0.3   |                |                 | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , frequency = 1 MHz;<br>see Figure 27 <sup>4</sup> |

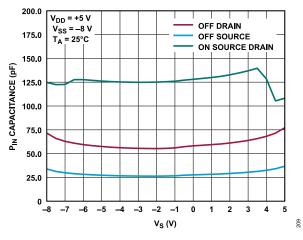

| Source Capacitance, C <sub>S</sub> (Off) | 27    |                |                 | pF typ  | V <sub>S</sub> = 0 V, frequency = 1 MHz <sup>1</sup>                                |

| Drain Capacitance, C <sub>D</sub> (Off)  | 58    |                |                 | pF typ  | V <sub>S</sub> = 0 V, frequency = 1 MHz <sup>1</sup>                                |

| C <sub>D</sub> , C <sub>S</sub> (On)     | 129   |                |                 | pF typ  | V <sub>S</sub> = 0 V, frequency = 1 MHz <sup>1</sup>                                |

| POWER REQUIREMENTS                       |       |                |                 |         | V <sub>DD</sub> = +5.5 V, V <sub>SS</sub> = -8.8 V                                  |

| Positive Supply Current, IDD             | 0.001 |                |                 | µA typ  | Digital inputs = 0 V or V <sub>DD</sub>                                             |

|                                          |       |                | 1.0             | µA max  |                                                                                     |

| Negative Supply Current, I <sub>SS</sub> | 0.001 |                |                 | µA typ  | Digital inputs = 0 V or V <sub>DD</sub>                                             |

|                                          |       |                | 1.0             | µA max  |                                                                                     |

$^1$  V<sub>S</sub> is the analog voltage for Terminal SA or Terminal SB and I<sub>S</sub> is the analog current for Terminal Sx.

$^2~~V_{\rm D}$  is the analog voltage on Terminal D.

$^3~$  V  $_{\rm IN}$  is the IN voltage, and V  $_{\rm GND}$  is the GND voltage.

- <sup>4</sup>  $R_L$  is the load resistance and  $C_L$  is the load capacitance.

- $^5~$  V\_{SA} is the Source A voltage, and V\_{SB} is the Source B voltage.

- $^{\rm 6}~~{\rm R}_{\rm S}$  is the source resistance.

# CONTINUOUS CURRENT PER CHANNEL, SX OR D

| Table 2.                                 |      |      |       |            |                                                    |

|------------------------------------------|------|------|-------|------------|----------------------------------------------------|

| Parameter                                | 25°C | 85°C | 125°C | Unit       | Test Conditions/Comments                           |

| CONTINUOUS CURRENT PER CHANNEL           |      |      |       |            |                                                    |

| Dual Supply                              |      |      |       |            | V <sub>DD</sub> = +4.5 V, V <sub>SS</sub> = -7.2 V |

| 8-Lead LFCSP ( $\theta_{JA}$ = 64.9°C/W) | 310  | 180  | 95    | mA maximum |                                                    |

#### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                                                         | Rating                                                                |  |  |

|-------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|

| V <sub>DD</sub> to V <sub>SS</sub>                                | 18 V                                                                  |  |  |

| V <sub>DD</sub> to GND                                            | –0.3 V to +16.5 V                                                     |  |  |

| V <sub>SS</sub> to GND                                            | +0.3 V to -16.5 V                                                     |  |  |

| Analog Inputs <sup>1</sup>                                        | $V_{SS}$ – 0.3 V to $V_{DD}$ + 0.3 V or 30 mA, whichever occurs first |  |  |

| Digital Inputs <sup>1</sup>                                       | $GND - 0.3$ V to $V_{DD} + 0.3$ V or 30 mA, whichever occurs first    |  |  |

| Peak Current, Sx or D (Pulsed at 1 ms, 10%<br>Duty-Cycle Maximum) | 600 mA                                                                |  |  |

| Continuous Current per Channel, Sx or D                           | Data in Table 2 + 15% mA                                              |  |  |

| Temperature                                                       |                                                                       |  |  |

| Operating Range                                                   | -40°C to +125°C                                                       |  |  |

| Storage Range                                                     | –65°C to +150°C                                                       |  |  |

| Junction                                                          | 150°C                                                                 |  |  |

| Reflow Soldering Peak, Pb Free                                    | JEDEC-J-STD-020                                                       |  |  |

| Peak Temperature                                                  | 260°C                                                                 |  |  |

<sup>1</sup> Over voltages at IN, Sx, or D are clamped by internal diodes. Limit the current to the maximum ratings given.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure, and  $\theta_{JC}$  is the junction-to-case thermal resistance.

#### Table 4. Thermal Resistance

| Package Type <sup>1</sup> | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|---------------------------|-----------------|-----------------|------|

| CP-8-31                   | 64.90           | 14.31           | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with four thermal vias. See JEDEC JESD-51.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

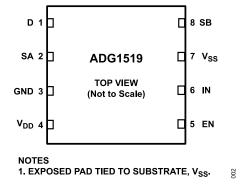

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 5. Pin Function Descriptions

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                      |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | D               | Drain Terminal. The D pin can be an input or output.                                                                                                                                                             |

| 2       | SA              | Source Terminal. The SA pin can be an input or output.                                                                                                                                                           |

| 3       | GND             | Ground (0 V) Reference.                                                                                                                                                                                          |

| 4       | V <sub>DD</sub> | Most Positive Power Supply Potential. Decouple the V <sub>DD</sub> pin using a 0.1 µF capacitor to GND.                                                                                                          |

| 5       | EN              | Active High Digital Input. When the EN pin is low, the device is disabled, and the SA, SB, and D terminals are high impedance. When the EN pin is high, the IN logic input determines which switch is turned on. |

| 6       | IN              | Logic Control Input.                                                                                                                                                                                             |

| 7       | V <sub>SS</sub> | Most Negative Power Supply Potential. Decouple the V <sub>SS</sub> pin using a 0.1 µF capacitor to GND.                                                                                                          |

| 8       | SB              | Source Terminal. The SB pin can be an input or output.                                                                                                                                                           |

| 0       | EPAD            | Exposed Pad. Exposed pad tied to substrate, V <sub>SS</sub> .                                                                                                                                                    |

#### Table 6. Truth Table

| EN | IN             | D              |

|----|----------------|----------------|

| 0  | X <sup>1</sup> | High impedance |

| 1  | 0              | SA             |

| 1  | 1              | SB             |

<sup>1</sup> X means don't care.

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

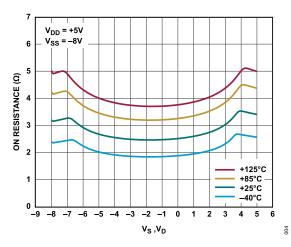

Figure 3. On Resistance as a Function of  $V_S$  and  $V_D$

Figure 4. On Resistance as a Function of V<sub>S</sub> and V<sub>D</sub> for Different Temperatures

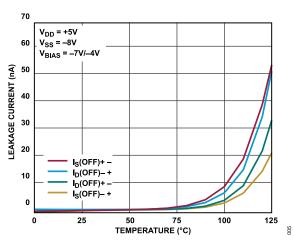

Figure 5. Off Leakage as a Function of Temperature

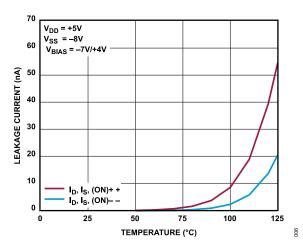

Figure 6. On Leakage as a Function of Temperature

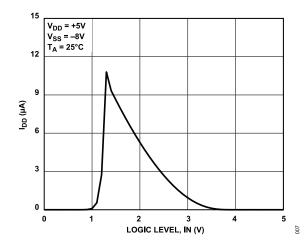

Figure 7. I<sub>DD</sub> vs. Logic Level, IN

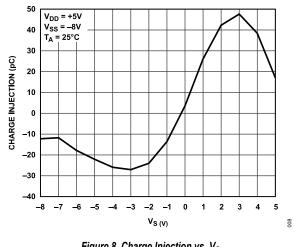

Figure 8. Charge Injection vs. V<sub>S</sub>

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 14. THD + N vs. Frequency

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

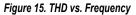

Figure 16. THD Fast Fourier Transform (FFT)

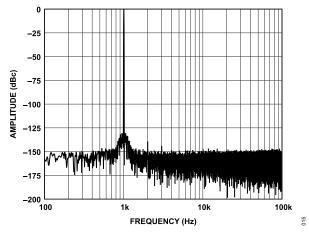

Figure 17. AC Power Supply Rejection Ratio (PSRR) vs. Frequency

# ADG1519

#### **TEST CIRCUITS**

Figure 20. On Leakage

Figure 18. On Resistance (IDS Is the Drain to Source Current.)

Figure 19. Off Leakage

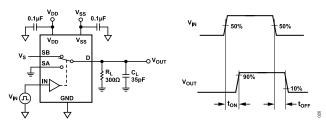

Figure 21. Switching Times, t<sub>ON</sub> and t<sub>OFF</sub> (V<sub>OUT</sub> Is the Output Voltage.)

Figure 22. Break-Before-Make Time Delay

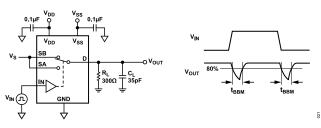

Figure 23. Enable Delay, t<sub>ON</sub> (EN), t<sub>OFF</sub> (EN)

Figure 24. Charge Injection

analog.com

# **TEST CIRCUITS**

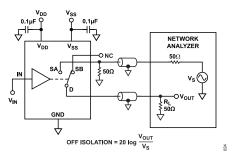

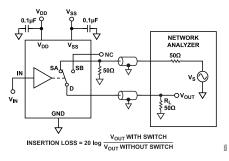

Figure 25. Off Isolation

CHANNEL-TO-CHANNEL CROSSTALK = 20 log  $\frac{V_{OUT}}{V_S}$

Figure 26. Channel-to-Channel Crosstalk

026

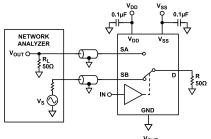

Figure 27. Bandwidth

Figure 28. THD and THD + N

# TERMINOLOGY

# I<sub>DD</sub>

The positive supply current.

# I<sub>SS</sub>

The negative supply current.

# $V_D$ and $V_S$

The analog voltage on Terminal D and Terminal S.

# R<sub>ON</sub>

The ohmic resistance between Terminal D and Terminal S.

# R<sub>FLAT ON</sub>

Flatness is defined as the difference between the maximum and minimum value of on resistance as measured over the specified analog signal range.

# I<sub>S</sub> Off

The source leakage current with the switch off.

# I<sub>D</sub> Off

The drain leakage current with the switch off.

# $I_D$ and $I_S$ On

The channel leakage current for Terminal D and Terminal S with the switch on.

# VINL

The maximum input voltage for Logic 0.

# V<sub>INH</sub>

The minimum input voltage for Logic 1.

# $I_{\rm INL}$ and $I_{\rm INH}$

The input high and low current of the digital input.

# C<sub>S</sub> Off

The off switch source capacitance, measured with reference to ground.

# C<sub>D</sub> Off

The off switch drain capacitance, measured with reference to ground.

# C<sub>D</sub> and C<sub>S</sub> On

The on switch capacitance for Terminal D and Terminal S, measured with reference to ground.

# CIN

The digital input capacitance.

# t<sub>ON</sub> EN

Delay time between the 50% and 90% points of the digital input and switch on condition. See Figure 23.

# t<sub>OFF</sub> EN

Delay time between the 50% and 90% points of the digital input and switch off condition. See Figure 23.

#### **t**TRANSITION

Delay time between the 50% and 90% points of the digital inputs and the switch on condition when switching from one address state to another.

# TD

Off time measured between the 80% point of both switches when switching from one address state to another. See Figure 22.

# **Charge Injection**

A measure of the glitch impulse transferred from the digital input to the analog output during switching. See Figure 24.

# Off Isolation

A measure of unwanted signal coupling through an off switch. See Figure 25.

#### Crosstalk

A measure of unwanted signal that is coupled through from one channel to another as a result of parasitic capacitance. See Figure 26.

#### Bandwidth

The frequency at which the output is attenuated by 3 dB. See Figure 27.

#### Insertion Loss

The loss due to the on resistance of the switch. See Figure 27.

# THD + N

The ratio of the harmonic amplitude plus noise of the signal to the fundamental. See Figure 28.

#### THD

THD is the ratio of the sum of the powers of all harmonic components to the power of the fundamental frequency. See Figure 28.

#### TERMINOLOGY

#### AC PSRR

AC PSRR measures the ability of a device to avoid coupling noise and spurious signals that appear on the supply voltage pin to the output of the switch. The dc voltage on the device is modulated by a sine wave of 0.62 V p-p. The ratio of the amplitude of the signal on the output to the amplitude of the modulation is the AC PSRR. See Figure 17.

#### **APPLICATIONS INFORMATION**

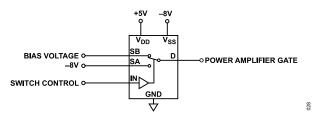

#### POWER AMPLIFIER GATE DRIVE

Figure 29 shows a typical application where the ADG1519 is used to set the gate bias voltage for an RF power amplifier for communications applications. The asymmetrical dual supply and rail-to-rail operation of the ADG1519 allows for negative voltages of up to -8 V for biasing gallium nitride (GaN) power amplifiers while the positive +5 V rail is ideal for laterally diffused metal-oxide semiconductor (LDMOS) power amplifiers.

Figure 29. GaN Power Amplifier Gate Drive

#### POWER SUPPLY RAILS

To guarantee correct operation of the ADG1519, 0.1  $\mu$ F decoupling capacitors are required on the V<sub>DD</sub> and V<sub>SS</sub> pins.

The ADG1519 can operate with asymmetrical bipolar supplies between of V<sub>DD</sub> = +5 V ± 10% and V<sub>SS</sub> = -4.5 V to -8.8 V. The supplies on V<sub>DD</sub> and V<sub>SS</sub> do not have to be asymmetrical. However, the V<sub>DD</sub> to V<sub>SS</sub> range must not exceed 18 V as stated in the Absolute Maximum Ratings section.

#### POWER SUPPLY RECOMMENDATIONS

Analog Devices, Inc., has a wide range of power management products to meet the requirements of most high performance signal chains.

An example of an asymmetrical bipolar power solution is shown in Figure 30. The ADP5070 (dual switching regulator) generates a positive and negative supply rail for the ADG1519. Also shown in Figure 30 are two optional low dropout regulators (LDOs), the ADP7118 and ADP7182 positive and negative LDOs, respectively, that can be used to reduce the output ripple of the ADP5070 in ultralow noise sensitive applications.

Figure 30. Bipolar Power Solution

#### Table 7. Recommended Power Management Devices

| Product | Description                                                                                     |

|---------|-------------------------------------------------------------------------------------------------|

| ADP5070 | 1 A/0.6 A, dc-to-dc switching regulator with independent positive<br>and negative outputs       |

| ADP7118 | 20 V, 200 mA, low noise, complementary metal oxide<br>semiconductor (CMOS) LDO linear regulator |

| ADP7182 | -28 V, -200 mA, low noise, LDO linear regulator                                                 |

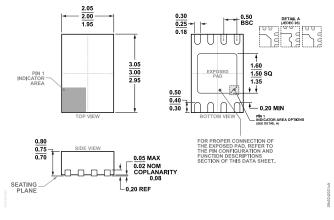

# **OUTLINE DIMENSIONS**

Figure 31. 8-Lead Lead Frame Chip Scale Package [LFCSP] 2 mm × 3 mm Body and 0.75 mm Package Height (CP-8-31) Dimensions shown in millimeters

Updated: January 15, 2022

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description      | Packing Quantity | Package<br>Option | Marking Code |

|--------------------|-------------------|--------------------------|------------------|-------------------|--------------|

| ADG1519BCPZ-RL7    | -40°C to +125°C   | LFCSP:LEADFRM CHIP SCALE | Reel, 3000       | CP-8-31           | S59          |

<sup>1</sup> Z = RoHS Compliant Part.

#### **EVALUATION BOARDS**

| Table 8.           |                  |

|--------------------|------------------|

| Model <sup>1</sup> | Description      |

| EVAL-ADG1519EBZ    | Evaluation Board |

<sup>1</sup> Z = RoHS-Compliant Part.