# AN-802 APPLICATION NOTE

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106 • Tel: 781/329-4700 • Fax: 781/461-3113 • www.analog.com

# ADG794—A 2.5 V Input Signal Range Switching Solution for HDTV

by Ferenc Barany

#### INTRODUCTION

The introduction of digital video has revolutionized the consumer market over the last few years. New technology has enabled the design and production of low cost, high quality equipment for capture, storage, transmission, and display of video signals. The new standards and interfaces associated with high definition TV signals have increased the number of signals per source and the bandwidth requirements. Compared with the 4 MHz to 6 MHz bandwidth required for composite video (CVBS) signals, the bandwidth required for HDTV can reach hundreds of MHz depending on resolution, vertical refresh rate, and scanning mode (progressive or interlaced). Also, in order to be able to switch between more and more video sources, larger switch arrays are required.

Switch designers have responded to this trend by changing the architecture of the switch cell to meet the high bandwidth and the large number of channel requirements. This application note describes different switch architectures and examines the performance of commonly used video switches; a brief description of the ADG794 HDTV video switch is also included.

#### THE CMOS SWITCH

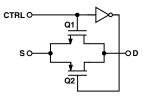

Traditional analog switches consist of two MOS transistors connected in parallel, as shown in Figure 1.

Figure 1. Simplified Schematic of a CMOS Switch

When the CTRL pin is driven with a HIGH logic level, both  $\Omega1$  and  $\Omega2$  will be turned ON allowing the signal applied to either S or D pins to pass through the structure. When a LOW logic level is applied to the CTRL pin the structure will act like a switch in the OFF position.

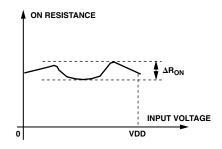

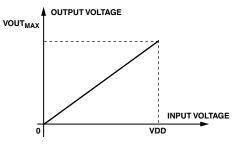

The main advantages offered by the CMOS switch are the relatively flat on resistance profile ( $\Delta R_{ON}$  in Figure 2) and rail-to-rail operation that allows the switch to pass or block input signals whose amplitude is less than or equal to the power supply voltage as shown in Figure 3. Signal distortion is minimized by keeping the absolute value of switch on resistance and the flatness of the resistance characteristic over the input signal range as low as possible.

Figure 2. On Resistance Profile of a CMOS Switch

Figure 3. Transfer Function of a CMOS Switch

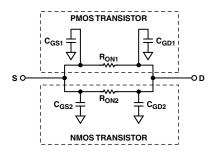

The main disadvantage of the CMOS switching cell is its reduced bandwidth due to an increased parasitic capacitance at the source and drain (S, D) pins. The small signal equivalent circuit of a CMOS switch is shown in Figure 4.

Figure 4. Small Signal Equivalent Circuit

Higher bandwidths can be achieved by reducing the on resistance and the parasitic capacitance at the source and drain pins.

## THE NMOS SWITCH

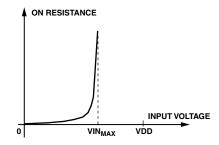

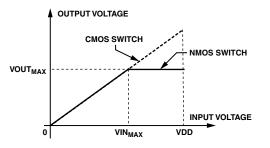

The NMOS transistors have an inherently higher bandwidth than the PMOS transistors, so the simplest way to increase the bandwidth of a CMOS switch is to remove the PMOS transistor and transform the CMOS switch into an NMOS only switch. This will lower the parasitic capacitance and reduce the physical size of the switch cell, allowing more switches per unit area. A typical on resistance profile and transfer function is shown in Figure 5 and Figure 6.

Figure 5. On Resistance Profile of a NMOS Switch

Figure 6. Transfer Function of a NMOS Switch

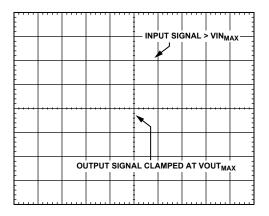

Figure 6 illustrates the input signal range of an NMOS switch compared to a CMOS switch. The input range is reduced from VDD to VIN<sub>MAX</sub> when an NMOS only switch is employed. If the voltage applied to the switch exceeds VIN<sub>MAX</sub>, the NMOS transistor will turn off and clamp the output voltage to the VOUT<sub>MAX</sub> level as shown in Figure 7.

Figure 7. Output Signal Clamping Effect

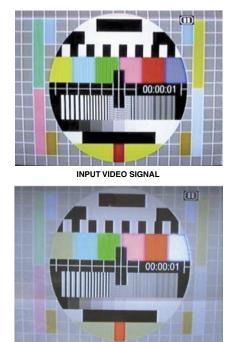

When a video signal is applied to the switch and its peakto-peak amplitude exceeds  $VIN_{MAX}$ , the clamping will alter both the luminance and chrominance components. For the luminance component, the resolution of the image will be reduced by limiting the maximum number of luminance levels that can be displayed. The alteration of the chrominance component will affect the saturation of the colors, or even wrong colors may be displayed. This effect is illustrated in Figure 8.

CLAMPED OUTPUT VIDEO SIGNAL

Figure 8. Clamping Effect on the Output Video Signal

To avoid distortion due to clamping, the signal range of the switch must be large enough to pass the maximum expected input signal. This last point is very important because most of the video switches available on the market have an input signal range of 0 V to 2 V. This is not sufficient to meet the needs of all sources given that video signals can vary in amplitude from 0.7 V p-p to 2.5 V p-p. The unique architecture of the ADG794 overcomes this limitation by providing an extended input signal range of 2.5 V while preserving the high bandwidth required for HDTV applications.

## ADG794-HDTV VIDEO SWITCH

The ADG794 video switch from Analog Devices consists of four SPDT (single-pole double throw) in a compact, 16-lead QSOP package. The operation of the switches is controlled using a 2-bit parallel interface available at the IN and  $\overline{\text{EN}}$  pins. The logic level applied to the IN pin will control which input is selected, and the  $\overline{\text{EN}}$  pin enables or disables all switches, allowing the user to connect more ADG794s in parallel for larger switching arrays.

The following are the main features of the ADG794:

- Input signal range: 0 V to 2.5 V (for 5 V supply)

- Bandwidth: 300 MHz (typical)

- On resistance: 5  $\Omega$  (typical)

- On resistance flatness: 0.68  $\Omega$

- Supply voltage: 3 V or 5 V

- Quiescent current: 1 μA max

- Off isolation: -65 dB (typical)

- Channel-to-channel crosstalk: -70 dB (typical)

- Fast switching times: t<sub>ON</sub> = 7 ns, t<sub>OFF</sub> = 5 ns

The full version of the ADG794 data sheet is available online at www.analog.com.

The high bandwidth and the extended input voltage range of the ADG794 allows the device to be used in video switching applications where the signal amplitudes can be as high as 2.5 V without introducing clamping distortions.

#### CONCLUSION

Apart from bandwidth, power consumption, and package size, the input signal range of a video switch should be carefully considered when designing high performance video switches. The ADG794 provides a cost-effective solution for high performance video switches due to its high bandwidth, low power, and extended input signal range.

AN05634-0-7/05(0)