|     | REVISIONS   |      |          |  |  |  |  |  |

|-----|-------------|------|----------|--|--|--|--|--|

| LTR | DESCRIPTION | DATE | APPROVED |  |  |  |  |  |

|     |             |      |          |  |  |  |  |  |

| Prepared   | l in accor            | dance | with A | SME Y           | 14.24                                |       |       |     |   |                                                                                                                        |                                                                                     |       |       |       |      |           | Ve     | ndor it | em dra | awing |  |

|------------|-----------------------|-------|--------|-----------------|--------------------------------------|-------|-------|-----|---|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|------|-----------|--------|---------|--------|-------|--|

| REV        |                       |       |        |                 |                                      |       |       |     |   |                                                                                                                        |                                                                                     |       |       |       |      |           |        |         |        |       |  |

| PAGE       |                       |       |        |                 |                                      |       |       |     |   |                                                                                                                        |                                                                                     |       |       |       |      |           |        |         |        |       |  |

| REV        |                       |       |        |                 |                                      |       |       |     |   |                                                                                                                        |                                                                                     |       |       |       |      |           |        |         |        |       |  |

| PAGE       |                       |       |        |                 |                                      |       |       |     |   |                                                                                                                        |                                                                                     |       |       |       |      |           |        |         |        |       |  |

| REV STA    | ATUS                  | F     | REV    | •               |                                      |       |       |     |   |                                                                                                                        |                                                                                     |       |       |       |      |           |        |         |        |       |  |

| OF PAGI    | ES                    | F     | PAGE   |                 | 1                                    | 2     | 3     | 4   | 5 | 6                                                                                                                      | 7                                                                                   | 8     | 9     | 10    | 11   | 12        | 13     | 14      | 15     | 16    |  |

| PMIC N/A   | 4                     |       |        |                 | ED BY<br>FFICEI                      |       |       |     |   |                                                                                                                        | DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 https://www.dla.mil/LandandMaritime |       |       |       |      | <u>ne</u> |        |         |        |       |  |

| Original o | date of dr<br>Y-MM-DE |       |        | HECKE<br>Rajesi | E <b>D BY</b><br>H PITH.             | ADIA  |       |     |   |                                                                                                                        | TITI                                                                                |       | יוםרו | IIT I | INIE | \D 5      | : 7 L\ | / DN//  | S S10  | ZNIAI |  |

| 1          | 19-05-24              |       |        |                 | <b>APPROVED BY</b><br>CHARLES F. SAF |       |       |     |   | <ul> <li>MICROCIRCUIT, LINEAR, 5.7 kV RMS, SIGNATISOLATED, BASIC CAN FD TRANSCEIVER,<br/>MONOLITHIC SILICON</li> </ul> |                                                                                     |       |       |       | •    |           |        |         |        |       |  |

|            |                       |       |        | SIZE            | COL                                  | E IDE | NT. N | Ο.  |   |                                                                                                                        | DWC                                                                                 | S NO. |       |       |      |           |        |         |        |       |  |

|            |                       |       |        | Α               |                                      |       | 162   | 236 |   |                                                                                                                        |                                                                                     |       |       | \     | /62  | /19       | 60     | 5       |        |       |  |

|            |                       |       | RI     | EV              | I                                    |       |       |     |   |                                                                                                                        | PAG                                                                                 | E 1   | OF    | 16    |      |           |        |         |        |       |  |

DISTRIBUTION STATEMENT A. Approved for public release. Distribution is unlimited.

AMSC N/A 5962-V050-19

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 5.7 kV rms, signal isolated basic controlled area network flexible data rate (CAN FD) transceiver, microcircuit, with an operating temperature range of -55°C to +125°C.

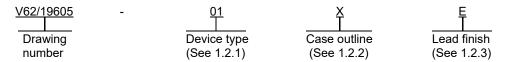

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

1.2.1 Device type(s).

Device type

Generic

Circuit function

01

ADM3050E-EP

5.7 kV rms, signal isolated basic CAN FD transceiver

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95 | Package style         |

|----------------|----------------|--------------|-----------------------|

| Χ              | 16             | MS-013-AA    | Small outline package |

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator | <u>Material</u>          |

|-------------------|--------------------------|

| Α                 | Hot solder dip           |

| В                 | Tin-lead plate           |

| С                 | Gold plate               |

| D                 | Palladium                |

| E                 | Gold flash palladium     |

| F                 | Tin-lead alloy (BGA/CGA) |

| Z                 | Other                    |

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 2           |

# 1.3 Absolute maximum ratings. 1/2/

| Supply voltage range (VDD1/VDD2)                                                                     |                                       |

|------------------------------------------------------------------------------------------------------|---------------------------------------|

| Logic side input/output: TXD, RXD                                                                    |                                       |

| CANH, CANL                                                                                           | 40 V to +40 V                         |

| Storage temperature range (TSTG)                                                                     | 65°C to +150°C                        |

| Junction temperature range (TJ)<br>Electrostatic discharge (ESD) rating:<br>IEC 61000-4-2, CANH/CANL | 150°C maximum                         |

| Across isolation barrier with respect to GND1                                                        | ±8 kV                                 |

| Contact discharge with respect to to GND <sub>2</sub>                                                | ±8 kV typical                         |

| Air discharge with respect to GND2                                                                   | ±15 kV                                |

| Human body model (HDM) all pins, 1.5 kΩ, 100 pF                                                      | ±4 kV                                 |

| Moisture sensitivity level (MSL)                                                                     | MSL3                                  |

| Thermal resistance, junction to ambient (θJA)                                                        | 60°C/W                                |

| 1.4 Recommended operating conditions. 3/                                                             |                                       |

| Supply voltage range:                                                                                |                                       |

| (VDD1)                                                                                               | 1.7 V to 5.5 V                        |

| (VDD2)                                                                                               | 4.5 V to 5.5 V                        |

| Operating free-air temperature range (TA)                                                            | 55°C to +125°C                        |

| 1.5 Package characteristics.                                                                         |                                       |

| Resistance (input to output) (RI-O)                                                                  | 10 <sup>13</sup> Ω typical <u>4</u> / |

| Capacitance (input to output) (CI-O) with f = 1 MHz                                                  |                                       |

| Input capacitance (CI)                                                                               |                                       |

| iliput capacitatice (Ci)                                                                             | 4.0 pr typical <u>5</u> /             |

<sup>5/</sup> Input capacitance is from any input data pin to ground.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 3           |

Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2/</sup> Unless otherwise specified, pin voltage with respect to GND1/GND2 are on the same side.

Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

<sup>4/</sup> The device is considered a 2-terminal device: pin 1 through pin 8 are shorted together, and pin 9 through pin 16 are shorted together.

### 2. APPLICABLE DOCUMENTS

International Electrotechnical Commission

IEC 61000-4-2 – Electromagnetic Compatibility (EMC) - Part 4-2:

Testing and measurement techniques - Electrostatic discharge immunity test

(Copies of these documents are available online at https://www.iec.ch.)

JEDEC Solid State Technology Association

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at <a href="https://www.jedec.org">https://www.jedec.org</a>.)

## 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

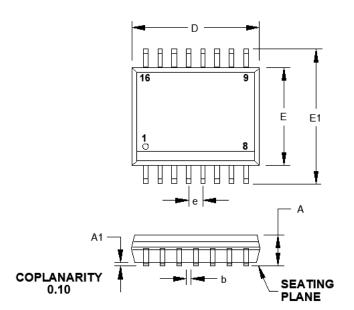

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

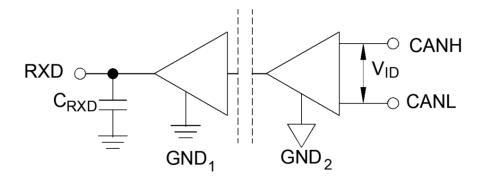

- 3.5.2 Terminal connections. The terminal connections shall be as shown in figure 2.

- 3.5.3 Truth table. The truth table shall be as shown in figure 3.

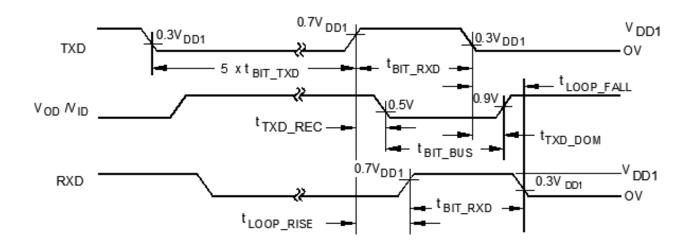

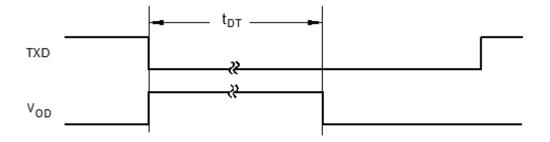

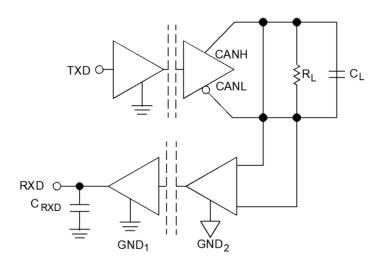

- 3.5.4 Timing waveforms and test circuit. The timing waveforms and test circuit shall be as shown in figures 4 through 8.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 4           |

TABLE I. Electrical performance characteristics. 1/

| Test                        | Test Symbol      |                                                                          | Conditions <u>2</u> / Temperature, |              |            |        | Unit |

|-----------------------------|------------------|--------------------------------------------------------------------------|------------------------------------|--------------|------------|--------|------|

|                             |                  |                                                                          |                                    |              | Min        | Max    |      |

| Supply current              | ·                |                                                                          | •                                  |              |            |        |      |

| Bus side                    | I <sub>DD2</sub> |                                                                          |                                    |              |            |        |      |

| Recessive state             |                  | TXD high,                                                                | +25°C                              | 01           | 5.3 ty     | ypical | mA   |

|                             |                  | load resistance (RL) = $60 \Omega$                                       | -55°C to +125°C                    |              |            | 7      |      |

| Dominant state I            |                  | Limited by transmit dominant                                             | +25°C                              | 01           | 63 typical |        | mA   |

|                             |                  | timeout (tDT), RL = $60 \Omega$                                          | -55°C to +125°C                    |              |            | 75     |      |

|                             |                  | Limited by (tDT), RL = 60 $\Omega$ ,<br>4.75 V $\leq$ VDD2 $\leq$ 5.25 V | -55°C to +125°C                    |              |            | 73     |      |

| 70% dominant /              |                  | 1 Mbps, worst case, RL = $60 \Omega$                                     | +25°C                              | 01           | 45 ty      | /pical | mA   |

| 30% recessive               |                  |                                                                          | -55°C to +125°C                    | <del>-</del> |            | 58     |      |

|                             |                  | 5 Mbps, worst case, RL = $60 \Omega$                                     | +25°C                              |              | 49 ty      | /pical |      |

|                             |                  |                                                                          | -55°C to +125°C                    |              |            | 60     |      |

|                             |                  | 12 Mbps, worst case, RL = $60 \Omega$                                    | +25°C                              |              | 58 ty      | /pical |      |

|                             |                  |                                                                          | -55°C to +125°C                    | 1            |            | 65     |      |

| Logic side icoupler current | IDD1             | TXD high, low, or switching                                              | -55°C to +125°C                    | 01           |            | 5.5    | mA   |

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |  |

|                       |          | REV            | PAGE 5           |  |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                          | Symbol          | Conditions 2/                     | Temperature,                 | Device<br>type | Lin   | nits  | Unit |

|-----------------------------------------------|-----------------|-----------------------------------|------------------------------|----------------|-------|-------|------|

|                                               |                 |                                   | 10                           |                | Min   | Max   |      |

| Driver                                        |                 |                                   | ·                            |                |       |       |      |

| Differential outputs                          |                 | See figure 4                      |                              |                |       |       |      |

| Recessive state voltage.                      |                 | TXD high, RL and common mode      | e filter capacitor (CF) oper | 1              |       |       |      |

| CANH, CANL voltage                            | VCANL,<br>VCANH |                                   | -55°C to +125°C              | 01             | 2.0   | 3.0   | V    |

| Differential output voltage                   | VOD             |                                   | -55°C to +125°C              | 01             | -500  | +50   | mV   |

| Dominant state voltage.                       |                 | TXD low, CF open                  |                              |                |       |       |      |

| CANH voltage                                  | VCANH           | $50~\Omega \le R_L \le 65~\Omega$ | -55°C to +125°C              | 01             | 2.75  | 4.5   | V    |

| CANL voltage                                  | VCANL           | $50~\Omega \le R_L \le 65~\Omega$ | -55°C to +125°C              | 01             | 0.5   | 2.0   | V    |

| Differential output voltage                   | Vod             | $50~\Omega \le R_L \le 65~\Omega$ | -55°C to +125°C              | 01             | 1.5   | 3.0   | V    |

| voltage                                       |                 | $45~\Omega \le R_L \le 70~\Omega$ |                              |                | 1.4   | 3.3   |      |

|                                               |                 | RL = 2240 Ω                       |                              |                | 1.5   | 5.0   |      |

| Output symmetry<br>(VDD2 – VCANH to<br>VCANL) | Vsym            | RL = 60 Ω, CF = 4.7 nF            | -55°C to +125°C              | 01             | -0.55 | +0.55 | V    |

| Short circuit current                         | Isc             | RL open                           |                              |                |       |       |      |

| Absolute CANH                                 |                 | VCANH = -3 V                      | -55°C to +125°C              | 01             |       | 115   | mA   |

| Absolute CANL                                 |                 | VCANL = 18 V                      | -55°C to +125°C              | 01             |       | 115   | mA   |

| Steady state CANH                             |                 | VCANH = -24 V                     | -55°C to +125°C              | 01             |       | 115   | mA   |

| Steady state CANL                             |                 | VCANL = 24 V                      | -55°C to +125°C              | 01             |       | 115   | mA   |

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 6           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                                                | Symbol         | Conditions 2/                             | Temperature,         | Device<br>type | Lir            | nits           | Unit |

|---------------------------------------------------------------------|----------------|-------------------------------------------|----------------------|----------------|----------------|----------------|------|

|                                                                     |                |                                           |                      |                | Min            | Max            |      |

| Driver - continued                                                  |                |                                           |                      | •              | •              | •              | •    |

| Logic inputs (TXD)                                                  |                |                                           |                      |                |                |                |      |

| Input voltage, high                                                 | VIH            |                                           | -55°C to +125°C      | 01             | 0.65 x<br>VDD1 |                | V    |

| Input voltage, low                                                  | VIL            |                                           | -55°C to +125°C      | 01             |                | 0.35 x<br>VDD1 | V    |

| Complementary metal oxide semiconductor (CMOS) logic input currents | lih ,<br> liL  | Input high or low                         | -55°C to +125°C      | 01             |                | 10             | μА   |

| Receiver                                                            |                |                                           |                      |                |                |                |      |

| Differential inputs                                                 |                |                                           |                      |                |                |                |      |

| Differential input voltage range                                    | VID            | RXD capacitance (CRXD) open, see          | figure 5, -25 V < VC | ANL, VCAN      | NH < +25 \     | /              |      |

| Recessive                                                           |                |                                           | -55°C to +125°C      | 01             | -1.0           | +0.5           | V    |

| Dominant                                                            |                |                                           | -55°C to +125°C      | 01             | 0.9            | 5.0            | V    |

| Input voltage hysteresis                                            | VHYS           |                                           | +25°C                | 01             | 150 t          | ypical         | mV   |

| Unpowered input leakage current                                     | lin(off)       | VCANH, VCANL = 5 V, VDD2 = 0 V            | -55°C to +125°C      | 01             |                | 10             | μА   |

| Input resistance,<br>CANH, CANL                                     | RINH,<br>RINL  |                                           | -55°C to +125°C      | 01             | 6              | 25             | kΩ   |

| Input resistance,<br>differential                                   | RDIFF          |                                           | -55°C to +125°C      | 01             | 20             | 100            | kΩ   |

| Input resistance,<br>matching                                       | m <sub>R</sub> | MR = 2 x (RINH – RINL) /<br>(RINH + RINL) | -55°C to +125°C      | 01             | -0.03          | +0.03          | Ω/Ω  |

| Input capacitance,<br>CANH, CANL                                    | CINH,<br>CRINL |                                           | +25°C                | 01             | 35 ty          | /pical         | pF   |

| Differential input capacitance                                      | CDIFF          |                                           | +25°C                | 01             | 12 ty          | /pical         | pF   |

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |  |

|                       |          | REV            | PAGE 7           |  |

TABLE I. <u>Electrical performance characteristics</u> – Continued.  $\underline{1}/$

| Test                        | Symbol       | Conditions 2/                              | Temperature, Device type |            |               |        | nits  | Unit |  |

|-----------------------------|--------------|--------------------------------------------|--------------------------|------------|---------------|--------|-------|------|--|

|                             |              |                                            |                          |            | Min           | Max    |       |      |  |

| Receiver – continued.       |              |                                            |                          |            |               |        |       |      |  |

| Logic outputs (RXD)         |              |                                            |                          |            |               |        |       |      |  |

| Output voltage , low        | VOL          | Output impedance (IOUT) = 2 mA             | +25°C                    | 01         | 0.2 ty        | /pical | V     |      |  |

|                             |              |                                            | -55°C to +125°           |            |               | 0.4    |       |      |  |

| Output voltage, high<br>RXD | Vон          | IOUT = -2 mA                               | -55°C to +125°C          | 01         | VDD1<br>- 0.2 |        | V     |      |  |

| Short circuit current RXD   | los          | Output voltage (VOUT) = GND1 or VDD1       | -55°C to +125°C          | 01         | 7             | 85     | mA    |      |  |

| Common mode transien        | t immunity.  | <u>3</u> / Common mode voltage (VCM) ≥ 1 k | V, transient magnitu     | de ≥ 800 V | ,             |        |       |      |  |

| Input high, recessive       | СМн          | Input voltage (VIN) = VDD1(TXD) or         | +25°C                    | 01         | 100 t         | ypical | kV/μs |      |  |

|                             |              | CANH/CANL recessive                        | -55°C to +125°           |            | 75            |        |       |      |  |

| Input low, dominant         | 101121 11110 |                                            | +25°C                    | 01         | 100 t         | ypical | kV/μs |      |  |

|                             |              | CANH/CANL dominant                         | -55°C to +125°           |            | 75            |        |       |      |  |

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |  |

|                       |          | REV            | PAGE 8           |  |

TABLE I. Electrical performance characteristics - Continued. 1/

| Test                                                   | Symbol          | Conditions 2/                      | Temperature,        | Device<br>type | Lin      | nits   | Unit |

|--------------------------------------------------------|-----------------|------------------------------------|---------------------|----------------|----------|--------|------|

|                                                        |                 |                                    | .,,                 |                | Min      | Max    |      |

| Timing specifications                                  |                 |                                    |                     |                |          | •      |      |

| Driver                                                 | See figure 4 a  | nd figure 6, tBIT_TXD = 200 ns, RL | = 60 Ω, load capaci | tance (CL)     | = 100 pF |        |      |

| Maximum data rate                                      |                 |                                    | -55°C to +125°      | 01             | 12       |        | Mbps |

| Propagation delay from TXD to bus (Recessive           | ttxd_dom        |                                    | +25°C               | 01             | 35 ty    | /pical | ns   |

| to Dominant)                                           |                 |                                    | -55°C to +125°      |                |          | 60     |      |

| Propagation delay from TXD to bus (Dominant            | tTXD_REC        |                                    | +25°C               | 01             | 45 ty    | /pical | ns   |

| to Recessive )                                         |                 |                                    | -55°C to +1205°     |                |          | 70     |      |

| Transmit dominant timeout                              | tDT             | TXD low, see figure 7              | -55°C to +125°      | 01             | 1175     | 4000   | μs   |

| Receiver                                               | See figure 6 ar | nd figure 8, tBIT_TXD = 200 ns, RL | = 60 Ω, CL = 100 pF | , CRXD = 1     | 5 pF     |        |      |

| Falling edge loop<br>propagation delay<br>(TXD to RXD) | tLOOP_FALL      |                                    | -55°C to +125°      | 01             |          | 145    | ns   |

| Falling edge loop<br>propagation delay<br>(TXD to RXD) | tLOOP_RISE      |                                    | -55°C to +125°      | 01             |          | 145    | ns   |

| Loop delay symmetry (minimum recessive                 | tBIT_RXD        | 2 Mbps, tBIT_TXD = 500 ns          | -55°C to +125°      | 01             | 450      | 550    | ns   |

| bit width)                                             |                 | 5 Mbps, tBIT_TXD = 200 ns          |                     |                | 160      | 220    |      |

|                                                        |                 | 8 Mbps, tBIT_TXD = 125 ns          |                     |                | 85       | 140    |      |

|                                                        |                 | 12 Mbps, tBIT_TXD = 83.3 ns        |                     |                | 50       | 91.6   |      |

- 1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- 2/ Unless otherwise specified, all voltages are relative to their respective ground. 1.7 V ≤  $V_{DD1}$  ≤ 5.5 V, 4.5 V ≤  $V_{DD2}$  ≤ 5.5 V, -55°C ≤  $T_A$  ≤ +125°C, and STBY low. Unless otherwise specified, typical specifications are at  $V_{DD1}$  =  $V_{DD2}$  = 5 V and  $V_{DD2}$  = 5 V a

- 3/ |CMH| is the maximum common-mode voltage slew rate that can be sustained while maintaining CANH/CANL recessive, or RXD ≥ V<sub>DD1</sub> 0.2 V. |CML| is the maximum common-mode voltage slew rate that can be sustained while maintaining CANH/CANL dominant, or RXD ≤ 0.4 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |  |

|                       |          | REV            | PAGE 9           |  |

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |  |

|                       |          | REV            | PAGE 10          |  |

|        | Dimensions |         |             |         |  |  |

|--------|------------|---------|-------------|---------|--|--|

| Symbol | Inc        | hes     | Millimeters |         |  |  |

|        | Minimum    | Maximum | Minimum     | Maximum |  |  |

| А      | .0925      | .1043   | 2.35        | 2.65    |  |  |

| A1     | .0039      | .0118   | 0.10        | 0.30    |  |  |

| b      | .0122      | .0201   | 0.31        | 0.51    |  |  |

| С      | .0079      | .0130   | 0.20        | 0.33    |  |  |

| D      | .3976      | .4134   | 10.10       | 10.50   |  |  |

| E      | .2913      | .2992   | 7.40        | 7.60    |  |  |

| E1     | .3937      | .4193   | 10.00       | 10.65   |  |  |

| е      | .0500 BSC  |         | 1.27 BSC    |         |  |  |

| L      | .0157      | .0500   | 0.40        | 1.27    |  |  |

# NOTES:

- Controlling dimensions are millimeter, inch dimensions are given for reference only.

Falls within reference to JEDEC MS-013-AA.

FIGURE 1. <u>Case outline</u> - Continued.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |  |

|                       |          | REV            | PAGE 11          |  |

| Device type     | 01                 |                                                                                                     |  |  |  |

|-----------------|--------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| Case outline    |                    | Х                                                                                                   |  |  |  |

| Terminal number | Terminal<br>symbol | Description                                                                                         |  |  |  |

| 1               | VDD1               | Power supply, logic side, 1.7 V to 5.5 V. This pin requires 0.1 $\mu\text{F}$ decoupling capacitor. |  |  |  |

| 2               | GND1               | Ground, logic side.                                                                                 |  |  |  |

| 3               | RXD                | Receiver output data                                                                                |  |  |  |

| 4               | NC                 | No connect. No internal connection to integrated circuit (IC).                                      |  |  |  |

| 5               | NC                 | No connect. No internal connection to integrated circuit (IC).                                      |  |  |  |

| 6               | TXD                | Driver input data.                                                                                  |  |  |  |

| 7               | GND1               | Ground, logic side.                                                                                 |  |  |  |

| 8               | GND1               | Ground, logic side.                                                                                 |  |  |  |

| 9               | GND <sub>2</sub>   | Ground, bus side.                                                                                   |  |  |  |

| 10              | GND <sub>2</sub>   | Ground, bus side.                                                                                   |  |  |  |

| 11              | NC                 | No connect. No internal connection to integrated circuit (IC).                                      |  |  |  |

| 12              | CANL               | CAN low input and output.                                                                           |  |  |  |

| 13              | CANH               | CAN high input and output.                                                                          |  |  |  |

| 14              | NC                 | No connect. No internal connection to integrated circuit (IC).                                      |  |  |  |

| 15              | GND2               | Ground, bus side.                                                                                   |  |  |  |

| 16              | VDD <sub>2</sub>   | Power supply, bus side, 4.5 V to 5.5 V. This pin requires 0.1 $\mu\text{F}$ decoupling capacitor.   |  |  |  |

FIGURE 2. <u>Terminal connections</u>.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/19605</b> |  |

|                       |      | REV            | PAGE 12          |  |

| V <sub>DD1</sub> | VDD2 | TXD        | Mode            | RXD           | CANH/CANL                 |

|------------------|------|------------|-----------------|---------------|---------------------------|

| On               | On   | Low        | Normal          | Low           | Dominant (limited by tDT) |

| On               | On   | High       | Normal          | High per bus  | Recessive and set by bus  |

| Off              | On   | Don't care | Normal          | Indeterminate | Recessive and set by bus  |

| On               | Off  | Don't care | Transceiver off | High          | High-Z                    |

FIGURE 3. Truth table.

FIGURE 4. Driver voltage measurement.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 13          |

FIGURE 5. Receiver voltage measurement.

FIGURE 6. <u>Transceiver timing diagram</u>.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 14          |

FIGURE 7. Dominant timeout tDT.

FIGURE 8. Switching characteristics measurements.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 15          |

## 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

## 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="https://landandmaritimeapps.dla.mil/programs/smcr/">https://landandmaritimeapps.dla.mil/programs/smcr/</a>.

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Mode of<br>transportation<br>and quantity | Vendor part number |

|------------------------------------------------------|-------------------------------------|-------------------------------------------|--------------------|

| V62/19605-01XE                                       | 24355                               | Tube, 47 units                            | ADM3050ETRWZ-EP    |

|                                                      | 24355                               | Reel, 1000 units                          | ADM3050ETRWZ-EP-RL |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

CAGE code

Source of supply

24355

Analog Devices Route 1 Industrial Park P.O. Box 9106 Norwood, MA 02062

Point of contact: 20 Alpha

Chelmsford, MA 01824

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/19605</b> |

|                       |          | REV            | PAGE 16          |