# K Band Quadrature Demodulator with Integrated Fractional-N PLL and VCO

## **FEATURES**

- ▶ Fractional-N synthesizer with low phase noise VCO

- ▶ K band quadrature demodulator

- ▶ Programmable via 4-wire SPI

- ▶ RF operating frequency range: 17 GHz to 22 GHz

- ▶ LO internal frequency range: 17 GHz to 21.5 GHz

- ▶ Double sideband noise figure: 5 dB at maximum conversion gain

- ▶ Output integrated phase noise, 1 kHz to 10 MHz: <1°

- ▶ Maximum conversion gain of >50 dB

- ► Conversion gain control range of >50 dB

- ▶ IM3 of -54 dBc at -30 dBm composite input level,  $\Delta f_{RF} = 1$  MHz

- ▶ 3 baseband, SPI-selectable LPFs with corner frequencies of: 125 MHz, 250 MHz, and 500 MHz on each baseband path

## **APPLICATIONS**

Satellite communications

## **GENERAL DESCRIPTION**

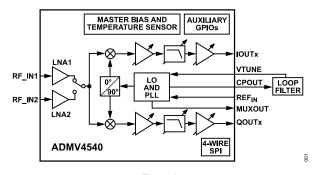

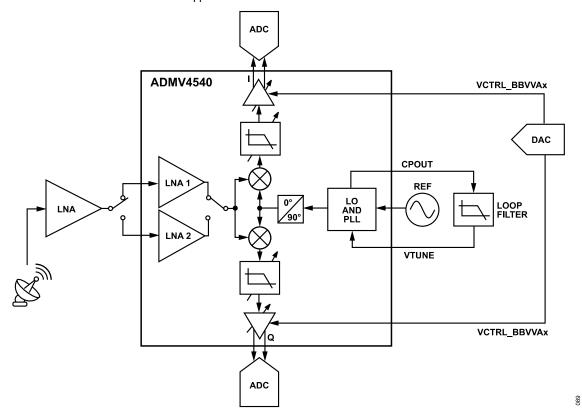

The ADMV4540 is a highly integrated quadrature demodulator with integrated synthesizer ideally suited for next generation K band satellite communication.

The RF front end of the ADMV4540 consists of two low noise amplifier (LNA) paths, each with an optimal cascaded, 5 dB, double sideband noise figure at maximum gain, while minimizing external components. The dual paths allow support for antenna polarization. Selection of the LNA path can be done through the SPI.

The LNA output is then downconverted to baseband using an inphase and quadrature (I/Q) mixer. The I/Q mixer output is then fed into fully differential low noise and low distortion programmable filters and variable gain amplifiers (VGAs). Each channel is capable of rejecting large, out of band interferers while reliably boosting the wanted signal, thus reducing the bandwidth and resolution requirements on the analog-to-digital converters (ADCs) of the system. The excellent matching between channels and their high spurious-free dynamic range (SFDR) over all gain and bandwidth settings make the ADMV4540 ideal for satellite communication systems with dense constellations, multiple carriers, and nearby interferers.

The three filter corners of 125 MHz, 250 MHz, and 500 MHz are all programmable via a serial peripheral interface (SPI). The filters provide a sixth-order Butterworth response with -3 dB corner frequencies of 141 MHz, 282 MHz, and 565 MHz. For operation beyond 565 MHz, the filter can be disabled and completely bypassed, thereby extending the -3 dB bandwidth up to 900 MHz.

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The high dynamic range baseband output amplifiers of the ADMV4540 provide an overall nominal conversion gain of 57 dB. The three baseband voltage variable attenuator (VVA) pins (VCTRL\_BBVVAx) of the ADMV4540 can be used for automatic gain control (AGC), giving the ADMV4540 a wide RF input dynamic range.

This feature rich device contains an integrated fractional-N phase-locked loop (PLL) and a low phase noise voltage controlled oscillator (VCO) that generates the necessary on-chip local oscillator (LO) signal for the two double balanced I/Q mixers, eliminating the need for external frequency synthesis. The VCO utilizes an internal automatic calibration routine that allows the PLL to select the necessary settings and lock.

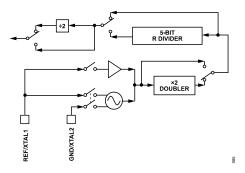

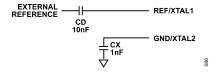

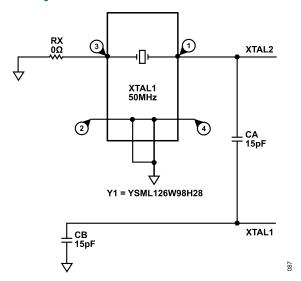

The reference input (REF $_{\rm IN}$ ) to the PLL of the ADMV4540 employs a differentially excited crystal oscillator at 50 MHz. Alternatively, the REF $_{\rm IN}$  can be driven by an external single-ended frequency reference up to 100 MHz. The phase frequency detector (PFD) comparison frequency operates up to 100 MHz, which allows for continuous LO coverage from 17 GHz to 21.5 GHz in extremely fine steps.

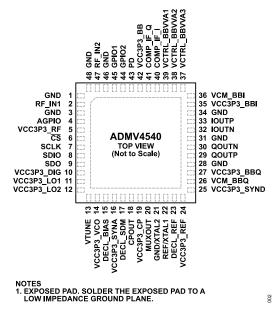

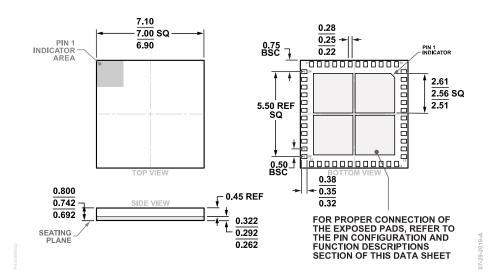

The ADMV4540 operates on a 3.3 V supply with less than 3.2 W of total power dissipation. It is available in a 48-terminal, RoHS compliant, 7 mm  $\times$  7 mm LGA package with an exposed paddle. The ADMV4540 can operate over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range on a +3.3 V power supply.

# **TABLE OF CONTENTS**

| Features                                    | 1  | Applications Information                   |      |

|---------------------------------------------|----|--------------------------------------------|------|

| Applications                                | 1  | Powering the ADMV4540                      | 36   |

| Functional Block Diagram                    | 1  | Heat Sink Selection                        | 36   |

| General Description                         | 1  | Recommended Land Pattern                   | . 36 |

| Specifications                              | 4  | Layout Considerations                      | 36   |

| Absolute Maximum Ratings                    | 7  | Register Summary                           |      |

| Thermal Resistance                          |    | Register Details                           |      |

| Electrostatic Discharge (ESD) Ratings       | 7  | Analog Devices SPI Standard Register       |      |

| ESD Caution                                 |    | Product ID (Lower 8 Bits of the 16 Bits)   |      |

| Pin Configuration and Function Descriptions |    | Register                                   | 40   |

| Typical Performance Characteristics         |    | Product ID (Upper 8 Bits of the 16 Bits)   |      |

| RF Bandwidth Performance Characteristic     |    | Register                                   | 40   |

| Baseband Bandwidth Performance              |    | Revision Number for Analog Devices SPI     |      |

| Characteristic                              | 14 | Definition Register                        | 41   |

| Temperature Sensor and ADC                  |    | RF Signal Chain Enables Register           |      |

| PLL and VCO Performance Characteristic      |    | I Path Common-Mode Register                |      |

| Performance with Controlling                |    | Q Path Common-Mode Register                |      |

| VCTRL_BBVVA1, VCTRL_BBVVA2, and             |    | LO Signal Chain Enables Register           |      |

| VCTRL_BBVVA3 Together                       | 25 | LO Phase Adjust Register                   |      |

| Theory of Operation                         |    | Crystal Oscillator Bits Register           |      |

| SPI Protocol                                |    | Baseband I Path Circuit Enables Register   |      |

| Supply Sequencing                           |    | Baseband Q Path Circuit Enables Register   |      |

| SPI Start-Up Sequences                      |    | Baseband Common Blocks Enables Register    |      |

| Frequency Update Sequence                   |    | Baseband Select Amplifier 1 IQ Gain and    |      |

| N Counter                                   |    | Bias Register                              | 43   |

| Double Buffered Registers                   |    | Baseband Select Amplifier 2 IQ Gain and    |      |

| Loop Filter                                 |    | Bias Register                              | 43   |

| Reference Input                             |    | Baseband Select Amplifier 3 IQ Gain and    |      |

| Crystal Oscillator                          |    | Bias Register                              | 43   |

| Charge Pump Current Setup                   |    | Baseband IQ Filters Bandwidth Select       |      |

| Bleed Current (BICP) Setup                  |    | Register                                   | 44   |

| Digital Lock Detect                         |    | Baseband Digital Step Attenuation Setting  |      |

| PFD and Charge Pump                         |    | Register                                   | 44   |

| VCO Autocalibration                         |    | N Divider INT LSB and Trigger Register     |      |

| Autocalibration Lock Time                   |    | N Divider INT MSB Register                 |      |

| Synthesizer Lock Timeout                    |    | N Divider FRAC1 LSB Register               |      |

| VCO Band Selection Time                     |    | N Divider FRAC1 Middle Register            |      |

| PLL Setting Time                            |    | N Divider FRAC1 MSB Register               |      |

| VCO Calibration Band Read Back              |    | Auxiliary Fractional Modulus LSB When      |      |

| Temperature Sensor Configuration            |    | Using the Exact Frequency Mode Register    | 45   |

| ADC Configuration                           |    | Auxiliary Fractional Modulus MSB When      |      |

| Gain Policy                                 |    | Using the Exact Frequency Mode Register    | 45   |

| Power Down                                  |    | N Divider Enable and Mode Select Register  |      |

| MUXOUT                                      |    | R Divider Setpoint Register                |      |

| GPIOs                                       |    | R Divider Controls Register                |      |

| LNA Selection                               |    | Lock Detect Configuration Register         |      |

| Baseband Filter Selection                   |    | SPI Override Value for VCO Band Register   |      |

| Image Reject Optimization                   |    | SPI Override Value for VCO Select Register |      |

| DC Offset Correction Loop                   |    | SYNTH LOCK TIMEOUT                         |      |

|                                             |    |                                            |      |

analog.com Rev. 0 | 2 of 54

# **TABLE OF CONTENTS**

| VCO Calibration Timeout LSB Register 47 | PLL MUXOUT Level Control Register  | 50 |

|-----------------------------------------|------------------------------------|----|

| VCO Calibration Timeout MSB Register 47 | AGPIO Mux and Pin Control Register | 50 |

| Automatic Frequency Calibration (AFC)   | ADC Control Bits Register          | 50 |

| Measurement Resolution Register47       | ADC Status Bits Register           | 51 |

| ALC_SELECT Register47                   | ADC Result Register                | 51 |

| Miscellaneous Control Register 147      | GPIOx Write Register               | 51 |

| Miscellaneous Control Register 248      | GPIO Read Register                 | 51 |

| Charge Pump High-Z Register48           | Control of GPIOx Pins              | 52 |

| Charge Pump Control Register48          | Spare Read Register 1              | 52 |

| Charge Pump Current Register48          | Spare Read Register 2              | 52 |

| Charge Pump Bleed Current Register48    | Spare Read Register 3              | 52 |

| FRAC2 LSB Register49                    | Spare Write Register 1             | 52 |

| FRAC2 MSB Register49                    | Spare Write Register 2             | 52 |

| VCO and Band Selection Adjustment       | Spare Write Register 3             | 53 |

| Register49                              | Outline Dimensions                 | 54 |

| VCO Calibration FSM Register49          | Ordering Guide                     | 54 |

| Lock Detect Readback Register49         | Evaluation Boards                  | 54 |

| MUXOUT50                                |                                    |    |

# **REVISION HISTORY**

10/2021—Revision 0: Initial Version

analog.com Rev. 0 | 3 of 54

# **SPECIFICATIONS**

Supply voltage ( $V_{CC}$ ) = 3.3 V, and  $T_A$  = 25°C, unless otherwise noted.

A 50  $\Omega$  source input impedance with a single-ended input drive was used, and the evaluation board RF traces were deembedded until the RF\_INx pin.

The performance metrics were per the I channel and Q channel, the evaluation board I channel and Q channel traces were deembedded until the I channel and Q channel pins, the I channel and Q channel outputs were ac-coupled with a 1  $\mu$ F capacitor on each channel output, the I channel and Q channel positive and negative outputs were combined with a 180° balun, and BB AMP1 GAIN x = 0, unless otherwise stated.

PLL filter bandwidth = 220 kHz with  $60^{\circ}$  of phase margin, reference frequency ( $f_{REF}$ ) = 50 MHz, DOUBLER\_EN = 1, PFD frequency ( $f_{PFD}$ ) = 100 MHz, and the external reference power is set to 3 dBm for the single-ended external reference, unless otherwise stated.

VCTRL\_BBVVA1 = 3.3 V, VCTRL\_BBVVA2 and VCTRL\_BBVA3 are used for automatic gain control (AGC), and the total output power for the I channel and Q channel is set to be −10 dBm each, unless otherwise stated.

Table 1.

| Parameter                                  | Test Conditions/Comments                                                | Min | Тур  | Max      | Unit    |

|--------------------------------------------|-------------------------------------------------------------------------|-----|------|----------|---------|

| RF INPUT INTERFACE                         | RF_IN1 and RF_IN2                                                       |     |      |          |         |

| Operating Frequency                        |                                                                         | 17  |      | 22       | GHz     |

| Return Loss                                | Single-ended input drive                                                |     | 12   |          | dB      |

| Nominal Input Impedance                    | Single-ended input drive                                                |     | 50   |          | Ω       |

| Composite Carrier Input Power              |                                                                         |     |      |          |         |

| Minimum                                    | Input carrier bandwidth of 250 MHz                                      |     | -66  |          | dBm     |

| Maximum                                    | Input carrier bandwidth of 1 GHz                                        |     | -30  |          | dBm     |

| RF1 to RF 2 Isolation                      |                                                                         |     | >25  |          | dB      |

| SYNTHESIZER                                |                                                                         |     |      |          |         |

| LO Internal Frequency                      |                                                                         | 17  |      | 21.5     | GHz     |

| PFD Frequency (f <sub>PFD</sub> )          |                                                                         |     |      | 100      | MHz     |

| VCO Tuning Sensitivity (K <sub>VCO</sub> ) |                                                                         |     | 190  |          | MHz/V   |

| VTUNE                                      |                                                                         | 1   | 1.5  | 2        | V       |

| MUXOUT                                     |                                                                         | 0   |      | $V_{CC}$ | V       |

| Charge Pump Current (I <sub>CP</sub> )     |                                                                         | 0.3 |      | 4.8      | mA      |

| CLOSED-LOOP PHASE NOISE                    | $f_{REF}$ = 50 MHz, $f_{PFD}$ = 100 MHz, $CP\_CURRENT$ = 4, $BICP$ = 4, |     |      |          |         |

|                                            | PLL filter bandwidth = 220 kHz with 58° of phase margin, and            |     |      |          |         |

|                                            | f <sub>REF</sub> = 50 MHz, see Loop Filter section                      |     |      |          |         |

| 1 kHz Offset                               |                                                                         |     | -84  |          | dBc/Hz  |

| 10 kHz Offset                              |                                                                         |     | -96  |          | dBc/Hz  |

| 100 kHz Offset                             |                                                                         |     | -98  |          | dBc/Hz  |

| 1 MHz Offset                               |                                                                         |     | -115 |          | dBc/Hz  |

| 10 MHz Offset                              |                                                                         |     | -128 |          | dBc/Hz  |

| Output Integrated Phase Noise              | Integrated from 1 kHz and 10 MHz                                        |     | 0.8  |          | °RMS    |

| BASEBAND I/Q INTERFACE                     |                                                                         |     |      |          |         |

| I/Q Output Voltage                         | Differential on I and Q                                                 |     | 200  |          | mV p-p  |

| I/Q Output Impedance                       | Differential on I and Q                                                 |     | 100  |          | Ω       |

| I/Q Amplitude Imbalance                    |                                                                         |     | ±0.5 |          | dB      |

| I/Q Phase Imbalance                        |                                                                         |     | 1.6  |          | Degrees |

| Return Loss                                | Differential return loss on I and Q                                     |     | 10   |          | dB      |

| BASEBAND LOW-PASS FILTERS (LPFs)           |                                                                         |     |      |          |         |

| 125 MHz SPI-Selectable LPF                 | Register 0x13C = 0x00                                                   |     |      |          |         |

| 3 dB Filter Bandwidth                      |                                                                         |     | 140  |          | MHz     |

| 2 × 3 dB Bandwidth Rejection               |                                                                         |     | 35   |          | dB      |

| Group Delay Variation                      |                                                                         |     | 1.6  |          | ns      |

| 3 dB Bandwidth Tolerance                   |                                                                         |     | ±10  |          | %       |

analog.com Rev. 0 | 4 of 54

# **SPECIFICATIONS**

Table 1.

| Parameter                                 | Test Conditions/Comments                                                                                                              | Min | Тур | Max | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 250 MHz SPI-Selectable LPF                | Register 0x13C = 0x05                                                                                                                 |     |     |     |      |

| 3 dB Filter Bandwidth                     |                                                                                                                                       |     | 285 |     | MHz  |

| 2 × 3 dB Bandwidth Rejection              |                                                                                                                                       |     | 35  |     | dB   |

| Group Delay Variation                     |                                                                                                                                       |     | 1.4 |     | ns   |

| 3 dB Bandwidth Tolerance                  |                                                                                                                                       |     | ±10 |     | %    |

| 500 MHz SPI-Selectable LPF                | Register 0x13C = 0x0A                                                                                                                 |     |     |     |      |

| 3 dB Filter Bandwidth                     |                                                                                                                                       |     | 565 |     | MHz  |

| 2 × 3 dB Bandwidth Rejection              |                                                                                                                                       |     | 35  |     | dB   |

| Group Delay Variation                     |                                                                                                                                       |     | 1   |     | ns   |

| 3 dB Bandwidth Tolerance                  |                                                                                                                                       |     | ±10 |     | %    |

| Bypass SPI-Selectable LPF                 | Register 0x13C = 0x0F                                                                                                                 |     |     |     |      |

| 3dB Filter Bandwidth                      |                                                                                                                                       |     | 900 |     | MHz  |

| 2 × 3 dB Bandwidth Rejection              |                                                                                                                                       |     | 35  |     | dB   |

| Group Delay Variation                     |                                                                                                                                       |     | 0.2 |     | ns   |

| I/Q DEMODULATOR PERFORMANCE               |                                                                                                                                       |     |     |     |      |

| Maximum Conversion Gain                   |                                                                                                                                       | 50  | 57  |     | dB   |

| Conversion Gain Control Range             | Gain control at baseband amplifiers using VCTRL_BBVVA2 and VCTRL_BBVA3                                                                |     | 55  |     | dB   |

|                                           | Gain control at baseband amplifiers using all VCTRL_BBVVAx                                                                            |     | 70  |     | dB   |

| Input Third-Order Intercept (IIP3)        | At -30 dBm composite input level, delta RF frequency (Δf <sub>RF</sub> ) = 1 MHz                                                      |     | -3  |     | dBm  |

| Third-Order Intermodulation Level (IM3)   | At -30 dBm composite input level, Δf <sub>RF</sub> = 1 MHz                                                                            |     | -54 |     | dBc  |

| Input 1 dB Compression Point (IP1dB)      | At maximum attenuation                                                                                                                |     | -19 |     | dBm  |

| Image Rejection                           | Uncalibrated                                                                                                                          |     | 30  |     | dBc  |

| Double Sideband Noise Figure              | At maximum conversion gain                                                                                                            |     | 5   |     | dB   |

| Ç                                         | At maximum attenuation                                                                                                                |     | 8   |     | dB   |

| Input Second-Order Intercept Point (IIP2) | At -30 dBm composite input level, Δf <sub>RF</sub> = 12 MHz                                                                           |     | 28  |     | dBm  |

| In Band Output Spurious                   |                                                                                                                                       |     | -50 |     | dBc  |

| Output Fractional Spurs                   |                                                                                                                                       |     | -60 |     | dBc  |

| LO to RF Leakage (dBm)                    |                                                                                                                                       |     | -60 |     | dBm  |

| DC Offset Error                           | 25°C                                                                                                                                  |     | 7.5 |     | mV   |

|                                           | 85°C                                                                                                                                  |     | 7.8 |     | mV   |

|                                           | -40°C                                                                                                                                 |     | 8   |     | mV   |

| PLL REF <sub>IN</sub> INTERFACE           |                                                                                                                                       |     |     |     |      |

| REF <sub>IN</sub> Frequency               | Single-ended mode, DOUBLER EN = 0                                                                                                     |     | 50  | 100 | MHz  |

| 114 1 7                                   | Single-ended mode, DOUBLER EN = 1                                                                                                     |     |     | 50  | MHz  |

|                                           | Crystal mode                                                                                                                          |     | 50  |     | MHz  |

| Power Level REF <sub>IN</sub>             | Single-ended mode                                                                                                                     | -5  | +3  | +5  | dBm  |

| VCTRL_BBVVAx INTERFACE                    |                                                                                                                                       | +   |     |     |      |

| AGC Voltage                               | On each VCTRL_BBVVAx pin                                                                                                              | 0   |     | 3.3 | V    |

| Impedance                                 | On each VCTRL BBVVAx pin                                                                                                              |     | 6.2 |     | kΩ   |

| Gain Slope                                | VCTRL_BBVVA1 = 3.3 V, AGC using VCTRL_BBVVA2 and VCTRL_BBVA3, series resistance of 5 kΩ on each VCTRL BBVVAx, AGC from 1.1 V to 2.6 V |     | 35  |     | dB/V |

|                                           | AGC using VCTRL_BBVVAx, series resistance of 5 kΩ on each VCTRL_BBVVAx, AGC from 1.1 V to 2.8 V                                       |     | 45  |     | dB/V |

analog.com Rev. 0 | 5 of 54

# **SPECIFICATIONS**

Table 1.

| Parameter                                                      | Test Conditions/Comments                                                                                | Min   | Тур | Max   | Unit |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| LOGIC INPUTS                                                   |                                                                                                         |       |     |       |      |

| Input Voltage Range                                            |                                                                                                         |       |     |       |      |

| High, V <sub>INH</sub>                                         |                                                                                                         | 1.5   |     | 3.3   | V    |

| Low, V <sub>INL</sub>                                          |                                                                                                         | 0     |     | 0.4   | V    |

| Input High and Low Current, I <sub>INH</sub> /I <sub>INL</sub> |                                                                                                         |       | 100 |       | μA   |

| LOGIC OUTPUTS                                                  |                                                                                                         |       |     |       |      |

| Output Voltage Range                                           |                                                                                                         |       |     |       |      |

| High, V <sub>OH</sub>                                          |                                                                                                         | 1.5   |     | 3.3   | V    |

| Low, V <sub>OL</sub>                                           |                                                                                                         | 0     |     | 0.4   | V    |

| Output High Current, I <sub>OH</sub>                           |                                                                                                         |       | 100 |       | μA   |

| POWER INTERFACE                                                |                                                                                                         |       |     |       |      |

| V <sub>CC</sub>                                                |                                                                                                         | 3.135 | 3.3 | 3.465 | V    |

| Supply Current (I <sub>CC</sub> )                              |                                                                                                         |       | 980 |       | mA   |

| Total Power Consumption                                        |                                                                                                         |       | 3.2 |       | W    |

|                                                                | Power down, PD = logic high                                                                             |       | 600 |       | mW   |

|                                                                | Power down, Register 0x100, Register 0x120, Register 0x130, Register 0x131, and Register 0x132 = 0x00.1 |       | 300 |       | mW   |

<sup>&</sup>lt;sup>1</sup> For further optimization of power-down power consumption, contact Analog Devices, Inc., sales.

analog.com Rev. 0 | 6 of 54

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                     | Rating                                     |

|-----------------------------------------------|--------------------------------------------|

| Maximum RF Power                              | 0 dBm                                      |

| Single-Ended External Reference Power         | 8 dBm                                      |

| $V_{CC}$                                      | 4 V                                        |

| Maximum Power Dissipation                     | 4 W                                        |

| VCTRL_BBVVAx                                  | 3.7 V                                      |

| Digital Logic                                 | $-0.4 \text{ V to V}_{CC} + 0.4 \text{ V}$ |

| AGPIO                                         | 3.7 V                                      |

| VCM_BBx                                       | 3.7 V                                      |

| Source and Sink Current (MUXOUT)              | 300 μΑ                                     |

| Temperature                                   |                                            |

| Storage Range (T <sub>STG</sub> )             | -50°C to +125°C                            |

| Operating Ambient (T <sub>A</sub> ) Range     | -40°C to +85°C                             |

| Maximum Junction (T <sub>J</sub> )            | 125°C                                      |

| Lifetime at Maximum T <sub>J</sub>            | 1 × 10 <sup>6</sup> hours                  |

| Peak                                          |                                            |

| Reflow Soldering                              | 260°C                                      |

| Time                                          | 40 secs                                    |

| Moisture Sensitivity Level (MSL) <sup>1</sup> | MSL3                                       |

Based on IPC/JEDEC J-STD-20 MSL classifications.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the junction to ambient thermal resistance, and  $\theta_{JC}$  is the junction to case thermal resistance.

Table 3. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | $\theta_{ m JC}$ | Unit |

|---------------------------|---------------|------------------|------|

| CC-48-5                   | 24.5          | 10               | °C/W |

<sup>1</sup> Thermal resistance values specified are simulated based on JEDEC specifications in compliance with JESD-51.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charged device model (FICDM) per ANSI/ESDA/JEDEC JS-002.

# **ESD Ratings for the ADMV4540**

Table 4. ADMV4540, 48-Terminal LGA

|           | Withstand Threshold |       |

|-----------|---------------------|-------|

| ESD Model | (V)                 | Class |

| НВМ       | ±500                | 1B    |

| FICDM     | ±500                | C2A   |

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 7 of 54

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

Table 5. Pin Function Descriptions

| Pin No. | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                         |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND         | Ground.                                                                                                                                                                                                                                                                                                                                                             |

| 2       | RF_IN1      | RF Input 1. The RF_IN1 pin has a 50 Ω input impedance. DC-coupled to ground. Ensure that no dc voltage is present on the RF_IN1 pin.                                                                                                                                                                                                                                |

| 3       | GND         | Ground.                                                                                                                                                                                                                                                                                                                                                             |

| 4       | AGPIO       | Analog General-Purpose Input and Output. Refer to the Temperature Sensor Configuration section to configure the temperature sensor output to the AGPIO pin. Refer to the ADC Configuration section to use the AGPIO pin as an input.                                                                                                                                |

| 5       | VCC3P3_RF   | 3.3 V Supply for the RF Path. Place a 0.01 µF capacitor close to the VCC3P3_RF pin.                                                                                                                                                                                                                                                                                 |

| 6       | CS          | Digital Logic Pin for SPI Chip Select (Negative Polarity, 3.3 V Logic). Place a series 33 $\Omega$ resistor for optimum performance. Serial communication is enabled when $\overline{CS}$ is set to logic low. When $\overline{CS}$ is set to logic high at the end of the serial data command, the data written into the register address is given in the command. |

| 7       | SCLK        | Digital Logic Pin for SPI Clock (3.3 V Logic). Place a series 33 Ω resistor for optimum performance. In write mode, data is sampled on the rising edge of SCLK. During a read cycle, output data changes at the falling edge of SCLK.                                                                                                                               |

| 8       | SDIO        | Digital Logic Pin for SPI Data Input and Output in 3-Wire Mode. SPI data input in 4-wire mode (3.3 V logic). Place a series 33 Ω resistor for optimum performance.                                                                                                                                                                                                  |

| 9       | SDO         | Digital Logic Pin. In 4-wire SPI mode, SDO is a serial data output (3.3 V logic), digital logic pin. In 3-wire SPI mode, SDO is unused and can be connected to ground. Place a series 33 Ω resistor for optimum performance.                                                                                                                                        |

| 10      | VCC3P3_DIG  | SPI and Digital Supply. Place a 0.01 μF capacitor close to the VCC3P3_DIG pin.                                                                                                                                                                                                                                                                                      |

| 11      | VCC3P3_LO1  | LO Path 3.3 V Supply 1. Place a 0.01 μF capacitor close to the VCC3P3_LO1 pin.                                                                                                                                                                                                                                                                                      |

| 12      | VCC3P3_LO2  | LO Path 3.3 V Supply 2. Place a 0.01 μF capacitor close to the VCC3P3_LO2 pin.                                                                                                                                                                                                                                                                                      |

| 13      | VTUNE       | VCO Tune Input (1 V to 2 V). The VTUNE pin is driven by the output of the loop filter.                                                                                                                                                                                                                                                                              |

| 14      | VCC3P3_VCO  | VCO 3.3 V Supply. Place a 0.01 μF capacitor close to the VCC3P3_VCO pin.                                                                                                                                                                                                                                                                                            |

| 15      | DECL_BIAS   | VCO Core Bias Decouple Pin. Place a 1 μF capacitor close to the DECL_BIAS pin.                                                                                                                                                                                                                                                                                      |

| 16      | VCC3P3_SYNA | Synthesizer Analog 3.3 V Supply. Place a 0.01 μF capacitor close to the VCC3P3_SYNA pin.                                                                                                                                                                                                                                                                            |

| 17      | DECL_SDM    | Σ-Δ Modulator Low Dropout (LDO) Regulator Decouple Pin. Place a 1 μF capacitor close to the DECL_SDM pin.                                                                                                                                                                                                                                                           |

| 18      | CPOUT       | Synthesizer Charge Pump Output. Connect the CPOUT pin to VTUNE (Pin 13) through the loop filter. Place the loop filter component, C1 as close as possible to the CPOUT pin.                                                                                                                                                                                         |

| 19      | VCC3P3_CP   | Charge Pump 3.3 V Supply. Place a 0.01 μF capacitor close to the VCC3P3_CP pin.                                                                                                                                                                                                                                                                                     |

| 20      | MUXOUT      | PLL Multiplexer Output. Refer to the EVAL-ADMV4540 for connection options.                                                                                                                                                                                                                                                                                          |

| 21      | GND/XTAL2   | Second Reference Clock Input for Differential Reference or Ground from Single-Ended Reference. See Crystal Oscillator section and Reference Input section for configuration options.                                                                                                                                                                                |

analog.com Rev. 0 | 8 of 54

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 5. Pin Function Descriptions

| Pin No. | Mnemonic     | Description                                                                                                                                                                                                                 |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22      | REF/XTAL1    | Reference Clock Input. Single ended external reference input. For more information, see the Reference Input section for configuration options.                                                                              |

| 23      | DECL_REF     | Reference 1.8 V LDO Regulator Decouple Pin. Place a 1 µF capacitor close to the DECL_REF pin.                                                                                                                               |

| 24      | VCC3P3_REF   | Reference Input Buffer 3.3 V Supply. Place a 0.01 µF capacitor close to the VCC3P3_REF pin.                                                                                                                                 |

| 25      | VCC3P3_SYND  | Synthesizer Digital 3.3 V Supply. Place a 0.01 µF capacitor close to the VCC3P3_SYND pin.                                                                                                                                   |

| 26      | VCM_BBQ      | Baseband Q Channel Output Common-Mode Level Input. Leave the VCM_BBQ pin floating.                                                                                                                                          |

| 27      | VCC3P3_BBQ   | Baseband Q Channel 3.3 V Supply. Place a 0.01 μF capacitor close to the VCC3P3_BBQ pin.                                                                                                                                     |

| 28      | GND          | Ground.                                                                                                                                                                                                                     |

| 29, 30  | QOUTP, QOUTN | Baseband Q Channel Positive and Negative Outputs. These 100 Ω differential impedance outputs can be ac-coupled with an ac coupling capacitor. The default common-mode output voltage is 1.65 V.                             |

| 31      | GND          | Ground.                                                                                                                                                                                                                     |

| 32, 33  | IOUTN, IOUTP | Baseband I Channel Negative and Positive Outputs. These 100 $\Omega$ differential impedance outputs can be ac-coupled with an ac coupling capacitor. The default common-mode output voltage is 1.65 V.                      |

| 34      | GND          | Ground.                                                                                                                                                                                                                     |

| 35      | VCC3P3_BBI   | Baseband I Channel 3.3 V Supply. Place a 0.01 µF capacitor close to the VCC3P3_BBI pin.                                                                                                                                     |

| 36      | VCM_BBI      | Baseband I Channel Output Common-Mode Level Input. Leave this pin floating.                                                                                                                                                 |

| 37      | VCTRL_BBVVA3 | Baseband VVA Control Voltage 3. Place a series resistor of 5 kΩ.                                                                                                                                                            |

| 38      | VCTRL_BBVVA2 | Baseband VVA Control Voltage 2. Place a series resistor of 5 kΩ.                                                                                                                                                            |

| 39      | VCTRL_BBVVA1 | Baseband VVA Control Voltage 1. Place a series resistor of 5 kΩ.                                                                                                                                                            |

| 40      | COMP_IF_I    | Baseband I Channel Offset Cancellation Compensation Capacitor. Place a 1 µF capacitor close to the COMP_IF_I pin.                                                                                                           |

| 41      | COMP_IF_Q    | Baseband Q Channel Offset Cancellation Compensation Capacitor. Place a 1 µF capacitor close to the COMP_IF_Q pin.                                                                                                           |

| 42      | VCC3P3_BB    | Baseband 3.3 V Supply. Place a 0.01 µF capacitor close to the VCC3P3_BB pin.                                                                                                                                                |

| 43      | PD           | Digital Logic Power-Down Pin. Set to logic low (0 V) for normal operation. Set to logic high (3.3 V) to power down the ADMV4540 while keeping the synthesizer locked. Refer to the Power Down section for more information. |

| 44      | GPIO1        | Digital Logic General-Purpose Digital Input and Output Pin 1. Do not exceed the input voltage of 3.3 V. Refer to GPIOs section for more details.                                                                            |

| 45      | GPIO2        | Digital Logic General-Purpose Digital Input and Output Pin 2. Do not exceed the input voltage of 3.3 V. Refer to GPIOs section for more details.                                                                            |

| 46      | GND          | Ground.                                                                                                                                                                                                                     |

| 47      | RF_IN2       | RF Input 2. The RF_IN2 has a 50 Ω input impedance. DC-coupled to ground. Ensure that no dc voltage is present on the RF_IN2 pin.                                                                                            |

| 48      | GND          | Ground.                                                                                                                                                                                                                     |

|         | EPAD         | Exposed Pad. Solder the exposed pad to a low impedance ground plane. See the Heat Sink Selection section and the Recommended Land Pattern section for more information.                                                     |

analog.com Rev. 0 | 9 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

## RF BANDWIDTH PERFORMANCE CHARACTERISTIC

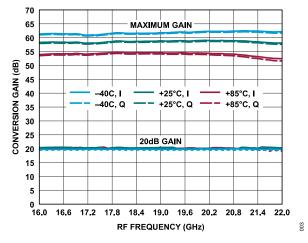

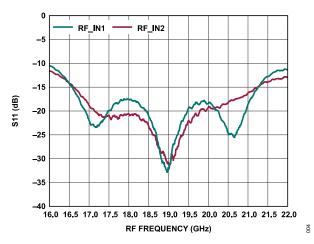

Baseband frequency ( $f_{BB}$ ) = 36 MHz,  $V_{CC}$  = 3.3 V, and  $T_A$  = 25°C, unless otherwise noted. The evaluation board RF traces were deembedded until RF\_INx, unless otherwise noted. The minimum input power was measured with BB\_AMP1\_GAIN\_x = 0, RF\_INx = -66 dBm, and VCTRL\_BBVVAx = 3.3 V. The maximum input power measurements were made with RF\_INx = -30 dBm, BB\_AMP1\_GAIN\_x = 3, VCTRL\_BBVVA1 = 3.3 V, AGC using VCTRL\_BBVVA2 and VCTRL\_BBVA3, and the total output power set to -10 dBm per I and Q through AGC. Performance metrics were per the I channel and Q channel, the evaluation board I channel and Q channel traces were deembedded until the I channel and Q channel pins. The I channel and Q channel outputs were ac-coupled with a 1  $\mu$ F capacitor on each channel output, and the I channel and Q channel positive and negative outputs were combined with a 180° balun, unless otherwise noted. PLL filter bandwidth = 220 kHz with 60° of phase margin,  $f_{REF}$  = 50 MHz, DOUBLER\_EN = 1,  $f_{PFD}$  = 100 MHz, and the external reference power was set to 3 dBm for the single-ended external reference, unless otherwise stated.

Figure 3. Conversion Gain vs. RF Frequency at Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Temperatures and I and Q Channels

Figure 4. Input Return Loss (S11) vs. RF Frequency for RF\_IN1 and RF\_IN2

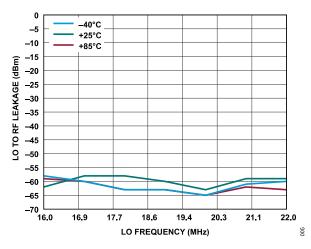

Figure 5. LO to RF Leakage vs. LO Frequency at Various Temperatures

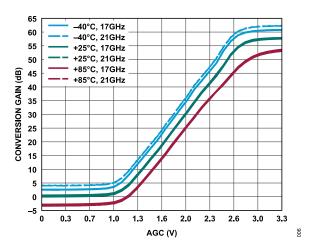

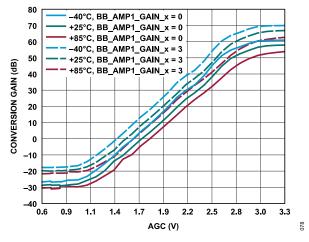

Figure 6. Conversion Gain vs. AGC for LO = 17 GHz and 21 GHz at Various Temperatures

analog.com Rev. 0 | 10 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

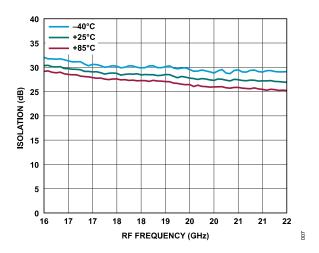

Figure 7. RF\_IN1 to RF\_IN2 Isolation vs. RF Frequency, 20 dB Gain (Maximum Input Power) at Various Temperatures

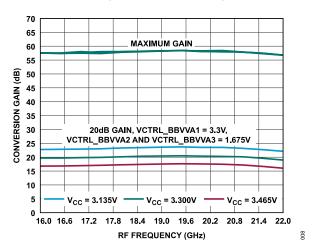

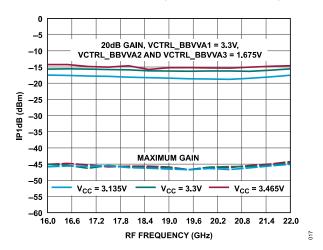

Figure 8. Conversion Gain vs. RF Frequency at Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Supply Voltages (±5%)

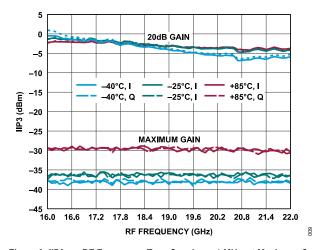

Figure 9. IIP3 vs. RF Frequency, Tone Spacing = 1 MHz, at Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Temperatures and I and Q Channels

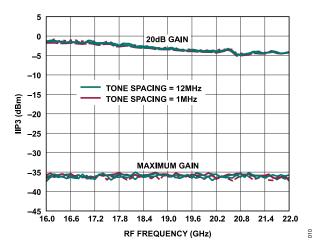

Figure 10. IIP3 vs. RF Frequency, Tone Spacing = 12 MHz and 1 MHz at Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power)

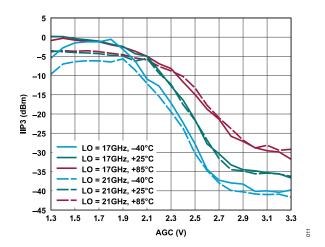

Figure 11. IIP3 vs. AGC, LO = 17 GHz and 21 GHz at Various Temperatures

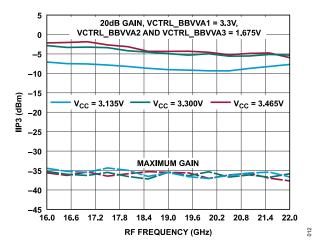

Figure 12. IIP3 vs. RF Frequency at Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Supply Voltages (±5)

analog.com Rev. 0 | 11 of 54

## TYPICAL PERFORMANCE CHARACTERISTICS

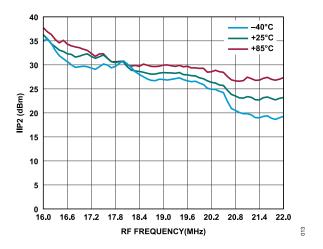

Figure 13. IIP2 vs. RF Frequency, Tone Spacing = 12 MHz at 20 dB Gain (Maximum Input Power) at Various Temperatures

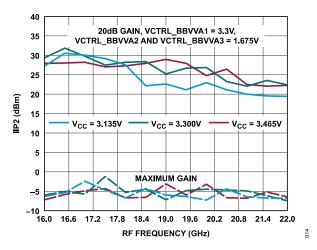

Figure 14. IIP2 vs. RF Frequency at Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Supply Voltages (±5)

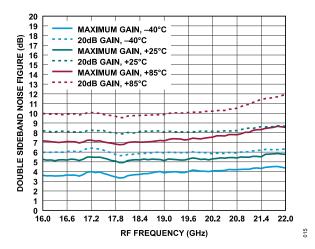

Figure 15. Double Sideband Noise Figure vs. RF Frequency at Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Temperatures

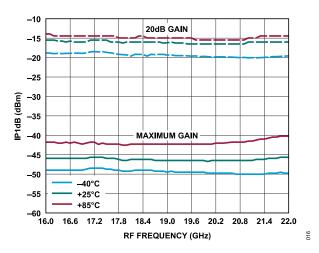

Figure 16. Input P1dB vs. RF Frequency, Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Temperatures

Figure 17. Input P1dB vs. RF Frequency at Maximum Gain (Minimum Input Power) and 20 dB Conversion Gain (Maximum Input Power) at Various Supply Voltages (±5%)

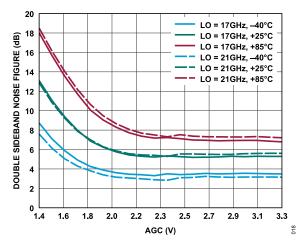

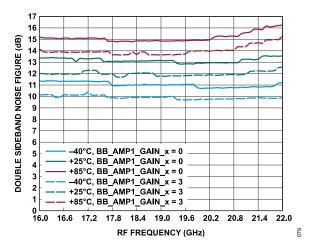

Figure 18. Double Sideband Noise Figure vs. AGC, LO = 17 GHz and 21 GHz at Various Temperatures

analog.com Rev. 0 | 12 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

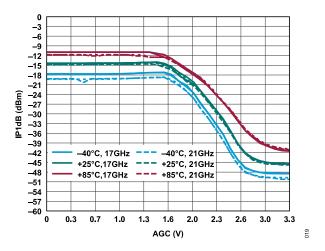

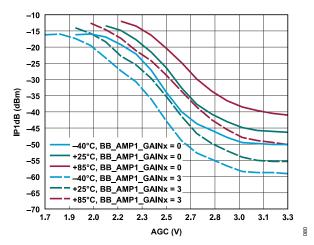

Figure 19. Input P1dB vs. AGC, LO = 17 GHz and 21 GHz at Various Temperatures

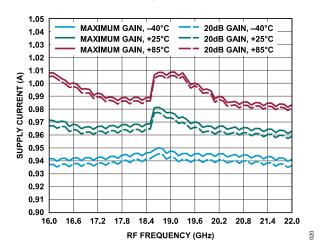

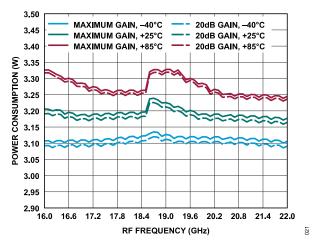

Figure 20. Supply Current vs. RF Frequency for Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Temperatures

Figure 21. Power Consumption vs. RF Frequency for Maximum Gain (Minimum Input Power) and 20 dB Gain (Maximum Input Power) at Various Temperatures

analog.com Rev. 0 | 13 of 54

## TYPICAL PERFORMANCE CHARACTERISTICS

## BASEBAND BANDWIDTH PERFORMANCE CHARACTERISTIC

$f_{BB}$  = 36 MHz,  $V_{CC}$  = 3.3 V, and  $T_A$  = 25°C, unless otherwise noted. The evaluation board RF traces were deembedded until RF\_INx, unless otherwise noted. The minimum input power was measured with BB\_AMP1\_GAIN\_x = 0, RF\_INx= -66 dBm, and VCTRL\_BBVVAx = 3.3 V. The maximum input power measurements were made with RF\_INx = -30 dBm, BB\_AMP1\_GAIN\_x = 0, VCTRL\_BBVVA1 = 3.3 V, AGC using VCTRL\_BBVVA2 and VCTRL\_BBVA3, and the total output power set to -10 dBm per I and Q through AGC. Performance metrics were per the I channel and Q channel, the evaluation board I channel and Q channel traces were deembedded until the I channel and Q channel pins. The I channel and Q channel outputs were ac-coupled with a 1  $\mu$ F capacitor on each channel output, and the I channel and Q channel positive and negative outputs were combined with a 180° balun, unless otherwise noted. PLL filter bandwidth = 220 kHz with 60° of phase margin,  $f_{REF}$  = 50 MHz, DOUBLER\_EN = 1,  $f_{PFD}$  = 100 MHz, and the external reference power was set to 3 dBm for the single-ended external reference, unless otherwise stated.

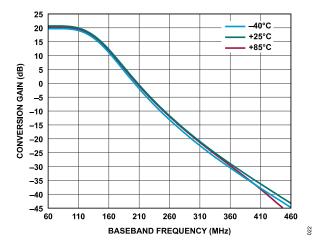

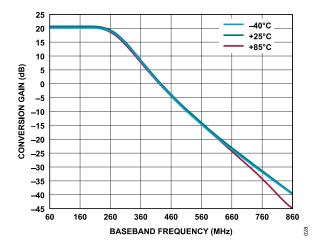

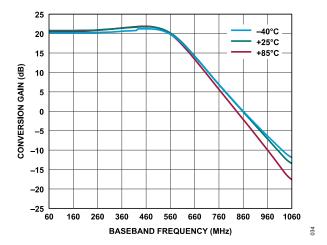

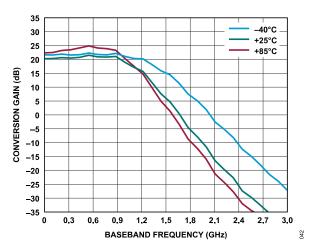

Figure 22. 125 MHz, SPI-Selectable Baseband LPF Frequency Response, Conversion Gain vs. Baseband Frequency at Various Temperature

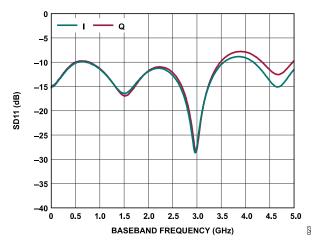

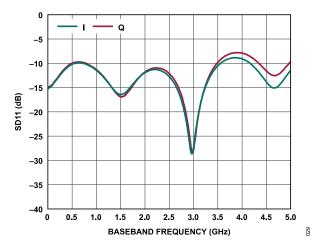

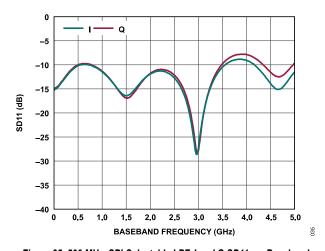

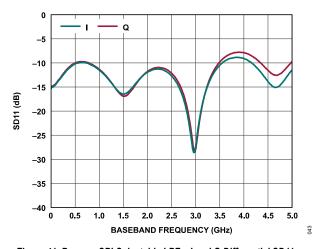

Figure 23. 125 MHz, SPI-Selectable Baseband LPF, I and Q Differential Return Loss (SD11) vs. Baseband Frequency

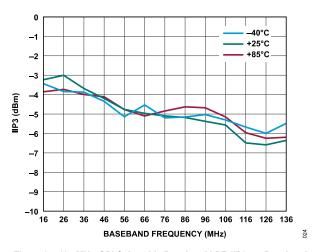

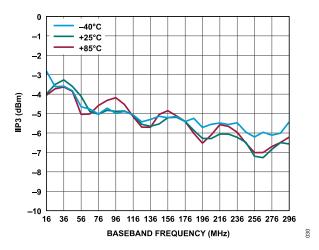

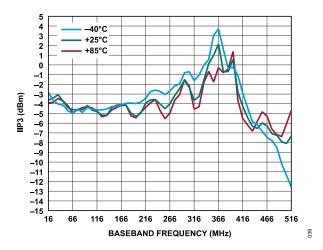

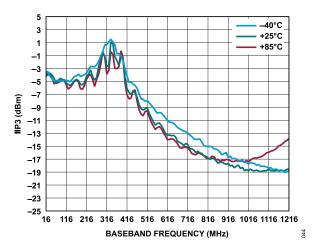

Figure 24. 125 MHz, SPI-Selectable Baseband LPF, IIP3 vs. Baseband Frequency at Various Temperatures at 20 dB Gain (Maximum Input Power)

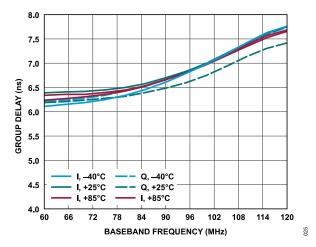

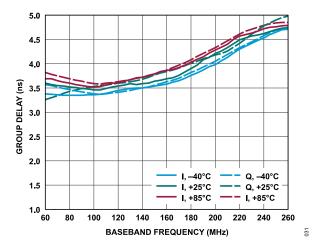

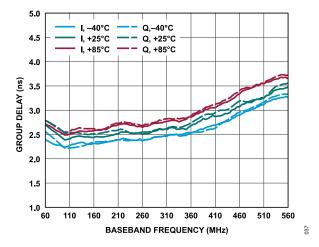

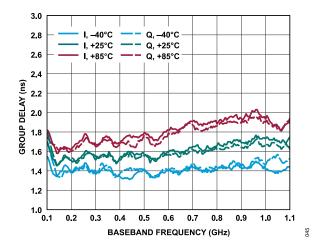

Figure 25. 125 MHz, SPI-Selectable Baseband LPF, Group Delay vs. Baseband Frequency at Various Temperatures and the I and Q Channels

analog.com Rev. 0 | 14 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

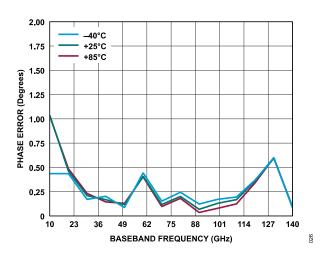

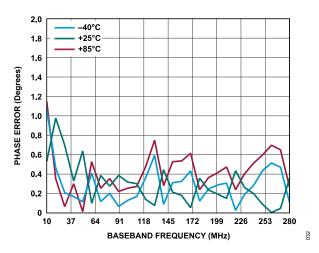

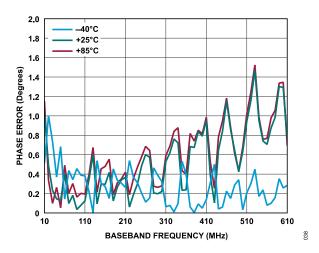

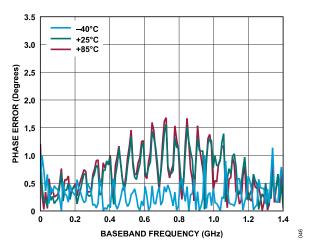

Figure 26. 125 MHz, SPI-Selectable Baseband LPF, Phase Error vs. Baseband Frequency at Various Temperatures

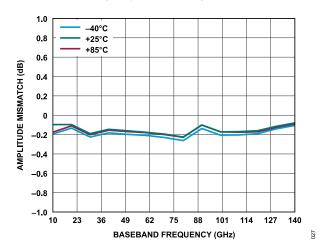

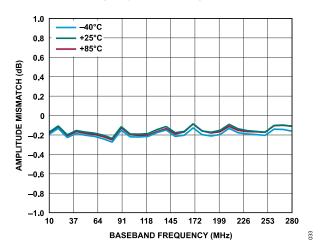

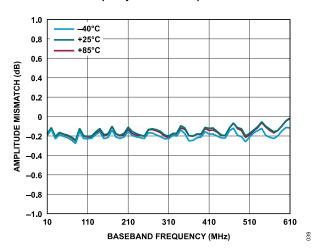

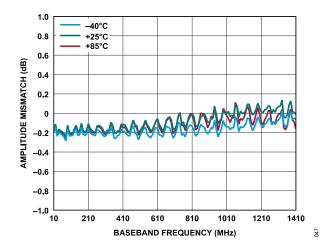

Figure 27. 125 MHz, SPI-Selectable Baseband LPF, Amplitude Mismatch vs. Baseband Frequency at Various Temperatures

Figure 28. 250 MHz, SPI-Selectable Baseband LPF Frequency Response, Conversion Gain vs. Baseband Frequency at Various Temperatures

Figure 29. 250 MHz, SPI-Selectable Baseband LPF, I and Q SD11 vs. Baseband Frequency

Figure 30. 250 MHz, SPI-Selectable Baseband LPF, IIP3 vs. Baseband Frequency at Various Temperatures at 20 dB Gain (Maximum Input Power)

Figure 31. 250 MHz, SPI-Selectable Baseband LPF, Group Delay vs. Baseband Frequency at Various Temperatures and the I and Q Channels

analog.com Rev. 0 | 15 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 32. 250 MHz, SPI-Selectable Baseband LPF, Phase Error vs. Baseband Frequency at Various Temperatures

Figure 33. 250 MHz, SPI-Selectable Baseband LPF, Amplitude Mismatch vs. Baseband Frequency at Various Temperatures

Figure 34. 500 MHz, SPI-Selectable LPF Frequency Response, Conversion Gain vs. Baseband Frequency at Various Temperatures

Figure 35. 500 MHz, SPI-Selectable LPF, I and Q SD11 vs. Baseband Frequency

Figure 36. 500 MHz, SPI-Selectable LPF, IIP3 vs. Baseband Frequency at Various Temperatures at 20 dB Gain (Maximum Input Power)

Figure 37. 500 MHz, SPI-Selectable LPF, Group Delay vs. Baseband Frequency at Various Temperatures and the I and Q Channels

analog.com Rev. 0 | 16 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 38. 500 MHz, SPI-Selectable LPF, Phase Error vs. Baseband Frequency at Various Temperatures

Figure 39. 500 MHz, SPI-Selectable LPF, Amplitude Mismatch vs. Baseband Frequency at Various Temperatures

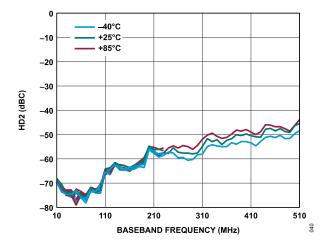

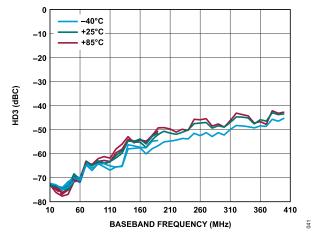

Figure 40. Harmonic Distortion 2 (HD2) vs. Baseband Frequency at 20 dB Gain (Maximum Input Power) and at Various Temperatures

Figure 41. Bypass, SPI-Selectable LPFs, I and Q Differential SD11 vs.

Baseband Frequency

Figure 42. Bypass, SPI-Selectable LPFs, Conversion Gain vs. Baseband Frequency at Various Temperatures

Figure 43. Harmonic Distortion 3 (HD3) vs. Baseband Frequency at 20 dB Gain (Maximum Input Power) and at Various Temperatures

analog.com Rev. 0 | 17 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 44. Bypass, SPI-Selectable LPFs, IIP3 vs. Baseband Frequency at Various Temperatures and at 20 dB Gain (Maximum Input Power)

Figure 45. Bypass, SPI-Selectable LPFs, Group Delay vs. Baseband Frequency at Various Temperatures and the I and Q Channels

Figure 46. Bypass, SPI-Selectable LPFs, Phase Error vs. Baseband Frequency at Various Temperatures

Figure 47. Bypass, SPI-Selectable LPFs, Amplitude Mismatch vs. Baseband Frequency at Various Temperatures

analog.com Rev. 0 | 18 of 54

# **TYPICAL PERFORMANCE CHARACTERISTICS**

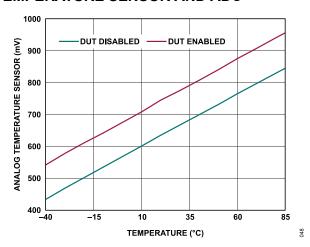

# **TEMPERATURE SENSOR AND ADC**

Figure 48. Analog Temperature Sensor at AGPIO Pin vs. Temperature with Device Under Test (DUT) Disabled and Enabled

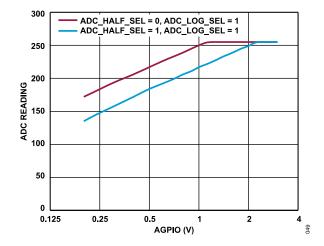

Figure 49. ADC Reading vs. AGPIO for ADC\_LOG\_SEL = 1

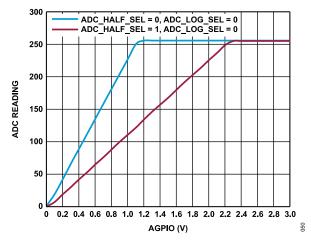

Figure 50. ADC Reading vs. AGPIO for ADC\_LOG\_SEL = 0

analog.com Rev. 0 | 19 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

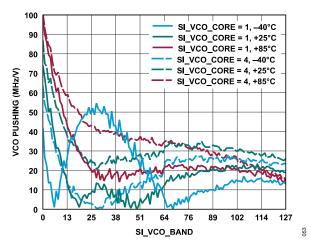

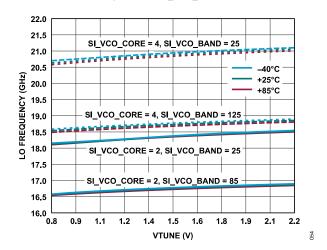

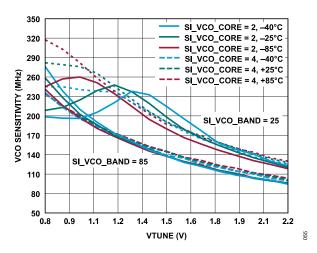

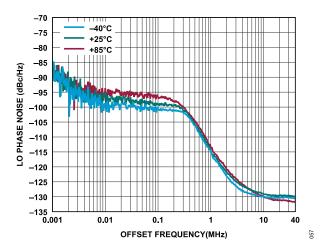

## PLL AND VCO PERFORMANCE CHARACTERISTIC

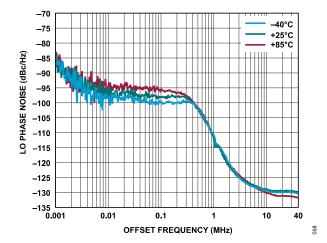

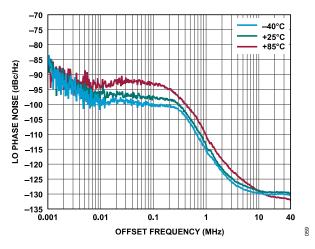

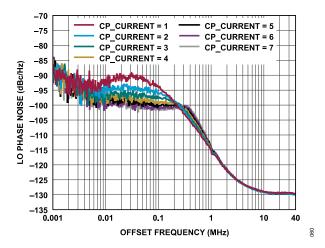

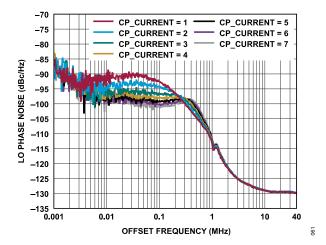

The I channel and Q channel outputs are ac-coupled with a 1  $\mu$ F capacitor on each channel output, and the I channel and Q channel positive and negative outputs are combined with a 180° balun, unless otherwise noted.  $f_{BB}$  = 100 MHz,  $V_{CC}$  = 3.3 V, and  $T_A$  = 25°C, unless otherwise noted. PLL filter bandwidth = 220 kHz with 60° of phase margin,  $f_{REF}$  = 50 MHz, DOUBLER\_EN = 1,  $f_{PFD}$  = 100 MHz, and the external reference power is set to 3 dBm for the single-ended external reference, unless otherwise stated.

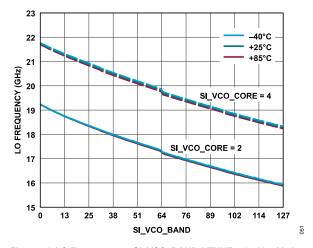

Figure 51. LO Frequency vs. SI\_VCO\_BAND, VTUNE = 1.5 V at Various Temperatures, Open Loop, SI\_VCO\_CORE = 1 and = 4

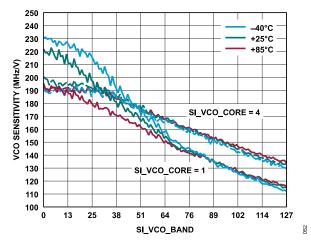

Figure 52. VCO Sensitivity vs. SI\_VCO\_BAND, VTUNE = 1.5 V, Open Loop at Various Temperatures, SI VCO CORE = 1 and = 4

Figure 53. VCO Pushing vs. SI\_VCO\_BAND, Open Loop, VTUNE = 1.5 V, at Various Temperatures, SI\_VCO\_CORE = 1 and = 4

Figure 54. LO Frequency vs. VTUNE over Temperature, Four Bands (Two Bands for VCO Core 1 and Two Bands for VCO Core 2)

analog.com Rev. 0 | 20 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 55. VCO Sensitivity vs. VTUNE at Various Temperatures, SI VCO CORE = 2 and = 4

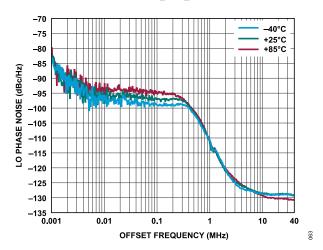

Figure 56. LO Phase Noise vs. Offset Frequency at 17.1 GHz and at Various Temperatures, CP\_CURRENT = 4 and SI\_VCO\_CORE = 1

Figure 57. LO Phase Noise vs. Offset Frequency at 18.6 GHz and at Various Temperatures, CP\_CURRENT = 4 and SI\_VCO\_CORE = 1

Figure 58. LO Phase Noise vs. Offset Frequency at 18.6 GHz and at Various Temperatures, CP\_CURRENT = 4 and SI\_VCO\_CORE = 4

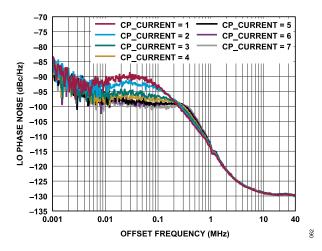

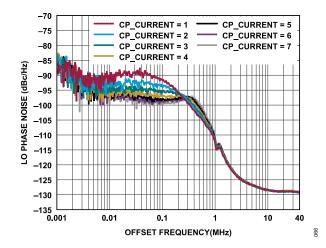

Figure 59. LO Phase Noise vs. Offset Frequency, CP\_CURRENT = 1 to 7, LO = 17 GHz, and SI\_VCO\_CORE = 1

Figure 60. LO Phase Noise vs. Offset Frequency, CP\_CURRENT = 1 to 7, LO = 18.5 GHz, and SI\_VCO\_CORE = 1

analog.com Rev. 0 | 21 of 54

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 61. LO Phase Noise vs. Offset Frequency, CP\_CURRENT = 1 to 7, LO = 19 GHz, and SI\_VCO\_CORE = 4

Figure 62. LO Phase Noise vs. Offset Frequency at 21 GHz and at Various Temperatures, CP\_CURRENT = 4 and SI\_VCO\_CORE = 4

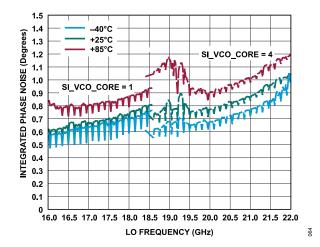

Figure 63. Integrated Phase Noise, 1 kHz to 10 MHz vs. LO Frequency and at Various Temperatures, CP\_CURRENT = 4

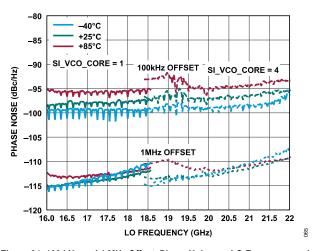

Figure 64. 100 kHz and 1 MHz Offset, Phase Noise vs. LO Frequency and at Various Temperatures, CP\_CURRENT = 4

Figure 65. LO Phase Noise vs. Offset Frequency, CP\_CURRENT = 1 to 7, LO = 21 GHz, and SI\_VCO\_CORE = 1

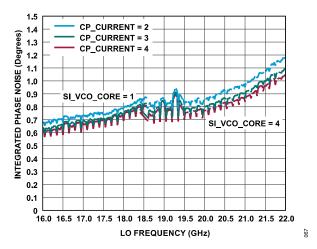

Figure 66. Integrated Phase Noise, 1 kHz to 10 MHz vs. LO Frequency, CP CURRENT = 2, 3, and 4

analog.com Rev. 0 | 22 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

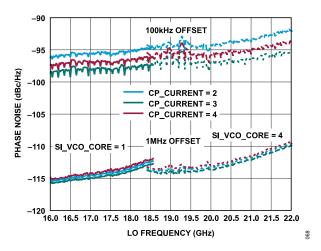

Figure 67. 100 kHz and 1 MHz Offset, Phase Noise vs. LO Frequency at Various Temperatures, CP \_CURRENT = 2, 3, and 4

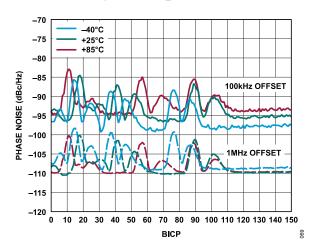

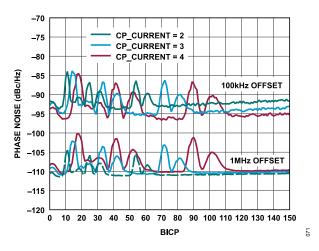

Figure 68. 1 MHz and 100 kHz Offset, Phase Noise vs. BICP at Various Temperatures, CP\_CURRENT = 4, and LO = 21 GHz

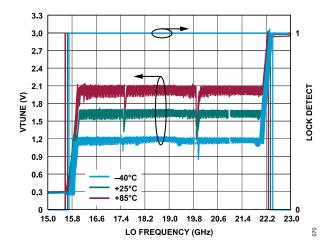

Figure 69. VTUNE and Lock Detect vs. LO Frequency at Various Temperatures

Figure 70. 100 kHz and 1 MHz Offset, Phase Noise vs. BICP, CP\_CURRENT = 2, 3, and 4 and LO = 21 GHz

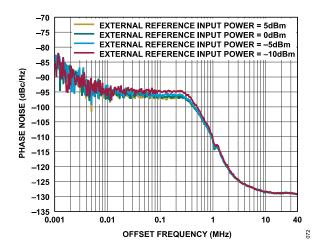

Figure 71. Phase Noise vs. Offset Frequency over the External Reference Input Power, LO = 21 GHz

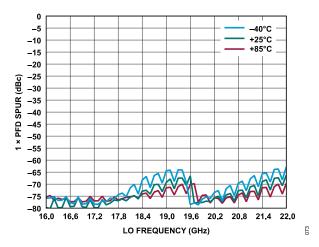

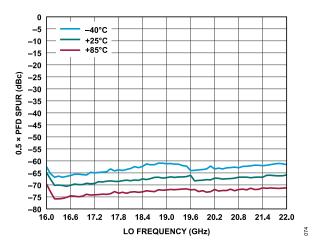

Figure 72. 1 × PFD Spur vs. LO Frequency at Various Temperatures, Spur Referred to the Main I Channel and Q Channel Output Frequency

analog.com Rev. 0 | 23 of 54

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 73. 0.5 × PFD Spur vs. LO Frequency at Various Temperatures, Spur Referred to the Main I Channel and Q Channel Output Frequency

analog.com Rev. 0 | 24 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

# PERFORMANCE WITH CONTROLLING VCTRL\_BBVVA1, VCTRL\_BBVVA2, AND VCTRL\_BBVVA3 TOGETHER

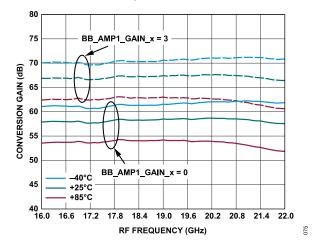

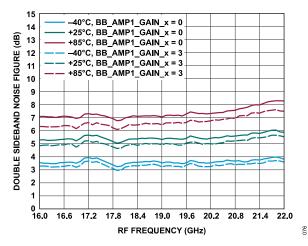

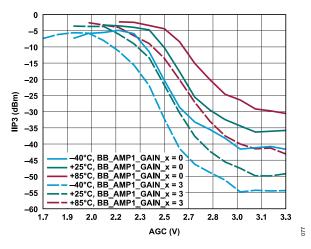

$f_{BB}$  = 36 MHz,  $V_{CC}$  = 3.3 V, and  $T_A$  = 25°C, unless otherwise noted. The evaluation board RF traces were deembedded until RF\_INx, unless otherwise noted. The minimum input power was measured with RF\_INx= -66 dBm and VCTRL\_BBVVAx = 3.3 V. The maximum input power measurements were made with RF\_INx = -30 dBm, AGC using VCTRL\_BBVVAx, and the total output power set to -10 dBm per I and Q through AGC. Performance metrics were per the I channel and Q channel, the evaluation board I channel and Q channel traces were deembedded until the I channel and Q channel pins. The I channel and Q channel outputs were ac-coupled with a 1  $\mu$ F capacitor on each channel output, and the I channel and Q channel positive and negative outputs were combined with a 180° balun, unless otherwise noted. PLL filter bandwidth = 220 kHz with 60° of phase margin,  $f_{REF}$  = 50 MHz, DOUBLER\_EN = 1,  $f_{PFD}$  = 100 MHz, and the external reference power was set to 3 dBm for the single-ended external reference, unless otherwise stated.

Figure 74. Conversion Gain vs. RF Frequency at Maximum Gain (Minimum Input Power) at Various Temperatures and Various BB\_AMP1\_GAIN\_x

Settings

Figure 75. Double Sideband Noise Figure vs. RF Frequency at Maximum Gain (Minimum Input Power) at Various Temperatures and Various BB\_AMP1\_GAIN\_x Settings

Figure 76. IIP3 vs. AGC, LO = 21 GHz at Maximum Gain (Minimum Input Power) at Various Temperatures and Various BB\_AMP1\_GAIN\_x Settings

Figure 77. Conversion Gain vs. AGC, LO = 17 GHz, Maximum Gain (Minimum Input Power) at Various Temperatures and Various BB\_AMP1\_GAIN\_x

Settings

analog.com Rev. 0 | 25 of 54

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 78. Double Sideband Noise Figure vs. RF Frequency 20 dB Gain (Minimum Input Power) at Various Temperatures and Various BB\_AMP1\_GAIN\_x Settings

Figure 79. IP1dB vs. AGC, LO = 21 GHz Various Temperatures

analog.com Rev. 0 | 26 of 54

### THEORY OF OPERATION

The ADMV4540 is a highly integrated quadrature demodulator with integrated fractional-N PLL and LO ideally suited for next generation K band satellite communication. The fractional-N PLL locks the LO to a precise reference input signal for low noise operation. The LO signal is then amplified to generate the necessary LO level for the I/Q mixer. The I/Q mixer generates differential baseband outputs that are amplified using differential baseband amplifiers whose gain can be controlled using external control voltages. The differential baseband output is then filtered using three SPI-selectable LPFs or optionally bypassed.

## SPI PROTOCOL

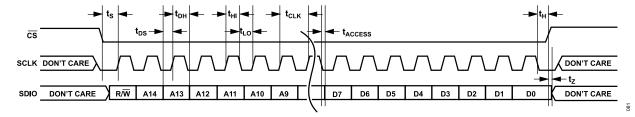

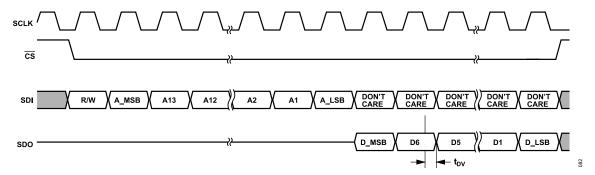

The SPI of the ADMV4540 allows the user to configure the device for specific operation using a 4-wire SPI (SCLK, SDIO, SDO, and  $\overline{CS}$ ). The SPI is compatible with 3.3 V dc logic. See Table 6 for the digital lock timing.

The ADMV4540 protocol consists of a write or read bit, followed by 15 register address (A14 to A0) bits and 8 data bits (D7 to D0). The default for both the address and data fields are organized MSB first and end with the LSB when Register 0x000, Bit 6 is set to 0. For a write, set the first bit (MSB) to 0, and for a read, set this bit to 1. The  $\overline{\text{CS}}$ , SCLK, SDIO, and optional SDO are used to communicate with the ADMV4540. The rising edge of the SCLK is used to latch the data. Figure 80 shows a typical write sequence, and Figure 81 shows a typical 4-wire SPI read sequence.

Table 6. Digital Logic Timing

| Parameter         | Value | Unit | Description                                                                                                       |

|-------------------|-------|------|-------------------------------------------------------------------------------------------------------------------|

| f <sub>SCLK</sub> | 10    | MHz  | Maximum serial clock rate, 1/t <sub>SCLK</sub> , which is the SCLK time                                           |

| t <sub>HI</sub>   | 50    | ns   | Minimum period that SCLK is in logic high state                                                                   |

| LO                | 50    | ns   | Minimum period that SCLK is in logic low state                                                                    |

| DS                | 15    | ns   | Setup time between data and rising edge of SCLK                                                                   |

| DH                | 10    | ns   | Hold time between data and rising edge of SCLK                                                                    |

| DV                | 14    | ns   | Maximum time delay between the falling edge of SCLK and the output data valid for a read operation in 4-wire mode |

| Н                 | 10    | ns   | Hold time between the rising edge of $\overline{\text{CS}}$ and the last falling edge of SCLK                     |

| S                 | 10    | ns   | Setup time between the falling edge of $\overline{\text{CS}}$ and the rising edge of SCLK                         |

| Z                 | 12    | ns   | Maximum time delay between $\overline{\text{CS}}$ deactivation and SDIO bus return to high impedance              |

| ACCESS            | 14    | ns   | Maximum time delay between the falling edge of SCLK and the output data valid for a read operation in 3-wire mode |

Figure 80. SPI Register Timing Diagram for Analog Devices, Inc., Standard SPI, MSB First

Figure 81. Timing Diagram for Analog Devices Standard SPI Register Read, 4-Wire Mode

analog.com Rev. 0 | 27 of 54

## THEORY OF OPERATION

## SUPPLY SEQUENCING

The ADMV4540 is designed so that all supply pins can be turned on simultaneously. If the different supply pins cannot be turned on simultaneously, turn on VCC3P3\_DIG at 3.3 V before all other supply pins. An arbitrary power supply sequence is not recommended. Contact Analog Devices Sales if additional guidance is needed.

## **SPI START-UP SEQUENCES**

The ADMV4540 SPI settings require the SPI to be configured for the required mode of operation. On startup, the SPI mode must be selected along with the RF input port and baseband filter settings.

## Soft Reset and 3-Wire and 4-Wire Mode

To set the soft reset in 3-wire mode, take the following steps:

- 1. Write 0x81 to Register 0x000.

- 2. Write 0x00 to Register 0x000.

To set the soft reset in 4-wire mode, take the following steps:

- 1. Write 0x81 to Register 0x000.

- 2. Write 0x18 to Register 0x000.

# **Baseband and Common-Mode Recommended Settings**

Program the following registers to the recommended settings listed after performing a soft reset and choosing either 3-wire or 4-wire mode:

- 1. Write 0xCC to Register 0x133.

- 2. Write 0xFF to Register 0x134.

- 3. Write 0xFF to Register 0x135.

- 4. Write 0x4e to Register 0x10A.

- **5.** Write 0x4e to Register 0x10B.

## **RF Input Port Selection**

Either RF\_IN1 or RF\_IN2 must be selected at startup. Both inputs cannot be selected at the same time.

For the RF\_IN1 input port, write 0x3E to Register 0x100, and for the RF\_IN2 input port, write 0x3D to Register 0x100.

## **Baseband Filter Settings**

One of the four filter settings must be selected at startup, which include the following:

- ► For the baseband filter 125 MHz setting, write 0x00 to Register 0x013C.

- ► For the baseband filter 250 MHz setting, write 0x05 to Register 0x013C.

- ▶ For the baseband filter 500 MHz setting, write 0x0A to Register 0x013C.

► For the baseband filter bypass setting, write 0x0F to Register 0x013C.

# FREQUENCY UPDATE SEQUENCE

After the SPI start-up sequences (see the SPI Start-Up Sequences section) are performed, the output frequency can be updated by programming the registers as detailed in LO Lock Write Sequence When DOUBLER\_EN = 0 section and the LO Lock Write Sequence for DOUBLER\_EN = 1 section.

# LO Synthesizer Calculations

The following are the LO synthesizer calculations required to calculate the register values when doing a frequency update as indicated in the LO Lock Write Sequence When DOUBLER\_EN = 0 section and the LO Lock Write Sequence for DOUBLER EN = 1 section:

Reference Multiplier

$$= \frac{(1 + DOUBLER\_EN)}{((1 + REF\_DIV\_2) \times (R\_DIV))}$$

(1)

$$f_{PFD} = \text{Reference Multiplier} \times f_{REF}$$

(2)

$$VCO\ Frequency = \frac{LO\ Frequency}{1.5} \tag{3}$$

$$N = \frac{VCO Frequency}{f_{PED}} \tag{4}$$

$$INT\_DIV = Integer \ Value \ of \ N$$

(5)

$$FRACValue Required = N - INT_DIV$$

(6)

$$FRAC1$$

$Required = FRAC Value$  (7)  $Required \times MOD1$

$$FRAC1 = Integer Value of FRAC1$$

$Required$  (8)

If FRAC1 is 0, SD\_EN\_OUT\_OFF = 1, SD\_EN\_FRAC0 = 0, and BICP = 0.

If FRAC1 is not 0, SD\_EN\_OUT\_OFF = 0, SD\_EN\_FRAC0 = 0, and BICP= 4 or 130.

$$FRAC1$$

Remainder =  $FRAC1$  Required (9)

$$FRAC2 = FRAC1 \quad Remainder \times MOD2$$

(10)

$$VCO\ Frequency = \frac{LO\ Frequency}{1.5} \tag{11}$$

where.

For DOUBLER\_EN = 1, CP\_CURRENT = 4. For DOUBLER\_EN = 0, CP\_CURRENT = 8.

R DIV = 1.

REF DIV 2 = 0.

$f_{RFF} = 50 \text{ MHz}.$

MOD1 = is a 24-bit primary modulus with a fixed value of  $2^{24}$  = 16777216.

analog.com Rev. 0 | 28 of 54

#### THEORY OF OPERATION

MOD2 is a programmable, 14-bit auxiliary fractional modulus (2 to 16,383) with a recommended value = 3.

# LO Lock Write Sequence When DOUBLER\_EN = 0

Use the following write sequence to update the LO frequency when DOUBLER\_EN = 0 and use the values calculated in LO Synthesizer Calculations section.

- **1.** Write 0xA1 to Register 0x22D.

- 2. Write 0x02 to Register 0x240.

- 3. If the LO frequency is greater than 18.6 GHz, write 0x04 to Register 0x217, and if the LO frequency is less than or equal to 18.6 GHz, write 0x01 to Register 0x217.

- **4.** Write the BICP value to Register 0x22F.

- 5. Write the CP CURRENT value to Register 0x022E.

- **6.** Write the R DIV value to Register 0x20C.

- 7. Write 0x04 to Register 0x20E.

- **8.** Write the SD\_EN\_OUT\_OFF value and the SD\_EN\_FRACO value to Register 0x22A.

- Write the MOD2 value to Register 0x208 to Register 0x209 from the highest to the lowest register.

- **10.** Write the FRAC2 value to Register 0x233 and Register 0x234 from the highest to the lowest register.

- **11.** Write 0x01 to Register 0x20B.

- **12.** Write 0x0A to Register 0x22B.

- **13.** Write the FRAC1 value to Register 0x202 to Register 0x204 from the highest to the lowest register.

- **14.** Write the INT\_DIV value to Register 0x200 and Register 0x201 from the highest to the lowest register.

- **15.** Read Register 0x24D. If Register 0x24D data is 0x01, the synthesizer is locked.

# LO Lock Write Sequence for DOUBLER\_EN = 1

Use the following write sequence to update the LO frequency when DOUBLER\_EN = 1 and use the values calculated in LO Synthesizer Calculations section. Note that, DOUBLER\_EN = 1 is the recommended mode for optimal integrated phase noise performance.

- 1. Write 0x80 to Register 0x21F.

- Lock the device with DOUBLER\_EN = 0 based on the LO synthesizer calculations (see the LO Synthesizer Calculations section) and the procedure outlined in LO Lock Write Sequence When DOUBLER\_EN = 0 section.

- **3.** Verify that the synthesizer is locked by reading Register 0x24D. If the readback is 0x01, the synthesizer is locked.

- Write 0xC0 to Register 0x21F.

- Go through the LO synthesizer calculations (see the LO Synthesizer Calculations section) again based on DOUBLER\_EN =

Make note of these values for the next steps.

- 6. Write 0xA1 to Register 0x022D.

- 7. Write 0x02 to Register 0x240.

- **8.** If the LO frequency is greater than 18.6 GHz, write 0x04 to Register 0x217, and if the LO frequency is less than or equal to 18.6 GHz, write 0x01 to Register 0x217.

- 9. Write the BICP value to Register 0x22F.

- 10. Write the CP\_CURRENT value to Register 0x022E. Program with half the value used in Step 2 to keep the loop gain constant.

- **11.** Write the R DIV value to Register 0x20C.

- **12.** Write 0x0C to Register 0x20E.

- **13.** Write the SD\_EN\_OUT\_OFF value and the SD\_EN\_FRACO value to Register 0x22A.

- **14.** Write the MOD2 value to Register 0x208 to Register 0x209 from the highest to the lowest register.

- **15.** Write the FRAC2 value to Register 0x233 and Register 0x234 from the highest to the lowest register.

- **16.** Write 0x01 to Register 0x20B.

- **17.** Write 0x0A to Register 0x22B.

- **18.** Write the FRAC1 value to Register 0x202 to Register 0x204 from the highest to the lowest register.

- **19.** Write the INT\_DIV value to Register 0x200 and Register 0x201 from the highest to the lowest register.

- **20.** Read Register 0x24D. If Register 0x24D data is 0x01, the synthesizer is locked.

- 21. Write 0x80 to Register 0x21F.

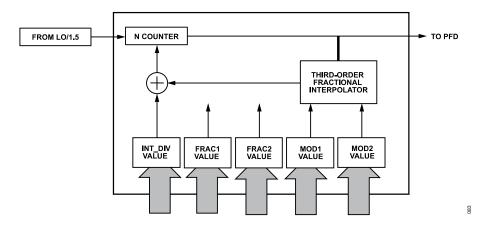

## **N COUNTER**

The N counter allows a division ratio in the PLL feedback path from the LO. Note that the signal from the N counter is multiplied by 1.5 to achieve the LO frequency at the input of the mixer. The division ratio is determined by using the Integer N (INT\_DIV), fractional-N (FRAC1 and FRAC2), and modulus (MOD2) values that this counter comprises. The applicable registers for setting the INT\_DIV, FRAC1, MOD2, and FRAC2 values are Register 0x200 to Register 0x204, Register 0x208 to Register 0x209 and Register 0x233 to Register 0x234.

analog.com Rev. 0 | 29 of 54

#### THEORY OF OPERATION

Figure 82. N Counter Functional Block Diagram

# **DOUBLE BUFFERED REGISTERS**