# 24 GHz to 29.5 GHz Transmitter/Receiver, Dual Polarization Beamformer

#### **FEATURES**

▶ RF frequency range: 24 GHz to 29.5 GHz

▶ 16 configurable transmit channels

▶ 16 configurable receive channels

▶ Dual polarization: 8 horizontal and 8 vertical channels

▶ Fast TDD switching time using external pins

$\blacktriangleright$  Matched, 50  $\Omega$ , single-ended RF inputs and outputs

▶ Integrated transmitter power detectors and temperature sensor

▶ High resolution, 6-bit vector modulators for phase control

▶ High resolution, 6-bit and 5-bit DVGAs for amplitude control

Gain compensation over temperature

Memory for 256 beam positions

Single power supply required: 3.3 V with on-chip LDO regulator for 1.8 V

▶ Adjustable power modes for power consumption reduction

▶ 3-wire or 4-wire SPI supporting up to a 61.44 MHz SPI clock speed

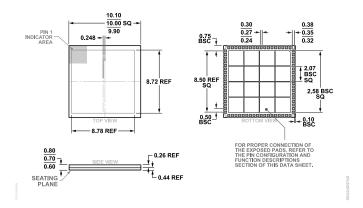

▶ 72-terminal, 10 mm × 10 mm, LGA package

#### **APPLICATIONS**

- ▶ 5G applications

- Broadband communication

- ▶ Test and measurement

- Aerospace and defense

#### **GENERAL DESCRIPTION**

The ADMV4821 is a silicon germanium (SiGe), 24 GHz millimeterwave (mmW) to 29.5 GHz mmW 5G beamformer. The RF IC is highly integrated and contains 16 independent channels with both transmit and receive functionality. The ADMV4821 supports eight horizontal and eight vertical polarized antennas via the independent RFV and RFH inputs/outputs common pins.

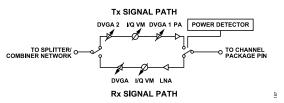

In transmit mode, both the RFV and RFH input signals are split via two independent 1:8 power splitters and pass through the eight, independent, corresponding transmit channels. In this mode, each channel includes a vector modulator (VM) to control the phase and two digital variable gain amplifiers (DVGAs) to control the amplitude.

In receive mode, input signals pass through two sets of eight receive channels (either vertical or horizontal) and are combined via one independent 8:1 combiner connected to the RFV pin and one independent 8:1 combiner connected to the RFH pin. In this mode, each channel includes a VM to control the phase and a DVGA to control the amplitude.

The VM provides a full 360° phase adjustment range in either transmit or receive mode. The VM provides six bits of resolution for 5.625° phase steps.

In transmit mode, the total DVGA dynamic range adjustment range is 32.4 dB. The DVGAs provide five bits or six bits of resolution, resulting in 1.0 dB or 0.5 dB amplitude steps, respectively.

In receive mode, the DVGA allows for 17.1 dB of dynamic range adjustment. The DVGA also provides six bits of resolution, resulting in 0.5 dB amplitude steps. The DVGAs provide a flat phase response across the full gain range.

The transmitter channels contain individual power detectors to detect and calibrate the gain for each channel as well as the channel to channel gain mismatch. Directly connect the ADMV4821 RF ports to a patch antenna to create a dual polarization mmW 5G subarray.

Users can program the ADMV4821 by using a 3-wire or 4-wire serial port interface (SPI). The integrated on-chip low dropout (LDO) regulator generates the 1.8 V supply for the SPI circuitry to reduce the number of supply domains required. There are various SPI modes to enable fast startup and control during normal operation.

Users can either set the amplitude and phase for each channel individually or program multiple channels simultaneously by using the on-chip memory for beamforming. The on-chip memory can store up to 256 beam positions, which can be allocated for either transmitter or receiver mode in any combination. In addition, four address pins allow SPI control of up to 16 devices on the same serial lines. Dedicated horizontal and vertical polarization load pins also synchronize all devices in the same array. There is a horizontal and vertical polarization transmit and receive mode control pins (TRXV and TRXH) for fast switching between transmit and receive mode.

The ADMV4821 comes in a compact, thermally enhanced 10 mm × 10 mm, RoHs compliant land grid array (LGA) package. The ADMV4821 operates over the -40°C to +95°C case temperature range. This LGA package allows users to heat-sink the ADMV4821 from the top side of the package for the most efficient thermal heatsinking and to allow flexible antenna placement on the opposite side of the printed circuit board (PCB).

Throughout the figures in this data sheet, Tx means transmit (or transmitter) and Rx means receive (or receiver).

Rev. B

DOCUMENT FEEDBACK

TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features1                                     | Recommended Gain/Phase Coefficient   |    |

|-----------------------------------------------|--------------------------------------|----|

| Applications1                                 | Initialization                       | 28 |

| General Description1                          | RF Signal Path                       | 28 |

| Functional Block Diagram3                     | Phase and Gain Control               | 28 |

| Specifications4                               | Transmit and Receive Control         | 29 |

| Transmitter Specifications4                   | Power Detectors                      | 29 |

| Receiver Specifications5                      | Temperature Sensor                   | 30 |

| Serial Port Interface (SPI)6                  | ADC Operation                        | 30 |

| Absolute Maximum Ratings8                     | Bias Control for Various Power Modes | 30 |

| Thermal Resistance8                           | Memory Access                        | 30 |

| ESD Caution8                                  | Calibration                          | 31 |

| Pin Configuration and Function Descriptions 9 | SPI Information                      | 31 |

| Typical Performance Characteristics12         | Applications Information             | 35 |

| Transmit Mode12                               | Powering the ADMV4821                | 35 |

| Power Detector Performance17                  | Heat Sink Selection                  | 35 |

| Receiver to Transmitter Switching Speed       | Performance at Various Power Modes   | 35 |

| and Amplitude/Phase Settling Time 18          | Transmit Mode Error Vector Magnitude |    |

| Receive Mode21                                | (EVM) Performance                    | 36 |

| Transmitter to Receiver Switching Speed       | Outline Dimensions                   | 38 |

| and Amplitude/Phase Settling Time25           | Ordering Guide                       | 38 |

| Theory of Operation28                         | Evaluation Boards                    | 38 |

|                                               |                                      |    |

# **REVISION HISTORY**

3/2022—Revision B: Initial Version

analog.com Rev. B | 2 of 38

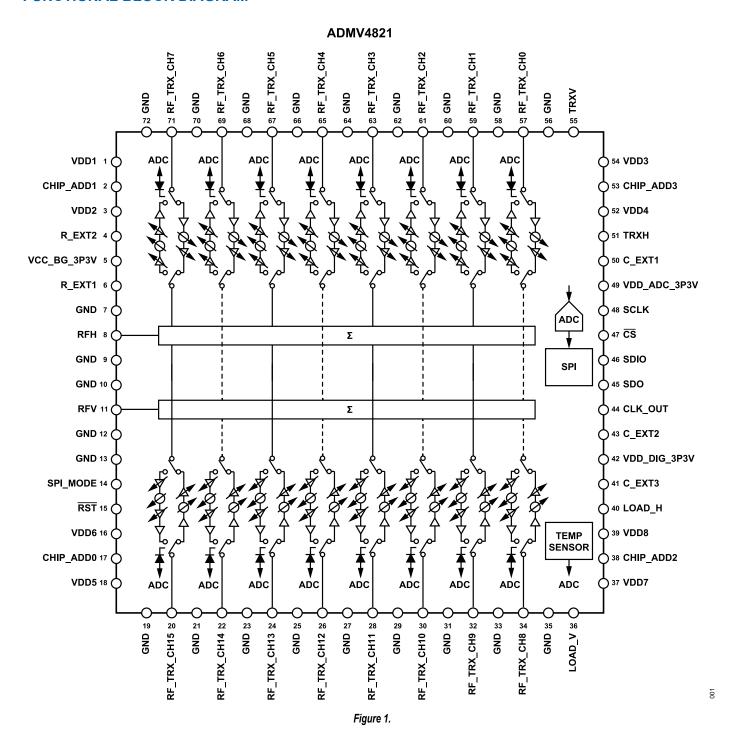

### **FUNCTIONAL BLOCK DIAGRAM**

analog.com Rev. B | 3 of 38

## **SPECIFICATIONS**

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6 = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set SPI values based on the start-up sequence described in the AN-2021 Application Note, *ADMV4801/ADMV4821 SPI Application Note* and the case temperature, which is referenced to the topside of package (T<sub>C</sub>), = 25°C, unless otherwise noted.

Table 1.

| Parameter                                 | Test Conditions/Comments | Min  | Тур           | Max  | Unit    |

|-------------------------------------------|--------------------------|------|---------------|------|---------|

| OPERATING CONDITIONS                      |                          |      |               |      |         |

| RF Range                                  |                          | 24   |               | 29.5 | GHz     |

| Operating Temperature                     |                          | -40  |               | +95  | °C      |

| POWER SUPPLY                              |                          |      |               |      |         |

| Voltage Range                             |                          | 3.15 | 3.3           | 3.45 | V       |

| Transmit Mode                             | 16 channels active       |      |               |      |         |

| VDDx <sup>1</sup> Current                 |                          |      | 1826          |      | mA      |

| VCC_BG_3P3V Current                       |                          |      | 45            |      | mA      |

| VDD_DIG_3P3V Current                      |                          |      | 9             |      | mA      |

| VDD_ADC_3P3V Current                      |                          |      | 16            |      | mA      |

| Receive Mode                              | 16 channels active       |      |               |      |         |

| VDDx Current                              |                          |      | 998           |      | mA      |

| VCC_BG_3P3V Current                       |                          |      | 45            |      | mA      |

| VDD_DIG_3P3V Current                      |                          |      | 8             |      | mA      |

| VDD ADC 3P3V Current                      |                          |      | 15            |      | mA      |

| TRANSMITTER AND RECEIVER SECTION          |                          |      |               |      |         |

| Impedance                                 |                          |      | 50            |      | Ω       |

| Number of Channels                        |                          |      | 16            |      |         |

| Phase Accuracy                            | Using 6 bits of control  |      | 5.625         |      | Degrees |

| Gain Variation                            | Due to phase setting     |      | 0.6           | 1    | dB      |

| Phase RMS Error                           |                          |      | 1.5           | 3    | Degrees |

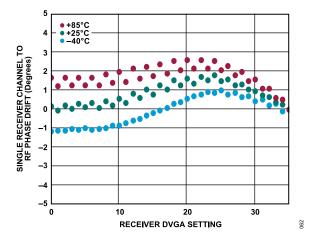

| Phase Variation                           | Due to gain setting      |      | ±2.0          |      | Degrees |

| Gain Flatness                             |                          |      |               |      |         |

| Across 100 MHz Bandwidth                  |                          |      | ±0.13         |      | dB      |

| Across 800 MHz Bandwidth                  |                          |      | ±0.35         |      | dB      |

| Across 3000 MHz Bandwidth                 |                          |      | ±0.7          |      | dB      |

| Gain/Phase Settling Time                  |                          |      | 30            |      | ns      |

| Time Division Duplex (TDD) Switching Time |                          |      |               |      |         |

| Transmitter Off to Receiver On            |                          |      | 120           |      | ns      |

| Receiver Off to Transmitter On            |                          |      | 60            |      | ns      |

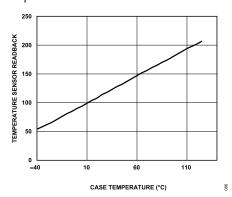

| TEMPERATURE SENSOR                        |                          |      | - <del></del> |      | -       |

| Range                                     |                          | -40  |               | +125 | °C      |

| Slope                                     | LSB in decimal           | .0   | 0.93          |      | LSB/°C  |

| Resolution                                |                          |      | 8             |      | Bits    |

<sup>&</sup>lt;sup>1</sup> Where x = 1 to 8.

#### TRANSMITTER SPECIFICATIONS

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6 = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set SPI values based on the start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note, and T<sub>C</sub> = 25°C, unless otherwise noted.

Measurements performed in transmit mode, RF amplitude = -20 dBm, and the channel Digital Variable Gain Amplifier 1 (DVGA 1) and common Digital Variable Gain Amplifier 2 (DVGA 2) set to the maximum gain.

analog.com Rev. B | 4 of 38

## **SPECIFICATIONS**

Table 2.

| Parameter                                | Test Conditions/Comments  | Min | Тур  | Max | Unit |

|------------------------------------------|---------------------------|-----|------|-----|------|

| TRANSMITTER                              |                           |     |      |     |      |

| Output 1 dB Compression Point (P1dB)     |                           | 14  | 17.5 |     | dBm  |

| Output Third-Order Intercept Point (IP3) | 100 MHz tone spacing      |     | 26   |     | dBm  |

| Gain                                     | Includes splitting losses | 16  | 25   |     | dB   |

| Gain Dynamic Range                       |                           | 30  | 32.4 |     | dB   |

| Gain Step                                |                           |     |      |     |      |

| DVGA 1                                   | Using 6 bits of control   |     | 0.5  |     | dB   |

| DVGA 2                                   | Using 5 bits of control   |     | 1.0  |     | dB   |

| Gain Error                               |                           |     | ±0.1 |     | dB   |

| Input Return Loss                        |                           |     | -10  |     | dB   |

| Output Return Loss                       |                           |     | -8   |     | dB   |

| Noise Figure                             |                           |     | 27.3 |     | dB   |

| Power Consumption per Channel            |                           |     |      |     |      |

| Nominal Power Mode                       |                           |     |      |     |      |

| At P1dB                                  | Output power = 17.5 dBm   |     | 0.66 |     | W    |

| Backoff from P1dB                        | Output power = 0 dBm      |     | 0.40 |     | W    |

| Medium Power Mode                        |                           |     |      |     |      |

| At P1dB                                  | Output power = 17.5dBm    |     | 0.57 |     | W    |

| Backoff from P1dB                        | Output power = 0 dBm      |     | 0.32 |     | W    |

| Low Power Mode                           |                           |     |      |     |      |

| At P1dB                                  | Output power = 15.9 dBm   |     | 0.44 |     | W    |

| Backoff from P1dB                        | Output power = 0 dBm      |     | 0.24 |     | W    |

| POWER DETECTOR                           |                           |     |      |     |      |

| Output Power Range                       |                           |     | ±15  |     | dBm  |

| Power Detector Range <sup>1</sup>        |                           |     | 30   |     | dB   |

| Resolution                               |                           |     | 6    |     | Bits |

<sup>1</sup> Refer to the AN-2021 Application Note, *ADMV4801/ADMV4821 SPI Application Note* (contact Analog Devices at mmwave5G@analog.com) for more details regarding specific ranges that can be programmed via the SPI.

### **RECEIVER SPECIFICATIONS**

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6 = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set SPI values based on the start-up sequence described in the AN-2021 Application Note, *ADMV4801/ADMV4821 SPI Application Note*, and T<sub>C</sub> = 25°C, unless otherwise noted.

Measurements performed in receive mode, RF amplitude = -30 dBm, and receiver DVGA set to maximum gain, unless otherwise noted.

Table 3.

| Parameter                                    | Test Conditions/Comments | Min   | Тур   | Max | Unit |

|----------------------------------------------|--------------------------|-------|-------|-----|------|

| RECEIVER                                     |                          |       |       |     |      |

| Single-Channel Noise Figure                  |                          |       |       |     |      |

| 8 Channels Active, Single Input              |                          |       | 15.2  |     | dB   |

| 1 Channel Active <sup>1</sup> , Single Input |                          |       | 6.2   |     | dB   |

| Input P1dB                                   |                          | -23.5 | -20.5 |     | dBm  |

| Input IP3                                    | 100 MHz tone spacing     |       | -12.7 |     | dBm  |

| Electrical Gain (EG) <sup>2</sup>            | 8 channels active        |       | 20.6  |     | dB   |

| Single Channel Gain (SCG)                    | 1 channel active         | 5     | 11.6  |     | dB   |

| Gain Dynamic Range                           |                          |       | 17.1  |     | dB   |

| Gain Step                                    | Using 6 bits of control  |       | 0.5   |     | dB   |

analog.com Rev. B | 5 of 38

## **SPECIFICATIONS**

Table 3.

| Parameter                     | Test Conditions/Comments | Min | Тур  | Max | Unit |

|-------------------------------|--------------------------|-----|------|-----|------|

| Gain Step Error               |                          |     | ±0.1 |     | dB   |

| Input Return Loss             |                          |     | -11  |     | dB   |

| Output Return Loss            |                          |     | -10  |     | dB   |

| Power Consumption Per Channel |                          |     |      |     |      |

| Nominal Power Mode            |                          |     | 0.22 |     | W    |

| Medium Power Mode             |                          |     | 0.21 |     | W    |

| Low Power Mode                |                          |     | 0.16 |     | W    |

The single-channel noise figure is calculated based on the following equations: SCNFM = SCNF1 + 10 × log(M), where SCNFM is the single-channel noise figure measured when M channels are active.

# **SERIAL PORT INTERFACE (SPI)**

Refer to the SPI Information section for full details.

Table 4. Logic Input and Output Specifications

| Parameter                                                         | Test Conditions/Comments                                                                                      | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| LOGIC INPUTS                                                      | CHIP_ADD0 to CHIP_ADD3, SPI_MODE, $\overline{RST}$ , LOAD_ $x^1$ , SDIO, $\overline{CS}$ , SCLK, and $TRXx^1$ |      |     |      |      |

| Input Voltage                                                     |                                                                                                               |      |     |      |      |

| High (V <sub>IH</sub> )                                           |                                                                                                               | 1.2  | 1.8 |      | V    |

| Low (V <sub>IL</sub> )                                            |                                                                                                               |      | 0   | 0.63 | V    |

| High and Low Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) |                                                                                                               |      | 7   |      | μA   |

| Input Capacitance (C <sub>IN</sub> )                              |                                                                                                               |      | 0.4 |      | pF   |

| LOGIC OUTPUTS                                                     | CLK_OUT, SDO, and SDIO                                                                                        |      |     |      |      |

| Output Voltage                                                    |                                                                                                               |      |     |      |      |

| High (V <sub>OH</sub> )                                           | Output high current (I <sub>OH</sub> ) = 8 mA                                                                 | 1.35 |     |      | V    |

| Low (V <sub>OL</sub> )                                            | Output low current (I <sub>OL</sub> ) = 8 mA                                                                  |      |     | 0.45 | V    |

<sup>&</sup>lt;sup>1</sup> Where x is either V or H.

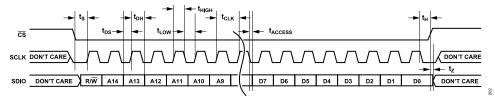

**Table 5. Timing Specifications**

| Parameter                              | Test Conditions/Comments           |  | Тур | Max   | Unit |

|----------------------------------------|------------------------------------|--|-----|-------|------|

| Maximum SCLK Rate (t <sub>SCLK</sub> ) |                                    |  |     |       |      |

| SRAM Write                             |                                    |  |     | 61.44 | MHz  |

| SRAM Read                              |                                    |  |     | 61.44 | MHz  |

| Register Write                         |                                    |  |     | 61.44 | MHz  |

| Register Read                          |                                    |  |     | 30.72 | MHz  |

|                                        | With first data bit double clocked |  |     | 61.44 | MHz  |

| Pulse Width                            |                                    |  |     |       |      |

| SCLK Minimum Pulse Width               |                                    |  |     |       |      |

| High (t <sub>HIGH</sub> )              |                                    |  | 4   |       | ns   |

| Low (t <sub>LOW</sub> )                |                                    |  | 4   |       | ns   |

| CS Minimum Pulse Width High            | Between two writes or reads        |  | 3   |       | ns   |

| RST Minimum Pulse Width Low            |                                    |  | 2.5 |       | ns   |

| LOAD_V Minimum Pulse Width             |                                    |  |     |       |      |

analog.com Rev. B | 6 of 38

<sup>&</sup>lt;sup>2</sup> Electrical gain (EG) is calculated based on EG = SCG + SPL where SCG is the single channel gain when one channel is active and SPL, the ideal splitter network losses, is represented by 10 × log(N) where N is the number of summations. In the case of the ADMV4821, SPL is 9 due to the 8:1 sum splitter. The EG value is typically used for cascade noise figure and gain calculations. Coherent gain (CG) is calculated based on CG = EG + 10 × log(M), where EG is the electrical gain and M is the number of channels active.

# **SPECIFICATIONS**

Table 5. Timing Specifications

| Parameter                                        | Test Conditions/Comments         | Min | Тур | Max | Unit |

|--------------------------------------------------|----------------------------------|-----|-----|-----|------|

| High                                             |                                  |     | 5.5 |     | ns   |

| Low                                              |                                  |     | 3.1 |     | ns   |

| Minimum Setup Time                               |                                  |     |     |     |      |

| $\overline{\text{CS}}$ to SCLK (t <sub>S</sub> ) |                                  |     | 1.0 |     | ns   |

| SDIO to SCLK (t <sub>DS</sub> )                  |                                  |     | 1.0 |     | ns   |

| Minimum Hold Time                                |                                  |     |     |     |      |

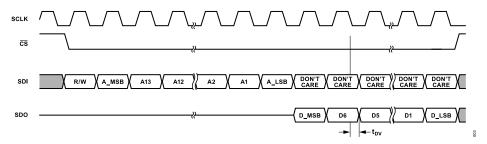

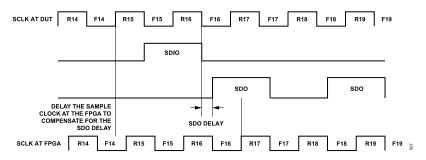

| SCLK to $\overline{CS}$ (t <sub>H</sub> )        | Falling SCLK edge, see Figure 80 |     | 8.0 |     | ns   |

| SCLK to SDIO (t <sub>DH</sub> )                  |                                  |     | 2.8 |     | ns   |

| SDO                                              |                                  |     |     |     |      |

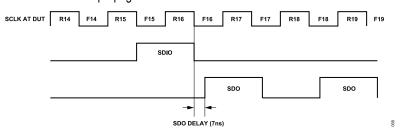

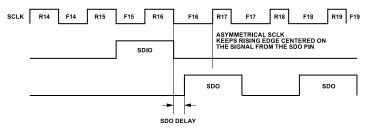

| Data Valid, SDO to SCLK (t <sub>DV</sub> )       | Falling SCLK edge, see Figure 81 |     | 6.0 |     | ns   |

| Rise Time                                        | 10% to 90%                       |     | 2.0 |     | ns   |

| Fall Time                                        | 90% to 10%                       |     | 2.6 |     | ns   |

analog.com Rev. B | 7 of 38

#### **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Parameter                                                  | Rating                    |

|------------------------------------------------------------|---------------------------|

| Supply Voltage                                             |                           |

| VDD1 to VDD8, VDD_DIG_3P3V, VCC_BG_3P3V,                   | 3.6 V                     |

| VDD_ADC_3P3V                                               |                           |

| Digital Input/Output Voltages                              |                           |

| Logic Input Low                                            | 0.63 V                    |

| Logic Input High                                           | 1.95 V                    |

| RF Input Power                                             | 0 dBm                     |

| Maximum Junction Temperature                               | 125°C                     |

| Maximum Power Dissipation <sup>1</sup>                     | 25 W                      |

| Lifetime at Maximum Junction Temperature (T <sub>J</sub> ) | 1 × 10 <sup>6</sup> hours |

| Operating Case Temperature Range                           | -40°C to +95°C            |

| Storage Temperature Range                                  | -55°C to +150°C           |

| Lead Temperature (Soldering 60 sec)                        | 260°C                     |

| Moisture Sensitivity Level (MSL) Rating <sup>2</sup>       | MSL3                      |

| Topside Force Ratings                                      |                           |

| One Time Maximum                                           | 5.44 kgf                  |

| Constant                                                   | 1 kgf                     |

| Electrostatic Discharge (ESD) Sensitivity                  | _                         |

| Human Body Model (HBM)                                     | 3.5 kV                    |

| Field Induced Charged Device Model (FICDM)                 | 750 V                     |

$<sup>^{1}</sup>$  The maximum power dissipation is a theoretical number calculated by (T  $_{J}$  –  $95^{\circ}\text{C})/\theta_{JC}$   $_{TOP}.$

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Only use  $\theta_{JA}$  and  $\theta_{JC}$  to compare the thermal performance of different packages when all test conditions listed are similar to the JEDEC specifications. Otherwise, use  $\Psi_{JT}$  and  $\Psi_{JB}$  to calculate the device junction temperature using the following equations:

$$T_J = (P \times \Psi_{JT}) + T_{TOP} \tag{1}$$

where:

P is the total power dissipation in the chip (W).

$\Psi_{JT}$  is the junction to top thermal characterization number.

$T_{TOP}$  is the package top temperature (°C).

$T_{TOP}$  is measured at the top center of the package.

$$T_I = \left(P \times \Psi_{IB}\right) + T_{BOARD} \tag{2}$$

where:

P is the total power dissipation in the chip (W).

$\Psi_{JB}$  is the junction to board thermal characterization number.  $T_{BOARD}$  is the board temperature measured on the midpoint of the longest side of the package no more than 1 mm from the edge of the package body (°C).

As stated in JEDEC51-12, only use Equation 1 and Equation 2 when no heat sink or heat spreader is present. When a heat sink or heat spreader is added, use  $\theta_{\text{JC\_TOP}}$  to estimate or calculate the junction temperature. The preferred heat sink or heat spreader placement for this device is to contact the topside of the exposed pad of the device to the heatsink using an appropriate thermal grease to efficiently reduce the junction temperature of the device.

Table 7. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}^2$ | $\theta_{\text{JC\_TOP}}^3$ | $\Psi_{\text{JT}}^{4}$ | $\Psi_{JB}^{5}$ | Unit |

|---------------------------|-----------------|-----------------------------|------------------------|-----------------|------|

| CC-72-3                   |                 |                             |                        |                 |      |

| Transmit Mode             | 16.0            | 0.9                         | 1.3                    | 2.7             | °C/W |

| Receive Mode              | 17.3            | 1.5                         | 1.9                    | 3.2             | °C/W |

The thermal resistance values specified in Table 7 are simulated based on JEDEC specifications, unless specified otherwise, and must be used in compliance with JESD51-12.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. B | 8 of 38

<sup>&</sup>lt;sup>2</sup> Based on IPC/JEDEC J-STD-20 MSL classifications.

$<sup>^2~\</sup>theta_{\text{JA}}$  is the junction to ambient thermal resistance in a natural convection, JEDEC environment.

$<sup>^{3}</sup>$   $\theta_{\text{JC TOP}}$  is the junction to case (top) JEDEC thermal resistance.

$<sup>^4</sup>$   $\Psi_{JT}$  is the junction to top JEDEC thermal characterization parameter.

$<sup>^{5}</sup>$   $\Psi_{JB}$  is the junction to board JEDEC thermal characterization parameter.

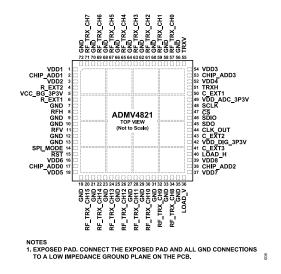

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

Table 8. Pin Function Descriptions

| Pin No.                                                                                  | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                        | VDD1        | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement. |

| 2                                                                                        | CHIP_ADD1   | Chip Select Address Bit 1 Input (1.8 V CMOS Logic). Together with the CHIP_ADD0, CHIP_ADD2, and CHIP_ADD3 pins, this pin selects one of 16 devices to accept serial instructions and data. Under normal operating conditions, connect this pin to ground.                                                                                                                                                               |

| 3                                                                                        | VDD2        | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement. |

| 4                                                                                        | R_EXT2      | On-Chip LDO Regulator Circuit Connection. This pin requires a 1.1 k $\Omega$ series, <1%, high precision resistor connected to ground.                                                                                                                                                                                                                                                                                  |

| 5                                                                                        | VCC_BG_3P3V | 3.3 V Power Supply for Variable Gain Amplifier (VGA) Chip Band Gap Circuit. Place a 10 μF shunt capacitor to ground. Then, place a 0.01 μF shunt capacitor to ground, and then a shunt 100 pF capacitor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement.                                                                                                     |

| 6                                                                                        | R_EXT1      | On-Chip LDO Regulator Circuit Connection. This pin requires a 1.1 kΩ series, <1%, high precision resistor connected to ground.                                                                                                                                                                                                                                                                                          |

| 7, 9, 10, 12, 13, 19, 21, 23, 25, 27, 29, 31, 33, 35, 56, 58, 60, 62, 64, 66, 68, 70, 72 | GND         | Ground. Tie all ground pins and grounds together to a low impedance plane on the PCB.                                                                                                                                                                                                                                                                                                                                   |

| 8                                                                                        | RFH         | Horizontal RF Input or Output. This pin is internally dc-coupled to ground and matches to 50 $\Omega$ , single-ended.                                                                                                                                                                                                                                                                                                   |

| 11                                                                                       | RFV         | Vertical RF Input or Output. This pin is internally dc-coupled to ground and matches to 50 $\Omega$ , single-ended.                                                                                                                                                                                                                                                                                                     |

| 14                                                                                       | SPI_MODE    | Standard SPI Mode Select Pin. Set this pin to logic low for standard SPI mode operation. For more information regarding the various SPI modes, refer to the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note.                                                                                                                                                                                           |

| 15                                                                                       | RST         | SPI Reset is an Active Low Interface. Connect this pin to logic high for normal operation. The SPI logic is 1.8 V.                                                                                                                                                                                                                                                                                                      |

| 16                                                                                       | VDD6        | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement. |

| 17                                                                                       | CHIP_ADD0   | Chip Select Address Bit 0 Input (1.8 V CMOS Logic). Together with the CHIP_ADD1, CHIP_ADD2, and CHIP_ADD3 pins, this pin selects one of 16 devices to accept serial instructions and data. Under normal operating conditions, connect this pin to ground.                                                                                                                                                               |

analog.com Rev. B | 9 of 38

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 8. Pin Function Descriptions

| Pin No. | Mnemonic     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | VDD5         | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement.                                                               |

| 20      | RF_TRX_CH15  | Antenna Connection for Horizontal Channel 15 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                                                                                    |

| 22      | RF_TRX_CH14  | Antenna Connection for Vertical Channel 14 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to 50 Ω, single-ended.                                                                                                                                                                                                                                                                                                                              |

| 24      | RF_TRX_CH13  | Antenna Connection for Horizontal Channel 13 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                                                                                    |

| 26      | RF_TRX_CH12  | Antenna Connection for Vertical Channel 12 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                                                                                      |

| 28      | RF_TRX_CH11  | Antenna Connection for Horizontal Channel 11 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                                                                                    |

| 30      | RF_TRX_CH10  | Antenna Connection for Vertical Channel 10 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                                                                                      |

| 32      | RF_TRX_CH9   | Antenna Connection for Horizontal Channel 9 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                                                                                     |

| 34      | RF_TRX_CH8   | Antenna Connection for Vertical Channel 8 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                                                                                       |

| 36      | LOAD_V       | Transmitter and Receiver Registers Load Input (1.8 V CMOS Logic) for Vertical Polarity Channels. Transitioning this pin from a logic low to a logic high three times causes values written to the corresponding registers, written since the last such load operation, to be fully loaded by the device.                                                                                                                                                                              |

| 37      | VDD7         | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement.                                                               |

| 38      | CHIP_ADD2    | Chip Select Address Bit 2 Input (1.8 V CMOS Logic). Together with the CHIP_ADD0, CHIP_ADD1, and CHIP_ADD3 pins, this pin selects one of 16 devices to accept serial instructions and data. Under normal operating conditions, connect this pin to ground.                                                                                                                                                                                                                             |

| 39      | VDD8         | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement.                                                               |

| 40      | LOAD_H       | Transmitter and Receiver Registers Load Input (1.8 V CMOS Logic) for Horizontal Polarity Channels. Transitioning this pin from a logic low to a logic high three times causes values written to the corresponding registers, written since the last such load operation, to be fully loaded by the device.                                                                                                                                                                            |

| 41      | C_EXT3       | On-Chip 1.8 V Reference LDO Regulator Circuit Decoupling Pin Connection. This pin requires a series 3.3 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor connected to ground. The voltage measured from this pin to ground is 1.8 V.                                                                                                                                                                                                                                          |

| 42      | VDD_DIG_3P3V | 3.3 V Power Supply for the LDO Regulator Circuit for Digital Circuitry. Place a 10 μF shunt capacitor to ground. Then, place a 0.01 μF shunt capacitor to ground, and then a 100 pF shunt capacitor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement.                                                                                                                                                                       |

| 43      | C_EXT2       | On-Chip 1.8 V Reference LDO Circuit Decoupling Pin Connection. This pin requires a series 3.3 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor connected to ground. The voltage measured from this pin to ground is 1.8 V.                                                                                                                                                                                                                                                    |

| 44      | CLK_OUT      | SPI Clock Output (1.8 V CMOS Logic). Under normal operating conditions, connect this pin to ground.                                                                                                                                                                                                                                                                                                                                                                                   |

| 45      | SDO          | SPI Serial Data Output (1.8 V CMOS Logic). In 4-wire SPI mode, this pin is an SPI serial data output. In 3-wire SPI mode, this pin is unused and may be connected to ground.                                                                                                                                                                                                                                                                                                          |

| 46      | SDIO         | SPI Serial Data Input/Output (1.8 V CMOS Logic). In 4-wire SPI mode, this pin is an SPI serial data input. In 3-wire SPI mode, this pin is an SPI serial data input/output.                                                                                                                                                                                                                                                                                                           |

| 47      | <u>cs</u>    | SPI Chip Select Input (1.8 V CMOS Logic). Serial communication is enabled when the $\overline{\text{CS}}$ pin is set to logic low. When the $\overline{\text{CS}}$ pin is set to logic high at the end of the serial data command, the data written to the register address is given in the command. For more information about using the $\overline{\text{CS}}$ pin in the various SPI modes, refer to the AN-2021 Application Note, <i>ADMV4801/ADMV4821 SPI Application Note</i> . |

analog.com Rev. B | 10 of 38

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 8. Pin Function Descriptions

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 48      | SCLK            | SPI Serial Clock Input (1.8 V CMOS Logic). In write mode, data is sampled on the rising edge of the SCLK pin. Durin read cycle, output data changes at the falling edge of the SCLK pin.                                                                                                                                                                                                                                 |  |

| 49      | VDD_ADC_3P3V    | 3.3 V Power Supply for the LDO Regulator Circuit for Digital Circuitry. Place a 10 µF shunt capacitor to ground. Then, place a 0.01 µF shunt capacitor to ground, and then a 100 pF shunt capacitor to ground as close as possible to this pin Refer to the ADMV4821-EVALZ user guide for component placement.                                                                                                           |  |

| 50      | C_EXT1          | On-Chip 1.8 V Reference LDO Regulator Circuit Decoupling Pin Connection. This pin requires a series 3.3 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor connected to ground. The voltage measured from this pin to ground is 1.8 V.                                                                                                                                                                             |  |

| 51      | TRXH            | Transmit and Receive Mode Select Input for TDD Operation (1.8 V CMOS Logic). A rising edge of an input signal transitions the mode from receive to transmit. A falling edge of an input signal transitions the mode from transmit to receive. On startup, set this pin to logic low to ensure that the ADMV4821 starts up in receive mode.                                                                               |  |

| 52      | VDD4            | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement.  |  |

| 53      | CHIP_ADD3       | Chip Select Address Bit 3 Input (1.8 V CMOS Logic). Together with the CHIP_ADD0, CHIP_ADD1, and CHIP_ADD2 pins, this pin selects one of 16 devices to accept serial instructions and data. Under normal operating conditions, connect this pin to ground.                                                                                                                                                                |  |

| 54      | VDD3            | 3.3 V Power Supply for the RF Signal Paths. Place a 10 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground. Then, place a 1 $\mu$ F shunt capacitor in series with a 6.04 $\Omega$ resistor to ground, and then a shunt 0.15 $\mu$ F capacitor in series with a 1.5 $\Omega$ resistor to ground, as close as possible to this pin. Refer to the ADMV4821-EVALZ user guide for component placement. |  |

| 55      | TRXV            | Transmit and Receive Mode Select Input for TDD Operation of Vertical Polarity Channels (1.8 V CMOS Logic). A rising edge of an input signal transitions the mode from receive to transmit. A falling edge of an input signal transitions the mode from transmit to receive. On startup, set this pin to logic low to ensure the ADMV4821 starts in receive mode.                                                         |  |

| 57      | RF_TRX_CH0      | Antenna Connection for Vertical Channel 0 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                          |  |

| 59      | RF_TRX_CH1      | Antenna Connection for Horizontal Channel 1 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                        |  |

| 61      | RF_TRX_CH2      | Antenna Connection for Vertical Channel 2 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to 50 Ω, single-ended.                                                                                                                                                                                                                                                                  |  |

| 63      | RF_TRX_CH3      | Antenna Connection for Horizontal Channel 3 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                        |  |

| 65      | RF_TRX_CH4      | Antenna Connection for Vertical Channel 4 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                          |  |

| 67      | RF_TRX_CH5      | Antenna Connection for Horizontal Channel 5 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                        |  |

| 69      | RF_TRX_CH6      | Antenna Connection for Vertical Channel 6 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to 50 Ω, single-ended.                                                                                                                                                                                                                                                                  |  |

| 71      | RF_TRX_CH7      | Antenna Connection for Horizontal Channel 7 Input or Output in Either Receive or Transmit Mode. This pin is dc-coupled and matched to $50 \Omega$ , single-ended.                                                                                                                                                                                                                                                        |  |

|         | EPAD (backside) | Exposed Pad. Connect the exposed pad and all GND connections to a low impedance ground plane on the PCB.                                                                                                                                                                                                                                                                                                                 |  |

analog.com Rev. B | 11 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

#### TRANSMIT MODE

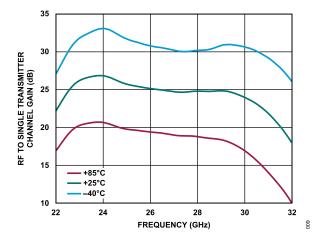

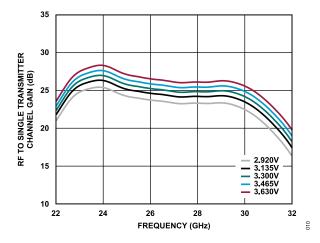

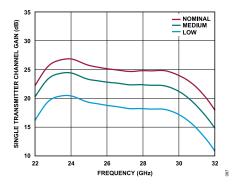

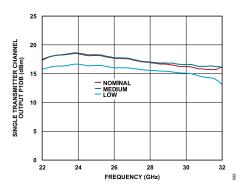

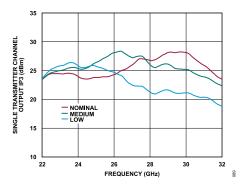

VDD1 to VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set SPI values based on the start-up sequence in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note,  $T_C = 25^{\circ}C$ , RF amplitude = -20 dBm, and set DVGA 1 and DVGA 2 to the maximum gain, unless otherwise noted.

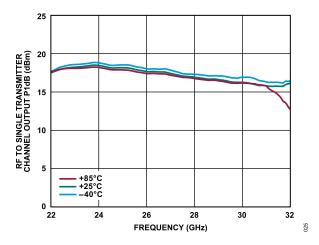

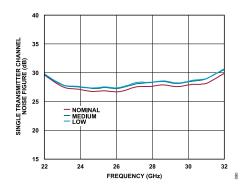

Figure 3. RF to Single Transmitter Channel Gain vs. Frequency at Various Temperatures at Maximum Gain

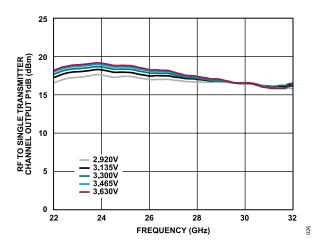

Figure 4. RF to Single Transmitter Channel Gain vs. Frequency at Various Supply Voltages at Maximum Gain

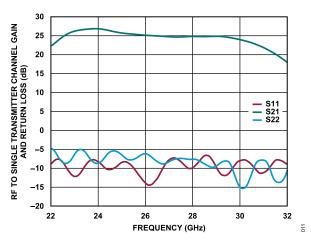

Figure 5. RF to Single Transmitter Channel Gain and Return Loss vs. Frequency at Maximum Gain

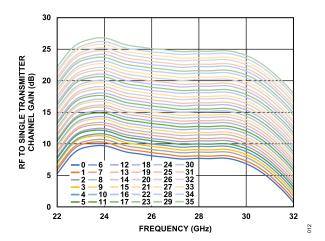

Figure 6. RF to Single Transmitter Channel Gain vs. Frequency at Various DVGA 1 Settings from 0 to 35

analog.com Rev. B | 12 of 38

### **TYPICAL PERFORMANCE CHARACTERISTICS**

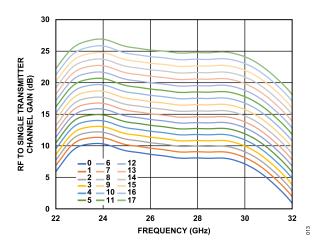

Figure 7. RF to Single Transmitter Channel Gain vs. Frequency at Various DVGA 2 Settings from 0 to 17

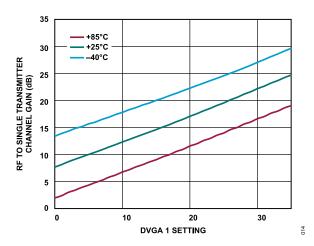

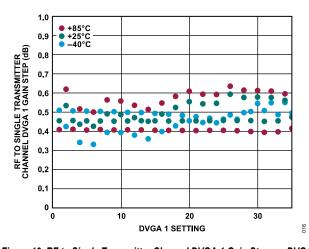

Figure 8. RF to Single Transmitter Channel Gain vs. DVGA 1 Setting from 0 to 35 over Various Temperatures at 27 GHz

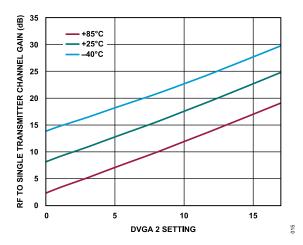

Figure 9. RF to Single Transmitter Channel Gain vs. DVGA 2 Setting from 0 to 17 over Various Temperatures at 27 GHz

Figure 10. RF to Single Transmitter Channel DVGA 1 Gain Step vs. DVGA 1 Setting from 0 to 35 over Various Temperatures at 27 GHz

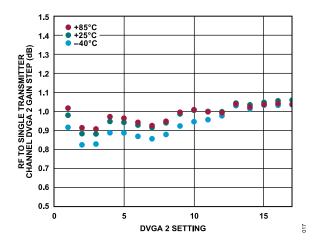

Figure 11. RF to Single Transmitter Channel DVGA 2 Gain Step vs. DVGA 2 Setting from 0 to 17 over Various Temperatures at 27 GHz

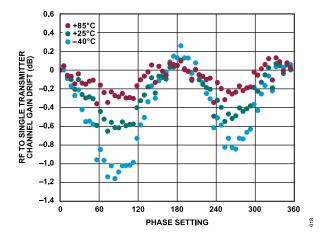

Figure 12. RF to Single Transmitter Channel Gain Drift vs. Phase Setting from 0° to 360° over Temperature at 27 GHz, Set to Maximum Gain

analog.com Rev. B | 13 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

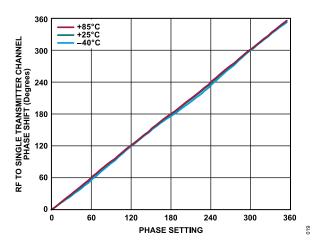

Figure 13. RF to Single Transmitter Channel Phase Shift vs. Phase Setting from 0° to 360° over Various Temperatures at 27 GHz, Set to Maximum Gain

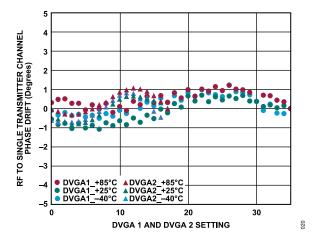

Figure 14. RF to Single Transmitter Channel Phase Drift vs. DVGA 1 Setting from 0 to 35 and DVGA 2 Setting from 0 to 17, over Various Temperatures at 27 GHz

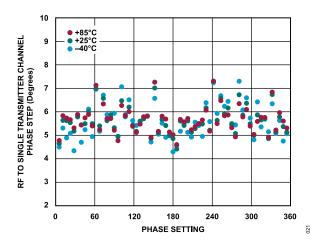

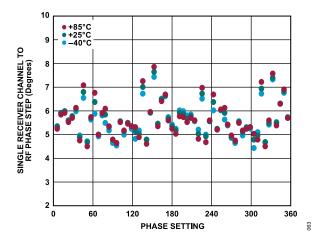

Figure 15. RF to Single Transmitter Channel Phase Step vs. Phase Setting from 0° to 360° over Various Temperatures at 27 GHz, Set to Maximum Gain, Nominal Step 5.625°

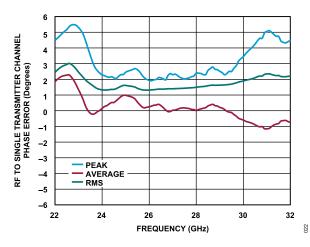

Figure 16. RF to Single Transmitter Channel Phase Error vs. Frequency for Peak, Average, and RMS Error

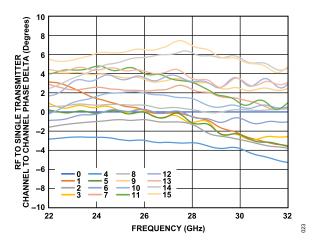

Figure 17. RF to Single Transmitter Channel to Channel Phase Delta vs. Frequency at Maximum Gain, Where Numbers in Legend Are Channel Numbers

Figure 18. RF to Single Transmitter Channel to Channel Gain Delta vs.

Frequency at Maximum Gain, Where Numbers in Legend Are Channel

Numbers

analog.com Rev. B | 14 of 38

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 19. RF to Single Transmitter Channel Output P1dB vs. Frequency at Various Temperatures at Maximum Gain

Figure 20. RF to Single Transmitter Channel Output P1dB vs. Frequency at Various Supply Voltages at Maximum Gain

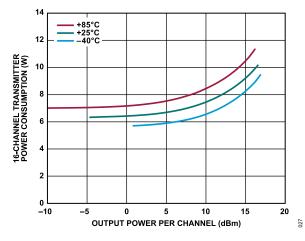

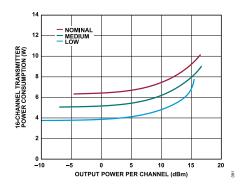

Figure 21. 16-Channel Transmitter Power Consumption vs. Output Power per Channel at Various Temperatures at Maximum Gain

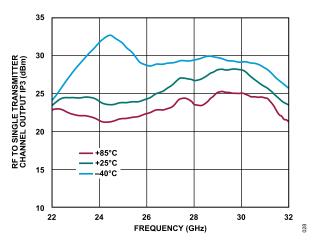

Figure 22. RF to Single Transmitter Channel Output IP3 vs. Frequency at Various Temperatures at Maximum Gain

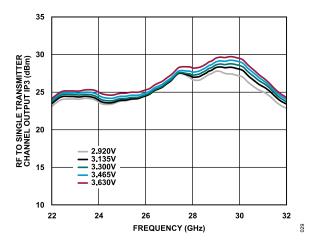

Figure 23. RF to Single Transmitter Channel Output IP3 vs. Frequency at Various Supply Voltages at Maximum Gain

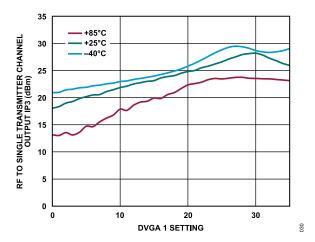

Figure 24. RF to Single Transmitter Channel Output IP3 vs. DVGA 1 Setting from 0 to 35 over Various Temperatures at 27 GHz

analog.com Rev. B | 15 of 38

### **TYPICAL PERFORMANCE CHARACTERISTICS**

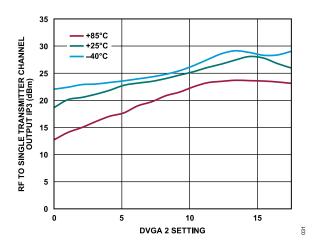

Figure 25. RF to Single Transmitter Channel Output IP3 vs. DVGA 2 Setting from 0 to 17 over Various Temperatures at 27 GHz

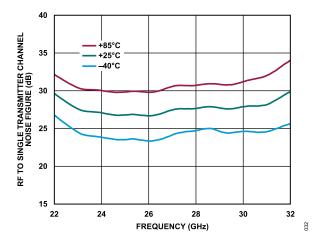

Figure 26. RF to Single Transmitter Channel Noise Figure vs. Frequency at Various Temperatures at Maximum Gain

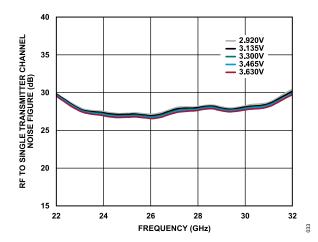

Figure 27. RF to Single Transmitter Channel Noise Figure vs. Frequency at Various Supply Voltages at Maximum Gain

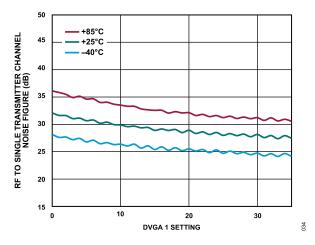

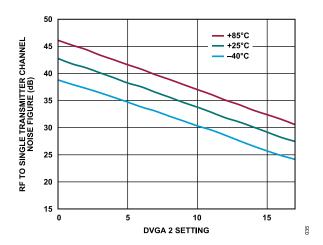

Figure 28. RF to Single Transmitter Channel Noise Figure vs. DVGA 1 Setting from 0 to 35 over Various Temperatures at 27 GHz

Figure 29. RF to Single Transmitter Channel Noise Figure vs. DVGA 2 Setting from 0 to 17 over Various Temperatures at 27 GHz

analog.com Rev. B | 16 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

#### POWER DETECTOR PERFORMANCE

VDD1 to VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set the SPI values based on the start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note,  $T_C = 25^{\circ}C$ , RF amplitude = -20 dBm, and set DVGA 1 and DVGA 2 to the maximum gain, unless otherwise noted. The detector range settings are written to Register 0x027, Bits[6:0].

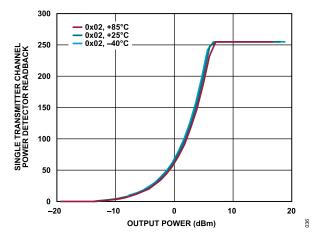

Figure 30. Single Transmitter Channel Power Detector Readback vs. Output Power at Various Temperatures at 27 GHz, Set to Maximum Gain, Detector Range Set to 0x02

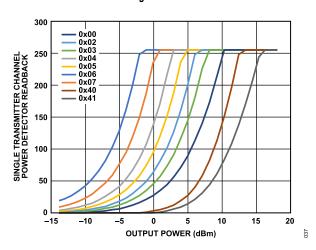

Figure 31. Single Transmitter Channel Power Detector Readback vs. Output Power at Various Detector Range Settings at 27 GHz, Set to Maximum Gain

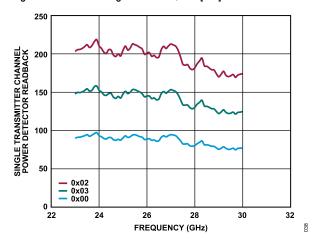

Figure 32. Single Transmitter Channel Power Detector Readback vs.

Frequency at Various Detector Range Settings, Set to Maximum Gain, Input

Power = 5 dBm

analog.com Rev. B | 17 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

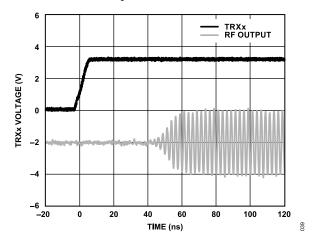

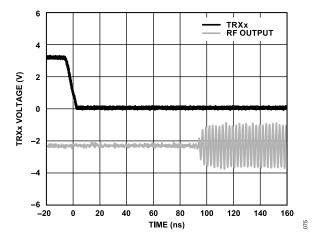

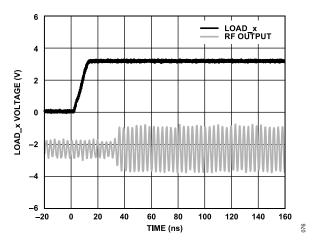

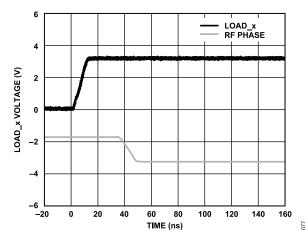

## RECEIVER TO TRANSMITTER SWITCHING SPEED AND AMPLITUDE/PHASE SETTLING TIME

VDD1 to VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set the SPI values based on the start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application No

Figure 33. Receiver to Transmitter Mode Switching Time

Figure 34. Gain Settling Time

Figure 35. RF Phase Settling Time

analog.com Rev. B | 18 of 38

#### TYPICAL PERFORMANCE CHARACTERISTICS

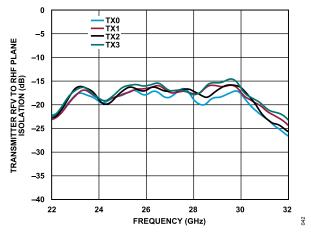

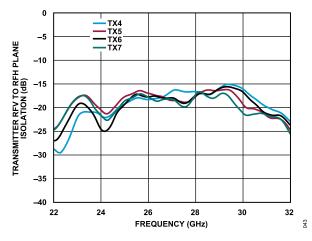

#### Transmitter RFV to RFH Plane Isolation Performance

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6 = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set the SPI values based on the start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note, and  $T_C = 25^{\circ}C$ , unless otherwise noted. Measurements are performed in receive mode, RF amplitude = -30 dBm, and set DVGA 1 and DVGA 2 to maximum gain, unless otherwise noted.

Figure 36. Transmitter RFV to RFH Plane Isolation vs. Frequency for Transmitter 0 (TX0), Transmitter 1 (TX1), Transmitter 2 (TX2), and Transmitter 3 (TX3)

Figure 37. Transmitter RFV to RFH Plane Isolation vs. Frequency for Transmitter 2 (TX4), Transmitter 5 (TX5), Transmitter 6 (TX6), and Transmitter 7 (TX7)

Figure 38. Transmitter RFV to RFH Plane Isolation vs. Frequency for Transmitter 8 (TX8), Transmitter 9 (TX9), Transmitter 10 (TX10), and Transmitter 11 (TX11)

Figure 39. Transmitter RFV to RFH Plane Isolation vs. Frequency for Transmitter 12 (TX12), Transmitter 13 (TX13), Transmitter 14 (TX14), and Transmitter 15 (TX15)

analog.com Rev. B | 19 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

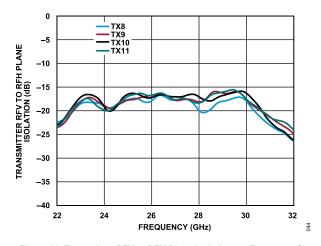

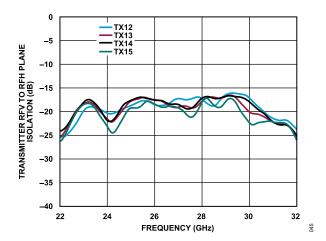

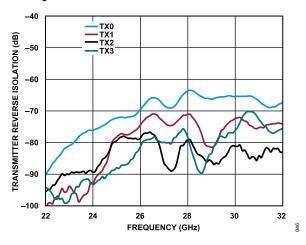

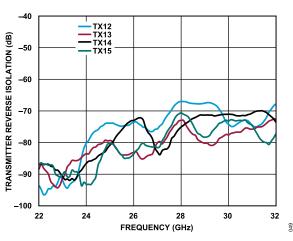

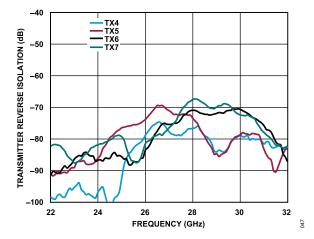

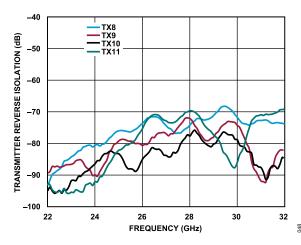

### **Transmitter Reverse Isolation Performance**

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6 = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set the SPI values based on the start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note, and T<sub>C</sub> = 25°C, unless otherwise noted. Measurements are performed in receive mode, RF amplitude = -30 dBm, and set DVGA 1 and DVGA 2 to maximum gain, unless otherwise noted.

Figure 40. Transmitter Reverse Isolation vs. Frequency for TX0 to TX3

Figure 43. Transmitter Reverse Isolation vs. Frequency for TX12 to TX15

Figure 41. Transmitter Reverse Isolation vs. Frequency for TX4 to TX7

Figure 42. Transmitter Reverse Isolation vs. Frequency for TX8 to TX11

analog.com Rev. B | 20 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

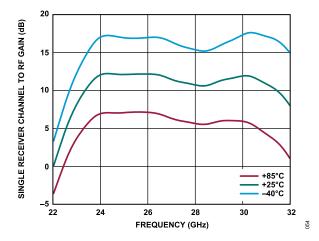

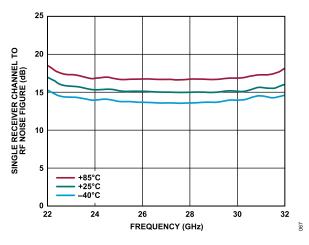

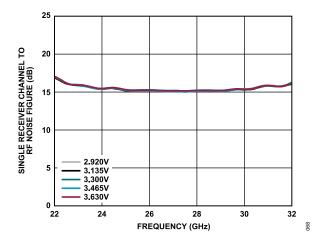

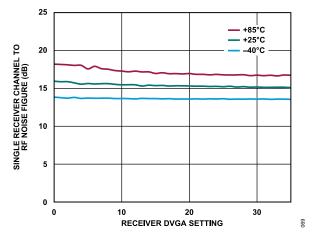

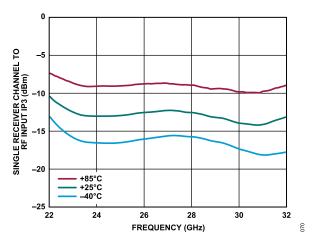

#### **RECEIVE MODE**

VDD1 to VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set the SPI values based on the start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note,  $T_C = 25^{\circ}C$ , RF amplitude = -30 dBm, and set the receiver DVGA to maximum gain, unless otherwise noted.

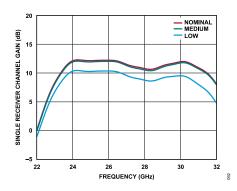

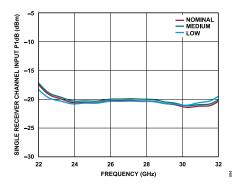

Figure 44. Single Receiver Channel to RF Gain vs. Frequency at Various Temperatures at Maximum Gain

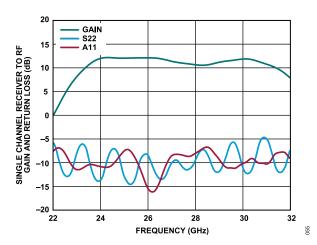

Figure 45. Single Channel Receiver to RF Gain and Return Loss vs.

Frequency at Maximum Gain

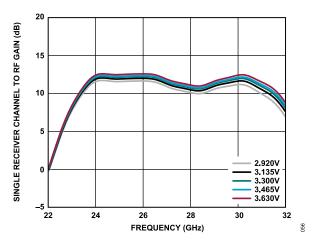

Figure 46. Single Receiver Channel to RF Gain vs. Frequency at Various Supply Voltages at Maximum Gain

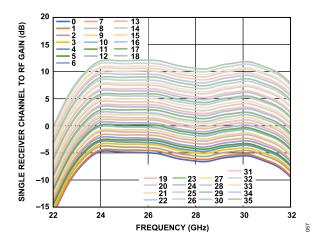

Figure 47. Single Receiver Channel to RF Gain vs. Frequency at Various Receiver DVGA Settings from 0 to 35

analog.com Rev. B | 21 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

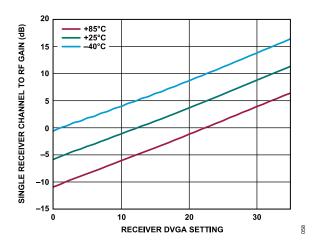

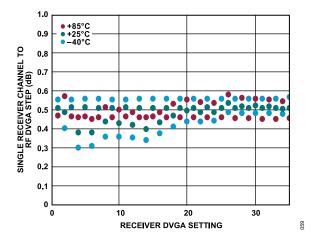

Figure 48. Single Receiver Channel to RF Gain vs. Receiver DVGA Setting from 0 to 35 over Various Temperatures at 27 GHz

Figure 49. Single Receiver Channel to RF DVGA Step vs. Receiver DVGA Setting from 0 to 35 over Various Temperatures at 27 GHz

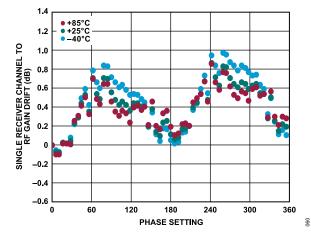

Figure 50. Single Receiver Channel to RF Gain Drift vs. Phase Setting from 0° to 360° over Temperature at 27 GHz, Set to Maximum Gain

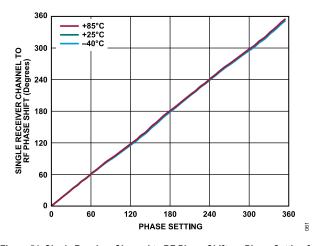

Figure 51. Single Receiver Channel to RF Phase Shift vs. Phase Setting from 0° to 360° over Various Temperatures at 27 GHz, Set to Maximum Gain

Figure 52. Single Receiver Channel to RF Phase Drift Setting from 0 to 35 over Various Temperatures at 27 GHz

Figure 53. Single Receiver Channel to RF Phase Step vs. Phase Setting from 0° to 360° over Various Temperatures at 27 GHz, Set to Maximum Gain, Nominal Step = 5.625°

analog.com Rev. B | 22 of 38

### TYPICAL PERFORMANCE CHARACTERISTICS

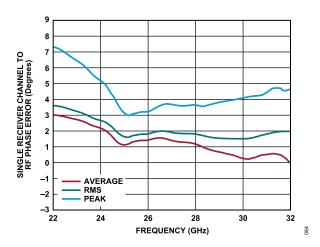

Figure 54. Single Receiver Channel to RF Phase Error vs. Frequency for Peak, Average, and RMS Error

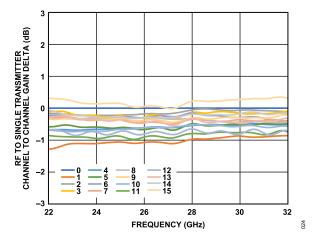

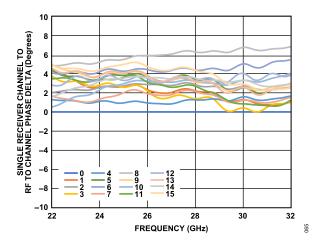

Figure 55. Single Receiver Channel to RF to Channel Phase Delta vs. Frequency at Maximum Gain, Where Numbers in Legend Are Channel Numbers

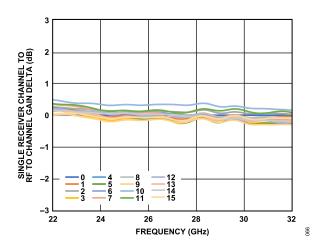

Figure 56. Single Receiver Channel to RF to Channel Gain Delta vs.

Frequency at Maximum Gain, Where Numbers in Legend Are Channel

Numbers

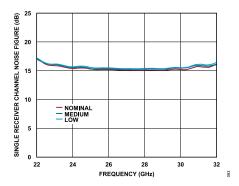

Figure 57. Single Receiver Channel to RF Noise Figure vs. Frequency at Various Temperatures at Maximum Gain

Figure 58. Single Receiver Channel to RF Noise Figure vs. Frequency at Various Supply Voltages at Maximum Gain

Figure 59. Single Receiver Channel to RF Noise Figure vs. Receiver DVGA Setting from 0 to 35 over Various Temperatures at 27 GHz

analog.com Rev. B | 23 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

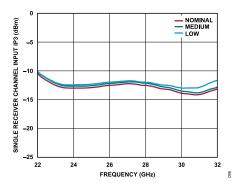

Figure 60. Single Receiver Channel to RF Input IP3 vs. Frequency at Various

Temperatures at Maximum Gain

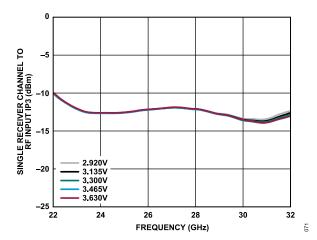

Figure 61. Single Receiver Channel to RF Input IP3 vs. Frequency at Various Supply Voltages at Maximum Gain

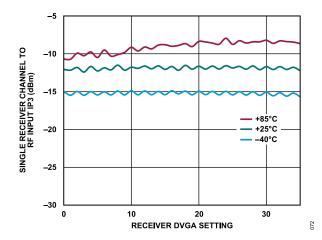

Figure 62. Single Receiver Channel to RF Input IP3 vs. Receiver DVGA Setting from 0 to 35 over Various Temperatures at 27 GHz

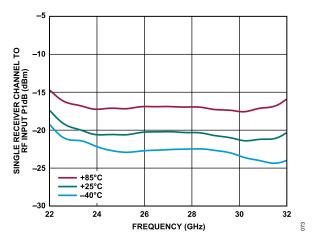

Figure 63. Single Receiver Channel to RF Input P1dB vs. Frequency at Various Temperatures at Maximum Gain

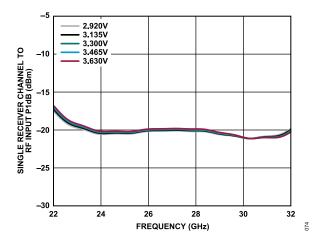

Figure 64. Single Receiver Channel to RF Input P1dB vs. Frequency at Various Supply Voltages at Maximum Gain

analog.com Rev. B | 24 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

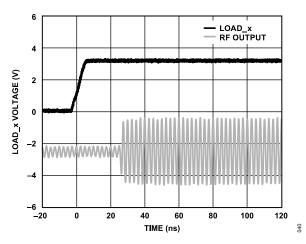

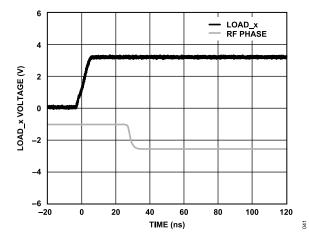

# TRANSMITTER TO RECEIVER SWITCHING SPEED AND AMPLITUDE/PHASE SETTLING TIME

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6= = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set the SPI values based on the start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note,  $T_C = 25^{\circ}C$ , RF amplitude = -30 dBm, and set the receiver DVGA to maximum gain, unless otherwise noted.

Figure 65. Transmitter to Receiver Mode Switching Time

Figure 66. Gain Settling Time

Figure 67. RF Phase Settling Time

analog.com Rev. B | 25 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

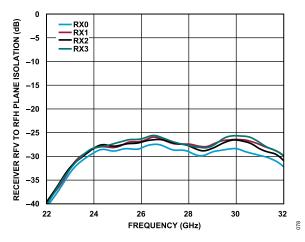

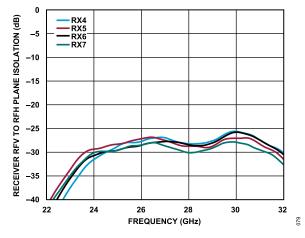

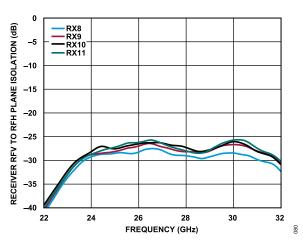

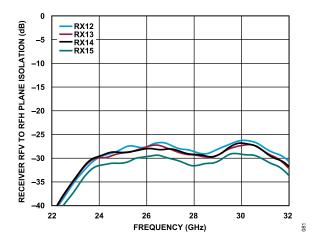

#### Receiver RFV to RFH Plane Isolation Performance

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6 = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set the SPI values based on start-up sequence described in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note, and  $T_C = 25^{\circ}C$ , unless otherwise noted. Measurements performed in receive mode, RF amplitude = -30 dBm, set the receiver DVGA to maximum gain, unless otherwise noted.

Figure 68. Receiver RFV to RFH Plane Isolation vs. Frequency for Receiver 0 (RX0), Receiver 1 (RX1), Receiver 2 (RX2), and Receiver 3 (RX3)

Figure 69. Receiver RFV to RFH Plane Isolation vs. Frequency for Receiver 4 (RX4), Receiver 5 (RX5), Receiver 6 (RX6), and Receiver 7 (RX7)

Figure 70. Receiver RFV to RFH Plane Isolation vs. Frequency for Receiver 8 (RX8), Receiver 9 (RX9), Receiver 10 (RX10), and Receiver 11 (RX11)

Figure 71. Receiver RFV to RFH Plane Isolation vs. Frequency for Receiver 12 (RX12), Receiver 13 (RX13), Receiver (RX14), and Receiver 15 (RX15)

analog.com Rev. B | 26 of 38

## TYPICAL PERFORMANCE CHARACTERISTICS

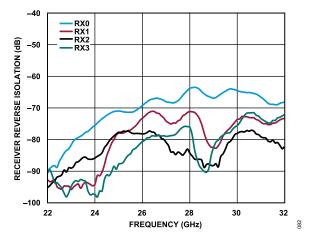

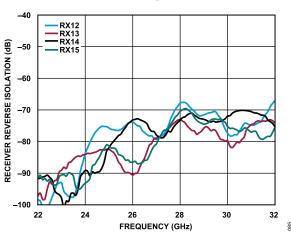

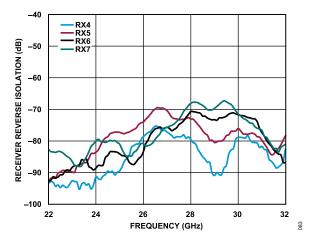

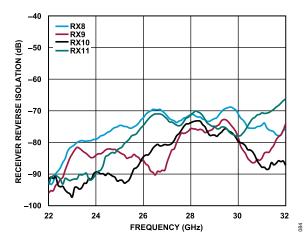

### **Receiver Reverse Isolation Performance**

VDD1 = VDD2 = VDD3 = VDD4 = VDD5 = VDD6 = VDD7 = VDD8 = VCC\_BG\_3P3V = VDD\_DIG\_3P3V = VDD\_ADC\_3P3V = 3.3 V, set SPI values based on start-up sequence in the AN-2021 Application Note, ADMV4801/ADMV4821 SPI Application Note, and  $T_C$  = 25°C, unless otherwise noted. Measurements performed in receive mode, RF amplitude = -30 dBm, DVGA set to maximum gain, unless otherwise noted.

Figure 72. Receiver Reverse Isolation vs. Frequency for RX0 to RX3

Figure 75. Receiver Reverse Isolation vs. Frequency for RX12 to RX15

Figure 73. Receiver Reverse Isolation vs. Frequency for RX4 to RX7

Figure 74. Receiver Reverse Isolation vs. Frequency for RX8 to RX11

analog.com Rev. B | 27 of 38

Data Sheet ADMV482'

#### THEORY OF OPERATION

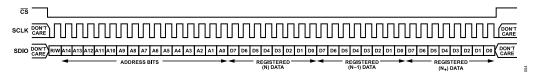

The ADMV4821 is a highly integrated beamformer optimized for mmW 5G applications in the 24 GHz to 29.5 GHz frequency range. See Figure 1 for a functional block diagram of the device. The 16 independent channels of the ADMV4821 support both transmit and receive functions. The odd numbered channels are connected internally on chip to the horizontal polarization signal path of the RFH input/output pin. The even numbered channels are connected internally on chip to the vertical polarization signal path to the RFV input/output pin.

# RECOMMENDED GAIN/PHASE COEFFICIENT INITIALIZATION

There are two methods for setting the gain and phase of the individual channels selected to provide efficient start-up time with minimal overhead based on the use case. One method is to use the beam pointer register, Register 0x081. This register recalls user defined beam positions from the SRAM. The beam pointer loads the beam steering values to the 16 channels. The LOAD\_x pin is toggled three times to write the gain and phase setting from the memory to the selected channels. The load feature ensures that the phase and gain settings are applied to the selected channels at the same time.

Use the optional bypass mode to bypass beam pointer mode. This mode allows users to configure and debug the phase and gain settings for each channel before implementing beam pointer mode. The user can change and apply gain and phase directly to each individual channel using the channel phase and gain SRAM, common gain SRAM, and transmit and receive SRAM. The LOAD\_x pin is toggled three times to write the gain and phase setting from the memory to the selected channels. The load feature ensures that the phase and gain settings are applied to selected channels at the same time. Refer to the AN-2021 Application Note, *ADMV4801/ADMV4821 SPI Application Note* for detailed information.

#### **RF SIGNAL PATH**

The primary function of the chip is to accurately set the relative phase and gain of each channel so that the signals coherently add in the desired direction. The individual element gain control can compensate for many impairments presented to the chip in normal operation. Such impairments include temperature variation, chip to chip or channel to channel variation, supporting external circuitry variation for phase and gain, and the ability to enable tapering for the beam to achieve low-side lobe levels.

All 16 channel signal paths are identical to provide symmetrical performance between channels, which reduces the amount of phase and amplitude calibration to allow TDD operation. As shown in Figure 77, each transmit channel includes a DVGA 2, an in phase and quadrature (I/Q) VM, a DVGA 1, a power amplifier (PA), a power detector, and two single-pole, double throw (SPDT) switches. Each receive channel includes a low noise amplifier (LNA), an I/Q VM, a channel DVGA, and two SPDT switches. The switches select between transmit and receive paths. These paths connect the RF signal paths to the corresponding package input/output pins (RFV, RFH, and 16 channels) through a passive combining and splitting network.

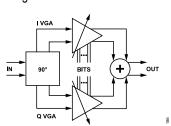

#### PHASE AND GAIN CONTROL

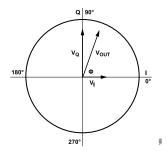

Phase control is implemented using an I/Q VM architecture, as shown in Figure 76. The incoming signal is split in equal amplitude, in-phase and quadrature (I and Q) signals that are amplified independently by two identical, biphase VGAs and summed at the output to generate the required phase shift. Each VGA is controlled by 7 independent bits, 6 bits for amplitude control and 1 bit for polarity control, for a total of 14 bits per phase shifter. The vector modulator output voltage amplitude ( $V_{OUT}$ ) and phase shift ( $\Phi$ ) are given by the following equations:

$$V_{OUT} = \sqrt{V_Q^2 + V_I^2}$$

$$\Phi = \arctan \frac{V_Q}{V_I}$$

#### where:

$V_Q$  is the output voltage of the Q channel VGA.  $V_I$  is the output voltage of the I channel VGA.

Figure 76. I/Q VM Phase Shift Block Diagram

Figure 77. Transmit and Receive Channel Functional Block Diagram

analog.com Rev. B | 28 of 38

#### THEORY OF OPERATION

When evaluating the arctangent function, the proper phase quadrant must be selected. The signs of  $V_I$  and  $V_Q$  determine the phase quadrant according to the following parameters:

- ▶ If  $V_I$  and  $V_Q$  are both negative, the phase shift is between  $0^\circ$  and  $90^\circ$ .

- ▶ If  $V_I$  is positive and  $V_Q$  is negative, the phase shift is between 90° and 180°.

- If V₁ and VQ are both positive, the phase shift is between 180° and 270°.

- If V₁ is negative and VQ is positive, the phase shift is between 270° and 360°.

Figure 78. Vector Gain Representation

In general, select the  $V_I$  and  $V_Q$  values to generate the desired phase shift and to minimize the variation in the  $V_{OUT}$  (gain). However, allowing some amplitude variation may result in finer phase step resolution and/or lower phase errors.

Refer to the AN-2021 Application Note, *ADMV4801/ADMV4821 SPI Application Note* for detailed information for phase control and features.

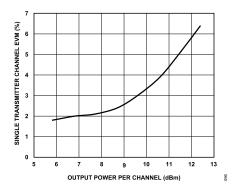

If the values given in the AN-2021 Application Note, *ADMV4801/ADMV4821 SPI Application Note* are used for the I and Q VGAs, the DVGAs in either the transmit or receive signal path execute gain control.