**ADP1829**

FCDC 00089

**Preliminary Technical Data**

### **FEATURES**

Two Output Voltages: 5.0 V, 3.3 V

Output Current: 3 A Input voltage: 8.0-16.0 V

Ripple 2% ppk of Output Voltage Transient step  $\pm 5\%$ , 50% max load

### **ADP1829 DESCRIPTION**

This ADP1829 reference design uses 8.0 V to 16.0 V for the input voltage. The output voltages and currents are as follows:

- $V_{OUT1} = 5.0 \text{ V}$  with a maximum output current of 3.0 A,

- $V_{OUT2} = 3.3 \text{ V}$  with a maximum output current of 3.0 A.

Design criteria require no tracking or sequencing. The ripple and transient assumptions are 2% peak to peak voltage ripple (for the switchers) and 5% deviation due to 50% instantaneous load step respectively. The nominal switching frequency is fixed at 300 kHz.

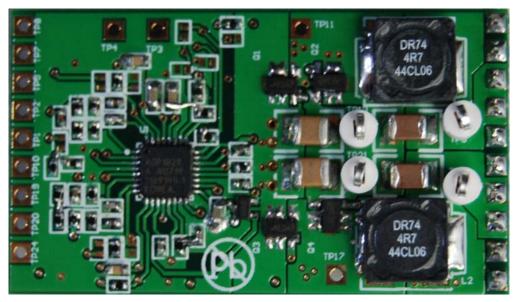

Figure 1. ADP1829 Evaluation Board

#### Rev. 0

Reference designs are as supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of reference designs. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Reference designs are not authorized to be used in life support devices or systems.

# **TABLE OF CONTENTS**

| Features                    |                                                                                                                                 | 1  |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| ADP1829                     | Description                                                                                                                     | 1  |  |  |  |

| Revision H                  | Iistory                                                                                                                         | 3  |  |  |  |

| General D                   | escription                                                                                                                      | 4  |  |  |  |

| ADP1829                     |                                                                                                                                 |    |  |  |  |

| Schematic                   |                                                                                                                                 | 5  |  |  |  |

| Bill of Mat                 | erials                                                                                                                          | 6  |  |  |  |

| Assembly 1                  | Drawing                                                                                                                         | 7  |  |  |  |

| Powering the ADP1829        |                                                                                                                                 |    |  |  |  |

| Input Po                    | ower Source                                                                                                                     | 8  |  |  |  |

| Output l                    | Load                                                                                                                            | 8  |  |  |  |

| Input and Output Voltmeters |                                                                                                                                 |    |  |  |  |

| Turning                     | On the Evaluation Board                                                                                                         | 9  |  |  |  |

| Typical Per                 | rformance Characteristics                                                                                                       | 10 |  |  |  |

| TABLE                       | OF FIGURES                                                                                                                      |    |  |  |  |

| Figure 1.                   | ADP1829 Evaluation Board                                                                                                        | 1  |  |  |  |

| Figure 2.                   | Schematic: V <sub>OUT1</sub> and V <sub>OUT2</sub>                                                                              | 5  |  |  |  |

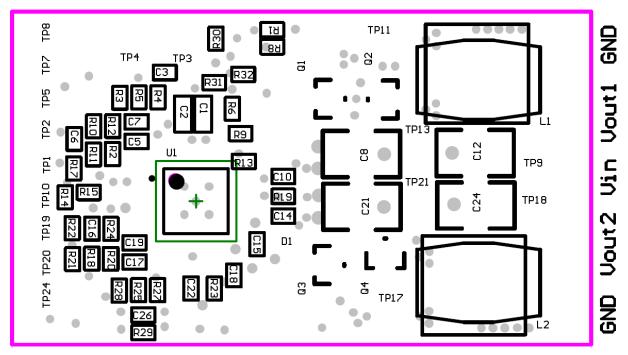

| Figure 3.                   | Top Assembly Drawing for 1829 Evaluation Board                                                                                  | 7  |  |  |  |

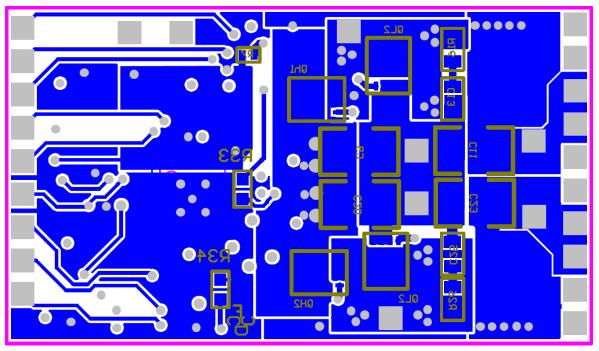

| Figure 4.                   | Bottom Assembly Drawing for 1829 Evaluation Board (looking through from top)                                                    | 7  |  |  |  |

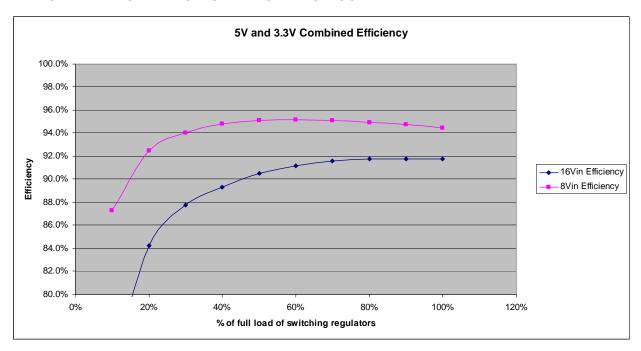

| Figure 5.                   | Efficiency                                                                                                                      | 10 |  |  |  |

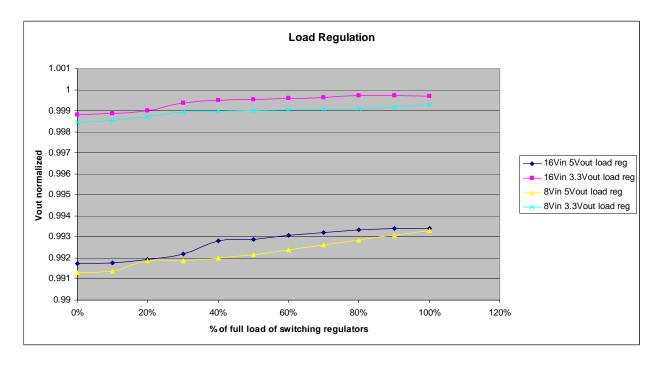

| Figure 6.                   | Normalized Load Regulation                                                                                                      | 10 |  |  |  |

| Figure 7.                   | Switching regulator turn on at no load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin                                                     | 11 |  |  |  |

| Figure 8.                   | Switching regulator turn on at full load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin                                                   | 11 |  |  |  |

| Figure 9.                   | Switching regulator turn off at no load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin                                                    | 12 |  |  |  |

| Figure 10.                  | Switching regulator turn off at full load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin                                                  | 12 |  |  |  |

| Figure 11.                  | Switching regulator ripple and noise at no load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 8.0 V                                    | 13 |  |  |  |

| Figure 12.                  | Switching regulator ripple and noise at full load: $Ch1 = 3.3 \text{ V}$ , $Ch2 = 5.0 \text{ V}$ , $Ch4 = Vin @ 8.0 \text{ V}$  | 13 |  |  |  |

| Figure 13.                  | Switching regulator ripple and noise at no load: $Ch1 = 3.3 \text{ V}$ , $Ch2 = 5.0 \text{ V}$ , $Ch4 = Vin @ 16.0 \text{ V}$   | 14 |  |  |  |

| Figure 14.                  | Switching regulator ripple and noise at full load: $Ch1 = 3.3 \text{ V}$ , $Ch2 = 5.0 \text{ V}$ , $Ch4 = Vin @ 16.0 \text{ V}$ | 14 |  |  |  |

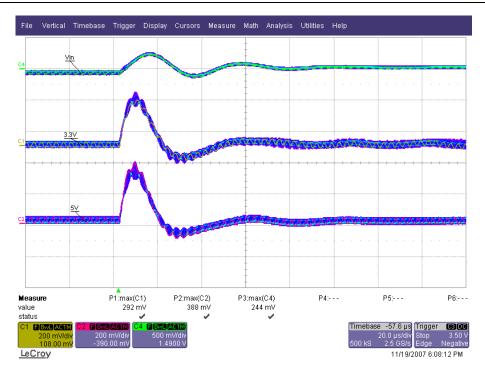

| Figure 15.                  | Transient 50% to 100% load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 8.0 V                                                         | 15 |  |  |  |

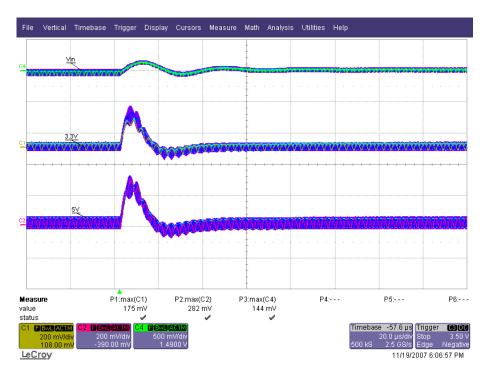

| Figure 16.                  | Transient 50% to 100% load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 16.0 V                                                        | 15 |  |  |  |

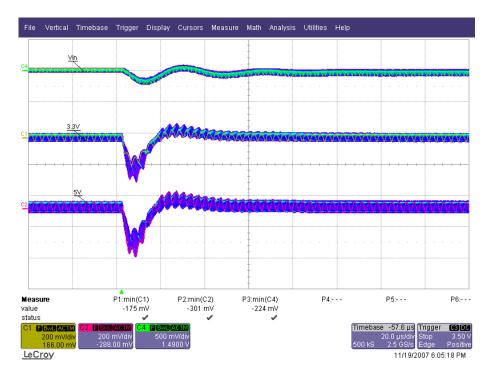

| Figure 17.                  | Transient 100% to 50% load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 8.0 V                                                         | 16 |  |  |  |

| Figure 18                   | Transient 100% to 50% load Ch1 - 3 3 V Ch2 - 5 0 V Ch4 - Vin @ 16 0 V                                                           | 16 |  |  |  |

FCDC 00089

## **REVISION HISTORY**

11/19/2007—Revision 0: Initial Version

## **GENERAL DESCRIPTION**

### **ADP1829**

The ADP1829 is a versatile, dual output, interleaved, synchronous PWM buck controller that generates two independent outputs from an input voltage of 2.9 V to 18 V. Each channel can be configured to provide output voltage from 0.6V to 85% of the input voltage. The two channels operate 180° out of phase, which reduces the current stress on the input capacitor and allows the use of a smaller and lower cost input capacitor.

The ADP1829 operates at a pin-selectable fixed switching frequency of either 300 kHz or 600 kHz. For some noise sensitive applications, it can also be synchronized to an external clock to achieve switching frequency between 300 kHz and 1 MHz. The switching frequency chosen is 300 kHz to get good efficiency over a wide range of input and output conditions.

The ADP1829 includes an adjustable soft start to limit input inrush current, voltage tracking for sequencing or DDR termination, independent power-good output, and a power enable pin. It also provides current-limit and short-circuit protection by sensing the voltage on the synchronous MOSFET.

# **SCHEMATIC**

## 5.0V at 2.0A and 3.3V at 2.0A R10 27 26 25 LDO EN2 EN1 SD : 32 31 30 29 28 CMP1 TRK1 SS1 VREG IN SYNC U2 ADP1829ACP DH1 Q1 SW1 UV2 CSL1 VœV0 C14⊥ ⊕ FB2 PGND1 DL1 TRK2 R25 \( \) C<sub>15</sub> \( \bigcup \) D1b C18 R23 R29 POK3V3 Q3 C22

Figure 2. Schematic:  $V_{OUT1}$  and  $V_{OUT2}$

# **BILL OF MATERIALS**

Table 1. Vout1, and Vout2 Bill of Materials (Vo5V0 and Vo3V3)

| Description                           | Designator       | Qty | Manufacturer | MFR#               |

|---------------------------------------|------------------|-----|--------------|--------------------|

| Cap Ceramic C0G 100p 0402 50V         | C5, C19          | 2   | Vishay       | Generic            |

| Cap Ceramic X5R 1u 0603 16V           | C2, C15          | 2   | Murata       | GRM188R61C105K     |

| Cap Ceramic X5R 1u 0603 25V           | C1               | 1   | Murata       | GRM188R61E105K     |

| Cap Ceramic X7R 47n 0402 10V          | C3, C26          | 2   | Vishay       | Generic            |

| Cap Ceramic X7R 22u 1210 25V          | C8, C21          | 2   | Murata       | CGRM32ER61E226K    |

| Cap Polymer 22u 7343 20V              | C20              | 1   | Kemet        | T520V226M020ATE090 |

| Cap Ceramic X5R 22u 1210 10V          | C12, C24         | 2   | TDK          | C3225X5R1A226M     |

| Cap Ceramic X7R 100n 0402 16V         | C10, C22         | 2   | Murata       | GRM155R71C104KA88D |

| Cap Ceramic C0G 33p 0402 50V          | C14, C18         | 2   | Vishay       | Generic            |

| Cap Ceramic COG 470p 0402 50V         | C6, C16          | 2   | Vishay       | Generic            |

| Cap Ceramic X7R 3.3n 0402 50V         | C7, C17          | 2   | Vishay       | Generic            |

| Diode Dual Schottky 200mA SOT-323 30V | D1               | 1   | Diodes inc   | BAT54AW            |

| Inductor Ferrite 4.7uH 7.6mm x 7.6mm  | L1, L2           | 2   | Coiltronics  | DR74-4R7-R         |

| Single N-Channel MOSFET 1206-8 30V    | Q1, Q2, Q3, Q4   | 4   | Vishay       | Si5404bdc          |

| Res 5% Thick Film 10 Ohms 0402        | R1, R7           | 2   | Vishay       | Generic            |

| Res 1% Thick Film 10.0k 0402          | R6, R9, R13, R29 | 4   | Vishay       | Generic            |

| Res 1% Thick Film 5.11k 0402          | R12, R20         | 2   | Vishay       | Generic            |

| Res 1% Thick Film 20.0k 0402          | R10, R21         | 2   | Vishay       | Generic            |

| Res 1% Thick Film 2.74k 0402          | R2               | 1   | Vishay       | Generic            |

| Res 1% Thick Film 100 Ohms 0402       | R11, R22         | 2   | Vishay       | Generic            |

| Res 1% Thick Film 4.42k 0402          | R24              | 1   | Vishay       | Generic            |

| Res 1% Thick Film 4.53k 0402          | R19, R23         | 2   | Vishay       | Generic            |

| 2 chan 300k to 600k PWM LFCSP-32      | U1               | 1   | Analog       | ADP1829ACPZ        |

## **ASSEMBLY DRAWING**

Figure 3. Top Assembly Drawing for 1829 Evaluation Board

Figure 4. Bottom Assembly Drawing for 1829 Evaluation Board (looking through from top)

## **POWERING THE ADP1829**

The ADP1829 is supplied fully assembled.

#### **INPUT POWER SOURCE**

- 1. Before connecting the power source to the ADP1829, make sure that it is turned off. If the input power source includes a current meter, use that meter to monitor the input current.

- 2. Connect the positive terminal of the power source to the VIN terminal on the evaluation board, and the negative terminal of the power source to the GND terminal just below the VIN terminal.

- 3. If the power source does not include a current meter, connect a current meter in series with the input source voltage.

- 4. Connect the positive lead (+) of the power source to the ammeter positive (+) connection, the negative lead (-) of the power source to the GND pins on the board, and the negative lead (-) of the ammeter to the VIN pins on the board.

#### **OUTPUT LOAD**

- 1. Although the ADP1829 can sustain the sudden connection of the load, it is possible to damage the load if it is not properly connected.

- 2. Make sure that the board is turned off before connecting the load.

- a) If the load includes an ammeter, or if the current is not measured, connect the load directly to the evaluation board with the positive (+) load connection to the  $V_{OUT}$  pins and negative (-) load connection to the GND pins next to the  $V_{OUT}$  pins.

- b) If an ammeter is used, connect it in series with the load; connect the positive (+) ammeter terminal to the evaluation board  $V_{OUT}$  pins, the negative (-) ammeter terminal to the positive (+) load terminal, and the negative (-) load terminal to the evaluation board GND pins next to the  $V_{OUT}$  pins.

- c) Repeat for the other  $V_{\text{OUT}}$  channel.

Once the loads are connected, make sure that they are set to the proper current before powering the ADP1829.

### **INPUT AND OUTPUT VOLTMETERS**

Measure the input and output voltages with voltmeters.

- 1. Connect the voltmeter measuring the input voltage with the positive (+) lead connected to the VIN pins on the test board and the negative lead (–) connected to the GND test point between the inductors (TP13 or TP21).

- 2. Connect the voltmeter measuring V<sub>OUT1</sub> with the positive lead (+) connected to the test point near the V<sub>OUT1</sub> pins (TP9) and the negative lead (-) connected to the adjacent GND test point (TP13).

- 3. Connect the voltmeter measuring  $V_{OUT2}$  in the same manner (between TP8 and TP21).

- 4. Make sure to connect the voltmeters to the appropriate evaluation board test points and not to the load or power source themselves.

- 5. If the voltmeters are not connected directly to the evaluation board at these connection points, the measured voltages will be incorrect due to the voltage drop across the leads connecting the evaluation board to both the source and load.

FCDC 00089

### **TURNING ON THE EVALUATION BOARD**

Once the power source and loads are connected to the ADP1829, the board can be powered for operation. Slowly increase the input power source voltage until the input voltage exceeds the minimum input operating voltage of 8.0 V. If the load is not already enabled, enable the load and check that it is drawing the proper current and that the output voltage maintains voltage regulation.

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 5. Efficiency

Figure 6. Normalized Load Regulation

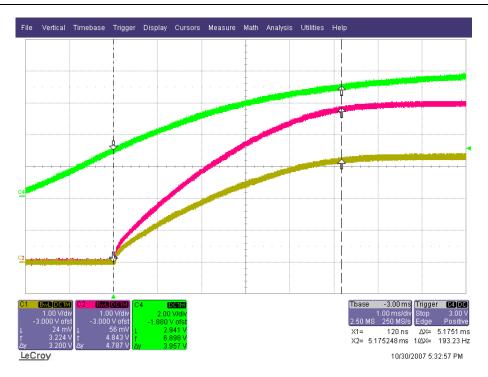

Figure 7. Switching regulator turn on at no load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin

Figure 8. Switching regulator turn on at full load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin

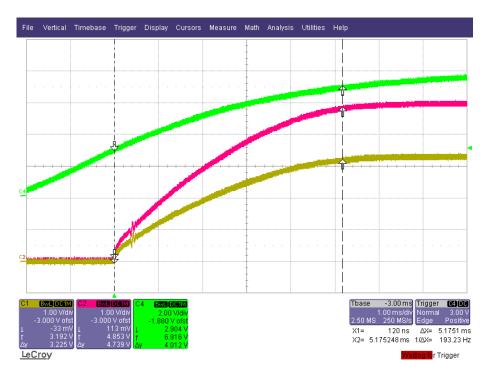

Figure 9. Switching regulator turn off at no load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin

Figure 10. Switching regulator turn off at full load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin

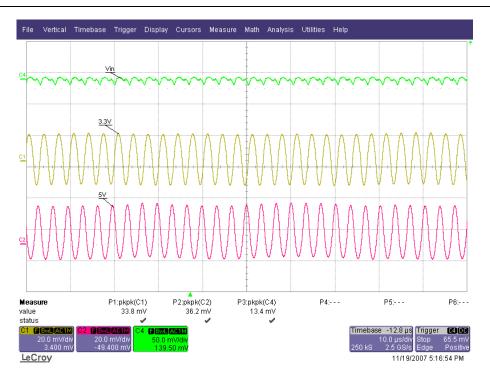

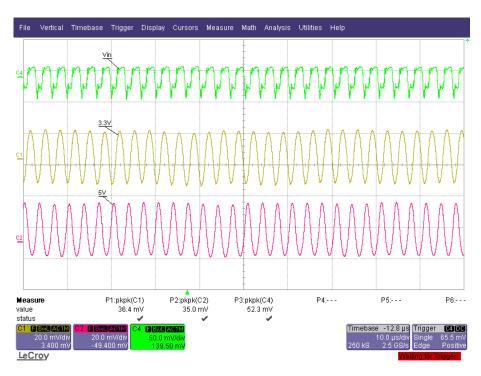

Figure 11. Switching regulator ripple and noise at no load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 8.0 V

Figure 12. Switching regulator ripple and noise at full load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 8.0 V

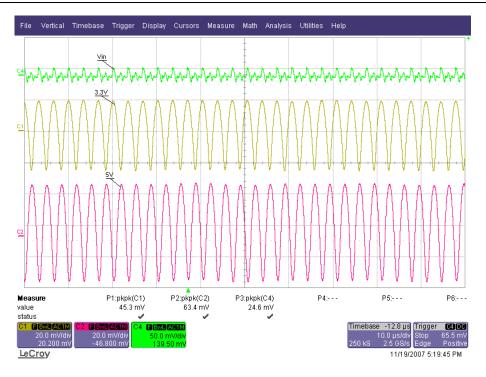

Figure 13. Switching regulator ripple and noise at no load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 16.0 V

Figure 14. Switching regulator ripple and noise at full load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 16.0 V

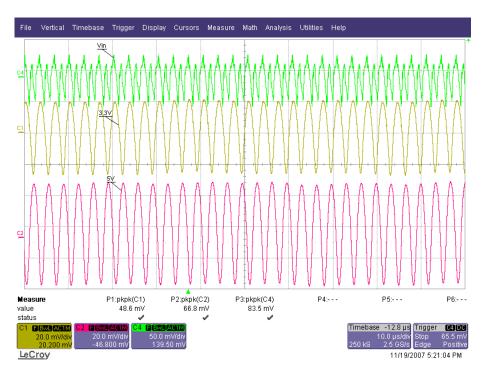

Figure 15. Transient 50% to 100% load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 8.0 V

Figure 16. Transient 50% to 100% load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 16.0 V

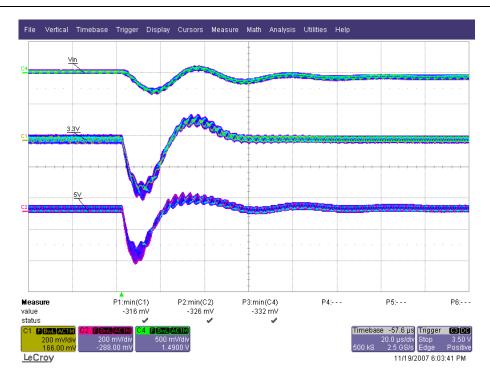

Figure 17. Transient 100% to 50% load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 8.0 V

Figure 18. Transient 100% to 50% load: Ch1 = 3.3 V, Ch2 = 5.0 V, Ch4 = Vin @ 16.0 V

# **NOTES**

©2007 Analog Devices, Inc. All rights reserved.

Trademarks and registered trademarks are the property of their respective owners.

EB

www.analog.com