## Broadband Up/Downconverting Mixer with Integrated Fractional-N PLL and VCO

**Data Sheet**

## **ADRF6655**

#### **FEATURES**

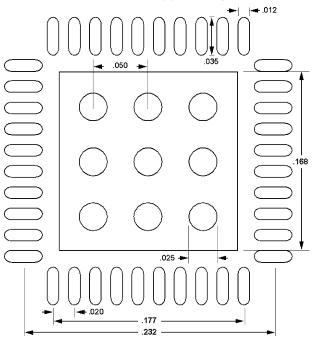

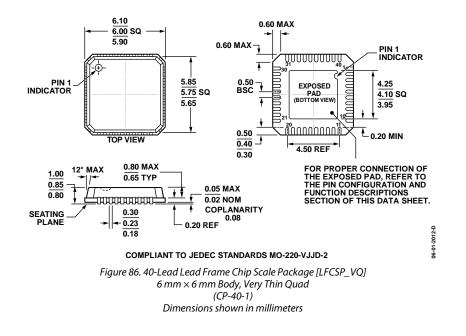

Broadband active mixer with integrated fractional-N PLL RF input frequency range: 100 MHz to 2500 MHz Internal LO frequency range: 1050 MHz to 2300 MHz Flexible IF output interface Input P1dB: 12 dBm Input IP3: 29 dBm Noise figure (SSB): 12 dB Voltage conversion gain: 6 dB Matched 200  $\Omega$  output impedance SPI serial interface for PLL programming 40-lead 6 mm × 6 mm LFCSP

ANALOG DEVICES

#### **GENERAL DESCRIPTION**

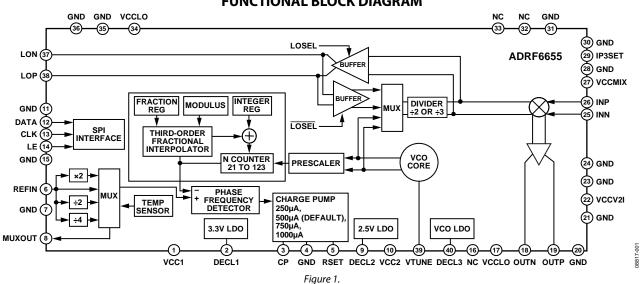

The ADRF6655 is a high dynamic range active mixer with integrated PLL and VCO. The synthesizer uses a programmable integer-N/fractional-N PLL to generate a local oscillator input to the mixer. The PLL reference input is nominally 20 MHz. The reference input can be divided by or multiplied by and then applied to the PLL phase detector. The PLL can support input reference frequencies from 10 MHz to 160 MHz. The phase detector output controls a charge pump whose output is integrated in an off-chip loop filter. The loop filter output is then applied to a local oscillator (LO) divider as well as to a programmable PLL divider.

The programmable divider is controlled by an  $\Sigma$ - $\Delta$  modulator (SDM). The modulus of the SDM can be programmed between 1 and 2047.

The broadband, active mixer employs a bias adjustment to allow for enhanced IP3 performance at the expense of increased supply current. The mixer provides an input IP3 exceeding 25 dBm with 12 dB single sideband NF under typical conditions. The IIP3 can be boosted to ~29 dBm with roughly 20 mA of additional supplied current. The mixer provides a typical voltage conversion gain of 6 dB with a 200  $\Omega$  differential IF output impedance. The IF output can be externally matched to support upconversion over a limited frequency range.

The ADRF6655 is fabricated using an advanced silicongermanium BiCMOS process. It is packaged in a 40-lead, exposed-paddle, Pb-free, 6 mm  $\times$  6 mm LFCSP. Performance is specified over a -40°C to +85°C temperature range.

#### FUNCTIONAL BLOCK DIAGRAM

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### TABLE OF CONTENTS

| Features                                                                                                 |

|----------------------------------------------------------------------------------------------------------|

| General Description 1                                                                                    |

| Functional Block Diagram1                                                                                |

| Revision History 2                                                                                       |

| Specifications                                                                                           |

| Timing Characteristics                                                                                   |

| Absolute Maximum Ratings                                                                                 |

| ESD Caution                                                                                              |

| Pin Configuration and Function Desperiptions7                                                            |

| Typical Performance Characteristics                                                                      |

| Downconversion                                                                                           |

| Upconversion11                                                                                           |

| PLL Characteristic                                                                                       |

| Complimentary Cumulative Distribution Function (CCDF):<br>Downconversion, LO = 1100 MHz, RF = 900 MHz14  |

| Complimentary Cumulative Distribution Function (CCDF):<br>Downconversion, LO = 1700 MHz, RF = 1900 MHz15 |

| Complimentary Cumulative Distribution Function (CCDF):<br>Upconversion Distribution                      |

| Circuit Description                                                                                      |

| PLL and VCO Block17                                                                                      |

| RF Mixer Block                                                                                           |

| Digital Interfaces                                                                                       |

| Analog Interfaces 19                                                                                     |

| Supply Connections                                                                                       |

| Synthesizer Connections 19                                                                               |

### **REVISION HISTORY**

| 9/14—Rev. 0 to Rev. A                                    |

|----------------------------------------------------------|

| Changes to Figure 37                                     |

| Changes to Table 4                                       |

| Changes to ADRF6655 Control Software Section, Figure 66, |

| and Figure 6723                                          |

| Updated Outline Dimensions                               |

#### 2/10—Revision 0: Initial Version

| Output Matching and Biasing19                            | 9 |

|----------------------------------------------------------|---|

| Input Matching                                           | ) |

| IP3SET Linearization Feature21                           | 1 |

| CDAC Linearization Feature                               | 1 |

| External LO Interface                                    | 1 |

| Using an External VCO22                                  | 2 |

| ADRF6655 Control Software 23                             | 3 |

| PLL Loop Filter Design                                   | 3 |

| Register Structure                                       | 4 |

| Device Programming25                                     | 5 |

| Initialization Sequence                                  | 5 |

| Register 0—Integer Divide Control                        | 5 |

| Register 1—Modulus Divide Control                        | 7 |

| Register 2—Fractional Divide Control                     | 7 |

| Register 3– $\Sigma$ - $\Delta$ Modulator Dither Control | 8 |

| Register 4—Charge Pump, PFD, and Reference               |   |

| Path Control                                             | ) |

| Register 5—LO Path and Mixer Control                     | 1 |

| Register 6—VCO Control and PLL Enables                   | 2 |

| Register 7—External VCO Control                          | 3 |

| Characterization Setups                                  | 4 |

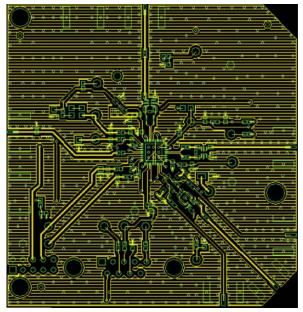

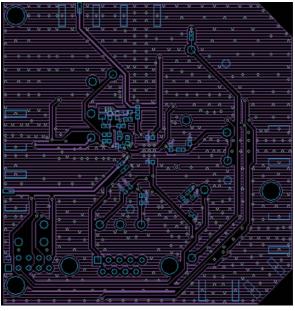

| Evaluation Board Layout and Thermal Grounding            | 8 |

| Outline Dimensions 41                                    | 1 |

| Ordering Guide41                                         | 1 |

|                                                          |   |

### SPECIFICATIONS

$V_{CC}$  = 5 V; ambient temperature (T<sub>A</sub>) = 25°C; REFIN = 20 MHz, phase frequency detector (PFD) frequency = 20 MHz, IF output loaded into 4-to-1 transformer matched to a 50  $\Omega$  system, unless otherwise noted.

| Parameter                                     | Test Conditions/Comments                                                                                                                                                                                                                                                                                 | Min  | Тур              | Max  | Unit   |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|------|--------|

| RF INPUT FREQUENCY RANGE                      |                                                                                                                                                                                                                                                                                                          | 100  |                  | 2500 | MHz    |

| IF OUTPUT FREQUENCY RANGE                     | Can be matched externally for improved return loss at higher frequencies (see the Output Matching and Biasing section)                                                                                                                                                                                   | LF   |                  | 2200 | MHz    |

| INTERNAL LO FREQUENCY RANGE                   | Divide-by-3 mode <sup>1</sup>                                                                                                                                                                                                                                                                            | 1050 |                  | 1530 | MHz    |

|                                               | Divide-by-2 mode <sup>1</sup>                                                                                                                                                                                                                                                                            | 1530 |                  | 2300 | MHz    |

| EXTERNAL LO FREQUENCY RANGE                   | Divide-by-2 mode <sup>2</sup>                                                                                                                                                                                                                                                                            | 500  |                  | 2300 | MHz    |

| MIXER                                         |                                                                                                                                                                                                                                                                                                          |      |                  |      |        |

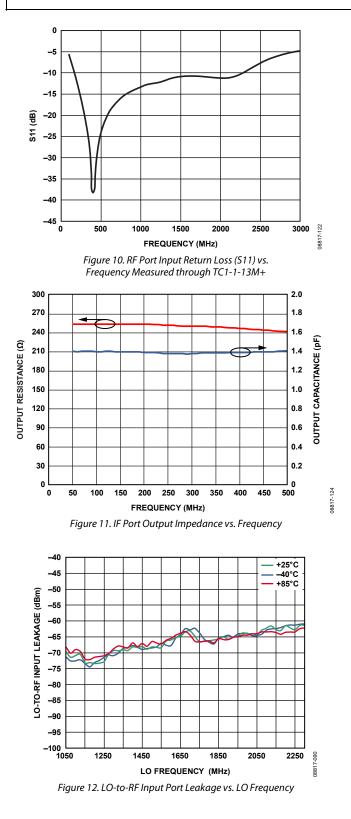

| Input Return Loss                             | INP, INN; relative to 50 $\Omega,$ from 350 MHz to 2200 MHz using TC1-1-13M+ balun^3                                                                                                                                                                                                                     |      | 12               |      | dB     |

| Output Return Loss                            | OUTP, OUTN; relative to 50 $\Omega$ out to 200 MHz using TC4-1W output transformer option <sup>3</sup>                                                                                                                                                                                                   |      | 12               |      | dB     |

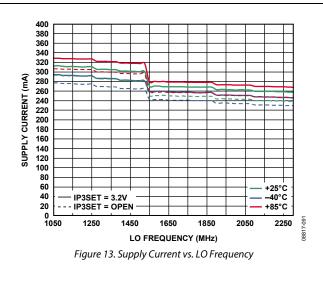

| IF Output Impedance                           | OUTP, OUTN                                                                                                                                                                                                                                                                                               |      | 200              |      | Ω      |

| Output Common Mode                            | OUTP, OUTN; external pull-up balun or inductors required                                                                                                                                                                                                                                                 |      | V <sub>POS</sub> |      | V      |

| Voltage Conversion Gain                       | IF output loaded into 200 $\Omega$ differential load                                                                                                                                                                                                                                                     |      | 6                |      | dB     |

| Output Swing                                  |                                                                                                                                                                                                                                                                                                          |      | 2                |      | V p-p  |

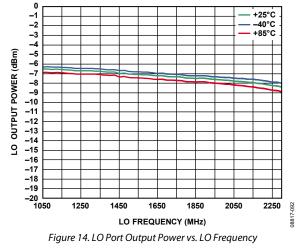

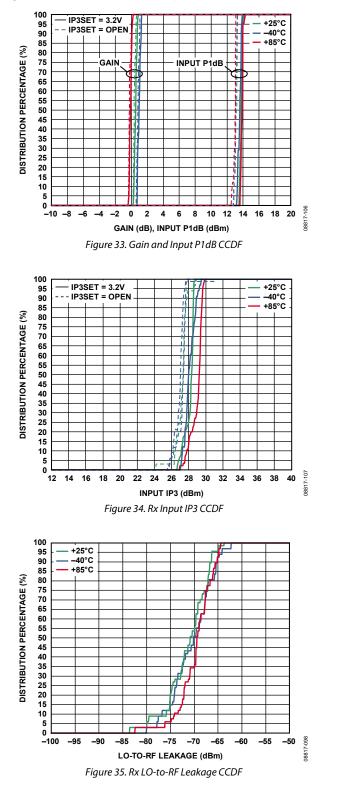

| LO-to-IF Output Leakage                       | Can be improved using external filtering                                                                                                                                                                                                                                                                 |      | -40              |      | dBm    |

| DYNAMIC PERFORMANCE                           | IP3Set = 3.2 V                                                                                                                                                                                                                                                                                           |      |                  |      |        |

| Upconversion                                  | 340 MHz RF input, 1200 MHz IF output using 1540 MHz<br>LO (see Figure 56 for output matching network)                                                                                                                                                                                                    |      |                  |      |        |

| Gain Flatness                                 | Over $\pm 50$ MHz bandwidth for 1200 MHz output center frequency                                                                                                                                                                                                                                         |      | 0.25             |      | dB p-p |

| Gain Temperature Coefficient                  | Average values from –40°C to +85°C                                                                                                                                                                                                                                                                       |      | -10              |      | mdB/°  |

| Output P1dB                                   |                                                                                                                                                                                                                                                                                                          |      | 11               |      | dBm    |

| Second-Order Output Intercept (IIP2)          | –5 dBm each tone                                                                                                                                                                                                                                                                                         |      | 60               |      | dBm    |

| Third-Order Output Intercept (IIP3)           | TC1-1-13M+ balun³OUTP, OUTN; relative to $50 \Omega$ out to 200 MHz using TC4-1W<br>output transformer option³OUTP, OUTN<br>OUTP, OUTN; external pull-up balun or inductors required<br>IF output loaded into 200 $\Omega$ differential loadCan be improved using external filteringIP3Set = $3.2 V$<br> |      | 31               |      | dBm    |

|                                               | –5 dBm each tone, IP3SET = open                                                                                                                                                                                                                                                                          |      | 28               |      | dBm    |

| Output Noise Spectral Density                 | IP3SET = 3.2 V, RF input terminated with 50 $\Omega$                                                                                                                                                                                                                                                     |      | -160             |      | dBm/H  |

|                                               | IP3SET = 3.2 V, RF input = $-5$ dBm, $f_{LO}$ = 1315 MHz with $f_{RF}$ = 380 MHz applied, measured noise at $f_{IF}$ = 915 MHz                                                                                                                                                                           |      | -155             |      | dBm/H  |

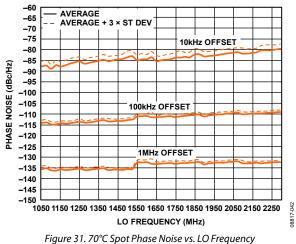

| Downconversion                                | 1880 MHz RF input, 140 MHz IF output using 1740 MHz LO                                                                                                                                                                                                                                                   |      |                  |      |        |

| Gain Flatness                                 | Over ±50 MHz bandwidth for 1880 MHz input center frequency                                                                                                                                                                                                                                               |      | 0.25             |      | dB p-p |

| Gain Temperature Coefficient                  | Average values from -40°C to +85°C                                                                                                                                                                                                                                                                       |      | -10              |      | mdB/°  |

| Input P1dB                                    | IP3SET = 3.2 V                                                                                                                                                                                                                                                                                           |      | 14               |      | dBm    |

|                                               | IP3SET = open                                                                                                                                                                                                                                                                                            |      | 12               |      | dBm    |

| Second-Order Input Intercept (IIP2)           | –5 dBm each tone                                                                                                                                                                                                                                                                                         |      | 50               |      | dBm    |

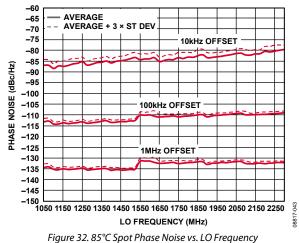

| Third-Order Input Intercept (IIP3)            | –5 dBm each tone, IP3SET = 3.2 V                                                                                                                                                                                                                                                                         |      | 27               |      | dBm    |

|                                               | –5 dBm each tone, IP3SET = open                                                                                                                                                                                                                                                                          |      | 26               |      | dBm    |

| SSB Noise Figure (NF)                         | IP3SET = 3.2 V                                                                                                                                                                                                                                                                                           |      | 14               |      | dB     |

|                                               | IP3SET = open                                                                                                                                                                                                                                                                                            |      | 12               |      | dB     |

| SSB Noise Figure Under Blocking<br>Conditions | -5 dBm RF input blocker applied at 995 MHz, $f_{LO}$ = 1200 MHz, noise measured at 5 MHz offset from IF output blocker                                                                                                                                                                                   |      |                  |      |        |

|                                               | IP3SET = 3.2 V                                                                                                                                                                                                                                                                                           |      | 20.75            |      | dB     |

|                                               | IP3SET = open                                                                                                                                                                                                                                                                                            |      | 20.25            |      | dB     |

| IF/2 Spurious                                 | –5 dBm RF input power                                                                                                                                                                                                                                                                                    |      | -65              |      | dBc    |

| LO OUTPUT                                     | LOP, LON                                                                                                                                                                                                                                                                                                 |      |                  |      |        |

| Output Level                                  | 1 × LO into a 50 Ω load, LO buffer enabled                                                                                                                                                                                                                                                               |      | -7               |      | dBm    |

| Parameter                             | Test Conditions/Comments                                                                | Min   | Тур  | Max  | Unit   |

|---------------------------------------|-----------------------------------------------------------------------------------------|-------|------|------|--------|

| SYNTHESIZER SPECIFICATIONS            | Synthesizer specifications referenced to 1 × LO <sup>4</sup>                            |       |      |      |        |

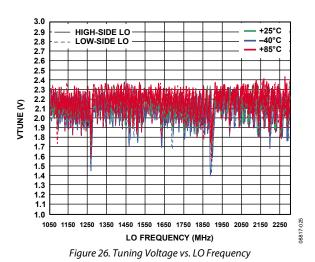

| Fundamental VCO Sensitivity           | VCO tuning sensitivity before divide-by-2 or divide-by-3                                |       | 75   |      | MHz/V  |

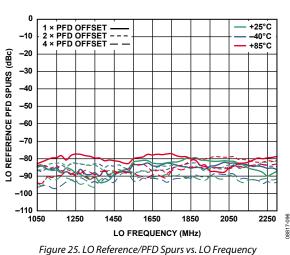

| Spurs                                 | Measured at LO output                                                                   |       |      |      |        |

| Reference/PFD Spurs                   | f <sub>PFD</sub> /2                                                                     |       | -95  |      | dBc    |

|                                       | <b>f</b> <sub>PFD</sub>                                                                 |       | -83  |      | dBc    |

|                                       | $2 \times f_{PFD}$                                                                      |       | -85  |      | dBc    |

|                                       | $4 \times f_{PFD}$                                                                      |       | -88  |      | dBc    |

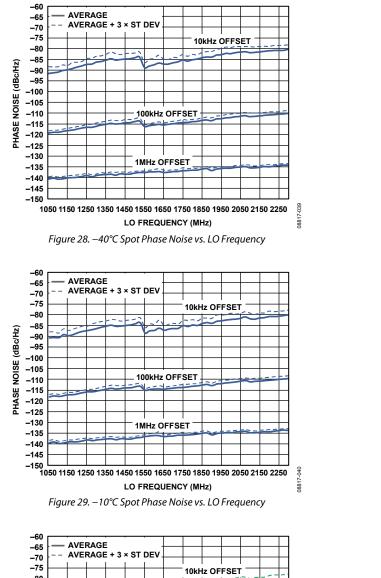

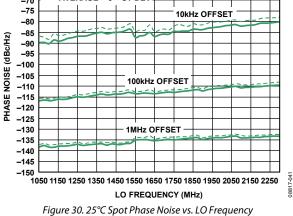

| Phase Noise                           | PFD frequency = 20 MHz <sup>4</sup>                                                     |       |      |      |        |

| LO Frequency = 1330 MHz               |                                                                                         |       |      |      |        |

|                                       | @ 10 kHz offset                                                                         |       | -85  |      | dBc/Hz |

|                                       | @ 100 kHz offset                                                                        |       | -114 |      | dBc/Hz |

|                                       | @ 1 MHz offset                                                                          |       | -138 |      | dBc/Hz |

|                                       | @ 10 MHz offset                                                                         |       | -154 |      | dBc/Hz |

| Integrated Phase Noise                | 10 kHz to 40 MHz integration bandwidth                                                  |       | 0.3  |      | °rms   |

| LO Frequency = 1840 MHz               |                                                                                         |       |      |      |        |

|                                       | @ 10 kHz offset                                                                         |       | -83  |      | dBc/Hz |

|                                       | @ 100 kHz offset                                                                        |       | -111 |      | dBc/Hz |

|                                       | @ 1 MHz offset                                                                          |       | -136 |      | dBc/Hz |

|                                       | @ 10 MHz offset                                                                         |       | -152 |      | dBc/Hz |

| Integrated Phase Noise                | 10 kHz to 40 MHz integration bandwidth                                                  |       | 0.4  |      | °rms   |

| PFD Frequency                         |                                                                                         | 19.33 | 20   | 40   | MHz    |

| REFERENCE CHARACTERISTICS             | REFIN, MUXOUT                                                                           |       |      |      |        |

| REFIN Input Frequency                 |                                                                                         | 10    | 20   | 160  | MHz    |

| <b>REFIN Input Capacitance</b>        |                                                                                         |       | 4    |      | рF     |

| REFIN Input Current                   |                                                                                         |       | ±100 |      | μA     |

| <b>REFIN Input Sensitivity</b>        | AC-coupled                                                                              | 0.25  | 1    | 3.3  | V p-p  |

| MUXOUT Output Levels                  | V <sub>OL</sub> (lock detect output selected)                                           |       |      | 0.25 | V      |

|                                       | V <sub>он</sub> (lock detect output selected)                                           | 2.7   |      |      | V      |

| CHARGE PUMP                           | СР                                                                                      |       |      |      |        |

| Pump Current                          | Charge pump current adjustable using Register 4 and/or                                  |       | 500  |      | μA     |

|                                       | R <sub>SET</sub> (see Pin 5 description)                                                |       |      |      |        |

| Output Compliance Range               |                                                                                         | 1     |      | 2.8  | V      |

| LOGIC INPUTS                          | CLK, DATA, LE                                                                           |       |      |      |        |

| V <sub>INH</sub> , Input High Voltage |                                                                                         | 1.4   |      | 3.3  | V      |

| V <sub>INL</sub> , Input Low Voltage  |                                                                                         | 0     |      | 0.7  | V      |

| IINH/IINL, Input Current              |                                                                                         |       | ±1   |      | μΑ     |

| C <sub>IN</sub> , Input Capacitance   |                                                                                         |       | 3    |      | pF     |

| POWER SUPPLIES                        | VCC1, VCC2, VCCLO                                                                       |       |      |      |        |

| Voltage Range                         |                                                                                         | 4.75  | 5    | 5.25 | V      |

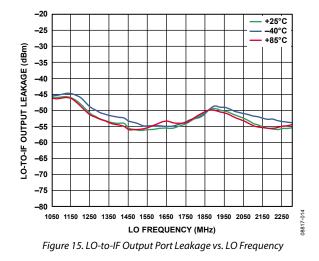

| Supply Current                        | LO output buffer disabled                                                               |       |      |      |        |

|                                       | PLL only                                                                                |       | 115  |      | mA     |

|                                       | Normal TX mode, IP3SET = $3.2 \text{ V}$ , $f_{LO} \leq 1530 \text{ MHz}$ (divide-by-3) |       | 310  |      | mA     |

|                                       | Normal TX mode, IP3SET = $3.2 \text{ V}$ , $f_{LO} > 1530 \text{ MHz}$ (divide-by-2)    |       | 270  |      | mA     |

|                                       | Normal RX mode, IP3SET = open, $f_{LO} \le 1530$ MHz (divide-by-3)                      |       | 285  |      | mA     |

|                                       | Normal RX mode, IP3SET = open, $f_{LO} > 1530$ MHz (divide-by-2)                        |       | 245  |      | mA     |

|                                       | Power-down mode                                                                         |       | 15   |      | mA     |

<sup>1</sup> Internal LO path divider programmed via serial interface. See the LO Signal Chain section for additional information.

<sup>2</sup> See the External LO Interface section. <sup>3</sup> Improved return loss can be achieved using external matching. See the Circuit Description section for more details. <sup>4</sup> Measured on standard evaluation board with 1.5 kHz loop filter (C13 = 47 nF, C14 = 0.1  $\mu$ F, C15 = 4.7  $\mu$ F, R9 = 270  $\Omega$ , R10 = 68  $\Omega$ ).

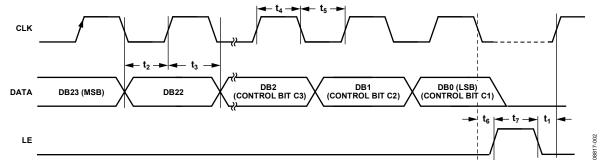

#### TIMING CHARACTERISTICS

| Parameter      | Limit | Unit       | Test Conditions/Comments |  |

|----------------|-------|------------|--------------------------|--|

| t1             | 20    | ns minimum | LE setup time            |  |

| t <sub>2</sub> | 10    | ns minimum | DATA to CLK setup time   |  |

| t3             | 10    | ns minimum | DATA to CLK hold time    |  |

| t4             | 25    | ns minimum | CLK high duration        |  |

| ts             | 25    | ns minimum | CLK low duration         |  |

| t <sub>6</sub> | 10    | ns minimum | CLK to LE setup time     |  |

| t <sub>7</sub> | 20    | ns minimum | LE pulse width           |  |

Figure 2. Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| 1 4010 51                                                 |                  |

|-----------------------------------------------------------|------------------|

| Parameter                                                 | Rating           |

| Supply Voltage, Vcc                                       | 5.5 V            |

| Digital I/O CLK, DATA, LE                                 | –0.3 V to +3.6 V |

| OUTP, OUTN                                                | Vcc              |

| LOP, LON                                                  | 16 dBm           |

| INN, INP                                                  | 20 dBm           |

| DECL3 Using External Bias Option                          | 3.5 V            |

| $\theta_{JA}$ (Exposed Paddle Soldered Down) <sup>1</sup> | 35°C/W           |

| Maximum Junction Temperature                              | 150°C            |

| Operating Temperature Range                               | -40°C to +85°C   |

| Storage Temperature Range                                 | –65°C to +150°C  |

<sup>1</sup> Per JDEC standard JESD 51-2. For information on optimizing thermal impedance, see the Evaluation Board Layout and Thermal Grounding section.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

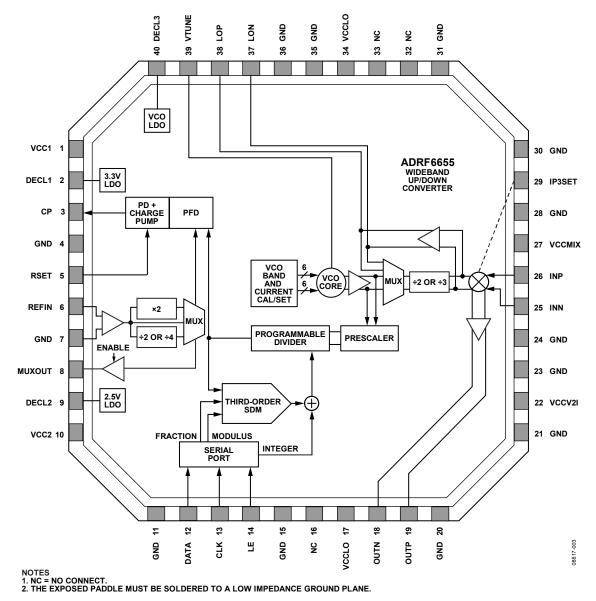

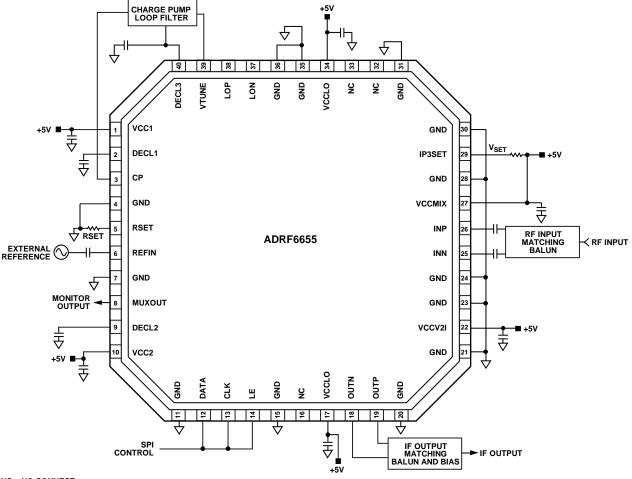

### PIN CONFIGURATION AND FUNCTION DESPCRIPTIONS

Figure 3. Pin Configuration

| Pin No.                                                   | Mnemonic | Description                                                                                                                                                                              |

|-----------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                         | VCC1     | Power Supply for Internal 3.3 V LDO. The power supply voltage range is 4.75 V to 5.25 V. Supply pin should be decoupled with 100 pF and 0.1 $\mu$ F capacitors located close to the pin. |

| 2                                                         | DECL1    | Decoupling Node for 3.3 V LDO. Pin should be decoupled with 100 pF, 0.1 $\mu$ F, and 10 $\mu$ F capacitors located close to the pin.                                                     |

| 3                                                         | СР       | Charge Pump Output Pin. Connect this pin to $V_{TUNE}$ through the loop filter.                                                                                                          |

| 4, 7, 11, 15,<br>20, 21, 23,<br>24, 28, 30,<br>31, 35, 36 | GND      | Ground. Connect these pins to a low impedance ground plane.                                                                                                                              |

#### **Table 4. Pin Function Descriptions**

| Pin No.    | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5          | RSET       | Charge Pump Current. The nominal charge pump current can be set to either 250 $\mu$ A, 500 $\mu$ A, 750 $\mu$ A, or 1 mA using DB10 and DB11 of Register 4 and by setting DB18 to 0 (internal reference current). In this mode, no external R <sub>SET</sub> is required. If DB18 is set to 1, the four nominal charge pump currents (I <sub>NOMINAL</sub> ) can be externally tweaked according to |

|            |            | $RSET[\Omega] = \left[\frac{217.4 \times I_{CP,BASE}}{250}\right] - 37.8$                                                                                                                                                                                                                                                                                                                           |

|            |            | where $I_{CP, BASE}$ is the base charge pump current in $\mu$ A.<br>For further details on the charge pump current, see the Register 4—Charge Pump, PFD, and Reference<br>Path Control section.                                                                                                                                                                                                     |

| 6          | REFIN      | Reference Input. Nominal input level is 1 V p-p. Input range is 10 MHz to 160 MHz. This pin must be ac-coupled.                                                                                                                                                                                                                                                                                     |

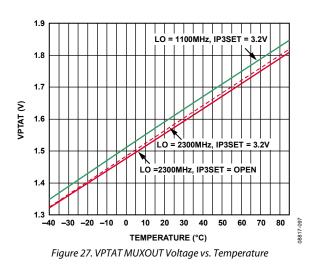

| 8          | MUXOUT     | Multiplexer Output. This output allows either a digital lock detect, a voltage proportional to temperature or a buffered, frequency-scaled reference signal to be accessed externally. The output is selected by programming the appropriate bits in Register 4.                                                                                                                                    |

| 9          | DECL2      | Decoupling Node for 2.5 V LDO. Pin should be decoupled with 100 pF, 0.1 $\mu$ F, and 10 $\mu$ F capacitors located close to the pin.                                                                                                                                                                                                                                                                |

| 10         | VCC2       | Power Supply for Internal 2.5 V LDO. The power supply voltage range is 4.75 V to 5.25 V. Supply pin should be decoupled with 100 pF and 0.1 $\mu$ F capacitors located close to the pin.                                                                                                                                                                                                            |

| 12         | DATA       | Serial Data Input. The serial data input is loaded MSB first with the three LSBs being the control bits.                                                                                                                                                                                                                                                                                            |

| 13         | CLK        | Serial Clock Input. This serial clock input is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. Maximum clock frequency is 20 MHz.                                                                                                                                                                                     |

| 14         | LE         | Load Enable. When the LE input pin goes high, the data stored in the shift registers is loaded into one of the six registers, the relevant latch being selected by the first three control bits of the 24-bit word.                                                                                                                                                                                 |

| 16, 32, 33 | NC         | No Connection.                                                                                                                                                                                                                                                                                                                                                                                      |

| 17, 34     | VCCLO      | Power Supply for LO Path. The power supply voltage range is 4.75 V to 5.25 V. Supply pin should be decoupled with 100 pF and 0.1 $\mu$ F capacitors located close to the pin.                                                                                                                                                                                                                       |

| 18,19      | OUTN, OUTP | Mixer IF Outputs. These pins should be pulled to VCC with RF chokes.                                                                                                                                                                                                                                                                                                                                |

| 22         | VCCV2I     | Power Supply for Voltage to Current Input Stage. The power supply voltage range is 4.75 V to 5.25 V. Supply pin should be decoupled with 100 pF and 0.1 µF capacitors located close to the pin.                                                                                                                                                                                                     |

| 25, 26     | INN, INP   | Mixer RF Inputs. Differential RF Inputs. Internally matched to 50 $\Omega$ . This pin must be ac-coupled.                                                                                                                                                                                                                                                                                           |

| 27         | VCCMIX     | Power Supply for Mixer. The power supply voltage range is 4.75 V to 5.25 V. Supply pin should be decoupled with 100 pF and 0.1 $\mu$ F capacitors located close to the pin.                                                                                                                                                                                                                         |

| 29         | IP3SET     | Connect Resistor to VCC to Adjust IP3.                                                                                                                                                                                                                                                                                                                                                              |

| 37, 38     | LON, LOP   | Local Oscillator Input/Output. The internally generated $1 \times f_{LO}$ is available on these pins. When internal LO generation is disabled, an external $2 \times f_{LO}$ or $3 \times f_{LO}$ (depending on divider selection) can be applied to these pins. This pin must be ac-coupled.                                                                                                       |

| 39         | VTUNE      | VCO Control Voltage Input. This pin is driven by the output of the loop filter. Nominal input voltage range on this pin is 1 V to 2.8 V.                                                                                                                                                                                                                                                            |

| 40         | DECL3      | Decoupling Node for VCO LDO. Connect a 100 pF capacitor and a 10 $\mu$ F capacitor between this pin and ground.                                                                                                                                                                                                                                                                                     |

|            | EPAD (EP)  | The exposed paddle must be soldered to a low impedance ground plane.                                                                                                                                                                                                                                                                                                                                |

881

08817-088

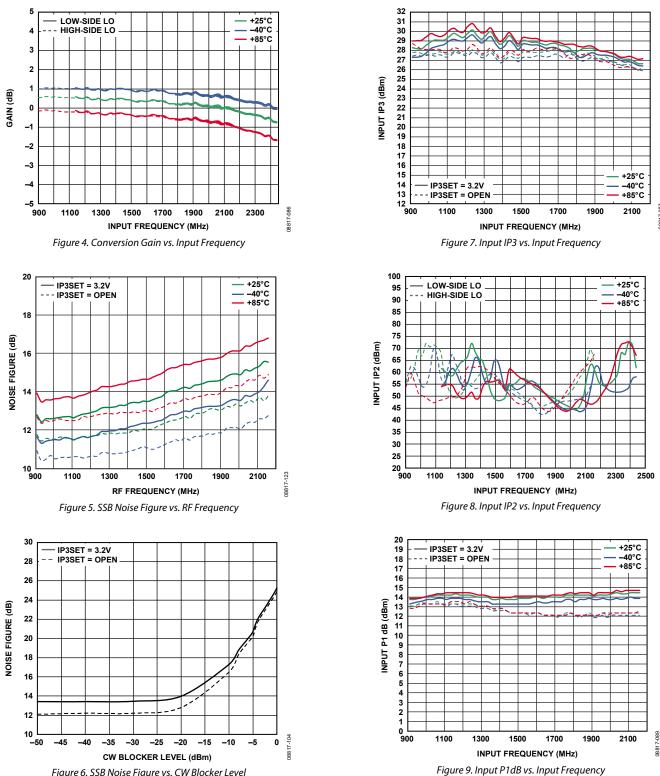

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Vs = 5 V, TA = 25°C, PFD = 20 MHz, REFIN = 20 MHz, IP3SET = 3.2 V, unless otherwise noted.

### **DOWNCONVERSION**

Measured using typical downconversion circuit schematic with high-side LO and 140 MHz IF output, unless otherwise noted.

Figure 6. SSB Noise Figure vs. CW Blocker Level

### UPCONVERSION

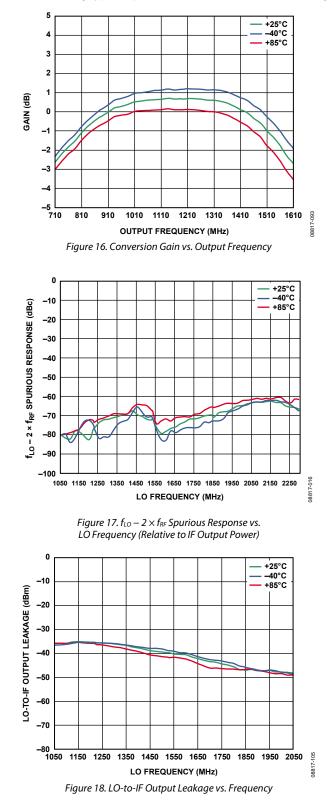

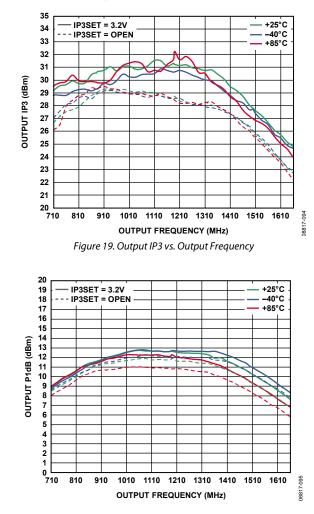

Measured using typical upconversion circuit schematic with high-side LO and 340 MHz RF input, unless otherwise noted.

Figure 20. Output P1dB vs. Output Frequency

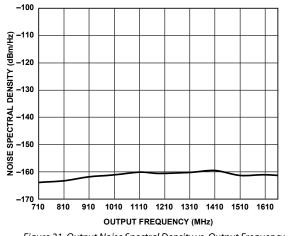

Figure 21. Output Noise Spectral Density vs. Output Frequency

08817-121

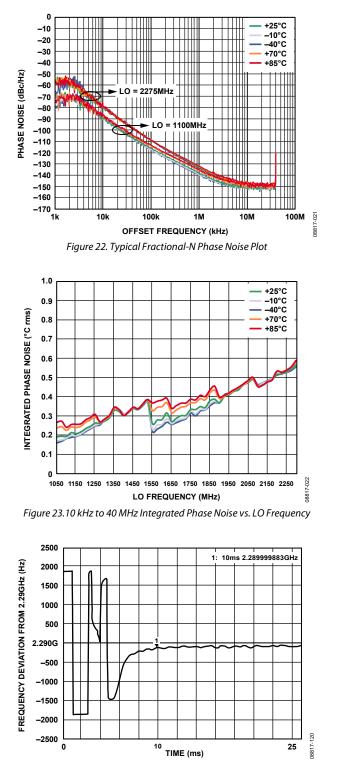

### **PLL CHARACTERISTIC**

Measured using typical downconversion circuit schematic with high-side LO and 140 MHz IF output, loop filter = 1.5 kHz, unless otherwise noted.

Figure 24. Lock Time for 10 MHz Step with 1.5 kHz Loop Filter

### **Data Sheet**

# ADRF6655

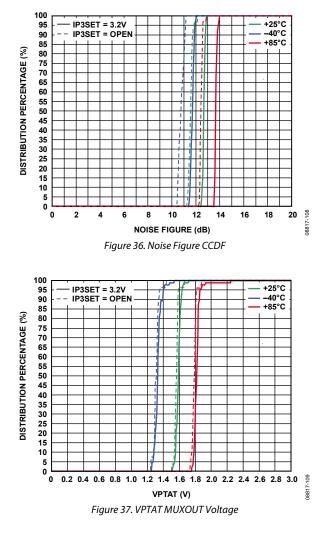

## COMPLIMENTARY CUMULATIVE DISTRIBUTION FUNCTION (CCDF): DOWNCONVERSION, LO = 1100 MHz, RF = 900 MHz

$V_s = 5 V$ ,  $T_A = 25^{\circ}C$ , PFD = 20 MHz, REFIN = 20 MHz, IP3SET = open, as measured using typical downconversion circuit schematic with high-side LO and 200 MHz IF output, unless otherwise noted.

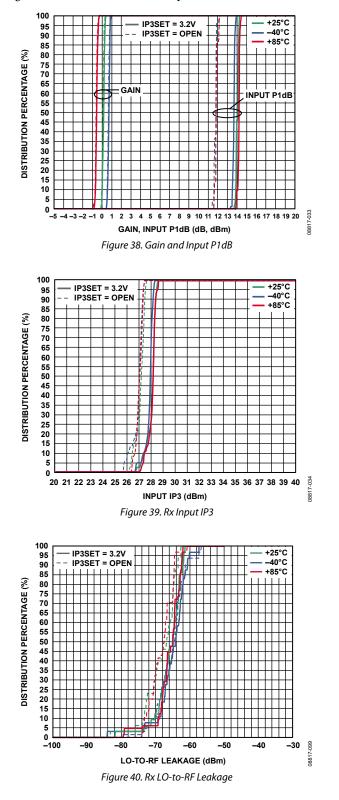

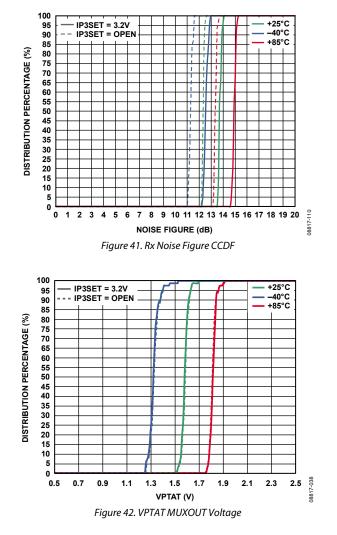

## COMPLIMENTARY CUMULATIVE DISTRIBUTION FUNCTION (CCDF): DOWNCONVERSION, LO = 1700 MHz, RF = 1900 MHz

$V_s = 5 V$ ,  $T_A = 25^{\circ}C$ , PFD = 20 MHz, REFIN = 20 MHz, IP3SET = open, as measured using typical downconversion circuit schematic with high-side LO and 200 MHz IF output, unless otherwise noted.

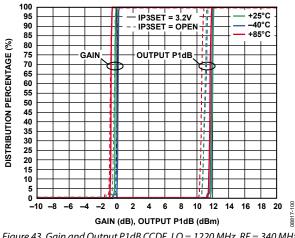

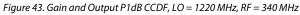

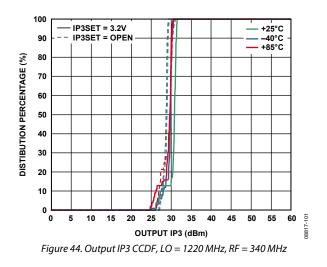

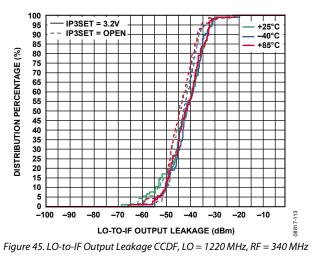

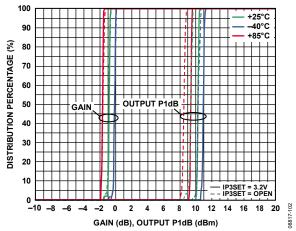

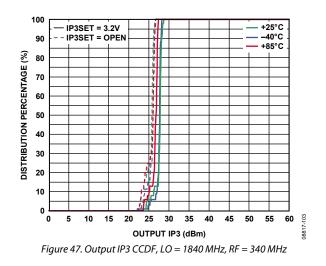

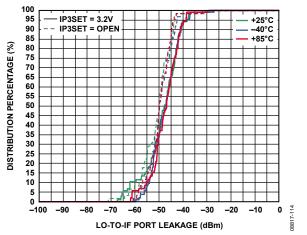

### COMPLIMENTARY CUMULATIVE DISTRIBUTION FUNCTION (CCDF): UPCONVERSION DISTRIBUTION

Figure 46. Gain and Output P1dB CCDF, LO = 1840 MHz, RF = 340 MHz

### **CIRCUIT DESCRIPTION**

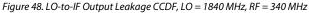

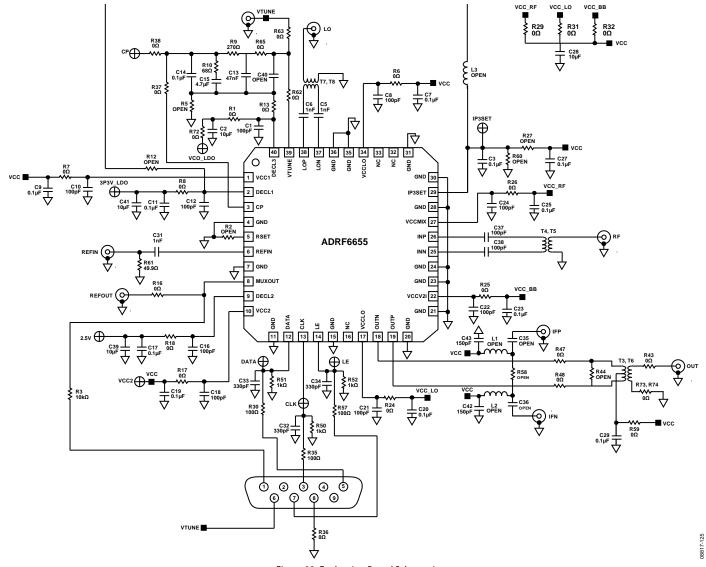

The ADRF6655 can be subdivided into a PLL and VCO block and a mixer block. A detailed circuit description for each block follows.

### PLL AND VCO BLOCK

The PLL and VCO block, shown in Figure 49, is made up of a reference input block, a phase and frequency detector (PFD), a charge pump, a VCO, and a divide-by-N modulus block. An off-chip loop filter completes the loop.

Figure 49. PLL and VCO Block

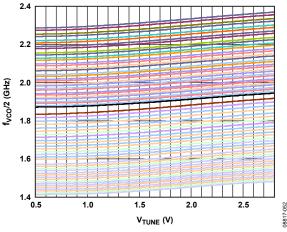

The VCO is implemented with a single core that consists of 64 overlapping bands, as shown in Figure 50. The correct band is selected automatically by the VCO band calibration circuit when Register R0, Register R1, or Register R2 is programmed. The VCO band selection takes roughly 4000 PFD cycles. During calibration, an internal mux is used to disconnect the VCO input voltage from the VTUNE pin and apply an internal reference voltage for calibration. When calibration is complete, the VCO input voltage is reconnected to the VTUNE pin and normal PLL operation resumes.

Figure 50. fvco/2 vs. Tuning Voltage for All 64 Bands

The VCO operates at twice the LO frequency for improved isolation. The nominal value of Kv is 75 MHz/V at the VCO output. As the VCO band is changed from 0 to 63, the size of the varactor is also changed, thus maintaining a roughly constant Kv across the entire operating range.

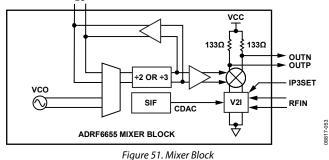

The mixer portion of the ADRF6655, shown in Figure 51, consists of an LO signal chain, an RF voltage-to-current (V-to-I) converter, and a mixer core. The LO chain receives a signal from either the internal VCO or an external LO source. This LO signal then passes through a frequency divider, which can be set to divide-by-2 or divide-by-3, depending on the desired LO frequency. The differential RF inputs are converted into currents by the V-to-I converter and fed into the mixer core. A pair of 133  $\Omega$  pull-up resistors are used to present a ~250  $\Omega$  source impedance at the IF output.

### LO Signal Chain

The LO chain consists of a mux that selects between the internal VCO and an external LO source. The LO signal can then be divided by 2 or divided by 3, providing a wide range of LO frequencies from 1050 MHz to 2300 MHz. A buffer then drives this divided down signal to the mixer core. The LO signal can also be observed via the LO I/O port when the internal VCO is selected. When the external LO buffer is enabled, the supply current and die temperature increase, resulting in a slight degradation of RF performance. In normal operation mode, the external LO buffer should be disabled to help minimize power consumption and provide optimal RF performance.

#### V-to-I Converter

The differential RF input signal is applied to a pair of resistively degenerated common-emitter stages, which converts the differential input voltage to output currents. The input stage also provides 50  $\Omega$  termination to the RF input port. The linearity of this V-to-I stage can be optimized for a given frequency with Pin IP3SET at the expense of power dissipation and noise figure. An additional way of improving linearity without affecting power dissipation or noise figure is provided by the CDAC signal controlled by serial port interface (SPI).

#### **Mixer** Core

The mixer core, based on the Gilbert cell design of four crossconnected transistors, takes the currents from the V-to-I stage and mixes them with the LO signal. This mixer core can be used as a downconvert mixer as is or as an upconvert mixer with an off-chip matching network for a given frequency range.

### **DIGITAL INTERFACES**

The ADRF6655 provides access to the many programmable features available within the IC using a 3-wire SPI control interface. The minimum delays and hold times are presented in the timing diagram in Figure 2. The SPI interface provides digital control of the internal PLL/VCO as well as several other features related to the mixer core, on-chip referencing, and available system monitoring functions. The MUXOUT pin provides access to several output signals that can be selected via the SPI interface. The available outputs are buffered, frequency-scaled versions of the reference, a PLL lock-detect signal, and an internal voltage that is proportional to the IC junction temperature. Details regarding the register settings and initialization sequence are included in the Register Structure section.

NC = NO CONNECT

Figure 52. Basic Circuit Connections

08817-054

### **ANALOG INTERFACES**

The basic circuit connections for a typical ADRF6655 application are presented in Figure 52.

### SUPPLY CONNECTIONS

The ADRF6655 has several supply connections and on-board regulated reference voltages that should be bypassed to ground using low inductance bypass capacitors located in close proximity to the supply and reference pins of the ADRF6655. Specifically Pin 1, Pin 2, Pin 9, Pin 10, Pin 17, Pin 22, Pin 27, and Pin 40 should be bypassed to ground using individual bypass capacitors. Pin 9 is the supply used for the on-board VCO, and for best phase noise performance, several bypass capacitors ranging from 100 pF to 10  $\mu$ F may help to improve phase noise performance. For additional details on bypassing the supply nodes, refer to the evaluation board schematic in Figure 82.

### SYNTHESIZER CONNECTIONS

The ADRF6655 includes an on-board VCO and PLL for LO synthesis. An external reference must be applied for the PLL to operate. The external reference should be ac-coupled and provide a ~1 V p-p nominal input level at Pin 6. The reference is compared to an internally divided version of the VCO output frequency to create a charge pump error current to control and lock the VCO. The charge pump output current is filtered and converted to a VTUNE control voltage through the external loop filter. ADIsimPLL™ can be a helpful tool when designing the external charge pump loop filter. The typical Kv of the VCO, the charge pump output current magnitude, and PFD frequency should all be considered when designing the loop filter. The charge pump current magnitude can be set internally or with an external RSET resistor connected to Pin 5 and ground, along with the internal digital settings applied to the PLL (see the Register 4-Charge Pump, PFD, and Reference Path Control section for more details).

### **OUTPUT MATCHING AND BIASING**

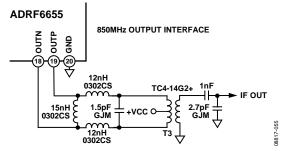

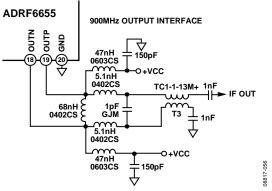

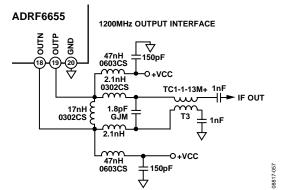

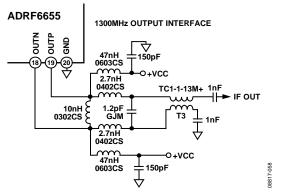

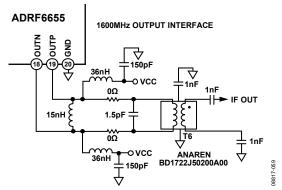

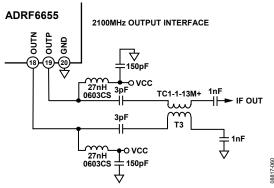

The ADRF6655 output stage consists of collector connected output transistors with on-board pull-up resistors. The output transistors and pull-up network presents a 200  $\Omega$  differential output impedance in parallel with a small amount of shunt capacitance. The measured RC equivalent impedance of Pin 18 and Pin 19 is ~250  $\Omega$ //1.5 pF. This impedance needs to be taken into consideration when designing the external output matching network. In addition to matching the presented output source impedance to the intended load impedance, it is important to provide pull-up choke connections to the supply pins to allow for dc current to directly supply the mixer output transistors. The reactance of the pull-up chokes may need to be considered when designing the output matching network. For convenience, several output matching/bias networks are presented in Figure 53 through Figure 58 for reference.

Figure 53. 850 MHz Output Matching Network Using the Center-Tap of the TC4-14T+ Transformer for Biasing the Open Collector Outputs (Output return loss measured to be better than 12 dB from 800 MHz to 925 MHz.)

Figure 54. 900 MHz Output Matching Network Using the TC1-1-13M+ 1:1 Impedance Ratio Balun and External Pull-Up Choke Inductors (Output return loss measured to be better than 12 dB from 815 MHz to 1075 MHz.)

Figure 55. 1200 MHz Output Matching Network (Output return loss measured to be better than 12 dB from 950 MHz to 1500 MHz.)

Figure 56. 1300 MHz Output Matching Network (Output return loss measured to be better than 12 dB from 1075 MHz to 1525 MHz.)

Figure 57. 1600 MHz Output Matching Network (Output return loss measured to be better than 12 dB from 1400 MHz to 1680 MHz.)

Figure 58. 2100 MHz Output Matching Network (Output return loss measured to be better than 12 dB from 2000 MHz to 2200 MHz.)

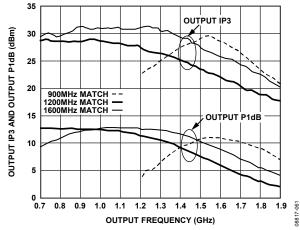

Figure 59. Measured Output Linearity for 900 MHz, 1200 MHz, and 1600 MHz Matching Networks (See Figure 54, Figure 55, and Figure 57 for Implementation)

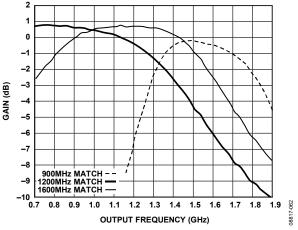

Figure 60. Measured Conversion Gain for 900 MHz, 1200 MHz, and 1600 MHz Matching Networks (See Figure 54, Figure 55, and Figure 57 for Implementation)

#### **INPUT MATCHING**

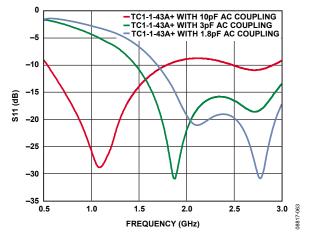

The ADRF6655 uses a balanced 50  $\Omega$  input impedance to help simplify external connections. For low loss interfacing, the driving source should be transformed to present a balanced 50  $\Omega$  source impedance. An appropriate 1:1 impedance ratio input balun should be used when attempting to interface to an unbalanced 50  $\Omega$ source. For input frequencies below ~1.5 GHz, the TC1-1-13M+ from Mini-Circuits or similar baluns should provide good return loss and maximum power gain. For higher frequencies, baluns, such as the TC1-1-43A+, are recommended for lowest insertion loss. The ac coupling capacitors can be optimized with the balun to provide optimum input match. A few examples are provided in Figure 61 for a range of different IF output frequencies.

Figure 61. Measured RF Input Return Loss Using the TC1-1-43A+ 1:1 Balun (Plotted for Several AC Coupling Capacitor Values)

It is also possible to use lumped element LC lattice networks to transform an unbalanced source into a balanced source at the mixer input pins. In either case, the mixer input pins should be dc blocked using adequately sized series capacitors.

#### **IP3SET LINEARIZATION FEATURE**

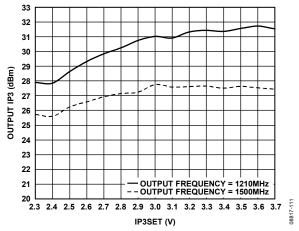

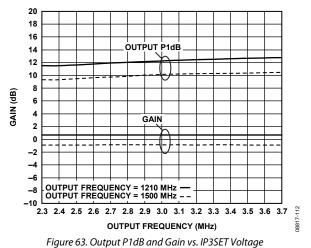

The IP3SET pin (Pin 29) controls the overall current consumption of the mixer core depending on the applied voltage. If left open, the voltage on the IP3SET pin is ~2.3 V, and a typical input IP3 of ~25 dBm or higher can be expected across the operating frequency range. As the IP3SET voltage is increased, the overall supply current increases and the input IP3 can be improved from ~3 dB to 6 dB. For upconversion applications, an IP3SET voltage of ~3.2 V to 3.3 V results in very high output IP3 performance in excess of 30 dBm. Using an external resistor divider network connected between VCC and GND, the IP3SET voltage can be derived. Alternatively, the on-board 3.3 V LDO output (Pin 2) can be used to derive the applied IP3SET voltage. However, it is advisable to use good bypassing and a series inductor or ferrite choke to ensure good high frequency isolation between Pin 1 and Pin 29. If an auxiliary control DAC is available, the IP3SET pin can be driven dynamically in applications where power levels are changing over time, and it is desirable to conserve power at lower input signal levels. Figure 62 and Figure 63 illustrate the output linearity dependency on the IP3SET voltage. Note that gain is independent of the IP3SET voltage.

Figure 62. Output IP3 vs. IP3SET Voltage for Output Frequency

#### **CDAC LINEARIZATION FEATURE**

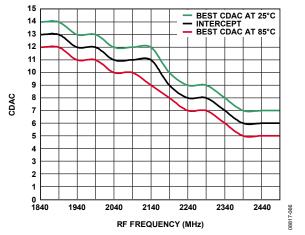

In addition to the IP3SET broadband linearization solution, the ADRF6655 also includes a special linearizer designed to provide enhanced IP3 performance at higher input frequencies. At low input frequencies, the CDAC setting offers very little influence on input IP3, and a CDAC setting of 15 is usually recommended. At high input frequencies, the CDAC setting can boost input IP3 as much as 5 dB with essentially no increase in supplied power. At a given input frequency, the ADRF6655 offers an optimum CDAC setting to provide high input IP3 performance. The recommended optimum CDAC setting vs. RF input frequency is shown in Figure 64.

Figure 64. Optimum CDAC Setting for Downconversion vs. RF Input Frequency

#### **EXTERNAL LO INTERFACE**

The ADRF6655 provides the option to use an external signal source for the LO into the mixer. It is important to note that the applied LO signal is divided by 2 or divided by 3 prior to the actual mixer core within the ADRF6655. The divider is determined by the register settings in LO path and mixer control register, (see the Register 5—LO Path and Mixer Control section). The LO input pins (Pin 37 and Pin 38) present a broadband balanced 50  $\Omega$  input interface similar to the input pins (Pin 25 and Pin 26). The LOP and LON input pins should be dc blocked and driven from a balanced 50  $\Omega$  source. When not in use, the LOP and LON pins may be left unconnected.

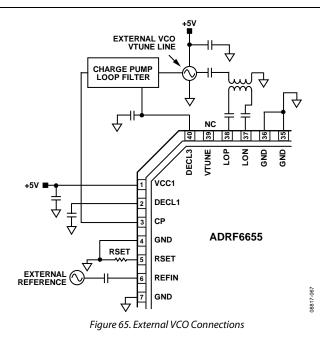

#### **USING AN EXTERNAL VCO**

The ADRF6655 has the necessary provisions for interfacing an external VCO. A high performance discrete VCO may be desirable in applications that call for the very best phase noise performance. The basic circuit connections for interfacing an external VCO are included in Figure 65. It is important to select a VCO with a frequency tuning voltage range that covers the available charge pump output compliance range of 1 V to 2.8 V. The external VCO waveform needs to pass through the on-chip divide-by-2/divideby-3 programmable dividers before reaching the mixer. As a result, the VCO center frequency should be selected to be roughly 2× or 3× the desired LO signal frequency. The available output power for the selected VCO should be greater than -10 dBm to ensure adequate signal levels into the mixer core. The charge pump loop filter components should be designed to provide adequate phase margin for the given K<sub>VCO</sub> tuning sensitivity of the selected VCO. It is important to properly configure the digital registers for external VCO operation. When using an external VCO, the internal VCO should be disabled using DB17 in Register 6. Other register programmable LDOs, including the VCO LDO (DB18 in Register 6), should be enabled. For more information on programming the ADRF6655, see the ADRF6655 Control Software section.

### ADRF6655 CONTROL SOFTWARE

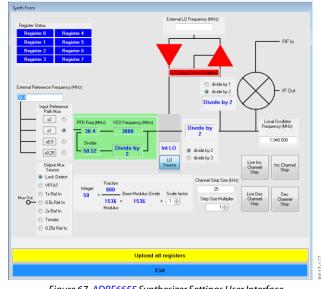

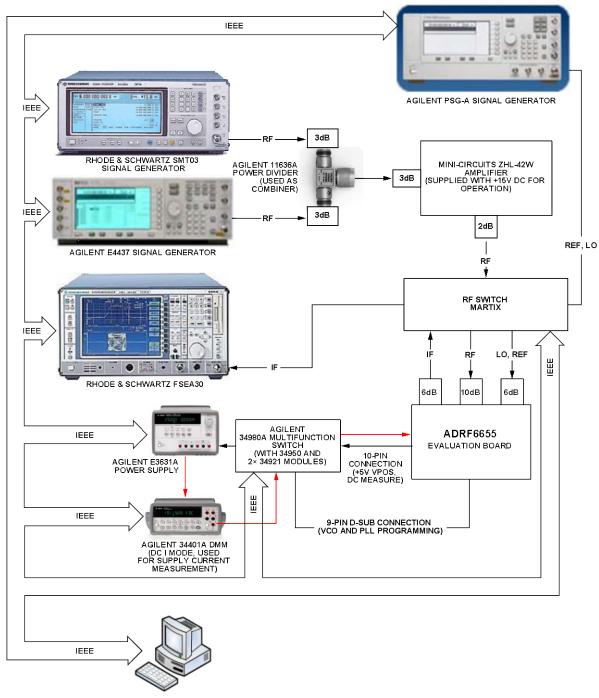

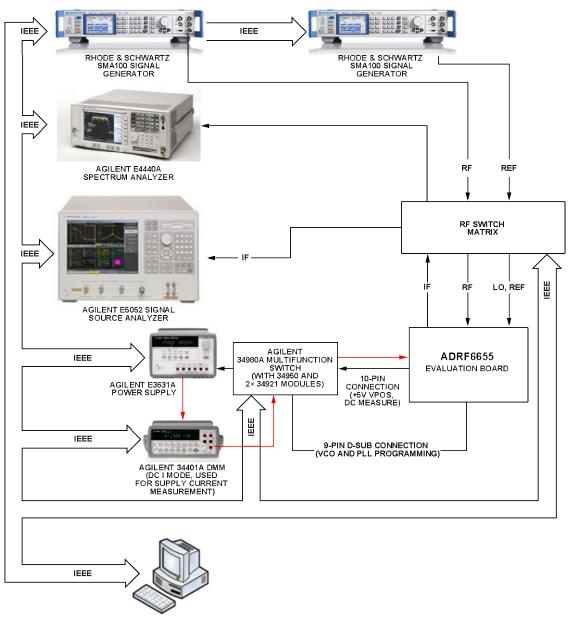

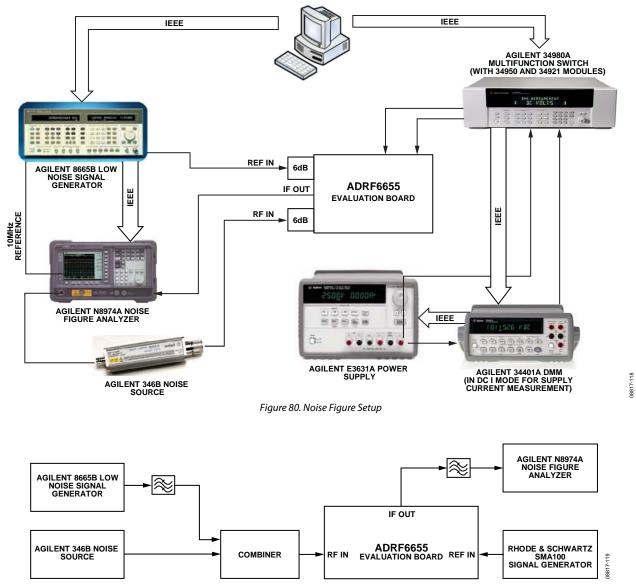

The ADRF6655 can be controlled from PCs that include a USB port. The basic user interfaces are shown in Figure 66 and Figure 67.

After launching the software, the user is prompted to select a device from the ADRF product family. Upon selecting the ADRF6655, the main control interface appears as shown in Figure 66. The main control interface allows the user to configure the device for various modes of operation. The internal synthesizer is controlled by clicking on any of the numeric values listed in the RF Section. Attempting to program the Ref Input Frequency, the PFD Frequency, the VCO Frequency(2xLO), or other values in the RF Section launches the control module shown in Figure 67. From the synthesizer settings control interface, the user can enter the desired Local Oscillator Frequency (MHz), Channel Step Size (kHz), and External Reference Frequency (MHz). The user can also enable the LO output buffer and divider options from this menu. After setting the desired values, it is important to click Upload all registers for the new settings to take effect.

|                                 |           |        | DE 0                                |                  |       |                                     | n (0)                              |                 |           |        |        |  |  |  |

|---------------------------------|-----------|--------|-------------------------------------|------------------|-------|-------------------------------------|------------------------------------|-----------------|-----------|--------|--------|--|--|--|

| 0 Path and Modulator Control    |           |        | RF Section                          |                  |       | -                                   | Pump (CF                           |                 |           |        |        |  |  |  |

| LO Output Driver Disabled       |           |        | Divide Mode                         | Fractional       | •     | Current                             | Reference                          | e Source        |           |        | e) 🗸   |  |  |  |

| Mixer LO Source - Internal VC   | 0         |        | Ref Input Frequency                 | 38.4 MHz         |       | Current                             | Multiplier                         |                 | ×2        | •      |        |  |  |  |

| Mixer Bias Enabled              | _         |        | PFD Frequency                       | 38.4 MHz         |       | CP Cu                               | rrent (u/                          | <b>()</b> =     |           |        |        |  |  |  |

|                                 |           |        | Modulus                             | 1536             |       | 500uA                               |                                    |                 |           |        |        |  |  |  |

| Div-by-2 in LO Output Chain Ena | bled      |        | VCO Frequency(2xLO)<br>LO Frequency | 3880<br>1940 MHz |       | Charge                              | Pump Co                            | ntrol           | Hi-Z      |        | •      |  |  |  |

| PLL Enabled                     |           |        | Channel Step Size                   | 25 kHz           |       | CP Cor                              | trol Source                        |                 | PFD       |        | -      |  |  |  |

|                                 |           |        | charine step size                   |                  |       | 0.00                                |                                    | ~<br>ise Offset |           | (0.01) |        |  |  |  |

|                                 |           |        |                                     |                  |       | R                                   | PFD Pha                            |                 |           |        |        |  |  |  |

|                                 |           |        |                                     |                  |       |                                     | PFD Phase Offset Polarity positive |                 |           |        |        |  |  |  |

|                                 |           |        |                                     |                  |       | hase Office                         |                                    | 112.5*          |           |        |        |  |  |  |

|                                 |           |        |                                     |                  |       | 11011                               | ISSO OTISO                         | n.              | 112.0     | 3      |        |  |  |  |

| lutput Reference Mux Source     |           |        | VEO Controls and Enal               | bles             |       | PFD                                 |                                    |                 |           |        |        |  |  |  |

| Lock Detect                     | -         |        | VOD Enable                          | Enab             | le 👻  |                                     | vider Path                         |                 | nsitivity |        |        |  |  |  |

| DM Dither Control               |           |        | VCD LDD Enable                      | Enal             | le 👻  | PED Beference Path Edge Sensitivity |                                    |                 |           |        |        |  |  |  |

| Dither Bestart Value            |           |        | 3.3V LDO Enable                     | Enab             | le 🗸  |                                     |                                    |                 |           |        |        |  |  |  |

| SDM Dither Enable               | Dither En |        |                                     | Enat             | le 👻  |                                     |                                    |                 |           |        |        |  |  |  |

|                                 | 1         | - 11   | Charge Pump Enabl                   | Diss             | ale 💌 |                                     | vti Backla:                        |                 |           |        |        |  |  |  |

| 6DM Dither Magnitude            |           | •      | External VCD Enable                 |                  |       | Unsec                               |                                    |                 |           |        |        |  |  |  |

| /CO Band Select from SPI        | 32        |        | VEB Switch Control                  | from SPI         |       |                                     |                                    |                 |           |        |        |  |  |  |

| /CD Amplitude Setting           | 55        |        | Regular                             |                  | •     | Cap DAG                             |                                    | 0               |           |        |        |  |  |  |

| /CD Band Select and SW Source   |           | •      | All Registe                         | ers Updated      |       | Spare (R                            | 7) Value                           | 0               |           |        |        |  |  |  |

| To be Loaded in Registers or    |           |        |                                     | 1                |       | To be Lo                            |                                    |                 | s on N    |        |        |  |  |  |

| MSB Binary                      | LSB       | Hex    |                                     | R4 Upt           |       | MSB                                 |                                    | inary           |           | LSB    | Hex    |  |  |  |

| 000 0000 0000 0001 1001         | 0 000     | 000190 | R1 Updated                          | R5 Upt           | lated | 0000 101                            | 0 1010                             | 0111 1          | 010 0     | 100    | 8aa7a4 |  |  |  |

| 000 0000 0011 0000 0000         | 0 001     | 003001 |                                     |                  |       | 0000 000                            | 0000                               | 0000 1          | 100 0     | 101    | 0000c5 |  |  |  |

| 000 0000 0001 1001 0000         | 0 010     | 001902 | R2 Updated                          | R6Upt            | ated  | 0001 111                            | 0 1101                             | 1101 0          | 000 0     | 110    | 1edd06 |  |  |  |

| 110 0000 0000 0000 0000         | 1 011     | 600001 | R3 Updated                          | B7 Upt           | lated | 0000 000                            | 0000                               | 0000 0          | 000 0     | 111    | 000007 |  |  |  |

Figure 66. ADRF6655 Software Control Interface

Figure 67. ADRF6655 Synthesizer Settings User Interface

#### PLL LOOP FILTER DESIGN

Designing the external loop filter, which connects between the charge pump output and VCO tuning control pin, is easy with the help of ADIsimPLL. ADIsimPLL is a free software application available from Analog Devices for designing PLL loop filters. Several passive filter topologies are support in ADIsimPLL along with the necessary component placements on the evaluation board.

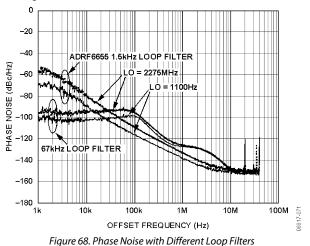

When designing a PLL loop filter, it is important to consider settling time and phase noise requirements. Figure 68 provides measured phase noise performance for a typical fast and slow loop filter design. Note that the wider loop filter offers better close-in phase noise but degraded phase noise at greater offset frequencies. The narrow 1.5 kHz loop filter design provides the best phase noise at 100 kHz and 1 MHz carrier offsets but with the penalty of decreased frequency settling time and poorer close-in performance.

### **REGISTER STRUCTURE**

#### INTEGER DIVIDE CONTROL REGISTER (R0)

| RESERVED |      |      |      |      |      |      |      |      |      |      | DIVIDE<br>MODE |      |      |     |     |     |     |     | CONTROL BITS |     |       |       |       |

|----------|------|------|------|------|------|------|------|------|------|------|----------------|------|------|-----|-----|-----|-----|-----|--------------|-----|-------|-------|-------|

| DB23     | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12           | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4          | DB3 | DB2   | DB1   | DB0   |

| 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0              | 0    | DM   | ID6 | ID5 | ID4 | ID3 | ID2 | ID1          | ID0 | C3(0) | C2(0) | C1(0) |

#### MODULUS DIVIDE CONTROL REGISTER (R1)

|      | RESERVED |      |      |      |      |      |      |      |      | MODULUS DIVIDE VALUE |      |      |      |     |     |     |     |     |     |     | CONTROL BITS |       |       |  |

|------|----------|------|------|------|------|------|------|------|------|----------------------|------|------|------|-----|-----|-----|-----|-----|-----|-----|--------------|-------|-------|--|

| DB23 | DB22     | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13                 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2          | DB1   | DB0   |  |

| 0    | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | MD10                 | MD9  | MD8  | MD7  | MD6 | MD5 | MD4 | MD3 | MD2 | MD1 | MD0 | C3(0)        | C2(0) | C1(1) |  |

#### FRACTIONAL DIVIDE CONTROL REGISTER (R2)

|      |                                                         |   |   | RESE |   |   |   |   | FRACTI | ONAL | DIVIDE | VALU | IE   |     |     |     | CON | TROL | SITS |     |       |       |       |

|------|---------------------------------------------------------|---|---|------|---|---|---|---|--------|------|--------|------|------|-----|-----|-----|-----|------|------|-----|-------|-------|-------|

| DB23 | RESERVED<br>323 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 |   |   |      |   |   |   |   |        | DB13 | DB12   | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5  | DB4  | DB3 | DB2   | DB1   | DB0   |

| 0    | 0                                                       | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0      | PD10 | PD9    | PD8  | PD7  | PD6 | PD5 | PD4 | PD3 | PD2  | PD1  | PD0 | C3(0) | C2(1) | C1(0) |

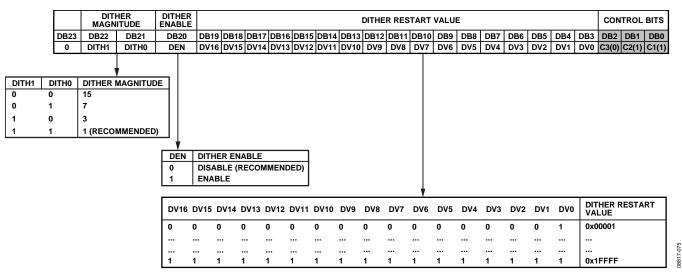

#### Σ-Δ MODULATOR DITHER CONTROL REGISTER (R3)

|      | DITI<br>MAGN |       | DITHER<br>ENABLE |      |      |      |      |      |      |      | DITHE | RRES | TART V | ALUE |     |     |     |     |     |     | CON   | ITROL I | BITS  |

|------|--------------|-------|------------------|------|------|------|------|------|------|------|-------|------|--------|------|-----|-----|-----|-----|-----|-----|-------|---------|-------|

| DB23 | DB22         | DB21  | DB20             | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12  | DB11 | DB10   | DB9  | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2   | DB1     | DB0   |

| 0    | DITH1        | DITH0 | DEN              | DV16 | DV15 | DV14 | DV13 | DV12 | DV11 | DV10 | DV9   | DV8  | DV7    | DV6  | DV5 | DV4 | DV3 | DV2 | DV1 | DV0 | C3(0) | C2(1)   | C1(1) |

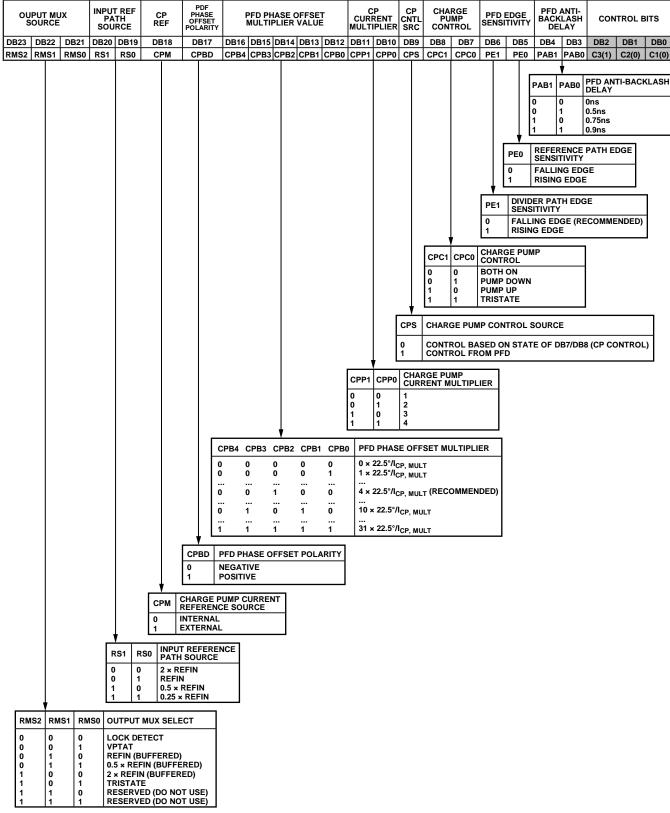

#### CHARGE PUMP, PFD, AND REFERENCE PATH CONTROL REGISTER (R4)

|      | JPUT MU<br>SOURCE | JX   | INPU <sup>-</sup><br>PA<br>SOU |      | CP<br>REF | F OFFSET MULTIPLIER VALUE |      | -    | CURI | ;P<br>RENT<br>IPLIER | CP<br>CNTL<br>SRC | CHA<br>PU<br>CON | MP   | PFD I<br>SENSI |      | PFD<br>BACK<br>DE |     | CON | TROL B | ытѕ  |       |       |       |

|------|-------------------|------|--------------------------------|------|-----------|---------------------------|------|------|------|----------------------|-------------------|------------------|------|----------------|------|-------------------|-----|-----|--------|------|-------|-------|-------|

| DB23 | DB22              | DB21 | DB20                           | DB19 | DB18      | DB17                      | DB16 | DB15 | DB14 | DB13                 | DB12              | DB11             | DB10 | DB9            | DB8  | DB7               | DB6 | DB5 | DB4    | DB3  | DB2   | DB1   | DB0   |

| RMS2 | RMS1              | RMS0 | RS1                            | RS0  | СРМ       | CPBD                      | CPB4 | СРВЗ | CPB2 | CPB1                 | CPB0              | CPP1             | CPP0 | CPS            | CPC1 | CPC0              | PE1 | PE0 | PAB1   | PAB0 | C3(1) | C2(0) | C1(0) |

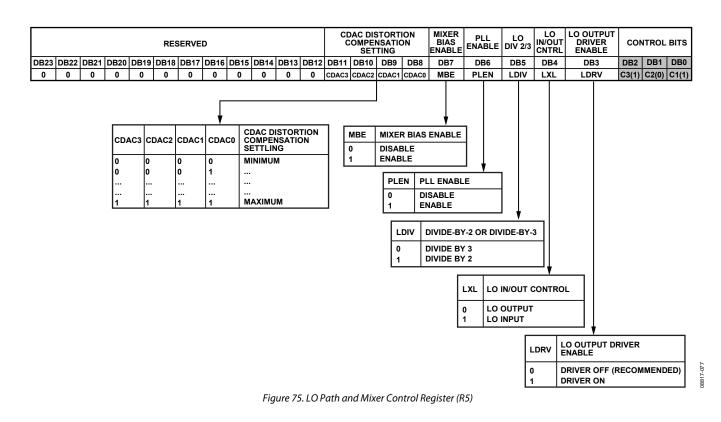

#### LO PATH AND MIXER CONTROL REGISTER (R5)

|      |      |      |      |      | RES  | ERVE | )    |      |      |      |      |       | AC DIS<br>DMPEN<br>SET | ISATIC | Ň     | MIXER<br>BIAS<br>ENABLE | PLL<br>ENABLE |      | IN/OUT | LO OUTPUT<br>DRIVER<br>ENABLE |       | NTROL | вітѕ  |

|------|------|------|------|------|------|------|------|------|------|------|------|-------|------------------------|--------|-------|-------------------------|---------------|------|--------|-------------------------------|-------|-------|-------|

| DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11  | DB10                   | DB9    | DB8   | DB7                     | DB6           | DB5  | DB4    | DB3                           | DB2   | DB1   | DB0   |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | CDAC3 | CDAC2                  | CDAC1  | CDAC0 | MBE                     | PLEN          | LDIV | LXL    | LDRV                          | C3(1) | C2(0) | C1(1) |

#### VCO CONTROL AND PLL ENABLES REGISTER (R6)

| R    | ESERV | ED   | CHARGE<br>PUMP<br>ENABLE | LDO<br>3.3V<br>ENABLE | VCO<br>LDO<br>ENABLE | VCO<br>ENABLE | VCO<br>SWITCH<br>CONTROL |      | 'CO AI | MPLIT | UDE S | ETTIN | G    | VCO<br>BS<br>SRC |      | vco  | BAN  | D SEL | ЕСТ  |      | CON   | ITROL | BITS  |

|------|-------|------|--------------------------|-----------------------|----------------------|---------------|--------------------------|------|--------|-------|-------|-------|------|------------------|------|------|------|-------|------|------|-------|-------|-------|