## ADSP-BF52x Blackfin Processor Hardware Reference

Revision 1.2, February 2013

Part Number 82-000525-03

Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106

## **Copyright Information**

© 2013 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

Printed in the USA.

#### Disclaimer

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

#### Trademark and Service Mark Notice

The Analog Devices logo, Blackfin, CrossCore, EngineerZone, EZ-KIT Lite, and VisualDSP++ are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

# **CONTENTS**

## **PREFACE**

| Purpose of This Manual       |

|------------------------------|

| Intended Audience lxi        |

| Manual Contents              |

| What's New in This Manual    |

| Technical Support            |

| Supported Processors lxviii  |

| Product Information          |

| Analog Devices Web Site      |

| EngineerZone                 |

| Notation Conventions lxx     |

| Register Diagram Conventions |

| INTRODUCTION                 |

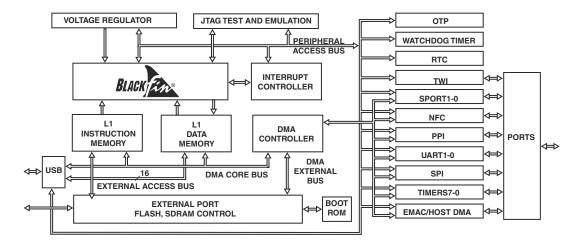

| Peripherals 1-1              |

| Memory Architecture          |

| Internal Memory              |

| External Memory 1-5          |

| I/O Memory Space 1-                      | 6 |

|------------------------------------------|---|

| One-Time-Programmable (OTP) Memory 1-    | 6 |

| DMA Support                              | 7 |

| External Bus Interface Unit              | 8 |

| SDRAM Controller 1-                      | 9 |

| Asynchronous Controller 1-               | 9 |

| Ports 1-                                 | 9 |

| General-Purpose I/O (GPIO) 1-1           | 0 |

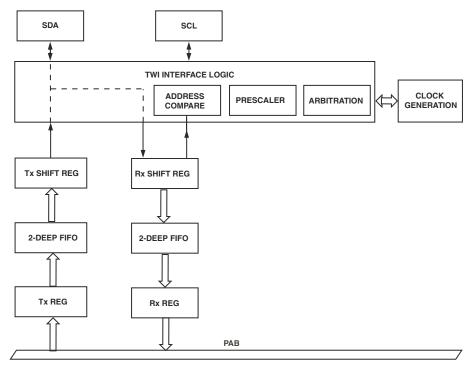

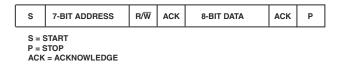

| Two-Wire Interface 1-1                   | 1 |

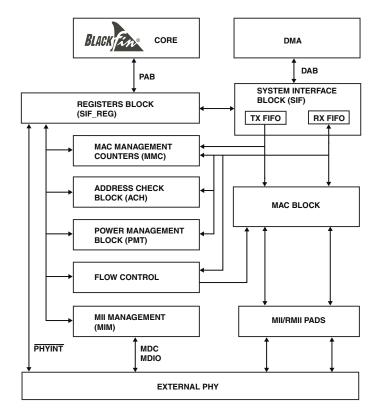

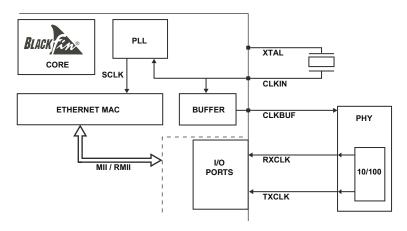

| Ethernet MAC                             | 2 |

| Parallel Peripheral Interface            | 2 |

| SPORT Controllers 1-1-                   | 4 |

| Serial Peripheral Interface (SPI) Port   | 6 |

| Timers 1-1                               | 7 |

| UART Ports                               | 7 |

| Security 1-1                             | 9 |

| Real-Time Clock                          | 0 |

| Watchdog Timer 1-2                       | 1 |

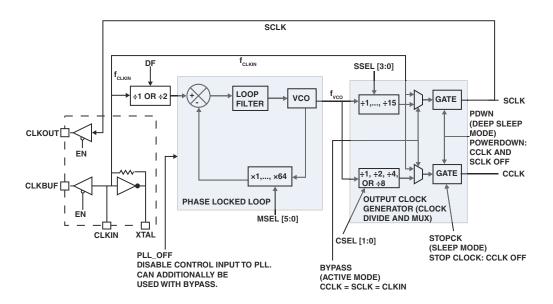

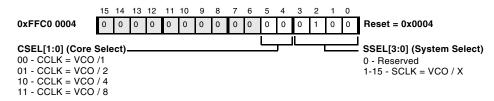

| Clock Signals                            | 1 |

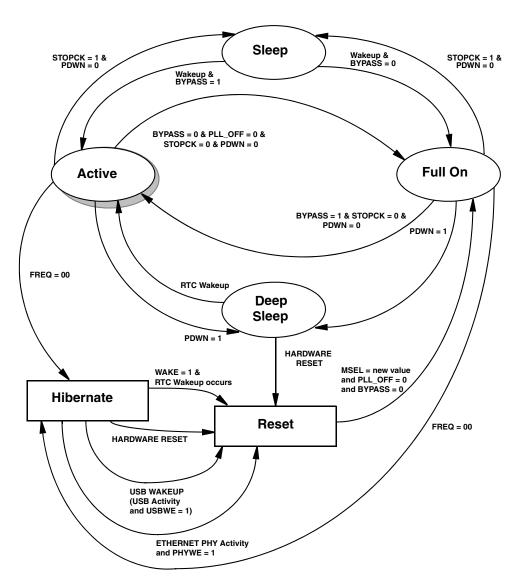

| Dynamic Power Management 1-2             | 2 |

| Full-On Mode (Maximum Performance) 1-2   | 2 |

| Active Mode (Moderate Power Savings) 1-2 | 3 |

| Sleep Mode (High Power Savings) 1-2      | 3 |

| Deep Sleep Mode (Maximum Power Savings)                        | 1-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hibernate State                                                | 1-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

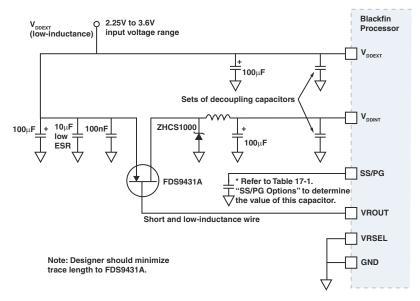

| Voltage Regulation                                             | 1-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Instruction Set Description                                    | 1-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Development Tools                                              | 1-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

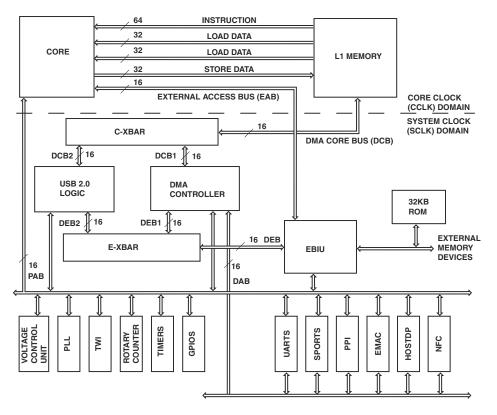

| CHIP BUS HIERARCHY                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Overview                                                       | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Interface Overview                                             | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Internal Clocks                                                | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Core Bus Overview                                              | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Peripheral Access Bus (PAB)                                    | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PAB Arbitration                                                | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PAB Agents (Masters, Slaves)                                   | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PAB Performance                                                | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DMA Access Bus (DAB), DMA Core Bus (DCI DMA External Bus (DEB) | The state of the s |

| DAB, DCB, DEB Arbitration                                      | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DCB Sharing                                                    | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Using the CDPRIO Bit to Change Priorit                         | ies 2-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DAB Bus Agents (Masters)                                       | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DAB, DCB, and DEB Performance                                  | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| External Access Bus (EAB)                                      | 2-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Arbitration of the External Bus                                | 2-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DEB/EAB Performance                                            | 2-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

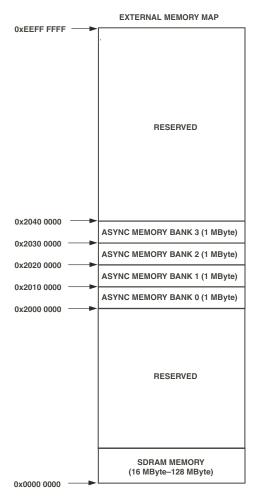

## **MEMORY**

|   | Memory Architecture                          | 3-1              |

|---|----------------------------------------------|------------------|

|   | L1 Instruction SRAM                          | 3-3              |

|   | L1 Data SRAM                                 | 3-4              |

|   | L1 Data Cache                                | 3-4              |

|   | Boot ROM                                     | 3-5              |

|   | External Memory                              | 3-5              |

|   | Processor-Specific MMRs                      | 3-5              |

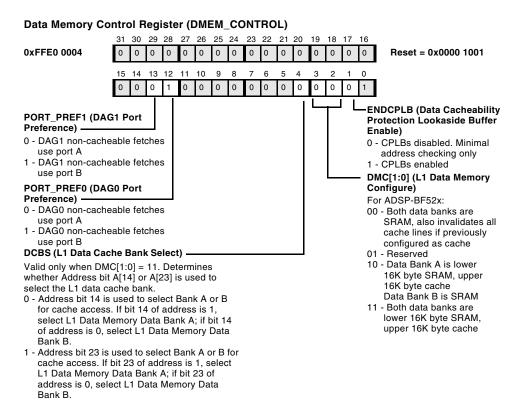

|   | DMEM_CONTROL Register                        | 3-6              |

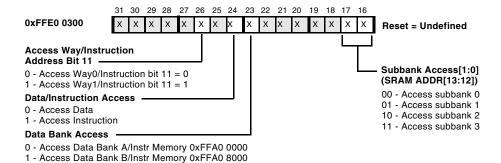

|   | DTEST_COMMAND Register                       | 3-6              |

| ( | ONE-TIME PROGRAMMABLE MEMORY                 |                  |

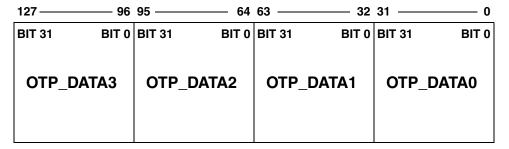

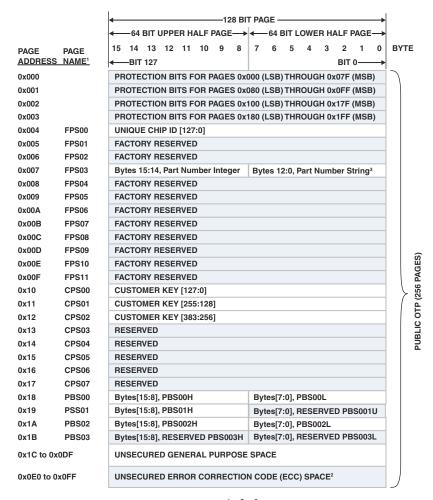

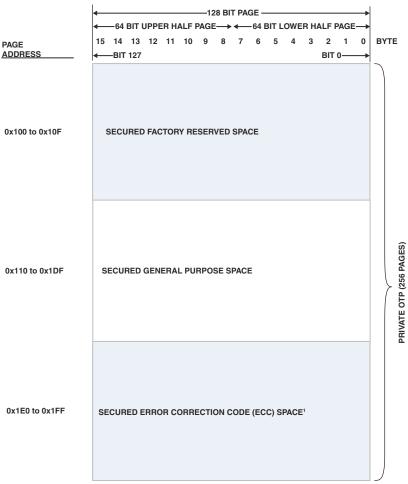

|   | OTP Memory Overview                          | 4-2              |

|   | OTP Memory Map                               | 4-3              |

|   | Error Correction                             | 4-8              |

|   | Error Correction Policy                      | 4-8              |

|   | OTP Access                                   | <del>1</del> -10 |

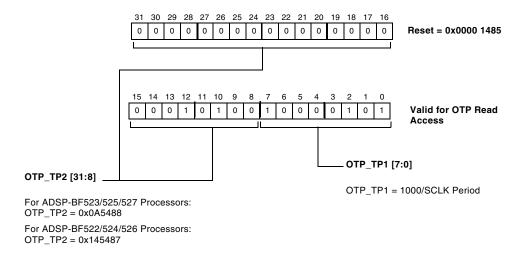

|   | OTP Timing Parameters                        | 4-12             |

|   | Timing for the ADSP-BF523/525/527 Processors | 4-13             |

|   | Timing for the ADSP-BF522/524/526 Processors | 4-14             |

|   | OTP_TIMING Register                          | <del>1</del> -17 |

|   | Callable ROM Functions for OTP ACCESS        | <del>1</del> -17 |

|   | Initializing OTP                             | 4-17             |

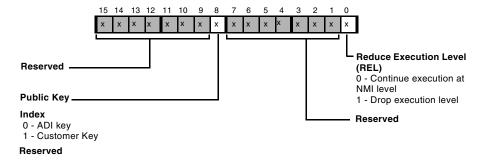

|   | bfrom_OtpCommand                             | <del>1</del> -18 |

|   |                                              |                  |

| Programming and Reading OTP 4-20                       |

|--------------------------------------------------------|

| bfrom_OtpRead                                          |

| bfrom_OtpWrite 4-21                                    |

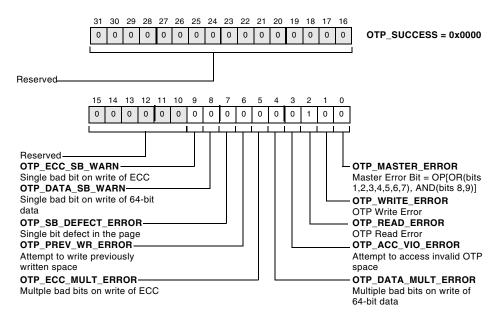

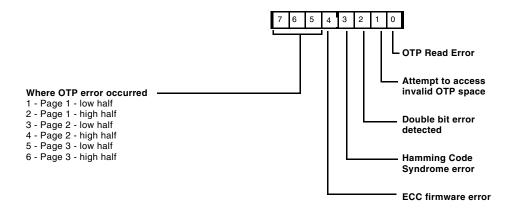

| Error Codes                                            |

| Write-protecting OTP Memory                            |

| Accessing Private OTP Memory                           |

| OTP Programming Examples                               |

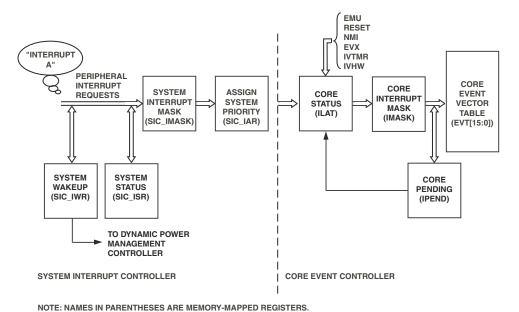

| SYSTEM INTERRUPTS                                      |

| Specific Information for the ADSP-BF52x 5-1            |

| Overview 5-1                                           |

| Features                                               |

| Description of Operation                               |

| Events and Sequencing 5-2                              |

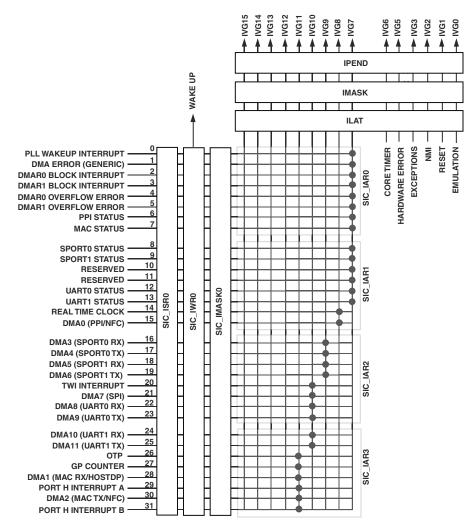

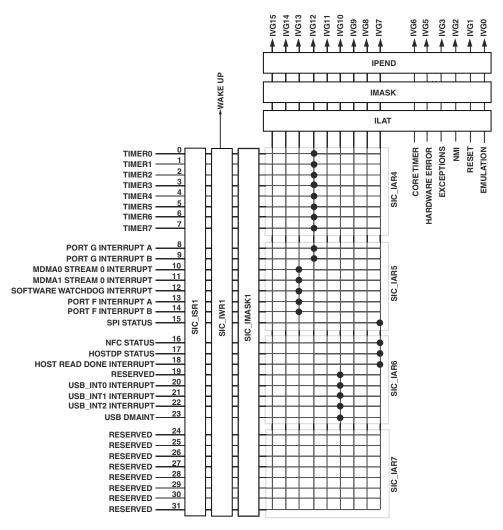

| System Peripheral Interrupts                           |

| Programming Model                                      |

| System Interrupt Initialization                        |

| System Interrupt Processing Summary 5-8                |

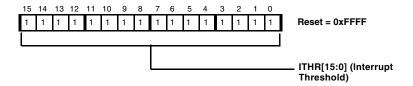

| System Interrupt Controller Registers                  |

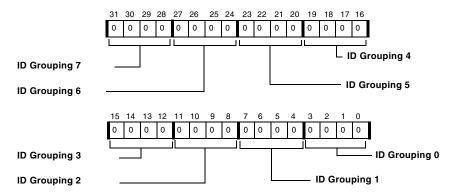

| System Interrupt Assignment (SIC_IAR) Register 5-11    |

| System Interrupt Mask (SIC_IMASK) Register 5-12        |

| System Interrupt Status (SIC_ISR) Register 5-12        |

| System Interrupt Wakeup-Enable (SIC_IWR) Register 5-13 |

| Programming Examples                                   |

| Clearing Interrupt Requests                            |

| Unique Behavior for the ADSP-BF52x Processor | 5-16 |

|----------------------------------------------|------|

| Interfaces                                   | 5-16 |

| System Peripheral Interrupts                 | 5-19 |

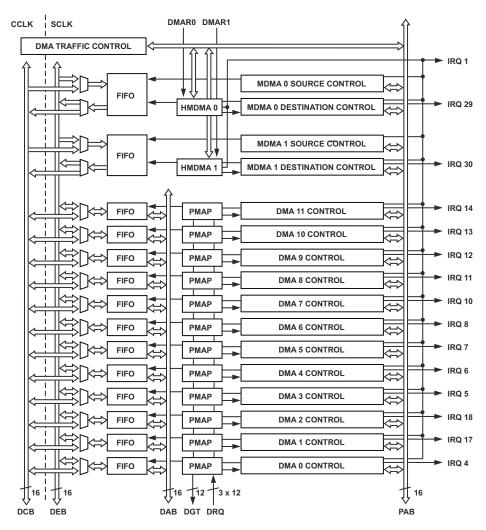

| DIRECT MEMORY ACCESS                         |      |

| Specific Information for the ADSP-BF52x      | 6-1  |

| Overview and Features                        | 6-2  |

| DMA Controller Overview                      | 6-4  |

| External Interfaces                          | 6-4  |

| Internal Interfaces                          | 6-5  |

| Peripheral DMA                               | 6-6  |

| Memory DMA                                   | 6-7  |

| Handshaked Memory DMA (HMDMA) Mode           | 6-9  |

| Modes of Operation                           | 6-10 |

| Register-Based DMA Operation                 | 6-10 |

| Stop Mode                                    | 6-11 |

| Autobuffer Mode                              | 6-12 |

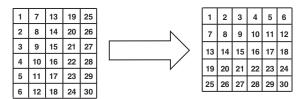

| Two-Dimensional DMA Operation                | 6-12 |

| Examples of Two-Dimensional DMA              | 6-13 |

| Descriptor-based DMA Operation               | 6-14 |

| Descriptor List Mode                         | 6-15 |

| Descriptor Array Mode                        | 6-16 |

| Variable Descriptor Size                     | 6-16 |

| Mixing Flow Modes                            | 6-17 |

|                                              |      |

| Functional Description               | 5-18 |

|--------------------------------------|------|

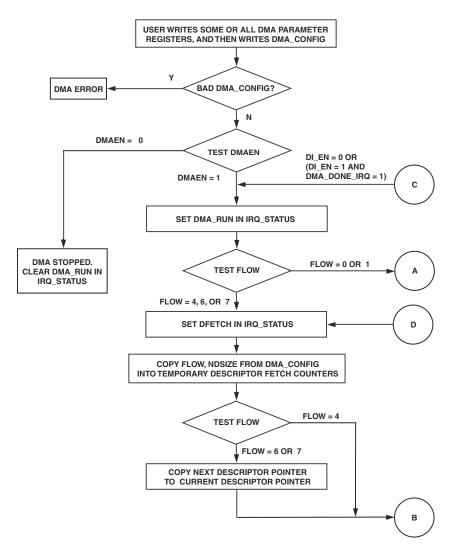

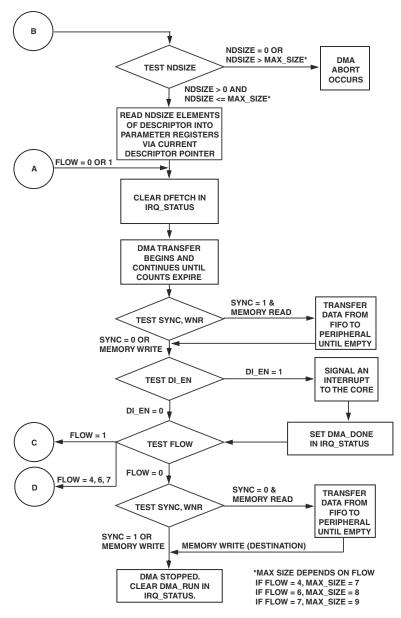

| DMA Operation Flow                   | 5-18 |

| DMA Startup6                         | 5-18 |

| DMA Refresh                          | 5-23 |

| Work Unit Transitions                | 5-25 |

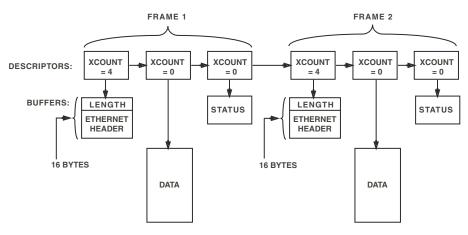

| DMA Transmit and MDMA Source 6       | 5-26 |

| DMA Receive                          | 5-28 |

| Stopping DMA Transfers               | 5-29 |

| DMA Errors (Aborts)                  | 5-30 |

| DMA Control Commands                 | 5-33 |

| Restrictions                         | 5-36 |

| Transmit Restart or Finish           | 5-36 |

| Receive Restart or Finish            | 5-37 |

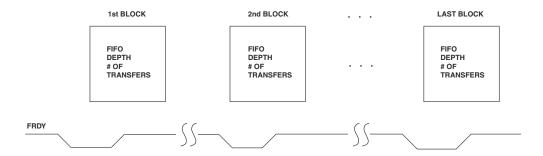

| Handshaked Memory DMA Operation6     | 5-38 |

| Pipelining DMA Requests              | 5-39 |

| HMDMA Interrupts                     | 5-42 |

| DMA Performance                      | 5-43 |

| DMA Throughput                       | 5-44 |

| Memory DMA Timing Details            | 5-47 |

| Static Channel Prioritization        | 5-47 |

| Temporary DMA Urgency 6              | 5-47 |

| Memory DMA Priority and Scheduling 6 | 5-49 |

| Traffic Control                      | 5-51 |

| Programming Model                                                                 | 6-53 |

|-----------------------------------------------------------------------------------|------|

| Synchronization of Software and DMA                                               | 6-53 |

| Single-Buffer DMA Transfers                                                       | 6-55 |

| Continuous Transfers Using Autobuffering                                          | 6-56 |

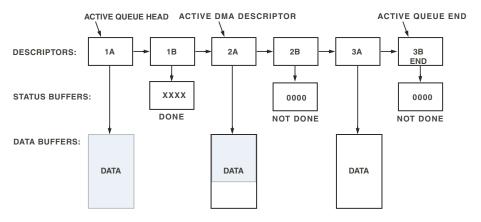

| Descriptor Structures                                                             | 6-58 |

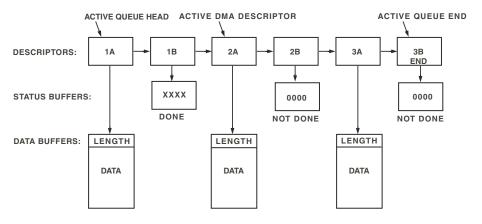

| Descriptor Queue Management                                                       | 6-59 |

| Descriptor Queue Using Interrupts on Every Descriptor                             | 6-60 |

| Descriptor Queue Using Minimal Interrupts                                         | 6-62 |

| Software Triggered Descriptor Fetches                                             | 6-63 |

| DMA Registers                                                                     | 6-66 |

| DMA Channel Registers                                                             | 6-66 |

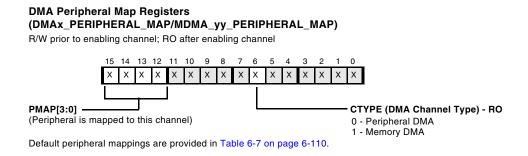

| DMA Peripheral Map Registers (DMAx_PERIPHERAL_MAP/ MDMA_yy_PERIPHERAL_MAP)        | 6-70 |

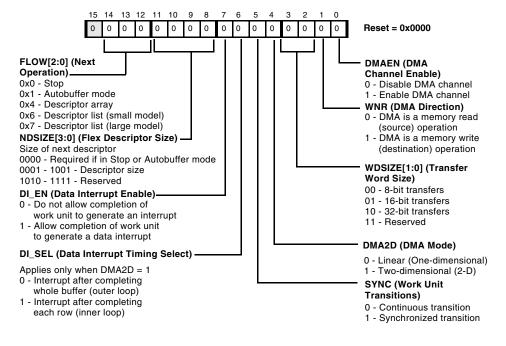

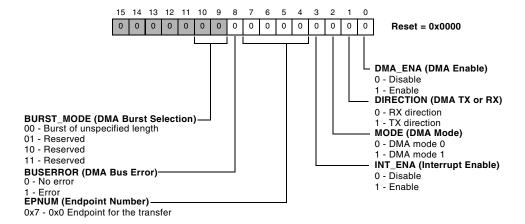

| DMA Configuration Registers (DMAx_CONFIG/MDMA_yy_CONFIG)                          | 6-71 |

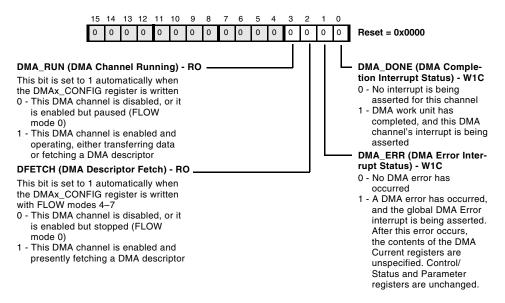

| DMA Interrupt Status Registers (DMAx_IRQ_STATUS/MDMA_yy_IRQ_STATUS)               | 6-75 |

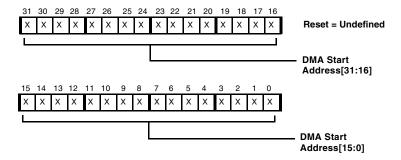

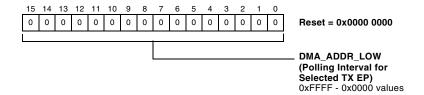

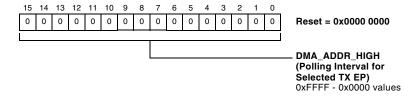

| DMA Start Address Registers (DMAx_START_ADDR/MDMA_yy_START_ADDR) .                | 6-78 |

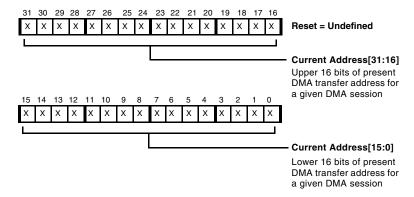

| DMA Current Address Registers (DMAx_CURR_ADDR/MDMA_yy_CURR_ADDR)                  | 6-79 |

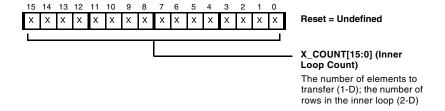

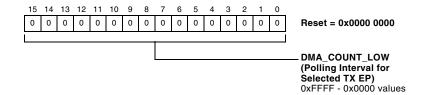

| DMA Inner Loop Count Registers (DMAx_X_COUNT/MDMA_yy_X_COUNT)                     | 6-80 |

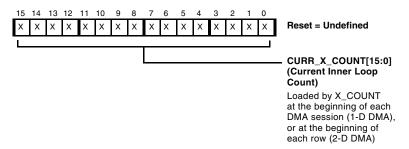

| DMA Current Inner Loop Count Registers (DMAx_CURR_X_COUNT) /MDMA_yy_CURR_X_COUNT) | 6-81 |

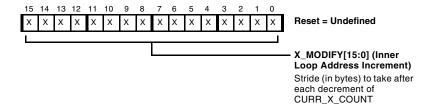

| DMA Inner Loop Address Increment Registers (DMAx_X_MODIFY/MDMA_yy_X_MODIFY) 6-       | -82 |

|--------------------------------------------------------------------------------------|-----|

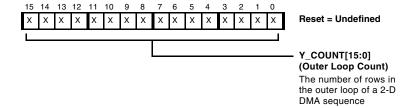

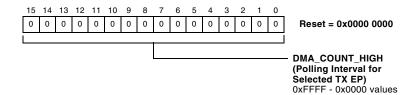

| DMA Outer Loop Count Registers (DMAx_Y_COUNT/MDMA_yy_Y_COUNT) 6-                     | -83 |

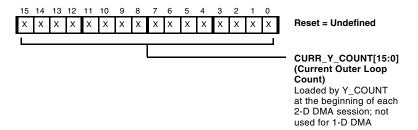

| DMA Current Outer Loop Count Registers (DMAx_CURR_Y_COUNT/ MDMA_yy_CURR_Y_COUNT)     | -84 |

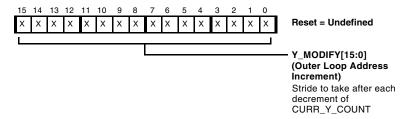

| DMA Outer Loop Address Increment Registers (DMAx_Y_MODIFY/MDMA_yy_Y_MODIFY) 6-       | -85 |

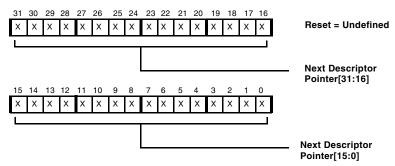

| DMA Next Descriptor Pointer Registers (DMAx_NEXT_DESC_PTR/ MDMA_yy_NEXT_DESC_PTR)    | -86 |

| DMA Current Descriptor Pointer Registers (DMAx_CURR_DESC_PTR/ MDMA_yy_CURR_DESC_PTR) | -87 |

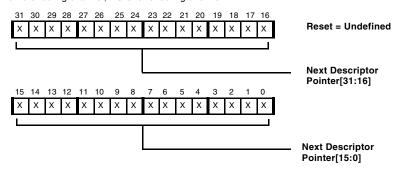

| HMDMA Registers 6-                                                                   | -88 |

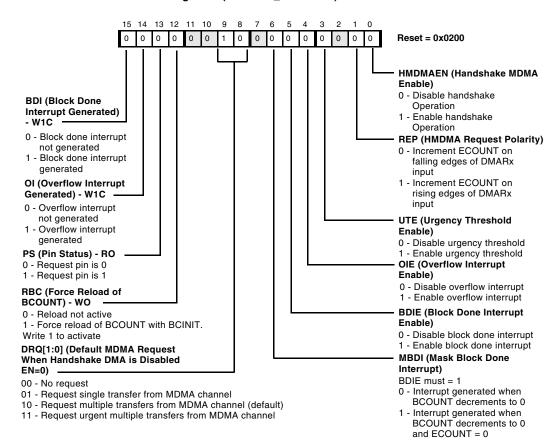

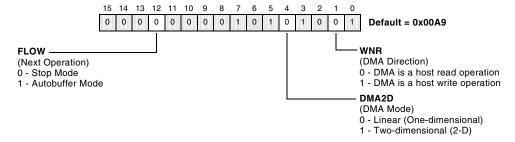

| Handshake MDMA Control Registers (HMDMAx_CONTROL)                                    | -88 |

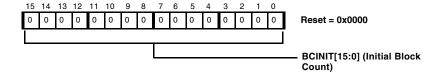

| Handshake MDMA Initial Block Count Registers (HMDMAx_BCINIT)                         | -90 |

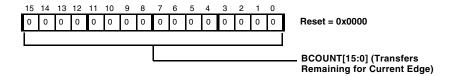

| Handshake MDMA Current Block Count Registers (HMDMAx_BCOUNT) 6-                      | -90 |

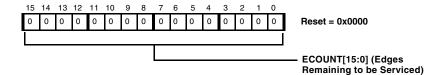

| Handshake MDMA Current Edge Count Registers (HMDMAx_ECOUNT)                          | -91 |

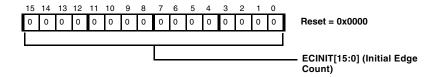

| Handshake MDMA Initial Edge Count Registers (HMDMAx_ECINIT)                          | -92 |

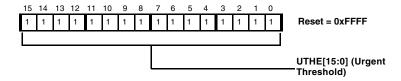

| Handshake MDMA Edge Count Urgent Registers (HMDMAx_ECURGENT) 6-93               |

|---------------------------------------------------------------------------------|

| Handshake MDMA Edge Count Overflow Interrupt Registers (HMDMAx_ECOVERFLOW) 6-93 |

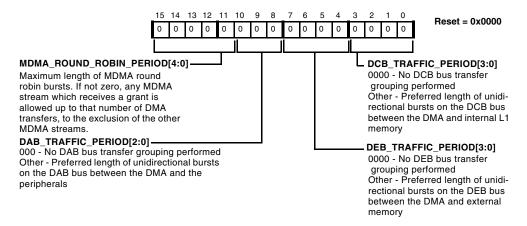

| DMA Traffic Control Registers (DMA_TC_PER and DMA_TC_CNT)                       |

| DMA_TC_PER Register 6-94                                                        |

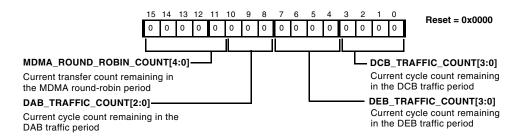

| DMA_TC_CNT Register 6-95                                                        |

| Programming Examples 6-96                                                       |

| Register-Based 2-D Memory DMA 6-97                                              |

| Initializing Descriptors in Memory 6-100                                        |

| Software-Triggered Descriptor Fetch Example 6-103                               |

| Handshaked Memory DMA Example 6-106                                             |

| Unique Behavior for the ADSP-BF52x Processor 6-109                              |

| Static Channel Prioritization 6-110                                             |

| DMA Control Commands 6-111                                                      |

| Handshaked Memory DMA Operation 6-111                                           |

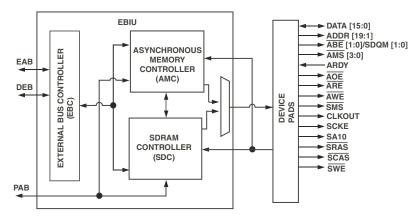

| EXTERNAL BUS INTERFACE UNIT                                                     |

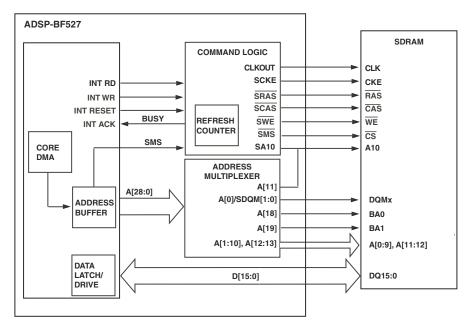

| EBIU Overview                                                                   |

| Block Diagram                                                                   |

| Internal Memory Interfaces                                                      |

| Registers                                                                       |

| Shared Pins                                                                     |

| System Clock                                                                    |

| Error Detection                                                                 |

|                                                                                 |

| AMC Overview and Features                    |

|----------------------------------------------|

| Features                                     |

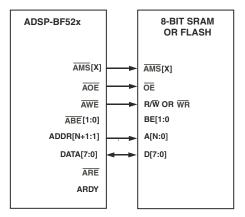

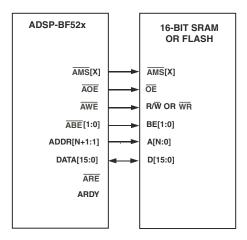

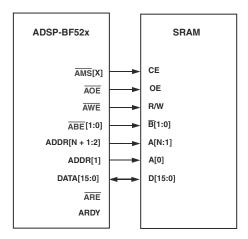

| Asynchronous Memory Interface                |

| Asynchronous Memory Address Decode           |

| AMC Pin Description                          |

| AMC Description of Operation                 |

| Avoiding Bus Contention                      |

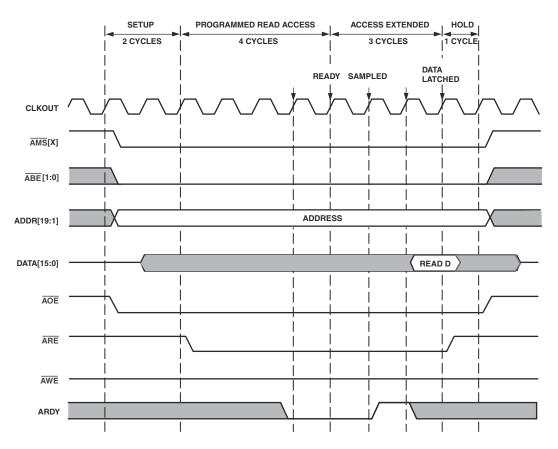

| External Access Extension                    |

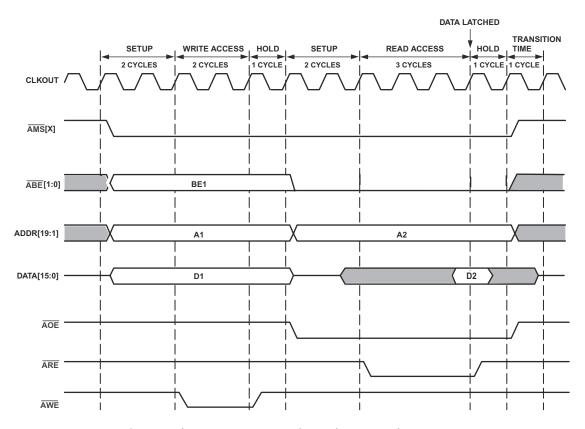

| AMC Functional Description                   |

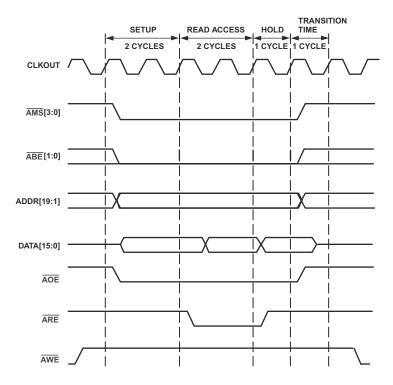

| Programmable Timing Characteristics          |

| Asynchronous Reads                           |

| Asynchronous Writes                          |

| Adding External Access Extension             |

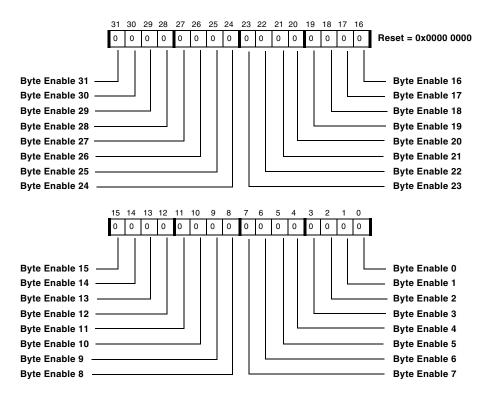

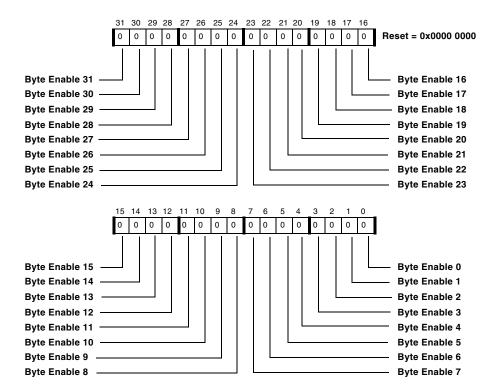

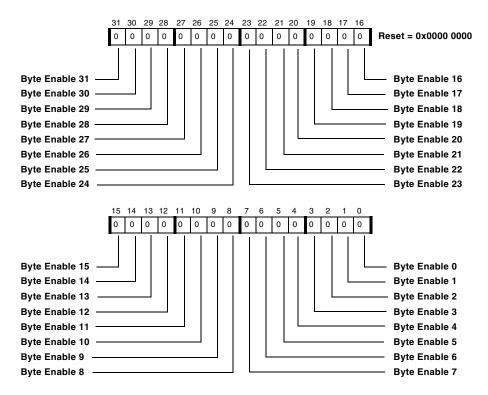

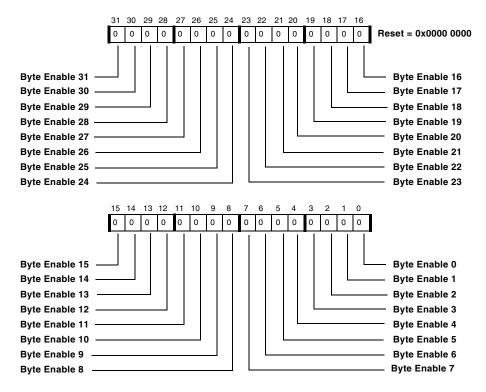

| Byte Enables                                 |

| AMC Programming Model                        |

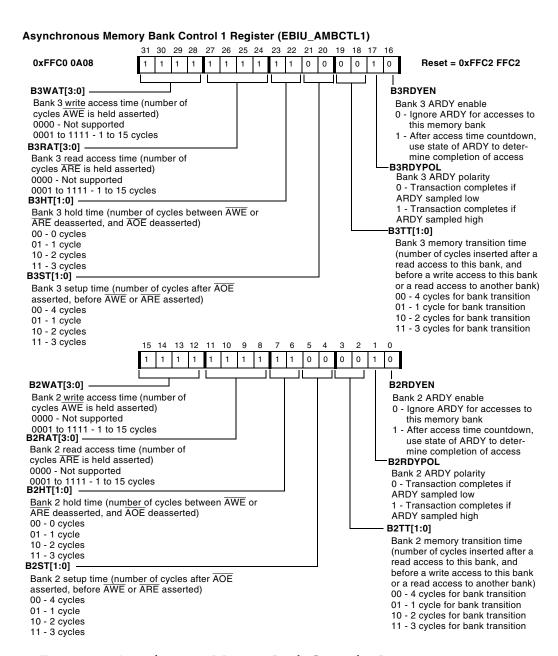

| AMC Registers                                |

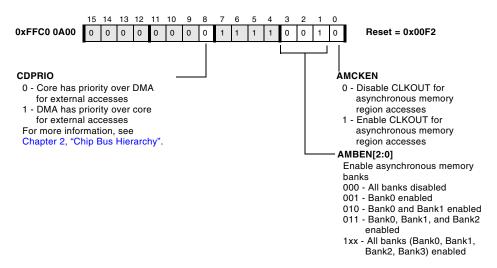

| EBIU_AMGCTL Register                         |

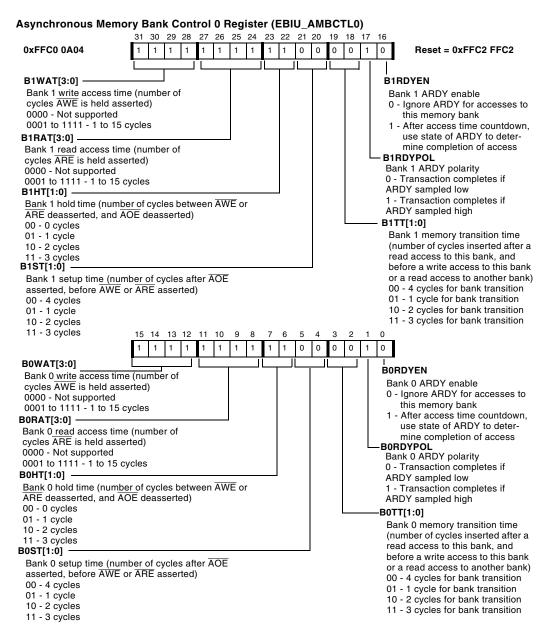

| EBIU_AMBCTL0 and EBIU_AMBCTL1 Registers 7-20 |

| AMC Programming Examples                     |

| SDC Overview and Features                    |

| Features                                     |

| SDRAM Configurations Supported               |

| SDRAM External Bank Size                     |

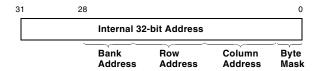

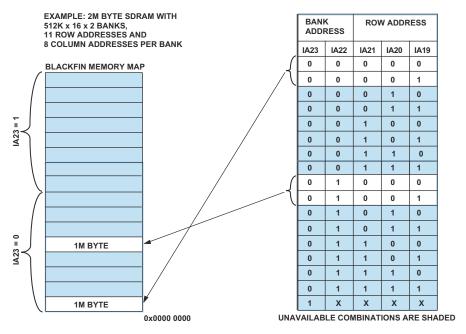

| SDC Address Mapping 7-26                     |

| Internal SDRAM Bank Select                | 7-27 |

|-------------------------------------------|------|

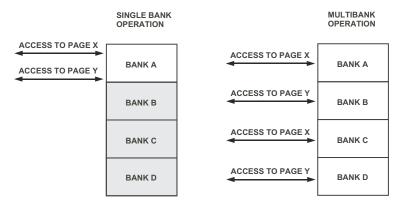

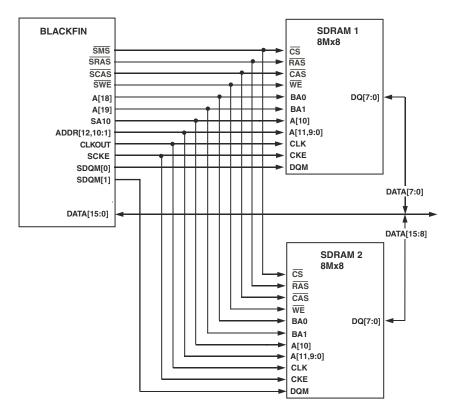

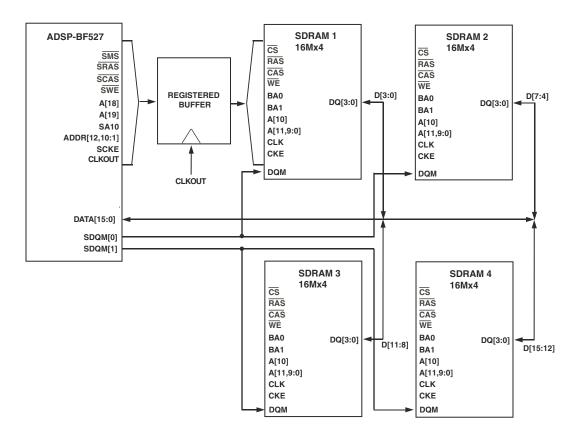

| Parallel Connection of SDRAMs             | 7-28 |

| SDC Interface Overview                    | 7-28 |

| SDC Pin Description                       | 7-29 |

| SDRAM Performance                         | 7-30 |

| SDC Description of Operation              | 7-31 |

| Definition of SDRAM Architecture Terms    | 7-31 |

| Refresh                                   | 7-31 |

| Row Activation                            | 7-31 |

| Column Read/Write                         | 7-31 |

| Row Precharge                             | 7-31 |

| Internal Bank                             | 7-32 |

| External Bank                             | 7-32 |

| Memory Size                               | 7-32 |

| Burst Length                              | 7-32 |

| Burst Type                                | 7-32 |

| CAS Latency                               | 7-33 |

| Data I/O Mask Function                    | 7-33 |

| SDRAM Commands                            | 7-33 |

| Mode Register Set (MRS) command           | 7-33 |

| Extended Mode Register Set (EMRS) command | 7-33 |

| Bank Activate command                     | 7-33 |

| Read/Write command                        | 7-34 |

| Precharge/Precharge All Command           | 7-34 |

| Auto-refresh command                     | 7-34 |

|------------------------------------------|------|

| Enter Self-Refresh Mode                  | 7-34 |

| Exit Self-Refresh Mode                   | 7-34 |

| SDC Timing Specifications                | 7-35 |

| t <sub>MRD</sub>                         | 7-35 |

| t <sub>RAS</sub>                         | 7-35 |

| t <sub>CL</sub>                          | 7-36 |

| t <sub>RCD</sub>                         | 7-36 |

| t <sub>RRD</sub>                         | 7-36 |

| t <sub>WR</sub>                          | 7-36 |

| t <sub>RP</sub>                          | 7-37 |

| t <sub>RC</sub>                          | 7-37 |

| t <sub>RFC</sub>                         | 7-37 |

| t <sub>XSR</sub>                         | 7-37 |

| t <sub>REF</sub>                         | 7-38 |

| t <sub>REFI</sub>                        | 7-38 |

| SDC Functional Description               | 7-39 |

| SDC Operation                            | 7-39 |

| SDC Address Muxing                       | 7-41 |

| Multibank Operation                      | 7-42 |

| Core and DMA Arbitration                 | 7-43 |

| Changing System Clock During Runtime     | 7-44 |

| Changing Power Management During Runtime | 7-45 |

| Deep Sleep Mode                                   | 7-45 |

|---------------------------------------------------|------|

| Hibernate State                                   | 7-45 |

| SDC Commands                                      | 7-46 |

| Mode Register Set Command                         | 7-47 |

| Extended Mode Register Set Command (Mobile SDRAM) | 7-48 |

| Bank Activation Command                           | 7-49 |

| Read/Write Command                                | 7-49 |

| Write Command With Data Mask                      | 7-50 |

| Single Precharge Command                          | 7-51 |

| Precharge All Command                             | 7-51 |

| Auto-Refresh Command                              | 7-51 |

| Self-Refresh Mode                                 | 7-52 |

| Self-Refresh Entry Command                        | 7-52 |

| Self-Refresh Exit Command                         | 7-52 |

| No Operation Command                              | 7-53 |

| SDC SA10 Pin                                      | 7-54 |

| SDC Programming Model                             | 7-54 |

| SDC Configuration                                 | 7-54 |

| Example SDRAM System Block Diagrams               | 7-57 |

| SDC Register Definitions                          | 7-59 |

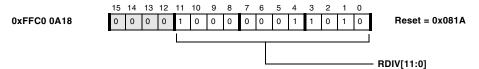

| EBIU_SDRRC Register                               | 7-59 |

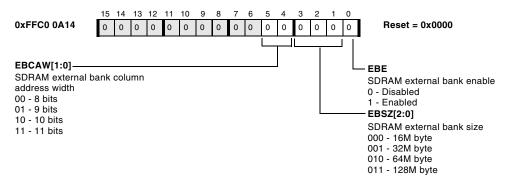

| EBIU_SDBCTL Register                              | 7-61 |

| Using SDRAMs With Systems Smaller than 16M byte   | 7-63 |

|                                                   |      |

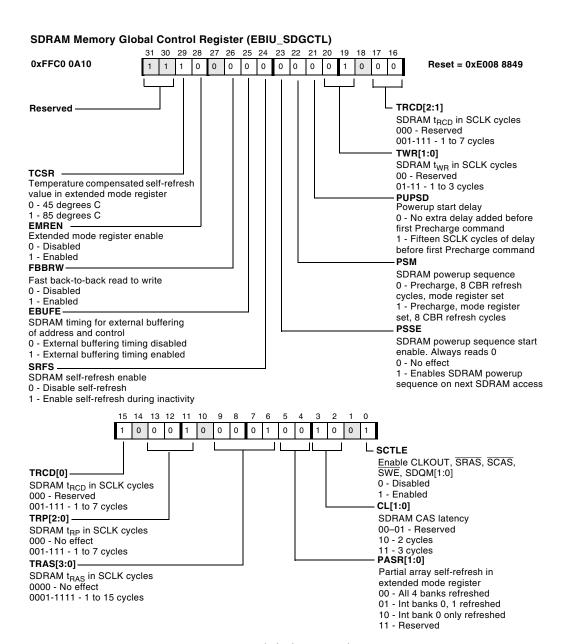

| EBIU_SDGCTL Register                        |

|---------------------------------------------|

| SDRAM clock enable (SCTLE)                  |

| CAS latency (CL)                            |

| Partial array self refresh (PASR)           |

| Bank activate command delay (TRAS)          |

| Bank precharge delay (TRP)                  |

| RAS to CAS delay (TRCD)                     |

| Write to precharge delay (TWR)              |

| Power-Up Start Delay (PUPSD)                |

| Power-Up Sequence Mode (PSM)                |

| Power-Up Sequence Start Enable (PSSE)       |

| Self-Refresh Setting (SRFS)                 |

| Enter Self-Refresh Mode                     |

| Exit Self-Refresh Mode                      |

| External buffering enabled (EBUFE)          |

| Fast Back-to-Back Read to Write (FBBRW)     |

| Extended Mode Register Enabled (EMREN)      |

| Temperature Compensated Self-Refresh (TCSR) |

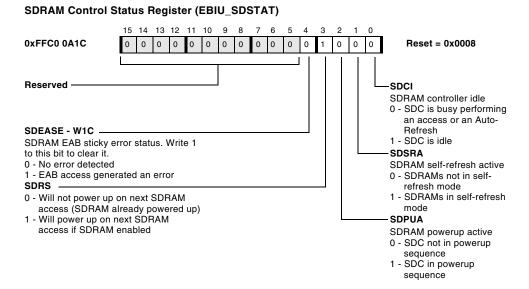

| EBIU_SDSTAT Register                        |

| SDC Programming Examples                    |

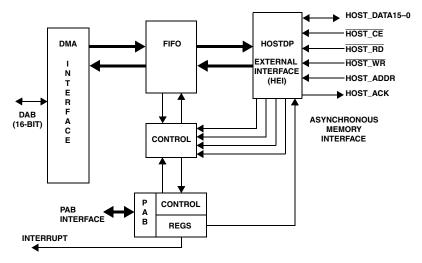

| HOST DMA PORT                               |

| Overview 8-1                                |

| Features 8-2                                |

| Interface Overview                          |

| Description of Operation 8-                               | .3 |

|-----------------------------------------------------------|----|

| Architecture                                              | .4 |

| Functional Description                                    | -5 |

| HOSTDP Configuration 8-                                   | -5 |

| HOSTDP Transactions                                       | -8 |

| Host Read Status 8-                                       | 8  |

| Host Read Data and Host Write Data Operations 8-          | .9 |

| HOSTDP Modes of Operation 8-1                             | 0  |

| Acknowledge Mode 8-1                                      | 1  |

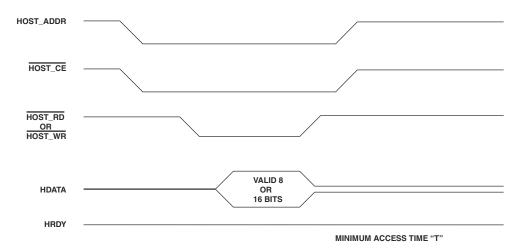

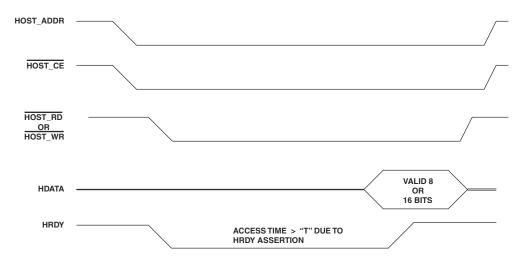

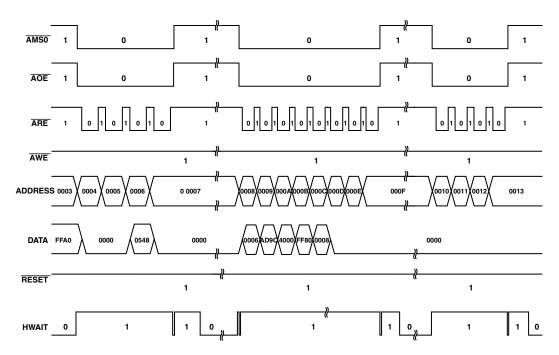

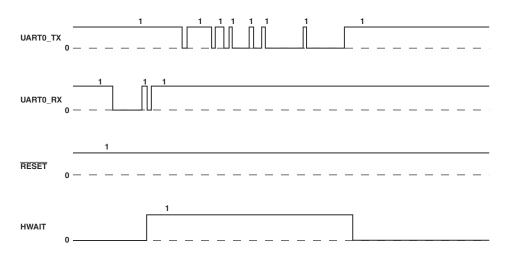

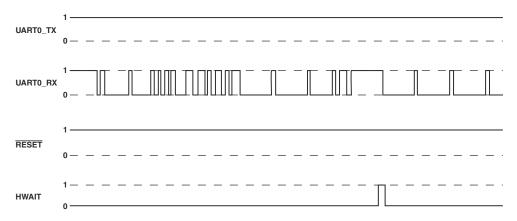

| Acknowledge Mode Timing Diagrams 8-1                      | 1  |

| Host Bus Timeout 8-1                                      | 3  |

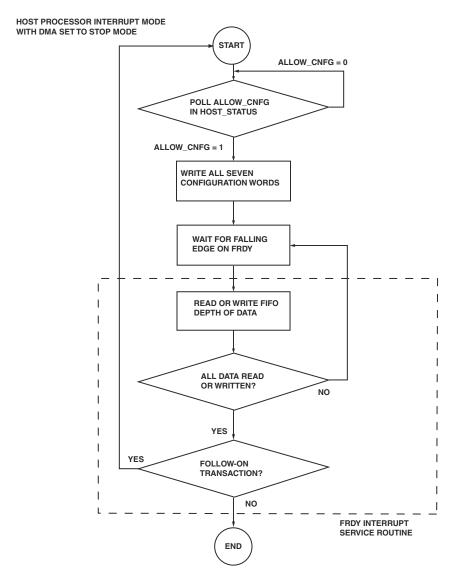

| Interrupt Mode 8-1                                        | 4  |

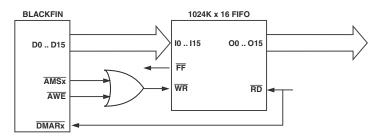

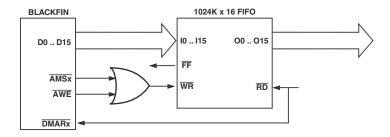

| DMA STOP Mode and AUTOBUFFER Mode 8-1                     | 6  |

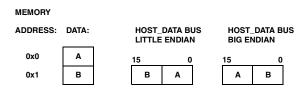

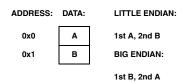

| Bus Widths and Endian Order 8-1                           | 6  |

| Access Control                                            | 7  |

| Improving HOSTDP DMA Bus Bandwidth 8-1                    | 8  |

| Control Commands Between the External Host and HOSTDP 8-2 | 20 |

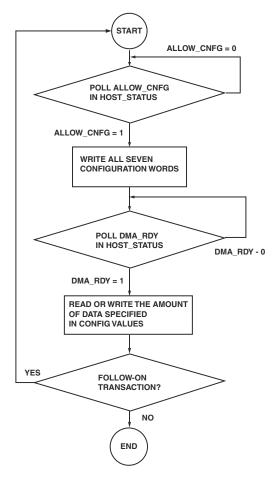

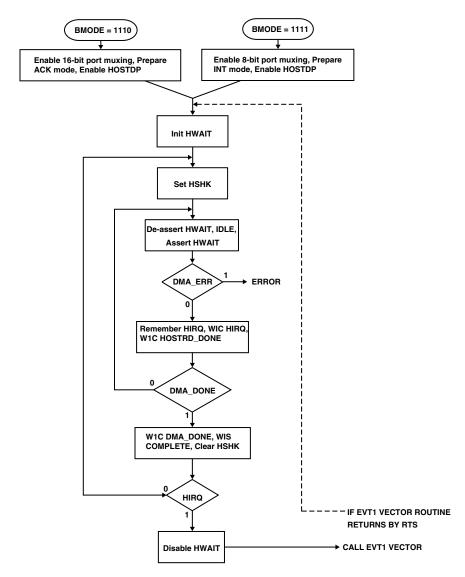

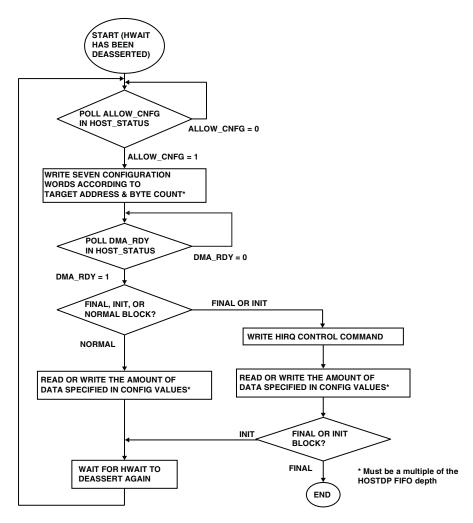

| Programming Model 8-2                                     | 22 |

| Host DMA Port Registers 8-2                               | 6  |

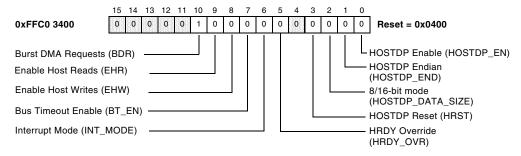

| HOSTDP Control (HOST_CONTROL) Register 8-2                |    |

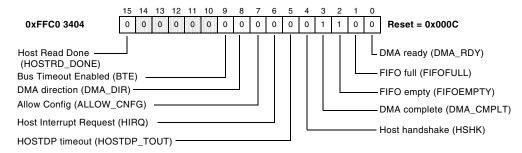

| HOSTDP Status (HOST_STATUS) Register 8-2                  |    |

| HOSTDP Timeout (HOST_TIMEOUT) Register 8-3                | 1  |

| Programming Examples 8-3                                  |    |

## **GENERAL-PURPOSE PORTS**

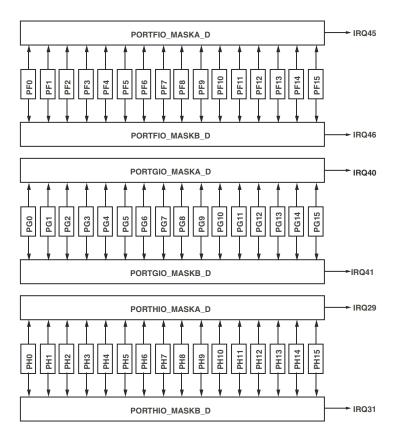

| Overview                                  | 9-1  |

|-------------------------------------------|------|

| Features                                  | 9-2  |

| Interface Overview                        | 9-4  |

| External Interface                        | 9-4  |

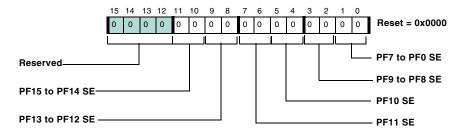

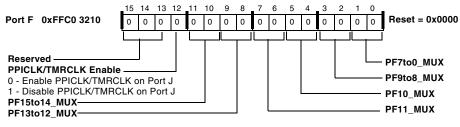

| Port F Structure                          | 9-4  |

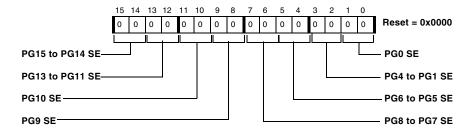

| Port G Structure                          | 9-6  |

| Port H Structure                          | 9-7  |

| Port J Structure                          | 9-9  |

| Input Tap Considerations                  | 9-9  |

| Internal Interfaces                       | 9-10 |

| Internal Signals                          | 9-10 |

| Performance/Throughput                    | )-11 |

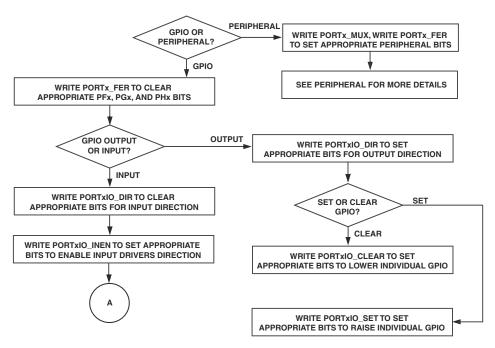

| Description of Operation                  | )-12 |

| Operation                                 | )-12 |

| General-Purpose I/O Modules               | )-13 |

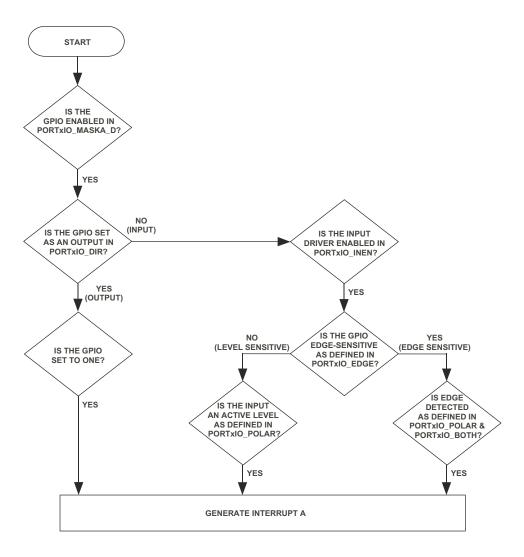

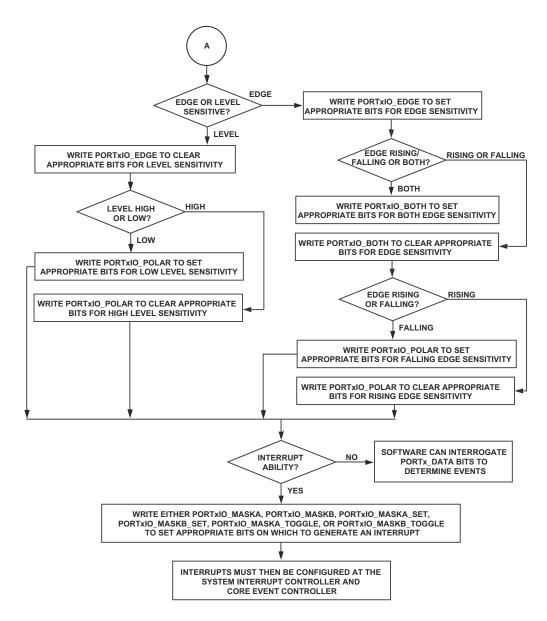

| GPIO Interrupt Processing                 | )-16 |

| Programming Model                         | )-22 |

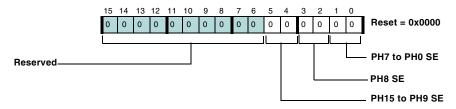

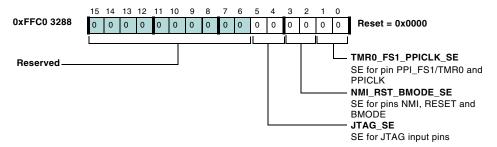

| GPIO Drive Hysteresis Control             | )-24 |

| Portx Control (PORTx_HYSTERESIS) Register | )-24 |

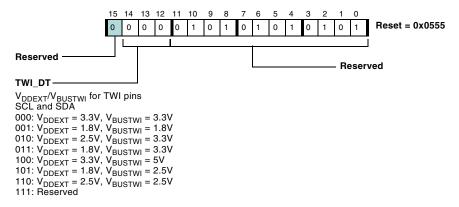

| Hysteresis Control Register               | 9-26 |

| TWI Drive Strength Control Register       | )-27 |

| Memory-Mapped GPIO Registers                                  | 9-27 |

|---------------------------------------------------------------|------|

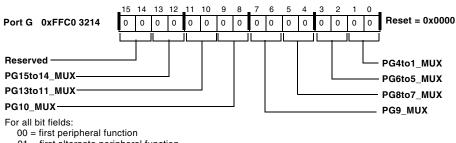

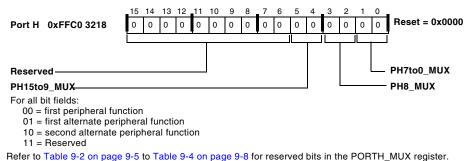

| Port Multiplexer Control Register (PORTx_MUX)                 | 9-28 |

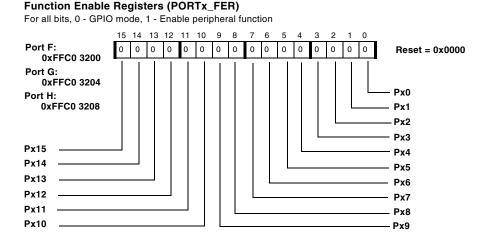

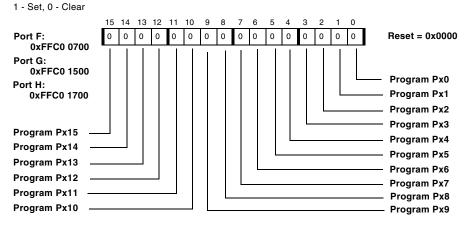

| Function Enable Registers (PORTx_FER)                         | 9-29 |

| GPIO Direction Registers (PORTxIO_DIR)                        | 9-30 |

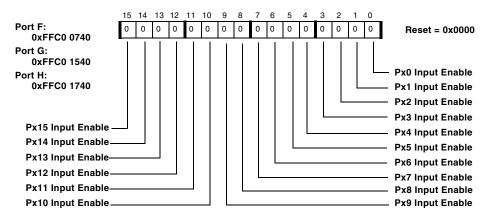

| GPIO Input Enable Registers (PORTxIO_INEN)                    | 9-31 |

| GPIO Data Registers (PORTxIO)                                 | 9-31 |

| GPIO Set Registers (PORTxIO_SET)                              | 9-32 |

| GPIO Clear Registers (PORTxIO_CLEAR)                          | 9-32 |

| GPIO Toggle Registers (PORTxIO_TOGGLE)                        | 9-33 |

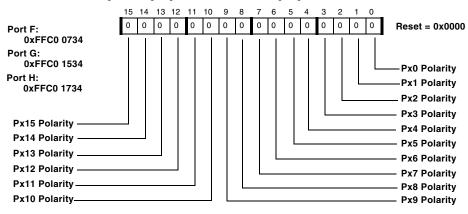

| GPIO Polarity Registers (PORTxIO_POLAR)                       | 9-33 |

| Interrupt Sensitivity Registers (PORTxIO_EDGE)                | 9-34 |

| GPIO Set on Both Edges Registers (PORTxIO_BOTH)               | 9-34 |

| GPIO Mask Interrupt Registers (PORTxIO_MASKA/B)               | 9-35 |

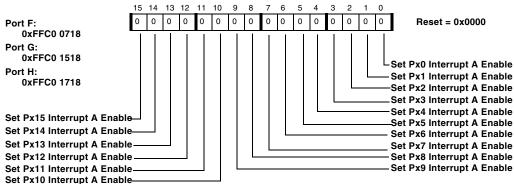

| GPIO Mask Interrupt Set Registers (PORTxIO_MASKA/B_SET)       | 9-36 |

| GPIO Mask Interrupt Clear Registers (PORTxIO_MASKA/B_CLEAR)   | 9-38 |

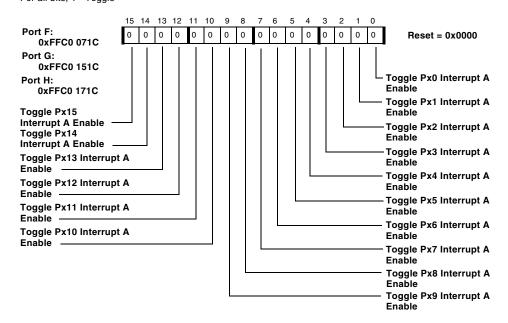

| GPIO Mask Interrupt Toggle Registers (PORTxIO_MASKA/B_TOGGLE) | 9-40 |

| Programming Examples                                          | 9-41 |

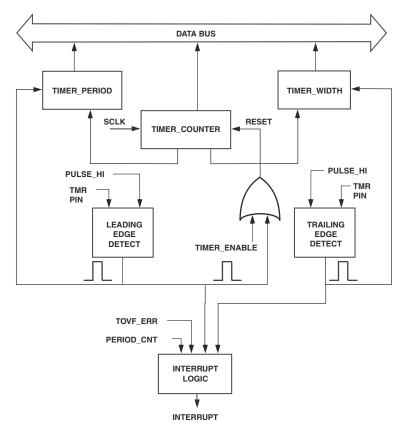

| GENERAL-PURPOSE TIMERS                                        |      |

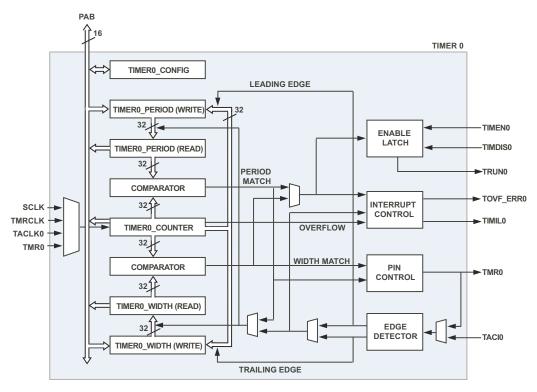

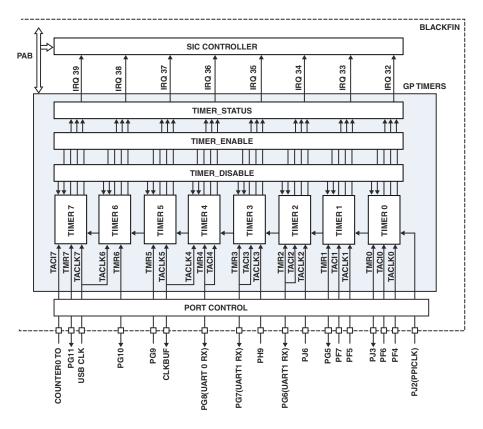

| Specific Information for the ADSP-BF52x                       | 10-1 |

| Overview                                                      | 10-2 |

| External Interface                                            | 10-3 |

| Internal Interface                                            | 10-4 |

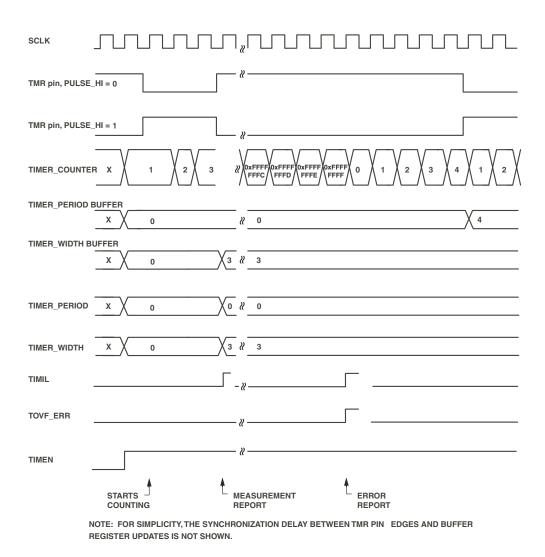

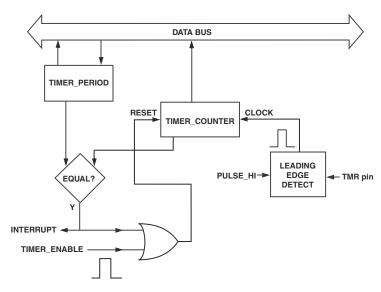

| Description of Operation                            |

|-----------------------------------------------------|

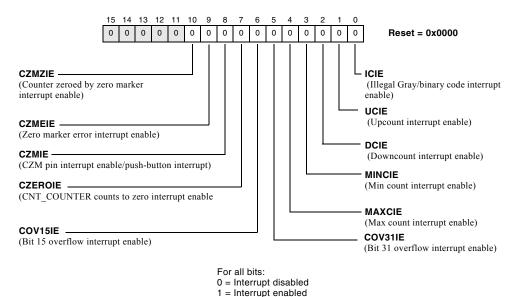

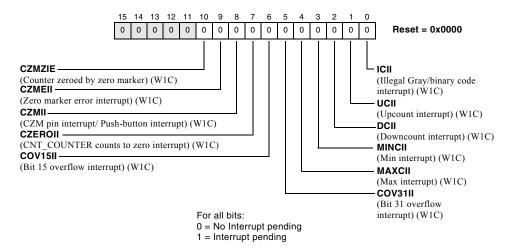

| Interrupt Processing                                |

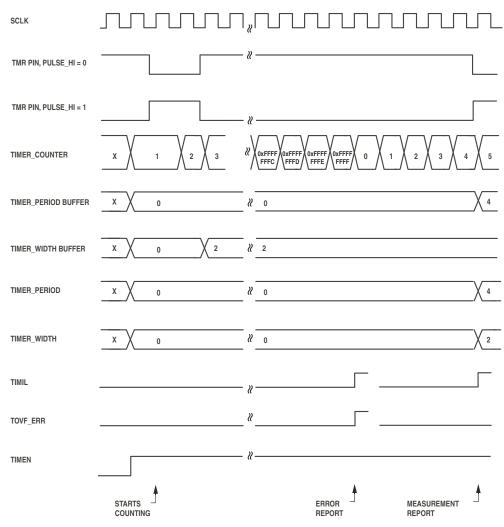

| Illegal States                                      |

| Modes of Operation                                  |

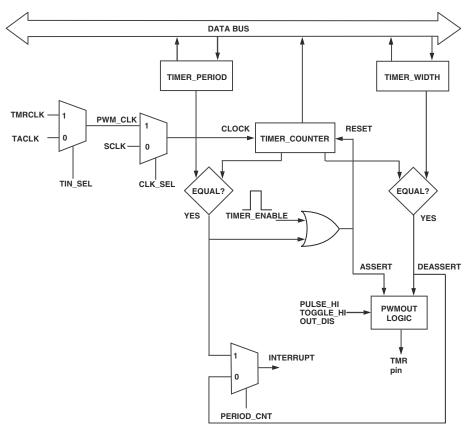

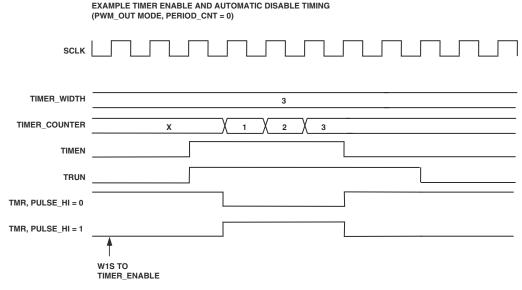

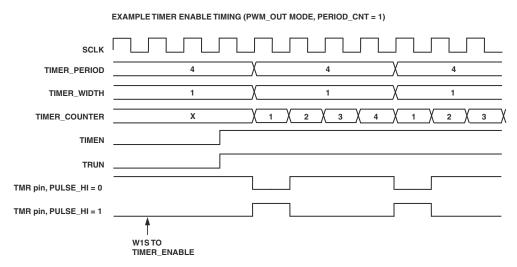

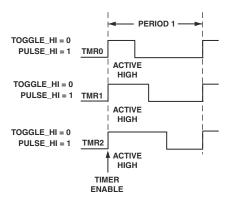

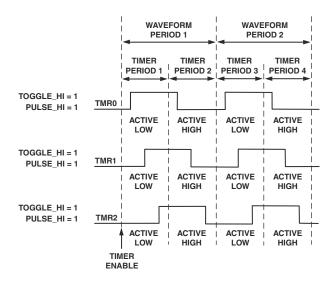

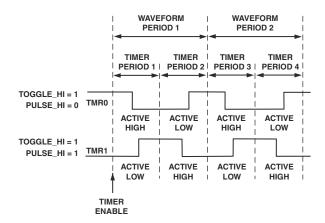

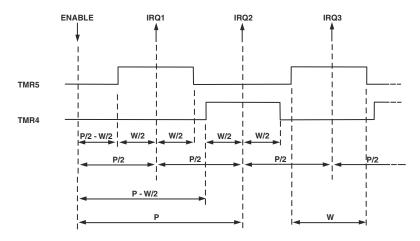

| Pulse Width Modulation (PWM_OUT) Mode 10-10         |

| Output Pad Disable                                  |

| Single Pulse Generation                             |

| Pulse Width Modulation Waveform Generation 10-13    |

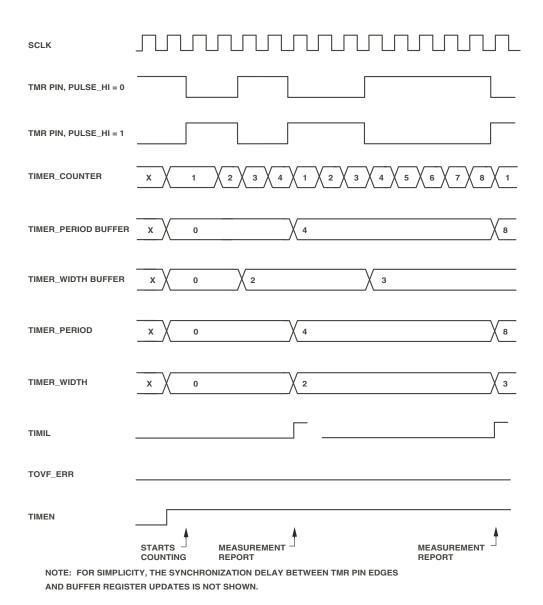

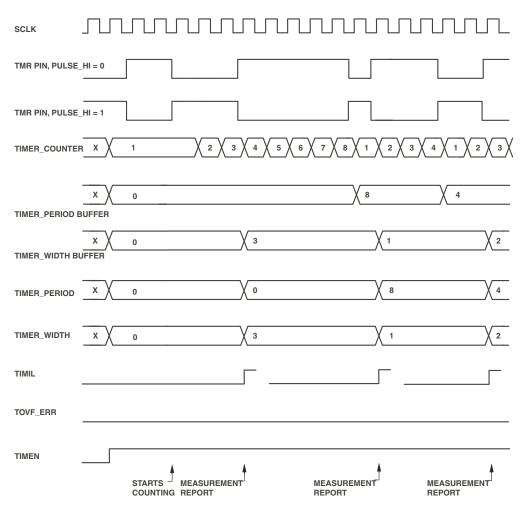

| PULSE_HI Toggle Mode 10-16                          |

| Externally Clocked PWM_OUT 10-21                    |

| Using PWM_OUT Mode With the PPI 10-22               |

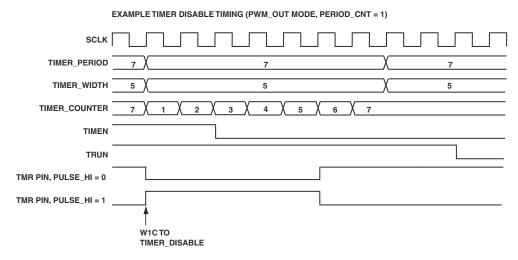

| Stopping the Timer in PWM_OUT Mode 10-22            |

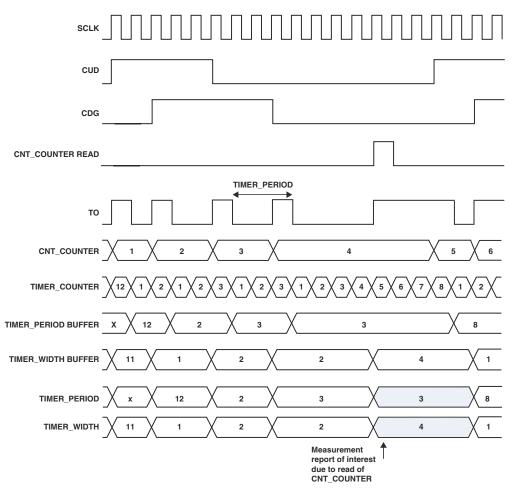

| Pulse Width Count and Capture (WDTH_CAP) Mode 10-24 |

| Autobaud Mode                                       |

| External Event (EXT_CLK) Mode                       |

| Programming Model                                   |

| Timer Registers                                     |

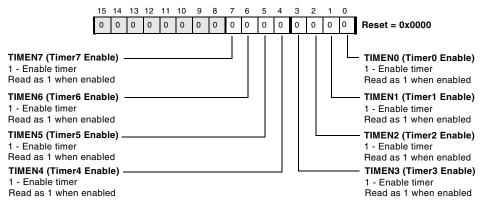

| Timer Enable Register (TIMER_ENABLE) 10-36          |

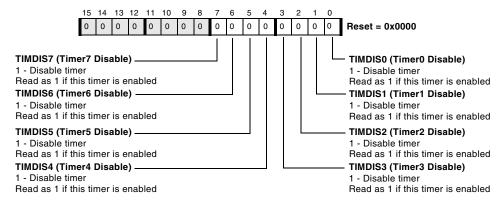

| Timer Disable Register (TIMER_DISABLE) 10-37        |

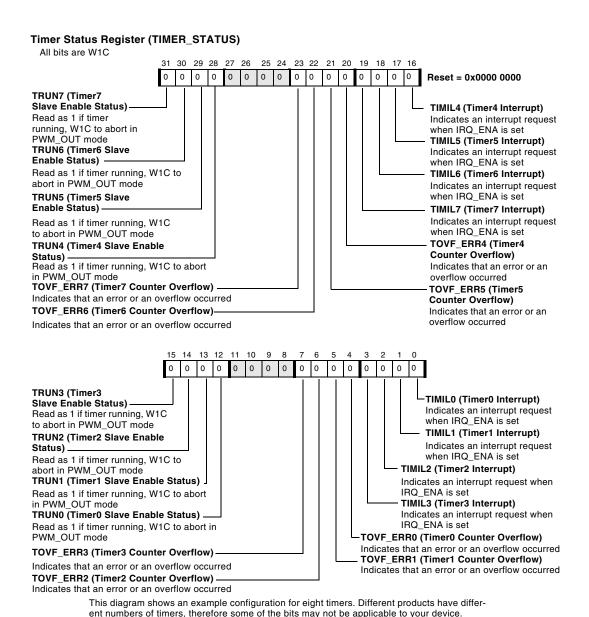

| Timer Status Register (TIMER_STATUS) 10-39          |

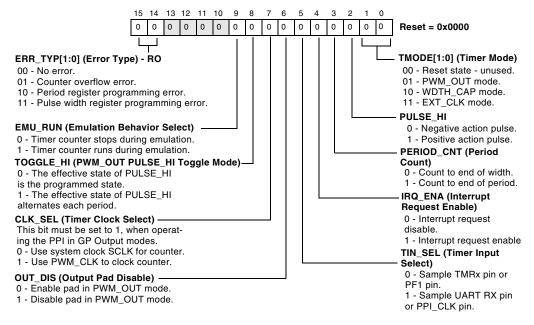

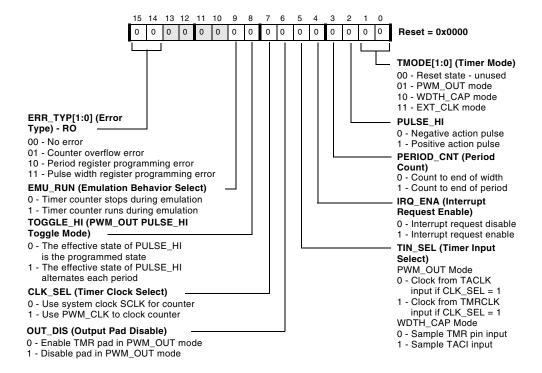

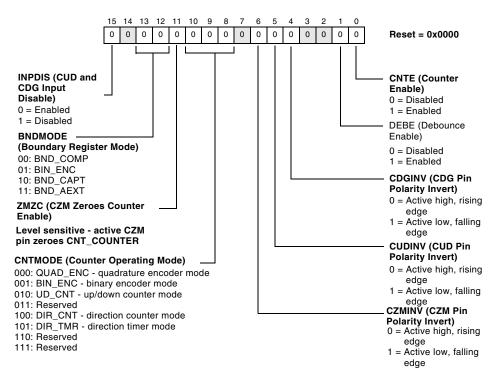

| Timer Configuration Register (TIMER_CONFIG) 10-41   |

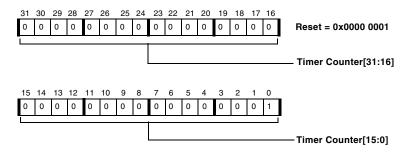

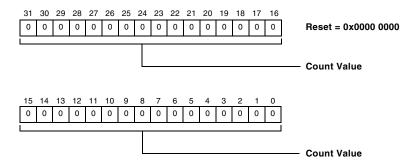

| Timer Counter Register (TIMER_COUNTER) 10-42        |

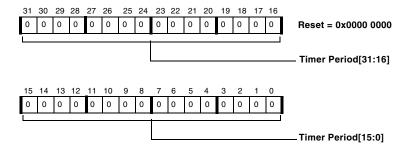

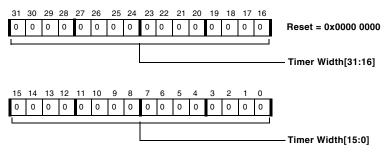

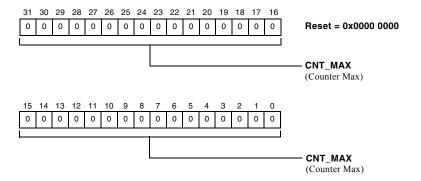

| Timer Period (TIMER_PERIOD) and Timer               |

| Width (TIMER_WIDTH) Registers                       |

| Summary                                             |

| Programming Examples                         | 10-49 |

|----------------------------------------------|-------|

| Unique Behavior for the ADSP-BF52x Processor | 10-58 |

| Interface Overview                           | 10-59 |

| External Interface                           | 10-60 |

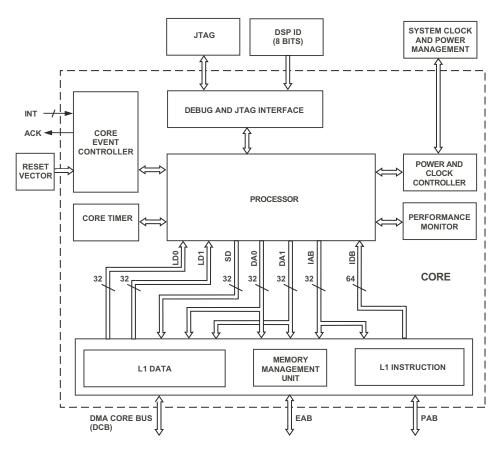

| CORE TIMER                                   |       |

| Specific Information for the ADSP-BF52x      | 11-1  |

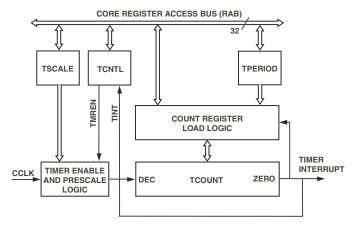

| Overview and Features                        | 11-2  |

| Timer Overview                               | 11-2  |

| External Interfaces                          | 11-3  |

| Internal Interfaces                          | 11-3  |

| Description of Operation                     | 11-3  |

| Interrupt Processing                         | 11-4  |

| Core Timer Registers                         | 11-4  |

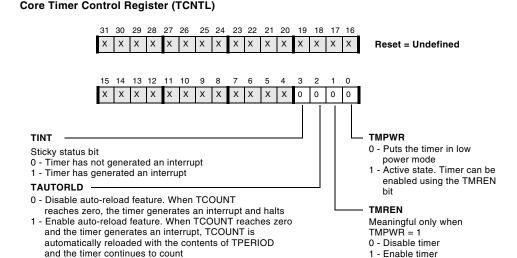

| Core Timer Control Register (TCNTL)          | 11-5  |

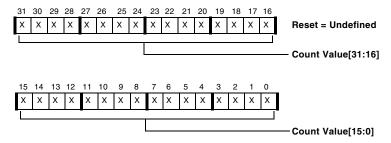

| Core Timer Count Register (TCOUNT)           | 11-5  |

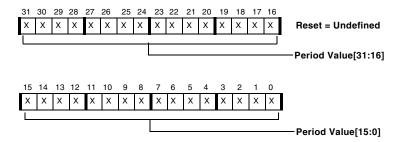

| Core Timer Period Register (TPERIOD)         | 11-6  |

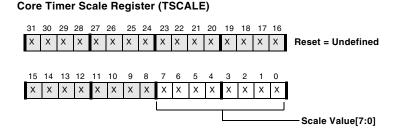

| Core Timer Scale Register (TSCALE)           | 11-7  |

| Programming Examples                         | 11-7  |

| Unique Behavior for the ADSP-BF52x Processor | 11-9  |

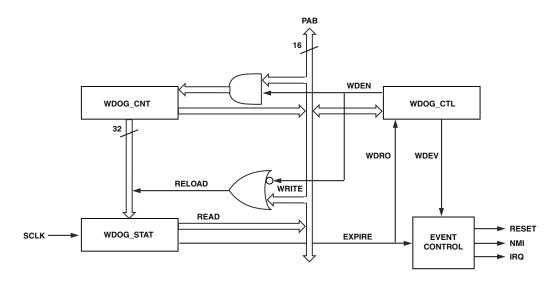

| WATCHDOG TIMER                               |       |

| Specific Information for the ADSP-BF52x      | 12-1  |

| Overview and Features                        | 12-1  |

| Interface Overview                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| External Interface                                                                                                                                       |

| Internal Interface                                                                                                                                       |

| Description of Operation                                                                                                                                 |

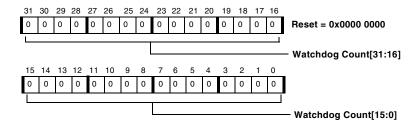

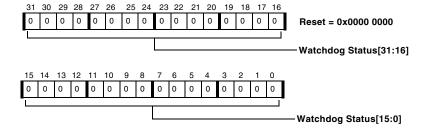

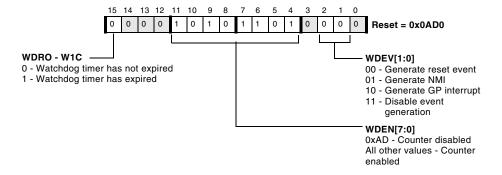

| Register Definitions                                                                                                                                     |