ANALOG Technical notes on using Analog Devices products and development tools Visit our Web resources http://www.analog.com/ee-notes and http://www.analog.com/processors or e-mail processor.support@analog.com or processor.tools.support@analog.com for technical support.

# **ADSP-CM41x Power Supply Transistor Selection Guidelines**

Contributed by Mangino, John

Rev 1 – December 15, 2016

## Introduction

ADSP-CM41x Mixed-Signal Control Processors operate from a single voltage supply (VDD EXT/VDD ANA), generating its own internal voltage supply (VDD INT) using an on-chip voltage regulator and an external pass transistor.

This processor family offers low static power consumption and is produced with a low-power and low-voltage design methodology, delivering world class performance with lower power consumption.

This EE-Note provides the guidelines for selecting an appropriate external transistor for the ADSP-CM41x power supply design. Note, however, that depending on the system resources, a separate voltage regulator may be used, if available.

#### Overview

The on-chip linear voltage regulator supplies 1.21 Volts to the digital section (core) of the chip (VDD INT). Its primary purpose is to support the processor's dynamic current. The regulator's input voltage is the external I/O supply (VDD VREG = 3.3V), which is then used to generate the appropriate core domain supply (VDD INT) of 1.21 Volts.

As mentioned earlier, the user may choose to bypass it at the added expense of an external regulator.

The on-chip voltage regulator provides current to the digital portion of the chip only. It is NOT recommended to connect any other external circuitry to the regulated output voltage of this block.

## **Implementation**

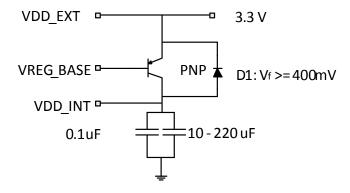

For proper operation, the on-chip voltage regulator requires several external components:

- A PNP bipolar junction transistor this component will act as an external pass device to bring the higher VDD VREG voltage down to the lower VDD INT voltage, thus dissipating power external to the IC package.

- A Schottky Diode with a maximum forward voltage no greater than 400 mV - this should be placed across the collector and emitter of the transistor, with the anode of the diode connected to the collector and the cathode of the diode connected to the emitter. This prevents an invalid voltage differential between VDD VREG and VDD INT, ensuring that VDD VREG-VDD INT  $\geq 400 \text{ mV}$ .

- Decoupling capacitors the capacitor load range is 10 uF - 220 uF. This range may be refined and must have a minimum Equivalent Series Resistance (ESR) of 0.5 Ohm. The ESR is for stability purposes and preventing ringing.

Copyright 2016, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Engineer-to-Engineer Notes.

Therefore, a possible implementation could be as shown in Figure 1:

Figure 1. Voltage Regulator External Circuitry Design

## **External Regulator**

As discussed, using an external 1.21 V source to power VDD\_INT permits bypassing of the internal voltage regulator, thus omitting the need for an external transistor.

When using an external regulator, VDD\_EXT and VREG\_BASE must be tied to ground for zero current consumption.

#### Transistor Selection Criteria

In this section, the main criteria for selecting a proper transistor are discussed:

- 1. High Beta.

- 2. Thermal characteristics.

- 3. Power dissipation.

- 4. Voltage and current requirements.

The maximum current consumption of the ADSP-CM41x VDD\_INT powered by the on-chip voltage

regulator is less than 400 mA<sup>[1]</sup>. Based on this requirement, to minimize the current from the base into the VREG\_BASE pin, a PNP transistor with a minimum Beta of 150 is recommended.

As an example, for a current requirement of 400 mA and a power requirement of 3.3 Volts, the selected transistor must be able to handle a load of: (3.3 V - 1.21 V) \* 400 mA = 840 mW.

Therefore, in this case, Vce = 2.1 V, Ic = 400 mA, and power dissipation = 840 mW.

With the above criteria, the DXTP19020DP5 transistor<sup>[3]</sup>, with the following specifications, is selected:

- Power dissipation of 1.3W

- Thermal Resistance, Junction to Ambient Air

@ 25°C, R<sub>θJA</sub> = 96.1 °C/W

- Max operating temperature 150 °C

Operating with 400 mA at 1.21 V, the maximum operating ambient temperature can be calculated as follows: 150 - (0.84 \* 96.1) = 69 °C

Furthermore, the DXTP19020DP5 transistor can also operate at higher ambient temperatures by adding copper to the pad area, as described in the device datasheet.

From Figure 2, Thermal Resistance, Junction to Ambient Air @ 25°C,  $R_{\theta JA} = 41.7$  C/W. Thus: 150 - (0.84 \* 41.7) = 115 °C.

#### **Diode Selection Criteria**

In this section, the main criteria for selecting a proper diode are discussed:

- 1. Forward Voltage  $\geq 400 \text{mV}$ .

- 2. Maximum average forward current  $\geq 3A$ .

### Maximum Ratings @TA = 25°C unless otherwise specified

| Characteristic                               | Symbol           | Value | Unit |

|----------------------------------------------|------------------|-------|------|

| Collector-Base Voltage                       | VcBo             | -25   | V    |

| Collector-Emitter Voltage                    | VCEO             | -20   | V    |

| Emitter-Collector Voltage (Reverse Blocking) | VECO             | -4    | V    |

| Emitter-Base Voltage                         | V <sub>EBO</sub> | -7    | V    |

| Continuous Collector Current                 | Ic               | -8    | А    |

| Base Current                                 | IB               | -1    | А    |

| Peak Pulse Current                           | I <sub>CM</sub>  | -15   | Α    |

#### **Thermal Characteristics**

| Characteristic                                                              | Symbol                            | Value       | Unit |

|-----------------------------------------------------------------------------|-----------------------------------|-------------|------|

| Power Dissipation @ T <sub>A</sub> = 25°C (Note 4)                          | PD                                | 1.3         | W    |

| Thermal Resistance, Junction to Ambient Air (Note 4) @TA = 25°C             | $R_{\theta JA}$                   | 96.1        | °C/W |

| Power Dissipation @ T <sub>A</sub> = 25°C (Note 5)                          | $P_{D}$                           | 3           | W    |

| Thermal Resistance, Junction to Ambient Air (Note 5) @T <sub>A</sub> = 25°C | $R_{\theta JA}$                   | 41.7        | °C/W |

| Operating and Storage Temperature Range                                     | T <sub>J</sub> , T <sub>STG</sub> | -55 to +150 | °C   |

Notes:

4. Device mounted on FR-4 PCB, 2 oz. copper, minimum recommended pad layout.

5. Device mounted on FR-4 PCB, 2 oz. copper, collector pad dimensions 0.42inch².

Figure 2. DXTP19020DP5 High Gain PowerDI®5 Transistor Specifications

### References

- [1] ADSP-CM411F/412F/413F/416F/417F/418F/419F Mixed-Signal Dual-Core Processor with ARM Cortex-M4/M0 and 16-bit ADCs Datasheet. Rev PrB, February 2016. Analog Devices, Inc.

- [2] ADSP-CM41x Mixed-Signal Control Processor Hardware Reference. Rev 0.1, Analog Devices, Inc.

- [3] DXTP19020DP5 High Gain PowerDI®5 Transistor Data Sheet. Rev 3-2, March 2010. Diodes, Inc.

- [4] VS-30BQ015PbF Schottky Rectifier, 3.0 A, Data Sheet. Rev 02-Oct-12, Oct 2012. Vishay Semiconductors.

## **Document History**

| Revision                                     | Description      |

|----------------------------------------------|------------------|

| Rev 1 – December 15th, 2016<br>by J. Mangino | Initial release. |