# Automotive Qualified, Dual-Channel, Precision ADCs with LIN2.2 Slave Interface

Data Sheet ADuCM300

#### **FEATURES**

Two precision 20-bit  $\Sigma$ - $\Delta$  ADCs Programmable ADC conversion rates from 4 Hz to 8000 Hz On-chip precision voltage reference Primary ADC

Differential voltage inputs to a 20-bit Σ-Δ ADC Programmable gain (from 4 to 512)

Digital comparator with accumulator

ADC absolute input voltage range: –200 mV to +300 mV

Auxiliary ADC

Flexible input mux for input channel selection

Single-ended voltage input (can be interfaced to an

external temperature sensor), internal temperature

sensor input, or diagnostic supply input

#### Microcontroller

Arm Cortex-M3 32-bit processor 16.384 MHz precision oscillator with 1% accuracy Serial wire download (SWD) port supporting code download and debug

Automotive qualified integrated LIN transceiver LIN 2.2-compatible slave SAE J-2602-compatible slave Low electromagnetic emissions (EME) High electromagnetic immunity (EMI)

#### Memory

128 kB Flash/EE memory, ECC 6 kB SRAM, ECC

4 kB data Flash/EE memory, ECC 10,000 cycle Flash/EE endurance

20-year Flash/EE data retention

In circuit download via SWD and LIN

On-chip peripherals: SPI, GPIO port, general-purpose timer,

wake-up timer, watchdog timer, and on-chip POR

#### **Power**

Operates directly from an external voltage supply, varying from 3.6 V to 18 V

Power consumption, 8 mA typical (16 MHz) at  $T_A = -40^{\circ}$ C to  $+115^{\circ}$ C

Low power monitor mode

Package and temperature range

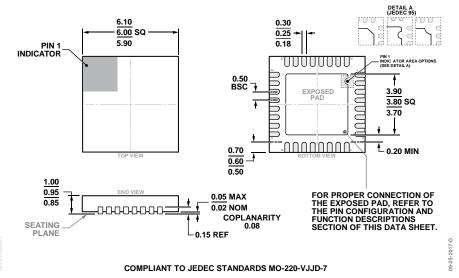

6 mm × 6 mm, 32-lead LFCSP

Fully specified for -40°C to +115°C operation, additional specifications are available for +115°C to +125°C operation

**AEC-Q100 qualified for automotive applications**

#### **APPLICATIONS**

LIN sensor interface for automotive applications General powertrain, body and chassis sensing Current and voltage sensing for industrial applications

# **TABLE OF CONTENTS**

| Features                                     | 1 |

|----------------------------------------------|---|

| Applications                                 |   |

| Revision History                             |   |

| Functional Block Diagram                     |   |

| General Description                          |   |

| Specifications                               | 5 |

| Absolute Maximum Ratings1                    | 1 |

| ESD Caution1                                 | 1 |

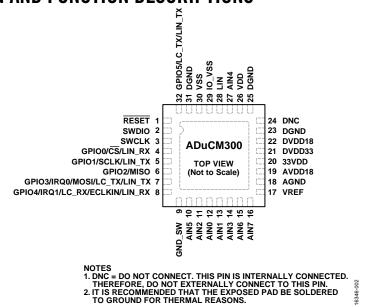

| Pin Configuration and Function Descriptions1 | 2 |

| Terminology1                                 | 4 |

| Applications Information                  | . 15 |

|-------------------------------------------|------|

| Design Guidelines                         | . 15 |

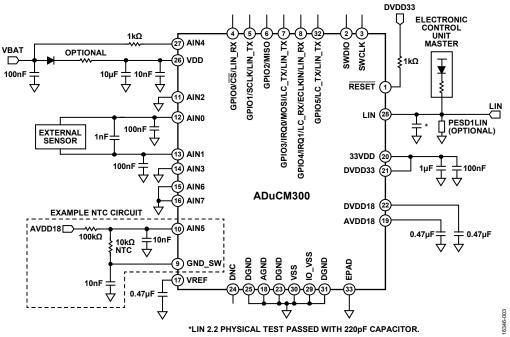

| Power and Ground Recommendations          | . 15 |

| Exposed Pad Thermal Recommendations       | . 15 |

| General Recommendations                   | . 15 |

| Recommended External Components Schematic | . 15 |

| Outline Dimensions                        | . 16 |

| Ordering Guide                            | . 16 |

| Automotive Products                       | . 16 |

## **REVISION HISTORY**

6/2019—Revision 0: Initial Version

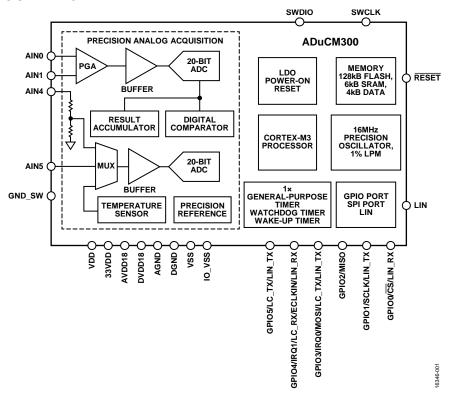

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **GENERAL DESCRIPTION**

The ADuCM300 is a fully integrated, 8 kSPS (8000 Hz conversion rate) data acquisition system that incorporates dual, high performance,  $\Sigma$ - $\Delta$  analog-to-digital converters (ADCs), a 32-bit Arm\* Cortex\*-M3 processor, and microcontroller unit (MCU) subsystem. The ADuCM300 has a 128 kB program Flash/EE, 4 kB data Flash/EE, and 6 kB static random access memory (SRAM).

The ADuCM300 is a complete system solution for external precision sensor voltage measurements in automotive applications. Minimizing external system components, the device can be powered directly from an external voltage supply that varies from 3.6 V to 18 V. On-chip, low dropout (LDO) regulators generate the supply voltages for the integrated digital and analog subsystems.

The analog subsystem consists of two 20-bit  $\Sigma$ - $\Delta$  ADCs: a primary ADC and an auxiliary ADC. The primary ADC accepts a differential input and is ideally suited to interface external sensors with low level signal amplitude outputs integrating a low noise, programmable gain amplifier (PGA), and precision, low drift reference. The auxiliary ADC is connected to a flexible input multiplexer and can measure external single-ended sensor input voltages (AIN5/GND\_SW), the internal (on-chip) temperature sensor, or monitor the supply voltage connected to AIN4 (see Figure 1).

The ADuCM300 operates from an on-chip, 16.384 MHz, high frequency oscillator that supplies the system clock. This clock is routed through a programmable clock divider from which the core clock operating frequency is generated. The device also contains a 32 kHz oscillator for low power operation.

The ADuCM300 integrates a range of on-chip peripherals that can be configured under core software control as required in the application. These peripherals include a serial peripheral interface (SPI) input/output communication controller, six general-purpose input/output (GPIO) pins, one general-purpose timer, a wake-up timer (WUT), and a watchdog timer (WDT).

The ADuCM300 operates in battery-powered applications where low power operation is critical. The microcontroller core can be configured in normal operating mode, resulting in an overall system current consumption of <18.5 mA when all peripherals are active. The device can also be configured in a number of low power operating modes under direct program control, consuming <100  $\mu A$ . The ADuCM300 includes a local interconnect network (LIN) physical interface for single wire, high voltage communications in automotive environments.

The device operates from an external 3.6 V to 18 V (on VDD, Pin 26) voltage supply and is specified over the  $-40^{\circ}$ C to  $+115^{\circ}$ C temperature range, with additional specifications available for the  $+115^{\circ}$ C to  $+125^{\circ}$ C temperature range.

For more information and register details, see the ADuCM300 Hardware Reference Manual.

# **SPECIFICATIONS**

Specifications are valid for VDD = 3.6 V to 18 V, Arm core frequency ( $f_{CORE}$ ) = 16.384 MHz, clock divider bits = 0, and voltage reference ( $V_{REF}$ ) = 1.2 V (internal), unless otherwise stated. The device is fully specified for the temperature range of  $T_A$  = -40°C to +115°C. Parameters specified in the 115°C to 125°C temperature range of operation are functional within this range, but with degraded performance. Typical values noted reflect the approximate parameter mean at  $T_A$  = 25°C under nominal conditions, unless otherwise stated.

Table 1.

|                                                 |                                                                                                                  | <b>T</b> <sub>A</sub> = | $T_A = 115^{\circ}C \text{ to } 125^{\circ}C^1$ |       |     | <del>.</del> |     |                                  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------|-------|-----|--------------|-----|----------------------------------|

| Parameter                                       | Test Conditions/Comments                                                                                         | Min                     | Тур                                             | Max   | Min | Тур          | Max | Unit                             |

| ADC SPECIFICATIONS                              |                                                                                                                  |                         |                                                 |       |     |              |     |                                  |

| Conversion Rate <sup>1</sup>                    | ADC normal operating mode                                                                                        | 4                       |                                                 | 8000  |     |              |     | Hz                               |

|                                                 | ADC low power mode, chop on                                                                                      | 1                       |                                                 | 656   |     |              |     | Hz                               |

| Primary ADC<br>(AIN0/AIN1 Only)                 |                                                                                                                  |                         |                                                 |       |     |              |     |                                  |

| No Missing Codes <sup>1</sup>                   | Valid for all ADC update rates and ADC modes                                                                     | 20                      |                                                 |       |     |              |     | Bits                             |

| Total Gain Error <sup>1,2,3,4</sup>             | Factory calibrated at a gain of 8, normal mode                                                                   | -0.5                    | ±0.1                                            | +0.5  |     | ±0.15        |     | %                                |

|                                                 | Low power mode                                                                                                   | -1                      | ±0.2                                            | ±1    |     |              |     | %                                |

| Integral Nonlinearity<br>(INL) <sup>1,5,6</sup> | ADCFLT = 0x10001, 0x08101, 0x00007                                                                               | -200                    | ±10                                             | +200  |     | ±80          |     | ppm of full-scale<br>range (FSR) |

| Offset Error <sup>1,3,4</sup>                   | Chop off, gain = 4, 8, or 16, external short, after user system calibration at 25°C, 1 LSB = 2.28 $\mu$ V ÷ gain | -100                    | ±24                                             | +100  |     |              |     | LSBs                             |

|                                                 | Chop off, gain = 32 or 64, external short, after user system calibration at 25°C, 1 LSB = $2.28 \mu V \div gain$ | -160                    | ±48                                             | +160  |     |              |     | LSBs                             |

|                                                 | Chop off, gain = 512, external short, after user system calibration at 25°C, 1 LSB = 2.28 µV ÷ gain              | -1400                   | ±60                                             | +1400 |     |              |     | LSBs                             |

|                                                 | Chop on, external short, low power mode, gain = 64 or 512, processor powered down                                | -300                    | ±50                                             | +250  |     | ±250         |     | nV                               |

|                                                 | Chop on, external short, after user system calibration at 25°C, VDD = 18 V                                       | -1.5                    |                                                 | +1.5  |     |              |     | μV                               |

| Offset Error Drift <sup>1, 5, 7</sup>           | Chop off, gains of 4 to 64, normal mode                                                                          |                         | ±0.48                                           |       |     |              |     | LSB/°C                           |

|                                                 | Chop on                                                                                                          |                         | ±5                                              |       |     | ±5           |     | nV/°C                            |

| Gain Drift <sup>1,8</sup>                       |                                                                                                                  |                         | ±3                                              |       |     | ±3           |     | ppm/°C                           |

| PGA Gain Mismatch<br>Error                      |                                                                                                                  |                         | ±0.1                                            |       |     | ±0.1         |     | %                                |

| Output Noise <sup>1</sup>                       | Register ADC0CON, PGASCALE bits<br>(Bits[11:10]) = 0x3                                                           |                         |                                                 |       |     |              |     |                                  |

|                                                 | Gain = 64, ADCFLT = 0x08101                                                                                      |                         | 0.80                                            |       |     | 1.2          |     | μV rms                           |

|                                                 | Gain = 64, ADCFLT = 0x00007                                                                                      |                         | 0.75                                            |       |     |              |     | μV rms                           |

|                                                 | Gain = 32, ADCFLT = 0x08101                                                                                      |                         | 1.00                                            |       |     | 1.3          |     | μV rms                           |

|                                                 | Gain = 32, ADCFLT = 0x00007                                                                                      |                         | 0.80                                            |       |     |              |     | μV rms                           |

|                                                 | Gain = 16, ADCFLT = 0x08101                                                                                      |                         | 1.50                                            |       |     | 2.0          |     | μV rms                           |

|                                                 | Gain = 16, ADCFLT = 0x00007                                                                                      |                         | 1.10                                            |       |     |              |     | μV rms                           |

|                                                 | Gain = 8, ADCFLT = 0x08101                                                                                       |                         | 2.10                                            |       |     | 2.5          |     | μV rms                           |

|                                                 | Gain = 8, ADCFLT = 0x00007                                                                                       |                         | 1.60                                            |       |     |              |     | μV rms                           |

|                                                 | Gain = 4, ADCFLT = 0x08101                                                                                       |                         | 3.40                                            |       |     | 4.0          |     | μV rms                           |

|                                                 | Gain = 4, ADCFLT = 0x00007                                                                                       |                         | 2.60                                            |       |     |              |     | μV rms                           |

|                                                 | Gain = 64, ADCFLT = 0x10001                                                                                      |                         | 1.60                                            |       |     | 1.85         |     | μV rms                           |

|                                                 | Gain = 32, ADCFLT = 0x10001                                                                                      |                         | 1.70                                            |       |     | 2.0          |     | μV rms                           |

|                                                 | Gain = 16, ADCFLT = 0x10001                                                                                      |                         | 2.00                                            |       |     | 2.1          |     | μV rms                           |

|                                                 | Gain = 8, ADCFLT = 0x10001                                                                                       |                         | 2.40                                            |       |     | 3.0          |     | μV rms                           |

|                                                 | Gain = 4, ADCFLT = 0x10001                                                                                       |                         | 4.35                                            |       |     | 5.0          |     | μV rms                           |

|                                                 | ADC low power mode, 221 Hz update rate, chop enabled, gain = 64                                                  |                         | 0.6                                             |       |     | 0.8          |     | μV rms                           |

|                                             | $T_A = -40^{\circ}C \text{ to } +115^{\circ}C$                                                                                                 |       |              | 115°C | T <sub>A</sub> = 115°C to 125°C¹ |       |     |            |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|----------------------------------|-------|-----|------------|

| Parameter                                   | Test Conditions/Comments                                                                                                                       | Min   | Тур          | Max   | Min                              | Тур   | Max | Unit       |

| Auxiliary ADC, AIN4<br>Only <sup>1, 9</sup> |                                                                                                                                                |       |              |       |                                  |       |     |            |

| No Missing Codes                            | Valid at all ADC update rates                                                                                                                  | 20    |              |       |                                  |       |     | Bits       |

| Total Gain Error <sup>3, 4, 10</sup>        | Includes resistor mismatch                                                                                                                     | -0.25 | ±0.06        | +0.25 |                                  | ±0.1  |     | %          |

|                                             | $T_A = -25^{\circ}\text{C to } +65^{\circ}\text{C}$                                                                                            | -0.15 | ±0.03        | +0.15 |                                  |       |     | %          |

| INL                                         | From 6 V to 18 V, ADCFLT = 0x10001,<br>0x08101, 0x00007                                                                                        | -350  | ±10          | +350  |                                  | ±150  |     | ppm of FSR |

| Offset Error <sup>3, 4</sup>                | Chop off, 1 LSB = 27.4 $\mu$ V, after two-point calibration                                                                                    | -160  | ±16          | +160  |                                  |       |     | LSB        |

|                                             | Chop on, after two-point calibration, offset measured using a 0 V differential voltage into the ADC voltage (V <sub>ADC</sub> ) auxiliary pins | -16   | ±4.8         | +16   |                                  | ±4.8  |     | LSB        |

| Offset Error Drift <sup>7</sup>             | Chop off                                                                                                                                       |       | ±0.48        |       |                                  | ±3    |     | LSB/°C     |

| Gain Drift <sup>8</sup>                     | Includes resistor mismatch drift                                                                                                               |       | ±3           |       |                                  |       |     | ppm/°C     |

| Output Noise11                              | 10 Hz update rate, chop on                                                                                                                     |       | 50           |       |                                  |       |     | μV rms     |

|                                             | ADCFLT = 0x00007                                                                                                                               |       | 180          |       |                                  |       |     | μV rms     |

|                                             | ADCFLT = 0x08101                                                                                                                               |       | 280          |       |                                  | 300   |     | μV rms     |

|                                             | ADCFLT = 0x10001                                                                                                                               |       | 400          |       |                                  | 470   |     | μV rms     |

| Auxiliary ADC, AIN5<br>Only¹                |                                                                                                                                                |       |              |       |                                  |       |     |            |

| No Missing Codes                            | Valid at all ADC update rates                                                                                                                  | 20    |              |       |                                  |       |     | Bits       |

| Total Gain Error <sup>3, 12</sup>           |                                                                                                                                                | -0.25 | ±0.06        | +0.25 |                                  | ±0.10 |     | %          |

| INL                                         | ADCFLT = 0x10001, 0x08101, 0x00007                                                                                                             | -60   | ±10          | +60   |                                  | ±15   |     | ppm of FSR |

| Offset Error <sup>3, 12</sup>               |                                                                                                                                                |       |              |       |                                  |       |     |            |

| Chop Off                                    | Chop off, 1 LSB = 1.14 $\mu$ V (unipolar mode), after two-point calibration                                                                    | -160  | ±48          | +160  |                                  |       |     | LSB        |

| Chop On                                     | Chop on                                                                                                                                        | -80   | +16          | +80   |                                  | +16   |     | LSB        |

| Offset Error Drift                          | Chop off                                                                                                                                       |       | ±0.48        |       |                                  | ±0.48 |     | LSB/°C     |

| Gain Drift <sup>8</sup>                     |                                                                                                                                                |       | 3            |       |                                  | 3     |     | ppm/°C     |

| Output Noise                                | 1 kHz update rate, ADCFLT = 0x00007                                                                                                            |       | 7.5          |       |                                  | 10    |     | μV rms     |

| ADC SPECIFICATIONS, ANALOG INPUT            | Register ADC0CON, PGASCALE bits (Bits[11:10]) = 0x3                                                                                            |       |              |       |                                  |       |     |            |

| Primary ADC <sup>1</sup>                    |                                                                                                                                                |       |              |       |                                  |       |     |            |

| Absolute Input<br>Voltage Range             | Applies to both AINO and AIN1                                                                                                                  | -200  |              | +300  |                                  |       |     | mV         |

| Input Voltage<br>Range <sup>13</sup>        |                                                                                                                                                |       |              |       |                                  |       |     | .,         |

|                                             | Gain = 4, limited by absolute input voltage range                                                                                              |       | ±300         |       |                                  |       |     | mV         |

|                                             | Gain = 8                                                                                                                                       |       | ±150         |       |                                  |       |     | mV         |

|                                             | Gain = 32                                                                                                                                      |       | ±37.5        |       |                                  |       |     | mV         |

| lament landers                              | Gain = 512                                                                                                                                     | _     | ±2.3         | . 2   |                                  | 10.3  |     | mV         |

| Input Leakage<br>Current <sup>14</sup>      |                                                                                                                                                | -3    |              | +3    |                                  | ±0.2  |     | nA         |

| Input Offset Current <sup>14</sup>          |                                                                                                                                                |       | 0.2          | 0.8   |                                  | 0.4   |     | nA         |

| Auxiliary ADC, AIN4 Only                    | Voltage ADC expedifications walled in this                                                                                                     | 6     |              | 10    |                                  |       |     | V          |

| Absolute Input Voltage Range <sup>1</sup>   | Voltage ADC specifications valid in this range                                                                                                 | 6     | 0.4-         | 18    |                                  |       |     | V          |

| Input Voltage<br>Range¹                     |                                                                                                                                                |       | 0 to<br>28.8 |       |                                  |       |     | V          |

| nange                                       |                                                                                                                                                |       | 20.0         |       | 1                                |       |     |            |

|                                                  |                                                     | $T_A = -40^{\circ}C \text{ to } +115^{\circ}C$ |       |       | $T_A = 115^{\circ}C \text{ to } 125^{\circ}C^1$ |      |      |                |  |

|--------------------------------------------------|-----------------------------------------------------|------------------------------------------------|-------|-------|-------------------------------------------------|------|------|----------------|--|

| Parameter                                        | Test Conditions/Comments                            | Min                                            | Тур   | Max   | Min                                             | Тур  | Max  | Unit           |  |

| Auxiliary ADC, AIN5                              | VREF = AVDD18 and GND_SW                            |                                                |       |       |                                                 |      |      |                |  |

| Only                                             |                                                     |                                                |       |       |                                                 |      |      | .,             |  |

| Absolute Input<br>Voltage Range <sup>1, 15</sup> |                                                     | 100                                            |       | 1500  |                                                 |      |      | mV             |  |

| Input Voltage                                    |                                                     |                                                | 0 to  |       |                                                 |      |      | V              |  |

| Range <sup>1</sup>                               |                                                     |                                                | 1.4   |       |                                                 |      |      | •              |  |

| Input Current <sup>1</sup>                       |                                                     |                                                | 2.5   | 10    |                                                 | 3.5  |      | nA             |  |

| VOLTAGE REFERENCE                                |                                                     |                                                |       |       |                                                 |      |      |                |  |

| Internal Reference                               |                                                     |                                                | 1.2   |       |                                                 | 1.2  |      | V              |  |

| Power-Up Time <sup>1</sup>                       |                                                     |                                                | 0.5   |       |                                                 | 0.5  |      | ms             |  |

| Initial Accuracy <sup>1</sup>                    | Measured at $T_A = 25^{\circ}C$                     | -0.15                                          |       | +0.15 |                                                 |      |      | %              |  |

| Temperature                                      |                                                     | -20                                            | ±5    | +20   |                                                 | ±8   |      | ppm/°C         |  |

| Coefficient <sup>1, 16</sup>                     |                                                     |                                                | 100   |       |                                                 |      |      | (4.000.1       |  |

| Long-Term Stability 17, 18                       |                                                     |                                                | 100   |       |                                                 |      |      | ppm/1000 hours |  |

| ADC DIAGNOSTICS                                  | At a construction                                   | 12                                             |       | 1.4   |                                                 |      |      |                |  |

| AVDD18 ÷ 136<br>Accuracy <sup>1,5,19</sup>       | At any gain setting                                 | 12                                             |       | 14    |                                                 |      |      | mV             |  |

| Voltage Attenuator                               | Differential voltage increases on the               | 2.4                                            |       | 3.2   |                                                 | 2.8  |      | V              |  |

| Current Source                                   | attenuator when current on                          | 2.4                                            |       | 3.2   |                                                 | 2.0  |      | •              |  |

| Accuracy                                         |                                                     |                                                |       |       |                                                 |      |      |                |  |

| RESISTIVE ATTENUATOR                             |                                                     |                                                |       |       |                                                 |      |      |                |  |

| Divider Ratio                                    |                                                     |                                                | 24    |       |                                                 |      |      |                |  |

| Resistor Mismatch                                | Implicit in the auxiliary ADC total gain error      |                                                | ±3    |       |                                                 |      |      | ppm/°C         |  |

| Drift                                            | specification                                       |                                                |       |       |                                                 |      |      |                |  |

| ADC GROUND SWITCH                                |                                                     |                                                |       |       |                                                 |      |      |                |  |

| Resistor to Ground                               |                                                     | 45                                             | 60    | 75    |                                                 |      |      | kΩ             |  |

| TEMPERATURE SENSOR <sup>1, 20</sup>              | Processor in hibernate mode                         |                                                |       |       |                                                 |      |      |                |  |

| Accuracy                                         |                                                     | -3                                             | ±1    | +3    | -3.5                                            | ±1   | +3.5 | °C             |  |

|                                                  | $T_A = -25^{\circ}\text{C to } +85^{\circ}\text{C}$ | -2.5                                           | ±0.5  | +2.5  |                                                 |      |      | °C             |  |

| 2014/52 014 25657 (202)1                         | $T_A = -10^{\circ}\text{C to } +55^{\circ}\text{C}$ | -2                                             | ±0.5  | +2    |                                                 |      |      | °C             |  |

| POWER-ON RESET (POR) <sup>1</sup>                | Refers to voltage at the VDD pin                    | 2.0                                            | 2.4   | 2.4   |                                                 | 2.2  |      |                |  |

| Trip Level                                       |                                                     | 2.8                                            | 3.1   | 3.4   |                                                 | 3.3  |      | V              |  |

| Hysteresis                                       |                                                     |                                                | 0.1   |       |                                                 |      |      | V              |  |

| LOW VOLTAGE FLAG                                 | Defers to valte so at the VDD pin                   | 2.6                                            | 2.75  | 2.00  |                                                 |      |      | V              |  |

| Low Voltage Flag<br>Level                        | Refers to voltage at the VDD pin                    | 2.6                                            | 2.75  | 3.00  |                                                 |      |      | V              |  |

| WDT                                              |                                                     |                                                |       |       |                                                 |      |      |                |  |

| Shortest Timeout                                 | 32,768 Hz clock with a prescaler of 1               |                                                | 30.5  |       |                                                 | 30.5 |      | μs             |  |

| Period                                           | 52,7 so 112 clock man a presenter or 1              |                                                | 5 0.5 |       |                                                 | 50.5 |      |                |  |

| Longest Timeout                                  | 32,768 Hz clock with a prescaler of 4096            |                                                | 8192  |       |                                                 |      |      | sec            |  |

| Period                                           |                                                     |                                                |       |       |                                                 |      |      |                |  |

| FLASH/EE MEMORY                                  |                                                     |                                                |       |       |                                                 |      |      |                |  |

| Program Flash Size                               |                                                     |                                                | 128   |       |                                                 |      |      | kB             |  |

| Data Flash Size                                  |                                                     |                                                | 4     |       |                                                 |      |      | kB             |  |

| Endurance <sup>21</sup>                          |                                                     | 10,000                                         |       |       |                                                 |      |      | Cycles         |  |

| Data Retention <sup>22</sup>                     |                                                     | 20                                             |       |       | 1                                               |      |      | Years          |  |

| LOGIC INPUTS <sup>1</sup>                        |                                                     |                                                |       |       |                                                 |      |      |                |  |

| Input Voltage                                    |                                                     |                                                |       | 0.4   |                                                 |      |      | .,             |  |

| Low (V <sub>INL</sub> )                          |                                                     | 20                                             |       | 0.4   |                                                 |      |      | V              |  |

| High (V <sub>INH</sub> )                         | All logic outputs                                   | 2.0                                            |       |       |                                                 |      |      | V              |  |

| LOGIC OUTPUTS <sup>1</sup>                       | All logic outputs, measured with ±1 mA load         |                                                |       |       |                                                 |      |      |                |  |

| Output Voltage                                   |                                                     |                                                |       |       |                                                 |      |      |                |  |

| High (V <sub>он</sub> )                          |                                                     | 33VDD -                                        |       |       |                                                 |      |      | V              |  |

|                                                  |                                                     | 0.4                                            |       |       |                                                 |      |      |                |  |

| Low (V <sub>OL</sub> )                           |                                                     |                                                |       | 0.4   |                                                 |      |      | V              |  |

|                                                     |                                                                                                    | <b>T</b> <sub>A</sub> = - | -40°C to + | 115°C   | T <sub>A</sub> = 115°C to 125°C <sup>1</sup> |          |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------|------------|---------|----------------------------------------------|----------|--|

| Parameter                                           | Test Conditions/Comments                                                                           | Min                       | Тур        | Max     | Min Typ Max                                  | Unit     |  |

| DIGITAL INPUTS <sup>1</sup>                         | All digital inputs except RESET, SWDIO, and                                                        |                           |            |         |                                              |          |  |

|                                                     | SWCLK                                                                                              |                           |            |         |                                              |          |  |

| Input Current                                       |                                                                                                    |                           |            |         |                                              |          |  |

| (Leakage Current)                                   | .,                                                                                                 |                           |            |         |                                              |          |  |

| Logic 1                                             | $V_{\text{INH}} = 3.3 \text{ V}$                                                                   | -10                       | ±1         | +10     |                                              | μA       |  |

| Logic 0                                             | $V_{INL} = 0 V$                                                                                    | -10                       | ±1         | +10     |                                              | μΑ       |  |

| Input Capacitance                                   |                                                                                                    |                           | 10         |         |                                              | pF       |  |

| ON-CHIP OSCILLATORS                                 |                                                                                                    |                           |            |         |                                              |          |  |

| Low Frequency                                       |                                                                                                    |                           | 32,768     |         |                                              | Hz       |  |

| Oscillator                                          |                                                                                                    |                           |            |         |                                              |          |  |

| Accuracy                                            |                                                                                                    |                           | ±5         |         |                                              | %        |  |

|                                                     | After a calibration from high frequency                                                            | -6                        |            | +6      |                                              | %        |  |

|                                                     | oscillator                                                                                         |                           | 46304      |         |                                              |          |  |

| High Frequency<br>Oscillator                        |                                                                                                    |                           | 16.384     |         |                                              | MHz      |  |

|                                                     |                                                                                                    |                           |            |         |                                              |          |  |

| Accuracy                                            |                                                                                                    | 0.7                       | . 0. 5     | . 0.75  |                                              | 0/       |  |

| LINCAL <sup>1, 23</sup>                             |                                                                                                    | -0.7                      | ±0.5       | +0.75   |                                              | %        |  |

| High Precision<br>Mode                              |                                                                                                    | -1                        |            | +1      |                                              | %        |  |

| Low Precision                                       |                                                                                                    | -3                        |            | +3      |                                              | %        |  |

| Mode                                                |                                                                                                    | _ <del>_</del>            |            | +3      |                                              | 70       |  |

| PROCESSOR START-UP                                  |                                                                                                    |                           |            |         |                                              |          |  |

| TIME <sup>1</sup>                                   |                                                                                                    |                           |            |         |                                              |          |  |

| At Power-On                                         | Includes kernel power-on execution time,                                                           |                           | 18         |         |                                              | ms       |  |

|                                                     | VDD drops to <0.8 V                                                                                |                           |            |         |                                              |          |  |

| Brownout                                            | VDD drops below POR voltage but not                                                                |                           | 1.15       |         |                                              | ms       |  |

|                                                     | below 0.8 V                                                                                        |                           |            |         |                                              |          |  |

| After Reset Event                                   | Includes kernel power-on execution time                                                            |                           | 1.25       |         |                                              | ms       |  |

| Wake-Up from LIN                                    |                                                                                                    |                           | 0.15       |         |                                              | ms       |  |

| LIN INPUT/OUTPUT                                    |                                                                                                    |                           |            |         |                                              |          |  |

| GENERAL <sup>1</sup>                                |                                                                                                    |                           |            |         |                                              |          |  |

| Baud Rate                                           |                                                                                                    | 1000                      |            | 20,000  |                                              | Bits/sec |  |

| VDD                                                 | Supply voltage range for which the LIN                                                             | 7                         |            | 18      |                                              | V        |  |

|                                                     | interface is functional                                                                            |                           |            |         |                                              |          |  |

| LIN Comparator                                      |                                                                                                    |                           | 38         | 90      |                                              | μs       |  |

| Response Time                                       |                                                                                                    |                           |            |         |                                              |          |  |

| LIN DC PARAMETERS                                   |                                                                                                    |                           |            |         |                                              |          |  |

| Current Limit for Driver                            | VBAT = VBAT (maximum)                                                                              | 40                        |            | 200     |                                              | mA       |  |

| when LIN Bus is in                                  |                                                                                                    |                           |            |         |                                              |          |  |

| Dominant State                                      |                                                                                                    |                           |            |         |                                              |          |  |

| (ILIN_DOM_MAX)                                      | 70V < voltage of UN bus (V - ) < 19 V VDD -                                                        |                           |            | 20      |                                              |          |  |

| Driver Off (I <sub>LIN_PAS_REC</sub> ) <sup>1</sup> | 7.0 V < voltage of LIN bus ( $V_{BUS}$ ) < 18 V, VDD = input leakage voltage ( $V_{LIN}$ ) – 0.7 V |                           |            | 20      |                                              | μΑ       |  |

| Input Leakage Current                               | $V_{LIN} = 0 \text{ V}, \text{ VBAT} = 12 \text{ V}, \text{ driver off}$                           | -1                        |            |         |                                              | mA       |  |

| at Receiver                                         | VLIN — 0 V, VDAT — 12 V, GITVET OIT                                                                | _ [                       |            |         |                                              | IIIA     |  |

| (I <sub>LIN PAS DOM</sub> ) <sup>1</sup>            |                                                                                                    |                           |            |         |                                              |          |  |

| Control Unit                                        | Ground = VDD, $0 \text{ V} < V_{\text{LIN}} < 18 \text{ V}$ ,                                      | -1                        |            | +1      |                                              | mA       |  |

| Disconnected from                                   | VBAT = 12 V                                                                                        |                           |            |         |                                              |          |  |

| Ground (I <sub>LIN_NO_GND</sub> ) <sup>1, 24</sup>  |                                                                                                    |                           |            |         |                                              |          |  |

| VBAT Disconnected                                   | VDD = ground, 0 V < V <sub>BUS</sub> < 18 V                                                        |                           |            | 30      |                                              | μΑ       |  |

| (I <sub>BUS_NO_BAT</sub> ) <sup>1</sup>             |                                                                                                    |                           |            |         |                                              |          |  |

| LIN Receiver Dominant                               | VDD > 7.0 V                                                                                        |                           |            | 0.4×    |                                              | V        |  |

| State (V <sub>LIN_DOM</sub> ) <sup>1</sup>          |                                                                                                    |                           |            | VDD     |                                              |          |  |

| LIN Receiver Recessive                              | VDD > 7.0 V                                                                                        | 0.6 ×                     |            |         |                                              | V        |  |

| State (V <sub>LIN_REC</sub> ) <sup>1</sup>          |                                                                                                    | VDD                       |            |         |                                              |          |  |

| LIN Receiver Threshold                              | $V_{\text{LIN\_CNT}} = $ (receiver threshold of recessive to                                       | 0.475×                    | 0.5 ×      | 0.525 × |                                              | V        |  |

| C 0.4 11                                            |                                                                                                    | // 1/ 1                   | 1/1 1/1 1  | VDD     | 1                                            | 1        |  |

| Center (V <sub>LIN_CNT</sub> ) <sup>1</sup>         | dominant bus edge (V <sub>TH_DOM</sub> ) + receiver threshold of dominant to recessive bus         | VDD                       | VDD        | VDD     |                                              |          |  |

|                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            | T <sub>A</sub> = - | 40°C to + | -115°C         | T <sub>A</sub> = |     |     |      |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|----------------|------------------|-----|-----|------|

| Parameter                                                                                        | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                   | Min                | Тур       | Max            | Min              | Тур | Max | Unit |

| LIN Receiver Threshold<br>Hysteresis (V <sub>HYS</sub> ) <sup>1</sup>                            | $V_{\text{HYS}} = V_{\text{TH\_REC}} - V_{\text{TH\_DOM}}$                                                                                                                                                                                                                                                                                                                                                                 |                    |           | 0.175 ×<br>VDD |                  |     |     | V    |

| LIN Dominant Output<br>Voltage with Supply<br>Voltage Low                                        | VDD = 7.0 V                                                                                                                                                                                                                                                                                                                                                                                                                |                    |           | VDD            |                  |     |     |      |

| $(V_{\text{LIN\_DOM\_DRV\_LOSUP}})^1$<br>Load Resistance (R <sub>L</sub> )<br>= 500 $\Omega$     |                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |           | 1.2            |                  |     |     | V    |

| $R_L=1000\;\Omega$                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.6                |           |                |                  |     |     | V    |

| LIN Dominant Output<br>Voltage with Supply<br>Voltage High<br>(VLIN_DOM_DRV_HISUP) <sup>1</sup>  | VDD = 18 V                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |           |                |                  |     |     |      |

| $R_L = 500 \ \Omega$                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |           | 2              |                  |     |     | V    |

| $R_L = 1000 \Omega$                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.8                |           |                |                  |     |     | V    |

| LIN Recessive Output                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.8 × VDD          |           |                |                  |     |     | V    |

| Voltage ( $V_{LIN\_RECESSIVE}$ ) <sup>1</sup><br>VBAT Shift <sup>1,24</sup>                      |                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                  |           | 0.115×         |                  |     |     | v    |

| C                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |           | VDD            |                  |     |     | V    |

| Ground Shift <sup>1,24</sup>                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                  |           | 0.115 ×<br>VDD |                  |     |     | V    |

| Slave Termination<br>Resistance (R <sub>SLAVE</sub> )                                            |                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                 | 30        | 47             |                  | 30  |     | kΩ   |

| Voltage Drop at the<br>Serial Diode                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.4                | 0.7       | 1              |                  |     |     | V    |

| (V <sub>SERIAL_DIODE</sub> ) <sup>1</sup>                                                        | Dual and any distance (laws are as site as a                                                                                                                                                                                                                                                                                                                                                                               |                    |           |                |                  |     |     |      |

| LIN AC PARAMETERS <sup>1</sup>                                                                   | Bus load conditions (bus capacitance (C <sub>BUS</sub> )  bus resistance (R <sub>BUS</sub> )): 1 nF  1 k $\Omega$ or 6.8 nF  660 $\Omega$ or 10 nF  500 $\Omega$                                                                                                                                                                                                                                                           |                    |           |                |                  |     |     |      |

| Duty Cycle 1 (D1)                                                                                | Threshold recessive maximum (TH <sub>REC(MAX)</sub> ) = $0.744 \times VBAT$ , threshold dominant maximum (TH <sub>DOM(MAX)</sub> ) = $0.581 \times VBAT$ , supply voltage at transceiver (V <sub>SUP</sub> ) = $7.0 \text{ V}$ to $18 \text{ V}$ , time of one bit on the LIN bus (t <sub>BIT</sub> ) = $50 \text{ µs}$ , D1 = minimum time for a bus recessive signal (t <sub>BUS REC(MIN)</sub> )/( $2 \times t_{BIT}$ ) | 0.396              |           |                |                  |     |     |      |

| Duty Cycle 2 (D2)                                                                                | Threshold recessive minimum (TH <sub>REC(MIN)</sub> ) = 0.284 × VBAT, threshold dominant minimum (TH <sub>DOM(MIN)</sub> ) = 0.422 × VBAT, V <sub>SUP</sub> = 7.0 V to 18 V, t <sub>BIT</sub> = 50 $\mu$ s, D2 = maximum time for a bus recessive signal (t <sub>BUS_REC(MAX)</sub> )/(2 × t <sub>BIT</sub> )                                                                                                              |                    |           | 0.581          |                  |     |     |      |

| Duty Cycle 3 (D3) <sup>24</sup>                                                                  | $TH_{REC(MAX)} = 0.778 \times VBAT, TH_{DOM(MAX)} = 0.616 \times VBAT, VDD = 7.0 V to 18 V, t_{BIT} = 96 \ \mu s, D3 = t_{BUS\_REC(MIN)}/(2 \times t_{BIT})$                                                                                                                                                                                                                                                               | 0.417              |           |                |                  |     |     |      |

| Duty Cycle 4 (D4) <sup>24</sup>                                                                  | $TH_{REC(MIN)} = 0.389 \times VBAT, TH_{DOM(MIN)} = 0.251 \times VBAT, VDD = 7.0 V to 18 V, t_{BIT} = 96 \ \mu s, D4 = t_{BUS} \ REC(MAX)/(2 \times t_{BIT})$                                                                                                                                                                                                                                                              |                    |           | 0.590          |                  |     |     |      |

| Propagation Delay of Receiver (t <sub>RX_PD</sub> ) <sup>24</sup>                                |                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |           | 6              |                  |     |     | μs   |

| Symmetry of Receiver<br>Propagation Delay<br>Rising Edge<br>(t <sub>RX_SYM</sub> ) <sup>24</sup> | With respect to falling edge ( $t_{RX\_SYM} = propagation$ delay rising edge ( $t_{RX\_PDR}$ ) – propagation delay falling edge ( $t_{RX\_PDF}$ ))                                                                                                                                                                                                                                                                         | -2                 |           | +2             |                  |     |     | μs   |

| V <sub>HYS</sub> <sup>1</sup>                                                                    | $V_{HYS} = V_{TH\_REC} - V_{TH\_DOM}$                                                                                                                                                                                                                                                                                                                                                                                      |                    |           | 0.175 ×<br>VDD |                  |     |     | V    |

| $V_{\text{LIN\_DOM\_DRV\_LOSUP}^1}$                                                              | VDD = 7.0 V                                                                                                                                                                                                                                                                                                                                                                                                                |                    |           |                |                  |     |     |      |

|                                                                              |                                                                                                                                                                                                      | $T_A = -40^{\circ}C \text{ to } +115^{\circ}C$ |     |      | T <sub>A</sub> = 115°C to 125°C <sup>1</sup> |     |     |      |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|------|----------------------------------------------|-----|-----|------|

| Parameter                                                                    | Test Conditions/Comments                                                                                                                                                                             | Min                                            | Тур | Max  | Min                                          | Тур | Max | Unit |

| POWER CONSUMPTION                                                            |                                                                                                                                                                                                      |                                                |     |      |                                              |     |     |      |

| Supply Current (I <sub>DD</sub> )<br>Processor, Normal<br>Mode <sup>25</sup> | Clock Divider 0 (CD0) (peripheral clock<br>(PCLK) = 16 MHz), 16 MHz, 1% mode, ADCs<br>off, reference buffer off, executing code<br>from program flash                                                |                                                | 8   | 17   |                                              |     |     | mA   |

|                                                                              | Clock Divider 1 (CD1) (PCLK = 8 MHz), 16 MHz,<br>1% mode, ADCs off, reference buffer off,<br>executing code from program flash                                                                       |                                                | 6   |      |                                              |     |     | mA   |

|                                                                              | CD0 (PCLK = 16 MHz), 16 MHz, 1% mode,<br>ADCs on, reference buffer on, executing<br>code from program flash                                                                                          |                                                | 9.5 | 18.5 |                                              |     |     | mA   |