|          |         |          |        |              | REVISIONS  |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|----------|---------|----------|--------|--------------|------------|--------|--------|----------|-----|----|------|-------------|-------|--------|--------|--------------|--------------|------|----------------|--------|-----------|----|

|          |         |          |        | LTR DESCRIPT |            |        |        | ION DATE |     |    |      | APPROVED    |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      | <b>—</b> .     |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                | έ¢.    |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      | <u> </u>       | ĽĀ.    | ×.        |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      | (A)            |        | Bł.       |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                | 2.0.46 | 99C       |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

| Prepared | d in ac | cordan   | ce wit | h ASN        | /E Y1      | 4.24   | 1      | -        | 1   |    | 1    |             | -     |        |        | 1            |              | Ve   | ndor it        | em dr  | awing     |    |

| REV      |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

| PAGE     |         |          |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

| REV      |         | _        |        |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

| PAGE     | 18      | 19       | 20     | 21           | 22         |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

| REV STA  |         |          | REV    |              |            |        |        |          |     |    |      |             |       |        |        |              |              |      |                |        |           |    |

| OF PAG   | E9      |          | PAG    |              |            | 1      | 2      | 3        | 4   | 5  | 6    | 7           | 8     | 9      | 10     | 11           | 12           | 13   | 14             | 15     | 16        | 17 |

| PMIC N/  | Α       |          |        |              | PARE       |        |        |          |     |    |      |             |       |        |        |              |              |      | RITIN<br>218-3 |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    |      |             | ht    | tps:// |        | <u>.dla.</u> | <u>mil/L</u> | .and | and N          | lariti | <u>me</u> |    |

| Original | date c  | of drawi | ng     |              | CKE        |        |        |          |     |    |      | ТІТ         | LE    |        |        |              |              |      |                |        |           |    |

|          | Y-MN    |          | -      |              | JESH       |        |        |          |     |    |      |             | ROC   | IRCL   | JIT, [ | DIGIT        | ΓAL, Ι       | LOW  | POV            | VER,   |           |    |

|          |         |          | PROVE  |              | ,<br>CHME. | YER    |        |          |     | PR | ECIS | ION A       | ۱NAL  | OG I   | MICF   |              |              |      |                |        |           |    |

|          |         |          |        |              |            |        |        |          |     |    | NOL  | IHIC        | , SIL | ICON   | 1      |              |              |      |                |        |           |    |

|          |         |          |        | ZE           | COE        | DE IDE | INT. N |          |     |    | DWO  | g no.       |       | ١      | IGO    | 2/21         | 60           | 6    |                |        |           |    |

|          |         |          |        | -            | 4          |        |        | 102      | 236 |    |      |             |       |        |        | 02           | ./ 2         | 00   | 0              |        |           |    |

| F        |         |          | REV    | ,            |            |        |        |          |     |    | PAG  | <b>BE</b> 1 | OF    | 22     |        |              |              |      |                |        |           |    |

DISTRIBUTION STATEMENT A. Approved for public release. Distribution is unlimited.

### 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance low power, precision analog microcontroller microcircuit, with an operating temperature range of -55°C to +125°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| <u>V62/21606</u> -                     | <u>01</u>                  | <u> </u>                    | E                                    |

|----------------------------------------|----------------------------|-----------------------------|--------------------------------------|

| Drawing<br>number                      | Device type<br>(See 1.2.1) | Case outline<br>(See 1.2.2) | Lead finish<br>(See 1.2.3)           |

| 1.2.1 <u>Device type(s)</u> .          |                            | , ,                         |                                      |

| Device type                            | Generic                    |                             | Circuit function                     |

| 01                                     | ADUCM362-EP                | Low pow                     | er, precision analog microcontroller |

| 122 Case outline(s) The case outline(s | are as specified herein    |                             |                                      |

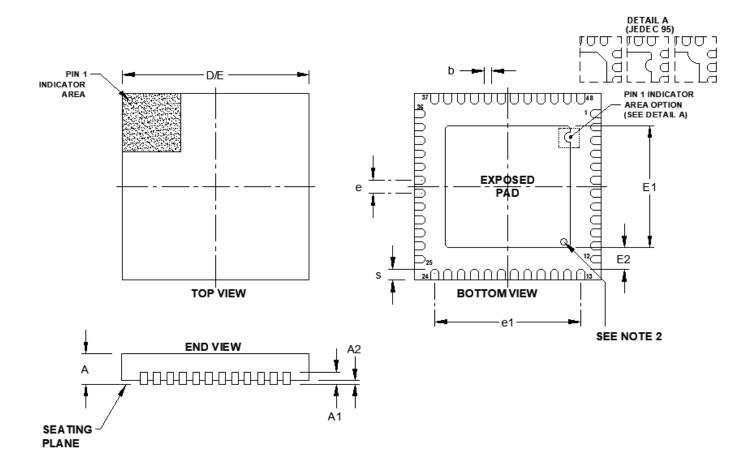

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95  | Package style                         |

|----------------|----------------|---------------|---------------------------------------|

| х              | 48             | MO-220-WKKD-4 | Lead frame chip scale package (LFCSP) |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator          | Material                                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>F | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Tin-lead alloy (BGA/CGA)<br>Other |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/21606</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 2                   |

### 1.3 Absolute maximum ratings. 1/

| AVDD to AGND<br>IOVDD to DGND<br>Digital input voltage to DGND<br>Digital output voltage to DGND<br>Analog inputs to AGND | 0.3 V to +3.96 V <u>2</u> /<br>0.3 V to +3.96 V <u>2</u> /<br>0.3 V to +3.96 V <u>2</u> / |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Temperature:                                                                                                              | 5500 ( 40500                                                                              |

| Operating range                                                                                                           | 55°C to +125°C                                                                            |

| Storage range                                                                                                             | 65°C to +150°C                                                                            |

| Junction (TJ)                                                                                                             | . +150°C                                                                                  |

| Peak solder reflow:                                                                                                       |                                                                                           |

| Tin Lead (SnPb) assemblies (10 seconds to 30 seconds)                                                                     | . 240°C                                                                                   |

| Nickel (Ni), Palladium (Pd), Gold (Au) assemblies (20 seconds to 40 seconds)                                              | . 260°C                                                                                   |

| Thermal resistance, junction to case (θJC)                                                                                | . 9.5°C/W                                                                                 |

| Thermal resistance, junction to ambient (θJA)                                                                             | . 28°C/W                                                                                  |

| Electrostatic discharge (ESD) rating:                                                                                     |                                                                                           |

| Human body model (HBM) per JEDEC JS-001                                                                                   | ±2 kV                                                                                     |

| Field induced charged device model (FICDM) per JEDEC JS-002                                                               | . ±1000 V                                                                                 |

| 1.4 <u>Recommended operating conditions</u> . <u>3/</u>                                                                   |                                                                                           |

|                                                                                                                           | 1.8 V to 3.6 V                                                                            |

|                                          | 1.6 V 10 5.0 V  |

|------------------------------------------|-----------------|

| Ambient operating temperature range (TA) | -55°C to +125°C |

DGND is the digital system ground reference.

<sup>&</sup>lt;u>2/</u> <u>3</u>/ Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/21606</b> |  |  |

|-----------------------|------|----------------|--------------------------|--|--|

| COLUMBUS, OHIO        | A    | 16236          |                          |  |  |

|                       |      | REV            | PAGE 3                   |  |  |

<sup>1/</sup> Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 2. APPLICABLE DOCUMENTS

JEDEC Solid State Technology Association

| JEDEC JS-001 | - | Human Body Model Testing of Integrated Circuits                              |

|--------------|---|------------------------------------------------------------------------------|

| JEDEC JS-002 | _ | Electrostatic Discharge Sensitivity Testing - Charge Device Model (CDM)      |

| JESD22-A117  | _ | Electrically Eraseable Programmable Rom (EEPROM) Program/Erase Endurance and |

|              |   | Data Retention Test                                                          |

| JEDEC PUB 95 | _ | Registered and Standard Outlines for Semiconductor Devices                   |

(Copies of these documents are available online at https://www.jedec.org.)

#### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

3.5 Diagrams.

3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

3.5.2 Terminal connections. The terminal connections shall be as shown in figure 2.

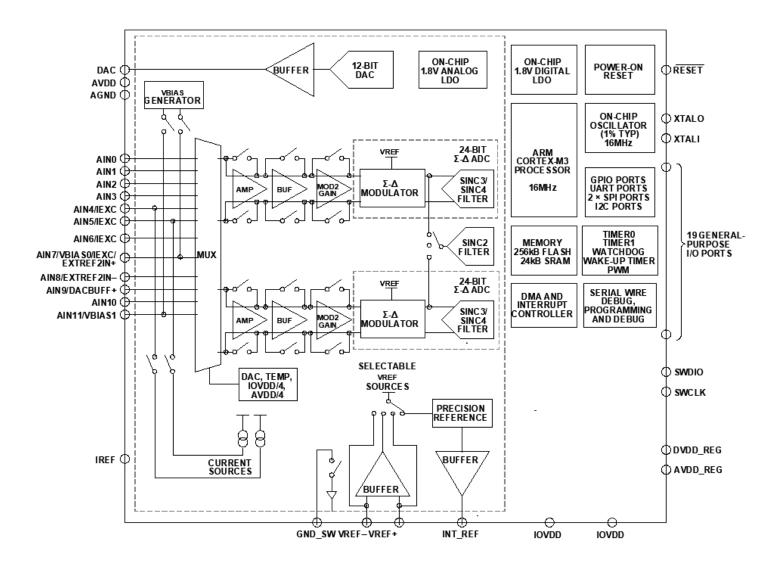

3.5.3 Functional block diagram. The functional block diagram shall be as shown in figure 3.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/21606</b> |  |  |

|-----------------------|------|----------------|--------------------------|--|--|

| COLUMBUS, OHIO        | A    | 16236          |                          |  |  |

|                       |      | REV            | PAGE 4                   |  |  |

| Test                                                                    | Symbol | Conditions <u>2</u> /                                                                                                              | Temperature,<br>TA | Device<br>type | Lin                  | Unit          |                 |

|-------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|----------------------|---------------|-----------------|

|                                                                         |        |                                                                                                                                    |                    |                | Min                  | Max           |                 |

| ADC specifications section                                              | on.    | ADC0 and ADC1                                                                                                                      |                    | •              |                      | •             |                 |

| Conversion rate <u>3</u> /                                              |        | Chop off                                                                                                                           | -55°C to +125°C    | 01             | 3.5                  | 3906          | Hz              |

|                                                                         |        | Chop on                                                                                                                            | _                  |                | 3.5                  | 1302          |                 |

| No missing codes <u>3</u> /                                             |        | Chop off, ADC frequency $(fADC) \le 500 \text{ Hz}$                                                                                | -55°C to +125°C    | 01             | 24                   |               | Bits            |

|                                                                         |        | Chop on, fADC $\leq$ 250 Hz                                                                                                        | _                  |                | 24                   |               |                 |

| Integral nonlinearity <u>3</u> /                                        |        | Gain = 1, input buffer off                                                                                                         | -55°C to +125°C    | 01             | ±10 t                | ppm of<br>FSR |                 |

|                                                                         |        | Gain = 2, 4, 8, or 16                                                                                                              | _                  |                | ±15 t                |               |                 |

|                                                                         |        | Gain = 32, 64, or 128                                                                                                              |                    |                | ±20 t                |               |                 |

| Offset error<br><u>4/ 5/ 6/ 7/ 8</u> /                                  |        | Chop off, and the offset error is in<br>the order of the noise for the<br>programmed gain and update rate<br>following calibration | -55°C to +125°C    | 01             | 01 ±230/gain typical |               | μV              |

|                                                                         |        | Chop on <u>3</u> /                                                                                                                 | _                  |                | ±1.0                 |               |                 |

| Offset error drift versus                                               |        | Chop off, gain ≤ 4                                                                                                                 | -55°C to +125°C    | 01             | 1/gain               | μV/°C         |                 |

| temperature<br><u>3</u> / <u>6</u> / <u>7</u> /                         |        | Chop off, gain ≥ 8                                                                                                                 |                    |                | 230 typical          |               |                 |

|                                                                         |        | Chop on                                                                                                                            | -                  |                | 10 typical           |               |                 |

| Offset error lifetime <u>9</u> /<br>stability                           |        | Gain = 128                                                                                                                         | -55°C to +125°C    | 01             | 1 ty                 | pical         | μV /<br>1000 Hr |

| Full scale error<br><u>3/ 6/ 7/ 8/ 10</u> /                             |        |                                                                                                                                    | -55°C to +125°C    | 01             | ±0.5/gai             | n typical     | mV              |

| Full scale error <u>9</u> /<br>lifetime stability                       |        | Gain = 128                                                                                                                         | -55°C to +125°C    | 01             | 70 ty                | /pical        | μV /<br>1000 Hr |

| Gain error drift versus<br>temperature <u>3</u> / <u>6</u> / <u>7</u> / |        | Gain = 1, 2, 4, 8, or 16,<br>External reference                                                                                    | -55°C to +125°C    | 01             | ±3 typical           |               | ppm/°C          |

|                                                                         |        | Gain = 32, 64, or 128,<br>External reference                                                                                       |                    |                | ±6 ty                | vpical        |                 |

| PGA gain mismatch<br>error                                              |        |                                                                                                                                    | -55°C to +125°C    | 01             | ±0.15                | typical       | %               |

## TABLE I. Electrical performance characteristics. 1/

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/21606</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | 16236          |                          |  |

|                       |      | REV            | PAGE 5                   |  |

| Test                                                | Symbol       | Conditions <u>2</u> /                                                                                                                                                                                            | Temperature,<br>TA           | Device<br>type | Lin           | nits          | Unit |    |

|-----------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|---------------|---------------|------|----|

|                                                     |              |                                                                                                                                                                                                                  |                              |                | Min           | Max           |      |    |

| ADC specifications section                          | on – continu | ed. ADC0 and ADC1                                                                                                                                                                                                |                              |                |               |               |      |    |

| Power supply <u>3</u> /<br>rejection                |              | Chop on, ADC input = 0.25 V,<br>gain = 4, external reference                                                                                                                                                     | -55°C to +125°C              | 01             | 95            |               | dB   |    |

|                                                     |              | Chop off, ADC input = 0.78 V,<br>gain = 128, external reference                                                                                                                                                  |                              |                | 80            |               |      |    |

|                                                     |              | Chop off, ADC input = 1 V,<br>gain = 1, external reference                                                                                                                                                       | -                            |                | 90            |               |      |    |

| Absolute input voltage<br>range, unbuffered<br>mode |              |                                                                                                                                                                                                                  | -55°C to +125°C              | 01             | AGND          | AVDD          | V    |    |

| Absolute input voltage<br>range, buffered<br>mode   |              | Available for all gain settings,<br>G = 1 to 128                                                                                                                                                                 | -55°C to +125°C              | 01             | AGND<br>+ 0.1 | AVDD<br>- 0.1 | V    |    |

| Differential input <u>3</u> /                       |              | Gain = 1                                                                                                                                                                                                         | -55°C to +125°C              | 01             |               | ±VREF         | V    |    |

| voltage ranges                                      |              | Gain = 2                                                                                                                                                                                                         |                              |                |               |               | ±500 | mV |

|                                                     |              | Gain = 4                                                                                                                                                                                                         |                              |                |               |               | ±250 |    |

|                                                     |              | Gain = 8                                                                                                                                                                                                         |                              |                |               |               | ±125 | 1  |

|                                                     |              | Gain = 16                                                                                                                                                                                                        |                              |                |               | ±62.5         |      |    |

| Common mode <u>3</u> /<br>voltage                   | Vсм          | Ideally, V <sub>CM</sub> = ((AIN+) + (AIN-))/2<br>and gain = 2 to 128, where AIN+ or<br>AIN- refers to any ADC input pin in<br>which the sign indicates a positive<br>or negative voltage input,<br>respectively | -55°C to +125°C              | 01             | AGND          | AVDD          | V    |    |

| Input current, <u>11</u> /<br>buffered mode         |              | Gain > 1 (excluding AIN4, AIN5,<br>AIN6, and AIN7 pins)                                                                                                                                                          | -55°C to +125°C 01 1 typical |                | pical         | nA            |      |    |

|                                                     |              | Gain > 1 (AIN4, AIN5, AIN6, and<br>AIN7 pins)                                                                                                                                                                    |                              |                | 2 ty          | pical         |      |    |

| Input current, <u>11</u> /<br>unbuffered mode       |              | Input current varies with input voltage                                                                                                                                                                          | -55°C to +125°C              | 01             | 860 t         | ypical        | nA/V |    |

## TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/21606</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV            | PAGE 6                   |

| Test                                                          | Symbol           | Conditions <u>2</u> /                                                                                                                      | Temperature,<br>TA | Device<br>type | Lin    | nits    | Unit    |       |        |   |

|---------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|--------|---------|---------|-------|--------|---|

|                                                               |                  |                                                                                                                                            |                    |                | Min    | Max     |         |       |        |   |

| ADC specification sectio                                      | n – continue     | ed. ADC0 and ADC1                                                                                                                          |                    |                |        |         |         |       |        |   |

| Average input <u>3</u> /                                      |                  | AIN1, AIN3, AIN5, AIN7, and AIN11                                                                                                          | -55°C to +125°C    | 01 ±5          |        | pical   | pA/°C   |       |        |   |

| current drift,<br>buffered mode                               |                  | AIN0, AIN4, AIN9, and AIN10                                                                                                                |                    |                | ±9 ty  | pical   |         |       |        |   |

|                                                               |                  | AIN2, AIN6, and AIN8                                                                                                                       |                    |                | ±15 t  | ypical  |         |       |        |   |

| Average input <u>3</u> /<br>current drift,<br>unbuffered mode |                  |                                                                                                                                            | -55°C to +125°C    | 01             | ±250 1 | typical | pA/V/°C |       |        |   |

| Common mode <u>3</u> /                                        | CMR              | On ADC input,                                                                                                                              | -55°C to +125°C    | 01             | 100 t  | ypical  | dB      |       |        |   |

| rejection, dc                                                 |                  | ADC gain = 1, AVDD < 2 V                                                                                                                   |                    |                | 65     |         | -       |       |        |   |

|                                                               |                  | On ADC input,                                                                                                                              |                    | -              |        |         |         | 100 t | ypical | - |

|                                                               |                  | ADC gain = 1, AVDD > 2 V                                                                                                                   |                    |                | 80     |         |         |       |        |   |

|                                                               |                  | On ADC input,<br>ADC gain = 2 to 128                                                                                                       |                    |                | 80     |         |         |       |        |   |

| Common mode <u>3</u> /<br>rejection,<br>50 Hz/60Hz            | CMR              | ADC gain = 1, 50 Hz/60 Hz ± 1 Hz,<br>f <sub>ADC</sub> = 16.67 Hz with chop on, and<br>f <sub>ADC</sub> = 50 Hz with chop off               | -55°C to +125°C    | 01             | 97     |         | dB      |       |        |   |

|                                                               |                  | ADC gain = 2 to 128,<br>50 Hz/60 Hz $\pm$ 1 Hz,<br>f <sub>ADC</sub> = 16.67 Hz with chop on, and<br>f <sub>ADC</sub> = 50 Hz with chop off |                    |                | 90     |         |         |       |        |   |

| Normal mode <u>3</u> /<br>rejection,                          | NMR              | On ADC input, 50 Hz/60 Hz ± 1 Hz,                                                                                                          | -55°C to +125°C    | 01             | 80 ty  | pical   | dB      |       |        |   |

| 50 Hz/60Hz                                                    |                  | f <sub>ADC</sub> = 16.67 Hz with chop on, and<br>f <sub>ADC</sub> = 50 Hz with chop off                                                    |                    |                | 60     |         | -       |       |        |   |

| Temperature sensor sec                                        | tion. <u>3</u> / |                                                                                                                                            |                    |                |        |         |         |       |        |   |

| Voltage output                                                |                  | After use calibration, processor<br>powered down or in standby mode<br>before measurements                                                 | +25°C              | 01             | 82.1 t | ypical  | mV      |       |        |   |

| Voltage temperature<br>coefficient                            |                  |                                                                                                                                            | -55°C to +125°C    | 01             | 250 t  | ypical  | μV/°C   |       |        |   |

| Accuracy                                                      |                  |                                                                                                                                            | -55°C to +125°C    | 01             | 6 ty   | pical   | °C      |       |        |   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. V62/21606 |

|-----------------------|------|----------------|-------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                   |

|                       |      | REV            | PAGE 7            |

| Test                                  | Test Symbol Conditions <u>2</u> / Te |                                                                           | Temperature,<br>TA | Device<br>type | Lin           | nits          | Unit   |

|---------------------------------------|--------------------------------------|---------------------------------------------------------------------------|--------------------|----------------|---------------|---------------|--------|

|                                       |                                      |                                                                           |                    |                | Min           | Max           | -      |

| Ground switch section.                | •                                    |                                                                           |                    | •              |               | •             |        |

| On resistance                         | Ron                                  |                                                                           | -55°C to +125°C    | 01             | 10 ty         | /pical        | Ω      |

|                                       |                                      |                                                                           |                    |                | 3.7           | 19            |        |

| Allowable current <u>3</u> /          |                                      | 20 k $\Omega$ resistor off, direct short to ground                        | -55°C to +125°C    | 01             |               | 20            | mA     |

| Voltage reference section             |                                      | ADC internal reference                                                    |                    |                |               |               |        |

| Internal reference voltage            | VREF                                 |                                                                           | -55°C to +125°C    | 01             | 1.2 ty        | ypical        | V      |

| Initial accuracy                      |                                      |                                                                           | +25°C              | 01             | -0.1          | +0.1          | %      |

| Reference <u>3/ 12/</u>               |                                      |                                                                           | -55°C to +125°C    | 01             | ±5 ty         | /pical        | ppm/°C |

| temperature coefficient               |                                      |                                                                           |                    |                | -15           | +15           |        |

| Power supply <u>3</u> /<br>rejection  | PSR                                  |                                                                           | -55°C to +125°C    | 01             | 90 ty         | /pical        | dB     |

|                                       |                                      |                                                                           |                    |                | 82            |               |        |

| External reference inputs             | section.                             |                                                                           |                    |                |               |               |        |

| Input range,<br>buffered model        |                                      | Minimum differential voltage<br>between VREF+ and VREF− pins<br>is 400 mV | -55°C to +125°C    | 01             | AGND<br>+ 0.1 | AVDD<br>- 0.1 | V      |

| Input range,<br>unbuffered model      |                                      |                                                                           | -55°C to +125°C    | 01             | 0             | AVDD          | V      |

| Input current,                        |                                      | Minimum differential voltage                                              | -55°C to +125°C    | 01             | +10 t         | ypical        | nA     |

| buffered mode                         |                                      | between VREF+ and VREF- pins is 400 mV                                    |                    |                | -20           | +27           |        |

| Input current,<br>unbuffered mode     |                                      |                                                                           | -55°C to +125°C    | 01             | 500 t         | ypical        | nA/V   |

| Normal mode <u>3</u> /<br>rejection   |                                      |                                                                           | -55°C to +125°C    | 01             | 80 ty         | vpical        | dB     |

| Common mode <u>3</u> /<br>rejection   |                                      |                                                                           | -55°C to +125°C    | 01             | 100 t         | ypical        | dB     |

|                                       |                                      |                                                                           |                    |                | 85            |               |        |

| Reference detect <u>3</u> /<br>levels |                                      |                                                                           | -55°C to +125°C    | 01             | 400 t         | ypical        | mV     |

| DLA LAND AND MARITIME | SIZE CODE IDENT NO. |     | DWG NO.   |

|-----------------------|---------------------|-----|-----------|

| COLUMBUS, OHIO        | A 16236             |     | V62/21606 |

|                       |                     | REV | PAGE 8    |

| Test                                   | Test Symbol Conditions <u>2</u> / |                                                                                                        | Temperature,<br>TA              | Device<br>type | Lin            | nits           | Unit   |  |  |  |  |  |     |  |

|----------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------|----------------|----------------|----------------|--------|--|--|--|--|--|-----|--|

|                                        |                                   |                                                                                                        |                                 |                | Min            | Max            |        |  |  |  |  |  |     |  |

| Excitation current source              | s section.                        |                                                                                                        |                                 |                |                |                |        |  |  |  |  |  |     |  |

| Output current                         |                                   | Available from each current source, value programmable from 10 $\mu$ A to 1 mA                         | -55°C to +125°C                 | 01             | 10             | 1000           | μA     |  |  |  |  |  |     |  |

| Initial tolerance                      |                                   | Output current (I <sub>OUT</sub> ) $\ge$ 50 µA                                                         | +25°C                           | 01             | ±5 ty          | pical          | %      |  |  |  |  |  |     |  |

| Drift <u>3</u> /                       |                                   | Using internal reference resistor                                                                      | -55°C to +125°C                 | 01             | 100 t          | ypical         | ppm/°C |  |  |  |  |  |     |  |

|                                        |                                   |                                                                                                        |                                 |                |                | 400            |        |  |  |  |  |  |     |  |

|                                        |                                   | Using external 150 kΩ reference<br>resistor between IREF pin and<br>AGND, and the resistor must have a |                                 |                | 75 ty          | rpical         |        |  |  |  |  |  |     |  |

|                                        |                                   | drift specification of 5 ppm/°C                                                                        |                                 |                |                |                |        |  |  |  |  |  | 400 |  |

| Initial current <u>3</u> /<br>matching |                                   | Matching between both current sources                                                                  | +25°C                           | 01             | ±0.5 t         | ypical         | %      |  |  |  |  |  |     |  |

| Drift matching <u>3</u> /              |                                   |                                                                                                        | -55°C to +125°C                 | 01             | 50 ty          | pical          | ppm/°C |  |  |  |  |  |     |  |

| Load regulation, <u>3</u> /<br>AVDD    |                                   | AVDD = 3.3 V                                                                                           | -55°C to +125°C                 | 01             | 0.2 ty         | /pical         | %/V    |  |  |  |  |  |     |  |

| Output compliance <u>3</u> /           |                                   | IOUT = 10 μA to 210 μA                                                                                 | -55°C to +125°C                 | 01             | AGND<br>- 0.03 | AVDD<br>- 0.85 | V      |  |  |  |  |  |     |  |

|                                        |                                   | IOUT > 210 μA                                                                                          |                                 |                | AGND<br>- 0.03 | AVDD<br>- 1.1  |        |  |  |  |  |  |     |  |

| DAC channel specificatio               | ons section.                      | Load resistance (RL) = 5 k $\Omega$ and load                                                           | capacitance (CL) = <sup>·</sup> | 100 pF         |                |                |        |  |  |  |  |  |     |  |

| Voltage range                          |                                   | Internal reference                                                                                     | -55°C to +125°C                 | 01             | 0              | VREF           | V      |  |  |  |  |  |     |  |

|                                        |                                   | External reference                                                                                     |                                 |                | 0              | 1.8            |        |  |  |  |  |  |     |  |

| DC specifications <u>13</u> /          |                                   |                                                                                                        |                                 |                |                |                |        |  |  |  |  |  |     |  |

| Resolution                             |                                   |                                                                                                        | -55°C to +125°C                 | 01             | 12             |                | Bits   |  |  |  |  |  |     |  |

| Relative accuracy                      |                                   |                                                                                                        | -55°C to +125°C                 | 01             | ±3 ty          | pical          | LSB    |  |  |  |  |  |     |  |

| Differential nonlinearity              |                                   | Guaranteed monotonic                                                                                   | -55°C to +125°C                 | 01             | ±0.5 t         | ypical         | LSB    |  |  |  |  |  |     |  |

|                                        |                                   |                                                                                                        |                                 |                |                | ±1             |        |  |  |  |  |  |     |  |

| Offset error                           | OE                                | 1.2 V internal reference                                                                               | -55°C to +125°C                 | 01             | ±2 ty          | pical          | mV     |  |  |  |  |  |     |  |

|                                        |                                   |                                                                                                        |                                 |                |                | ±10            |        |  |  |  |  |  |     |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/21606</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV            | PAGE 9                   |

| Test                               | Symbol              | Conditions <u>2</u> /                                                                                       | Temperature,<br>TA          | Device<br>type | Lin          | nits    | Unit       |

|------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------|----------------|--------------|---------|------------|

|                                    |                     |                                                                                                             |                             |                | Min          | Max     |            |

| DAC channel specification          | ons section         | - continued. Load resistance (RL) = 5                                                                       | $k\Omega$ and load capacita | nce (CL) =     | 100 pF       |         |            |

| DC specifications - conti          | nued. <u>13</u> /   |                                                                                                             |                             |                |              |         |            |

| Gain error                         |                     | VREF range (reference = 1.2 V)                                                                              | -55°C to +125°C             | 01             |              | ±0.5    | %          |

| NPN mode. <u>3</u> /               | •                   |                                                                                                             |                             |                | 1            |         |            |

| Resolution                         |                     |                                                                                                             | -55°C to +125°C             | 01             | 12           |         | Bits       |

| Relative accuracy                  |                     |                                                                                                             | -55°C to +125°C             | 01             | ±3 ty        | pical   | LSB        |

| Differential nonlinearity          |                     |                                                                                                             | -55°C to +125°C             | 01             | ±0.5 t       | ypical  | LSB        |

| Offset error                       |                     |                                                                                                             | -55°C to +125°C             | 01             | ±0.35        | typical | mA         |

| Gain error                         |                     |                                                                                                             | -55°C to +125°C             | 01             | ±0.75        | typical | mA         |

| Output current range               |                     |                                                                                                             | -55°C to +125°C             | 01             | 0.008        | 23.6    | mA         |

| Interpolation mode.                | <u>3/ 14/</u>       | Only monotonic to 14 bits                                                                                   |                             | I              | 1            | 1       | 1          |

| Resolution                         |                     |                                                                                                             | -55°C to +125°C             | 01             | 14 ty        | vpical  | Bits       |

| Relative accuracy                  |                     | For 14 bits resolution                                                                                      | -55°C to +125°C             | 01             | ±6 typical   |         | LSB        |

| Differential nonlinearity          |                     | Monotonic (14 bits)                                                                                         | -55°C to +125°C             | 01             | ±0.6 typical |         | LSB        |

| Offset error                       |                     | 1.2 V internal reference                                                                                    | -55°C to +125°C             | 01             | ±2 ty        | pical   | mA         |

| Gain error                         |                     | VREF range (reference = 1.2 V)                                                                              | -55°C to +125°C             | 01             | ±1 ty        | pical   | %          |

|                                    |                     | AVDD range                                                                                                  |                             |                | ±1 ty        | pical   |            |

| DAC AC characteristics             | section. <u>3</u> / | 1                                                                                                           |                             |                | 1            |         |            |

| Voltage output settling time       |                     |                                                                                                             | -55°C to +125°C             | 01             | 10 ty        | pical   | μs         |

| Digital to analog glitch<br>energy |                     | 1 LSB change at major carry<br>(maximum number of bits changes<br>simultaneously in the DACDAT<br>register) | -55°C to +125°C             | 01             | ±20 typical  |         | nV-<br>sec |

| Power on reset (POR) se            | ection.             |                                                                                                             |                             | I              | 1            |         | 1          |

| POR trip level                     |                     | Voltage at IOVDD pin, power on levels                                                                       | -55°C to +125°C             | 01             | 1.65 t       | ypical  | V          |

|                                    |                     | Voltage at IOVDD pin,<br>power down levels                                                                  |                             |                | 1.65 t       | ypical  |            |

| Timeout from POR <u>3</u> /        |                     |                                                                                                             | -55°C to +125°C             | 01             | 50 ty        | vpical  | ms         |

# TABLE I. <u>Electrical performance characteristics</u> – Continued. $\underline{1}$ /

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/21606 |

|                       |      | REV            | PAGE 10   |

| Test                          | Symbol            | Conditions <u>2</u> /                                             | Temperature,<br>TA | Device<br>type | Lim            | its            | Unit   |  |        |       |    |

|-------------------------------|-------------------|-------------------------------------------------------------------|--------------------|----------------|----------------|----------------|--------|--|--------|-------|----|

|                               |                   |                                                                   |                    |                | Min            | Max            |        |  |        |       |    |

| Watchdog timer (WDT) s        | section. <u>3</u> |                                                                   |                    |                |                |                |        |  |        |       |    |

| Timeout period                |                   |                                                                   | -55°C to +125°C    | 01             | 0.00003        | 8192           | sec    |  |        |       |    |

| Timeout step size             |                   | Register T3CON,<br>bits[3:2] (PRE) = 10                           | -55°C to +125°C    | 01             | 7.8125         | typical        | ms     |  |        |       |    |

| Flash/EE memory sectio        | n. <u>3</u> /     |                                                                   |                    |                |                |                |        |  |        |       |    |

| Endurance <u>15</u> /         |                   |                                                                   | -40°C to +125°C    | 01             | 10,000         |                | Cycles |  |        |       |    |

| Read                          |                   |                                                                   | -55°C to +125°C    | 01             | 10,000         |                | Cycles |  |        |       |    |

| Write                         |                   |                                                                   | -55°C to -40°C     | 01             | 1000           |                | Cycles |  |        |       |    |

| Data Retention <u>16</u> /    |                   |                                                                   | TJ = +85°C         | 01             | 10             |                | Years  |  |        |       |    |

| Digital inputs section.       |                   | All digital inputs                                                |                    |                |                |                | •      |  |        |       |    |

| Input leakage current.        | Digital inp       | outs except for the $\overline{\text{RESET}}$ , SWCLK, and        | d SWDIO pins       |                |                |                |        |  |        |       |    |

| Logic 1                       |                   | High input voltage (V <sub>INH</sub> ) = IOVDD<br>or VINH = 1.8 V | -55°C to +125°C    | 01             | 140 typical    |                | μΑ     |  |        |       |    |

|                               |                   | Internal pull-up disabled                                         |                    |                | 1 typ          | 1 typical      |        |  |        |       |    |

| Logic 0                       |                   | Low input voltage (VINL) = 0 V                                    | -55°C to +125°C    | 01             | 160 ty         | pical          | μA     |  |        |       |    |

|                               |                   | Internal pull up disabled                                         |                    |                |                |                |        |  | 10 typ | pical | nA |

| Input leakage current.        | ·                 | RESET, SWCLK, and SWDIO pins                                      |                    |                |                |                |        |  |        |       |    |

| Logic 1                       |                   |                                                                   | -55°C to +125°C    | 01             | 140 ty         | pical          | μA     |  |        |       |    |

| Logic 0                       |                   |                                                                   | -55°C to +125°C    | 01             | 160 ty         | pical          | μA     |  |        |       |    |

| Input capacitance <u>3</u> /  | CIN               |                                                                   | -55°C to +125°C    | 01             | 10 typ         | oical          | pF     |  |        |       |    |

| Logic input voltage,<br>low   | VINL              |                                                                   | -55°C to +125°C    | 01             |                | 0.2 x<br>IOVDD | V      |  |        |       |    |

| Logic input voltage,<br>high  | VINH              |                                                                   | -55°C to +125°C    | 01             | 0.7 x<br>IOVDD |                | V      |  |        |       |    |

| Logic output voltage,<br>high | Vон               | Source current (I <sub>SOURCE</sub> ) = 1 mA                      | -55°C to +125°C    | 01             | IOVDD<br>- 0.4 |                | V      |  |        |       |    |

| Logic output voltage, low     | VOL               | Sink current (ISINK) = 1 mA                                       | -55°C to +125°C    | 01             |                | 0.4            | V      |  |        |       |    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/21606 |

|                       |      | REV            | PAGE 11   |

| Test                                                         | Symbol                | Conditions <u>2</u> /                                             | Temperature,<br>TA | Device<br>type | Lim         | its     | Unit               |

|--------------------------------------------------------------|-----------------------|-------------------------------------------------------------------|--------------------|----------------|-------------|---------|--------------------|

|                                                              |                       |                                                                   |                    |                | Min         | Max     |                    |

| Crystal oscillator section.                                  | <u>3</u> /            | 32.768 kHz crystal inputs                                         | ·                  |                |             |         |                    |

| Logic input <u>17</u> /<br>voltage, XTALI only               | VINL                  |                                                                   | -55°C to +125°C    | 01             |             | 0.8     | V                  |

|                                                              | VINH                  |                                                                   |                    |                | 1.7         |         |                    |

| XTALI capacitance                                            |                       |                                                                   | -55°C to +125°C    | 01             | 6 typ       | ical    | pF                 |

| XTALO capacitance                                            |                       |                                                                   | -55°C to +125°C    | 01             | 6 typ       | ical    | pF                 |

| On chip low power oscilla                                    | tor section.          |                                                                   |                    | 1              |             |         | 1                  |

| Oscillator frequency                                         |                       |                                                                   | -55°C to +125°C    | 01             | 32.768      | typical | kHz                |

| Accuracy                                                     | cy -55°C to +125°C 01 |                                                                   | 01                 | ±10 ty         | pical       | %       |                    |

|                                                              |                       |                                                                   |                    |                | -30         | +30     |                    |

| On chip high frequency of                                    | scillator sec         | ction.                                                            | ·                  |                |             |         | •                  |

| Oscillator frequency                                         |                       |                                                                   | -55°C to +125°C    | 01             | 16 typ      | pical   | MHz                |

| Accuracy                                                     |                       |                                                                   | -55°C to +125°C    | 01             | -1.8        | +1.4    | %                  |

| Long term stability <u>9</u> /                               |                       |                                                                   | -55°C to +125°C    | 01             | 0.8 ty      | pical   | °C /<br>1000<br>Hr |

| Processor clock rate <u>3</u> /<br>section                   |                       | Nine programmable core clock<br>selections within specified range | -55°C to +125°C    | 01             | 0.5 typical |         | MHz                |

|                                                              |                       |                                                                   |                    |                | 0.0625      | 16      |                    |

| Using an external clock                                      |                       |                                                                   | -55°C to +125°C    | 01             | 0.032768    | 16      | MHz                |

| Processor start up time se                                   | ection. <u>3</u> /    |                                                                   |                    | •              |             |         |                    |

| At power on                                                  |                       | Includes kernel power on execution time                           | -55°C to +125°C    | 01             | 41 ty       | bical   | ms                 |

| After reset event                                            |                       |                                                                   | -55°C to +125°C    | 01             | 1.44 ty     | vpical  | ms                 |

| From processor power<br>down (mode 1,<br>mode 2, and mode 3) |                       | Clock frequency (fCLK) is the<br>Cortex-M3 core clock             | -55°C to +125°C    | 01             | 3 to 5 t    | ypical  | fCLK               |

| From total halt or<br>hibernate mode<br>(mode 4 or mode 5)   |                       | Clock frequency (fCLK) is the<br>Cortex-M3 core clock             | -55°C to +125°C    | 01             | 30.8 ty     | vpical  | μs                 |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/21606 |

|                       |      | REV            | PAGE 12   |

| Test                                                     | Symbol                                                                                                                           | Conditions <u>2</u> /                                                                       | Temperature,<br>TA | Device<br>type | Lir           | nits   | Unit |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------|----------------|---------------|--------|------|

|                                                          |                                                                                                                                  |                                                                                             |                    |                | Min           | Max    |      |

| Power requirements sec                                   | tion.                                                                                                                            |                                                                                             |                    |                |               |        |      |

| Power supply voltage range                               | VDD                                                                                                                              | AVDD, IOVDD                                                                                 | -55°C to +125°C    | 01             | 1.8           | 3.6    | V    |

| Power consumption.                                       | ·                                                                                                                                |                                                                                             | ·                  |                |               |        |      |

| IDD (microcontroller<br>unit (MCU) active                |                                                                                                                                  | Processor clock rate = 16 MHz,<br>all peripherals on (CLKSYSDIV = 0)-55°C to +125°C015.5 ty |                    | ypical         | mA            |        |      |

| mode <u>18</u> / <u>19</u> /                             |                                                                                                                                  | Processor clock rate = 8 MHz,<br>all peripherals on (CLKSYSDIV = 1)                         |                    |                | 3 typical     |        |      |

|                                                          | Processor clock rate = 500 kHz,<br>both ADCs on (input buffers off )<br>with PGA gain = 4, 1 × SPI port on,<br>and all timers on |                                                                                             |                    | 1 typical      |               |        |      |

| IDD (MCU powered down)                                   |                                                                                                                                  | Total halt mode (mode 4)                                                                    | -55°C to +125°C    | 01             | 4 ty          | pical  | μA   |

| IDD, total (ADC0) <u>19</u> /                            |                                                                                                                                  | PGA enabled, gain $\ge$ 32                                                                  | -55°C to +125°C    | 01             | 320 t         | ypical | μA   |

| PGA                                                      |                                                                                                                                  | Gain = 4, 8, or 16, PGA only                                                                | -55°C to +125°C    | 01             | 130 t         | ypical | μA   |

|                                                          |                                                                                                                                  | Gain = 32, 64, 0r 128, PGA only                                                             |                    |                | 180 typical   |        |      |

| Input buffers                                            |                                                                                                                                  | 2 x input buffers = 70 μA                                                                   | -55°C to +125°C    | 01             | 01 70 typical |        | μA   |

| Digital interface and modulator                          |                                                                                                                                  |                                                                                             | /pical             | μA             |               |        |      |