One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### ADuCM410/ADuCM420 Reference Manual

#### **SCOPE**

This manual provides a detailed description of the ADuCM410 and ADuCM420 functionality and features.

#### **DISCLAIMER**

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. See the ADuCM410 and ADuCM420 data sheets for the functional block diagrams.

## **TABLE OF CONTENTS**

| Scope 1                                                                               |

|---------------------------------------------------------------------------------------|

| Disclaimer                                                                            |

| Revision History 4                                                                    |

| Using the ADuCM410/ADuCM420 Reference Manual 5                                        |

| Introduction to the ADuCM410 and ADuCM4206                                            |

| Main Features of the ADuCM410 and ADuCM4207                                           |

| Clocking Architecture                                                                 |

| Clocking Architecture Operation: Switching Clock Settings When PLL Clock Is Included8 |

| PLL Interrupt9                                                                        |

| Register Summary: Clock Gating and Other Settings (Clock)                             |

|                                                                                       |

| Register Details: Clock Gating and Other Settings (Clock) . 10                        |

| Power Management Unit                                                                 |

| Power Management Unit Features                                                        |

| Power Management Unit Overview                                                        |

| Power Management Unit Operation                                                       |

| Register Summary: Power Management Unit 14                                            |

| Register Details: Power Management Unit                                               |

| Arm Cortex-M33 Processor                                                              |

| Arm Cortex-M33 Processor Features                                                     |

| Arm Cortex-M33 Processor Overview 15                                                  |

| Arm Cortex-M33 Processor Operation                                                    |

| Arm Cortex-M33 Processor Related Documents16                                          |

| System Exceptions and Peripheral Interrupts17                                         |

| Cortex-M33 and Fault Management17                                                     |

| External Interrupt Configuration21                                                    |

| Register Summary: External Interrupts                                                 |

| Register Details: External Interrupts                                                 |

| Reset                                                                                 |

| Reset Features                                                                        |

| Reset Operation                                                                       |

| Register Summary: Reset                                                               |

| Register Details: Reset25                                                             |

| Analog Pin Functionality26                                                            |

| ADC Circuit                                                                           |

| ADC Circuit Features27                                                                |

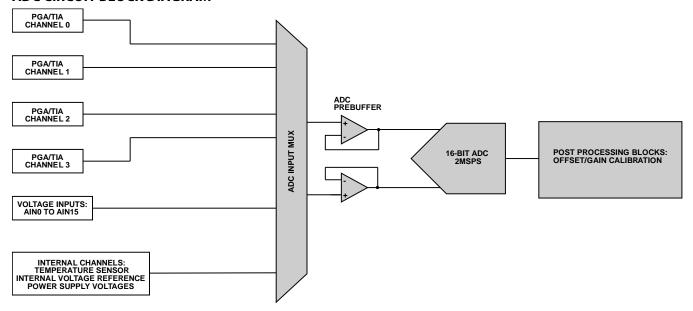

| ADC Circuit Block Diagram27                                                           |

| ADC Circuit Overview28                                                                |

| ADC Circuit Operation                                                                 |

|    | ADC Chainlet Sequencer                                                                                                     | 20 |

|----|----------------------------------------------------------------------------------------------------------------------------|----|

|    | ADC Transfer Function                                                                                                      | 29 |

|    | ADC Oversampling and Output Data Rate                                                                                      | 30 |

|    | Digital Comparators Overview                                                                                               | 30 |

|    | PGA/TIA Input Amplifier (ADuCM410 Only)                                                                                    | 30 |

|    | Temperature Sensor Channel                                                                                                 | 33 |

|    | Other Internal Channels                                                                                                    | 34 |

|    | ADC Calibration                                                                                                            | 34 |

|    | ADC Interrupts                                                                                                             | 34 |

|    | ADC Power-Up Requirements                                                                                                  | 35 |

|    | Register Summaries: ADC Control, ADC Voltage<br>Programmable Gain Amplifier (PGA), and ADC<br>Temperature Sensor Registers | 37 |

|    | Register Details ADC Control, ADC Voltage Programmabl<br>Gain Amplifier (PGA), and ADC Temperature Sensor<br>Registers     |    |

| 7. | oltage References                                                                                                          |    |

| ,  | External ADC Reference Details                                                                                             |    |

| ۱  | nalog Comparators                                                                                                          |    |

| •  | Analog Comparators Features                                                                                                |    |

|    | Analog Comparator Overview                                                                                                 |    |

|    | Analog Comparator Operation                                                                                                |    |

|    | Register Summary: Analog Comparators                                                                                       |    |

|    | Register Details: Analog Comparators                                                                                       |    |

| 7  | DACS                                                                                                                       |    |

|    | DAC Features                                                                                                               |    |

|    | DAC Overview                                                                                                               | 61 |

|    | DAC Operation                                                                                                              | 61 |

|    | DAC to Bias Comparator or TIA                                                                                              |    |

|    | VDAC Power-Up Requirements                                                                                                 |    |

|    | Register Summary: DAC                                                                                                      |    |

|    | Register Details: DAC                                                                                                      | 63 |

| 7] | ash Controller                                                                                                             | 64 |

|    | Flash Controller Features                                                                                                  | 64 |

|    | Flash Controller Overview                                                                                                  | 65 |

|    | Flash Protection and Integrity                                                                                             | 67 |

|    | Flash Controller Performance and Command Duration                                                                          | 69 |

|    | Flash Erase/Program Requirements                                                                                           | 69 |

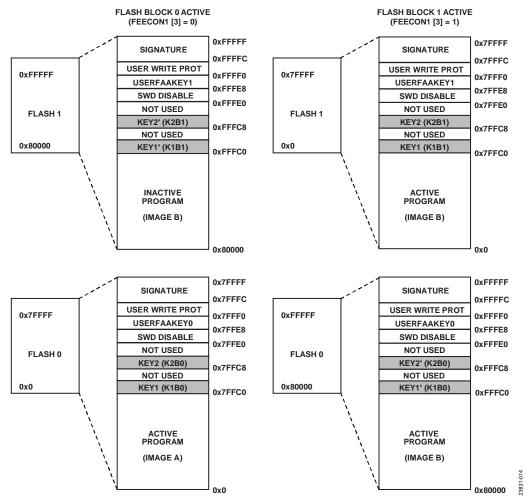

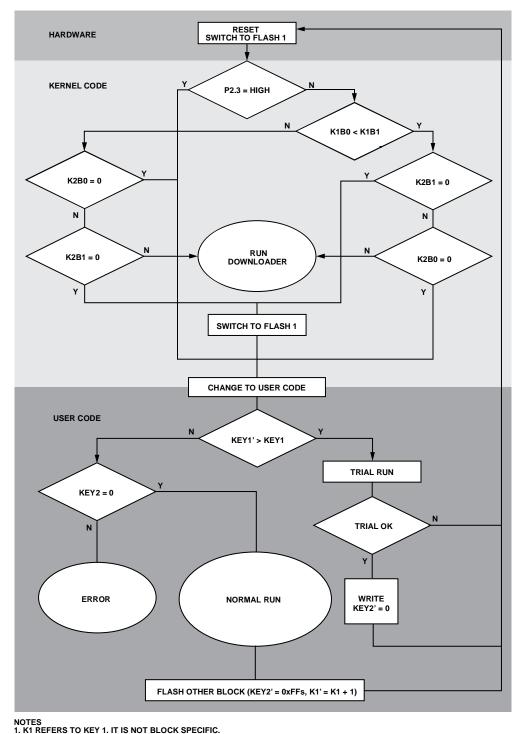

|    | Flash Block Switching                                                                                                      | 69 |

|    | Register Summary: Flash Controller (Flash)                                                                                 | 74 |

|    | Register Details: Flash Controller (Flash)                                                                                 | 75 |

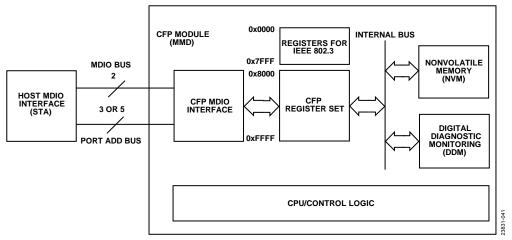

| Static Random Access Memory (SRAM)84                                   | MDIO Overview                                         | 140 |

|------------------------------------------------------------------------|-------------------------------------------------------|-----|

| SRAM Features84                                                        | MDIO Operation                                        | 140 |

| SRAM Configuration: Instruction SRAM vs. Data SRAM84                   | Register Summary: MDIO Interface                      | 143 |

| ECC Protection85                                                       | Register Details: MDIO Interface                      | 143 |

| Initialization in Cache and Instruction SRAM85                         | Digital Inputs/Outputs                                | 147 |

| Register Summary: SRAM Controller (SRAM)85                             | Digital Inputs/Outputs Features                       | 147 |

| Register Details: SRAM Controller (SRAM)86                             | Digital Inputs/Outputs Block Diagram                  | 147 |

| Cache                                                                  | Digital Inputs/Outputs Overview                       | 147 |

| Cache Programming Model89                                              | Digital Inputs/Outputs Operation                      | 147 |

| Programming Guidelines89                                               | Interrupts                                            | 149 |

| Register Summary: Cache Controller89                                   | Digital Port Multiplex                                | 150 |

| Register Details: Cache Controller89                                   | Register Summary: Digital Input/Output                | 152 |

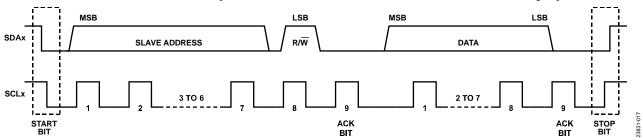

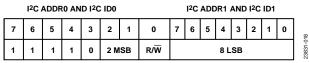

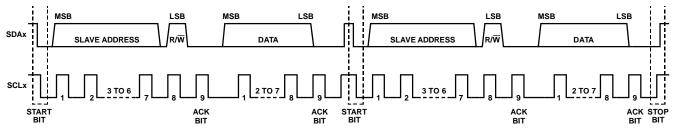

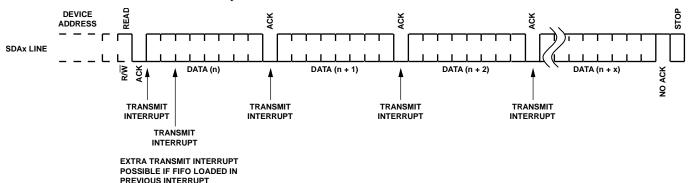

| I <sup>2</sup> C Serial Interfaces91                                   | Register Details: Digital Input/Output                | 154 |

| I <sup>2</sup> C Features91                                            | General-Purpose Timers (16-Bit)                       | 161 |

| I <sup>2</sup> C Overview91                                            | Timer Features and Overview                           | 161 |

| I <sup>2</sup> C Operation91                                           | General-Purpose Timers Operation                      | 161 |

| I <sup>2</sup> C Operating Modes93                                     | Register Summary: General-Purpose Timers              | 162 |

| Register Summaries: I <sup>2</sup> C Master/Slave I2C0, I2C1, and I2C2 | Register Details: General-Purpose Timers              | 163 |

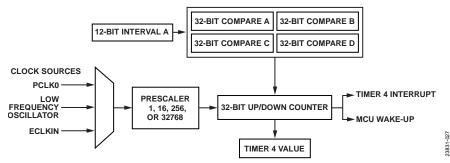

| 97                                                                     | General-Purpose Timers (32-Bit)                       | 165 |

| Register Details: I <sup>2</sup> C Master/Slave I2C0, I2C1, and I2C299 | Timer Compare Feature                                 |     |

| UART Serial Interface                                                  | Timer Capture Feature                                 |     |

| UART Features                                                          | Register Summaries: 32-Bit Timer 0 and 32-Bit Timer 1 |     |

| UART Overview111                                                       | Register Details: 32-Bit Timer 0 and 32-Bit Timer 1   |     |

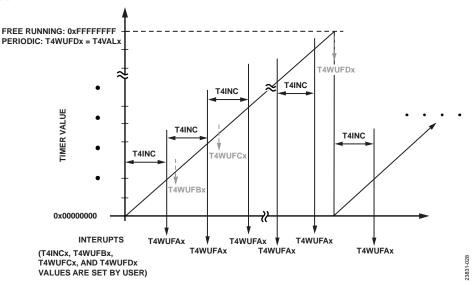

| UART Operation111                                                      | Wake-Up Timer                                         |     |

| Register Summary: UART0, UART1115                                      | Wake-Up Timer Features                                |     |

| Register Details: UART0, UART1116                                      | Wake-Up Timer Block Diagram                           |     |

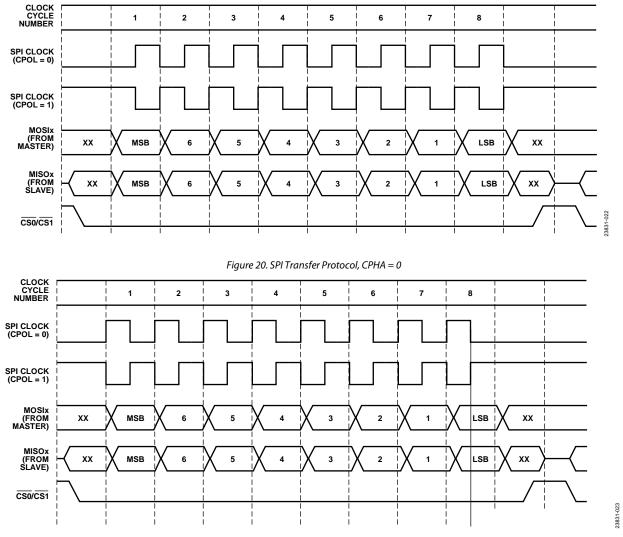

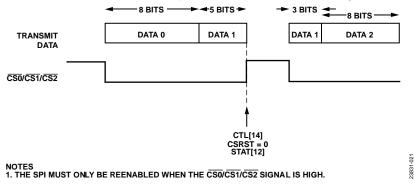

| Serial Peripheral Interfaces                                           | Wake-Up Timer Overview                                |     |

| SPI Features                                                           | Wake-Up Timer Operation                               |     |

| SPI Overview                                                           | Register Summary: WUT                                 |     |

| SPI Operation                                                          | Register Details: WUT                                 |     |

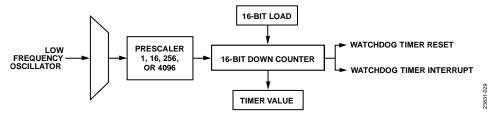

| SPI Transfer Initiation                                                | Watchdog Timer                                        |     |

| SPI Interrupts                                                         | Watch Dog Timer Features                              |     |

| SPI Wire-OR'ed Mode (WOM)128                                           | Watchdog Timer Block Diagram                          |     |

| SPI CSERR Condition                                                    | Watch Dog Timer Operation                             |     |

| SPI DMA128                                                             | Windowed Watchdog Feature                             |     |

| SPI and Power-Down Modes129                                            | Interrupt Mode                                        |     |

| Register Summary: Serial Peripheral Interface (SPI0, SPI1, SPI2)130    | Register Summary: Watchdog Timer Register Map (WD     | T)  |

| Register Details: Serial Peripheral Interface (SPI0, SPI1, SPI2)       | Register Details: Watchdog Timer Register Map (WDT)   | 177 |

| MDIO140                                                                | Direct Memory Access (DMA) Controller                 | 179 |

|                                                                        | DMA Features                                          | 179 |

## UG-1807

## ADuCM410/ADuCM420 Hardware Reference Manual

| DMA Overview                                | Downloader                               | 208 |

|---------------------------------------------|------------------------------------------|-----|

| DMA Operation                               | I <sup>2</sup> C Downloader              | 208 |

| DMA Interrupts180                           | MDIO Downloader                          | 208 |

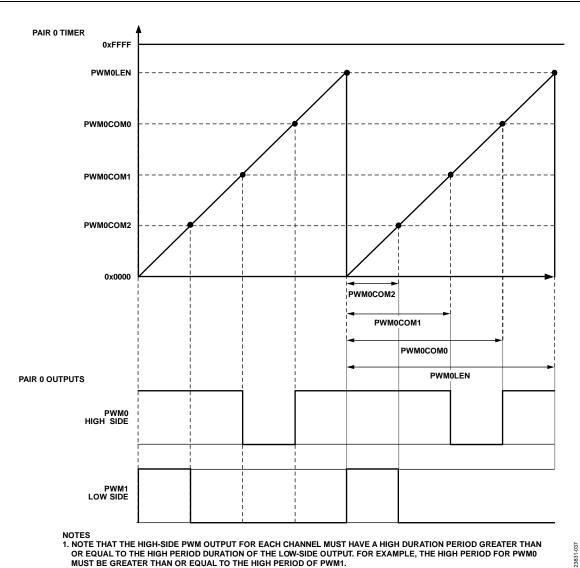

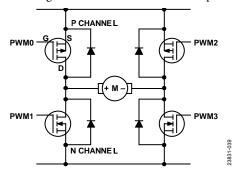

| DMA Priority180                             | Pulse Width Modulator (PWM)              | 209 |

| Channel Control Data Structure              | PWM Features                             | 209 |

| Control Data Configuration181               | PWM Overview                             | 209 |

| DMA Transfer Types (CHNL_CFG, Bits[2:0])183 | PWM Operation                            | 209 |

| Address Calculation                         | PWM Interrupt Generation                 | 212 |

| PLA Trigger Channel                         | Register Summary: PWM                    | 213 |

| Aborting DMA Transfers186                   | Register Details: PWM                    | 213 |

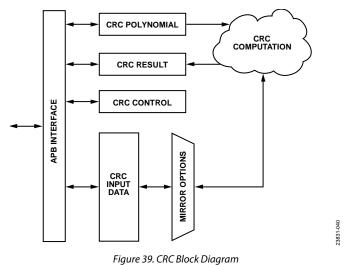

| Flash DMA Channel                           | Cyclic Redundancy Check                  | 218 |

| Register Summary: DMA187                    | CRC Features                             | 218 |

| Register Summary: DMA Request187            | CRC Functional Description               | 218 |

| Register Details: DMA188                    | CRC Data Transfer                        | 221 |

| Register Details: DMA Request               | CRC Programming Model                    | 221 |

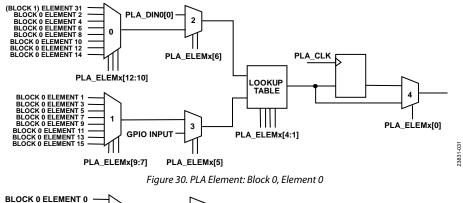

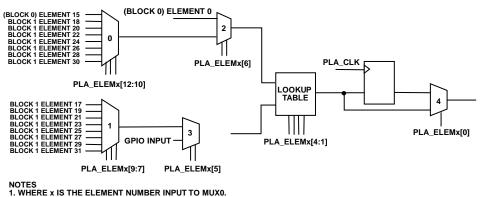

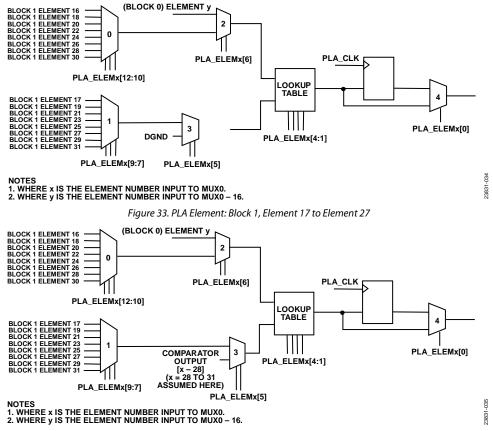

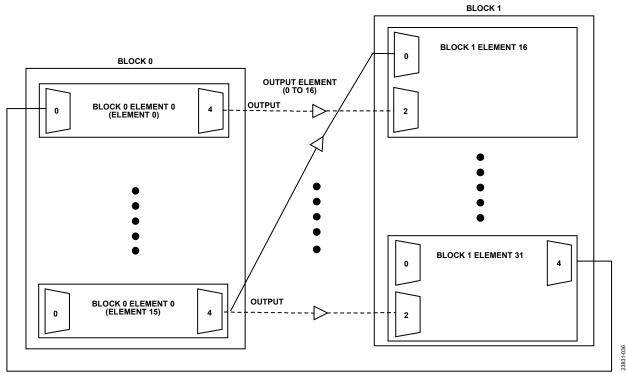

| Programmable Logic Array (PLA)198           | Register Summary: CRC                    | 222 |

| PLA Features                                | Register Details: CRC                    | 222 |

| PLA Overview198                             | Silicon Identification                   | 224 |

| PLA Operation200                            | Register Summary: Silicon Identification | 225 |

| Register Summary: PLA                       | Register Details: Silicon Identification | 225 |

| Register Details: PLA202                    |                                          |     |

### **REVISION HISTORY**

1/2021—Revision 0: Initial Version

## **USING THE ADUCM410/ADUCM420 REFERENCE MANUAL**

#### **Table 1. Number Notations**

| Notation | Description                                                                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------|

| Bit N    | Bits are numbered in little endian format, where the least significant bit of a number is referred to as Bit 0. |

| V[x:y]   | A range from Bit x to Bit y of a value or a field (V) is represented in bit field format V[x:y].                |

| 0xNN     | Hexadecimal (Base 16) numbers are preceded by the 0x prefix.                                                    |

| 0bNN     | Binary (Base 2) numbers are preceded by the 0b prefix.                                                          |

### **Table 2. Register Access Conventions**

| Mode  | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| R/W   | Memory location has read and write access.                                                |

| RC    | Memory location is cleared after reading it.                                              |

| R     | Memory location is read access only. A read always returns 0, unless otherwise specified. |

| W     | Memory location is write access only.                                                     |

| R/W1C | Memory location has read access. To clear to 0, write 1 once to the memory location       |

Memory mapped register (MMR) bits that are not documented are reserved. When writing to MMRs with reserved bits, the reserved bits must be written with the value in the reset column of the relevant MMR description, unless otherwise specified.

## INTRODUCTION TO THE ADUCM410 AND ADUCM420

The ADuCM410 and ADuCM420 are fully integrated, single package devices that include high performance analog peripherals together with digital peripherals (controlled by a 160 MHz Arm® Cortex®-M33 processor) and integrated flash for code and data.

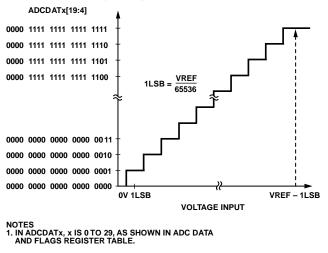

The analog-to-digital converter (ADC) on the devices provides 16-bit (ADuCM410) and 12-bit (ADuCM420), 2 MSPS data acquisition using up to 16 input pins that can be programmed for single-ended or differential operation with a programmable gain amplifier (PGA) or transimpedance amplifier (TIA) for voltage and current measurements. Additionally, the die temperature and supply voltages can be measured.

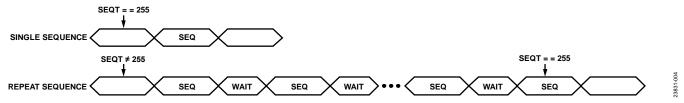

The ADC input voltage is 0 V to VREF. A sequencer is provided that allows a user to select a set of ADC channels to be measured in sequence without software involvement during the sequence. The sequence can optionally repeat automatically at a user-selectable rate.

Up to 12 channels of 12-bit voltage digital-to-analog converters (VDACs) are provided with output buffers supported.

The ADuCM410 and ADuCM420 can be configured so that the digital and analog outputs retain their output voltages through a watchdog or software reset sequence. Therefore, a product can remain functional even while the ADuCM410 or ADuCM420 is resetting itself.

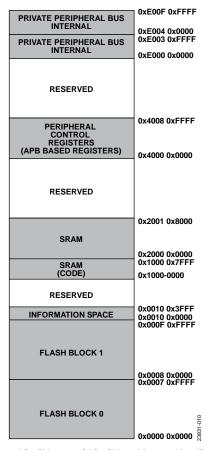

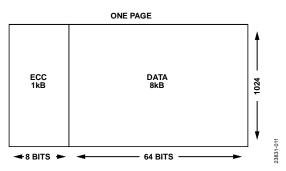

The ADuCM410 and ADuCM420 have a low power Arm Cortex-M33 processor and a 32-bit reduced instruction set computer (RISC) machine that offers up to 240 million instructions per second (MIPS) peak performance with a floating-point unit (FPU). Also integrated are 2×512 kB Flash/EE memories and 128 kB static random access memory (SRAM)—both with single-error correction (SEC) and double error detection (DED) error checking and correction (ECC). The flash comprises two separate 512 kB blocks supporting execution from one flash block and simultaneous writing and/or erasing of the other flash block.

The ADuCM410 and ADuCM420 operate from an on-chip oscillator and have a phase-locked loop (PLL) of 160 MHz. This clock can optionally be divided down to reduce current consumption. Additional low power modes can be set via the ADuCM410 and ADuCM420 software.

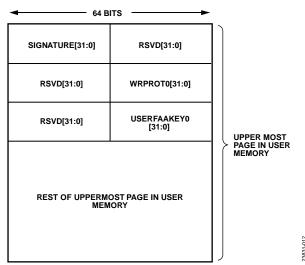

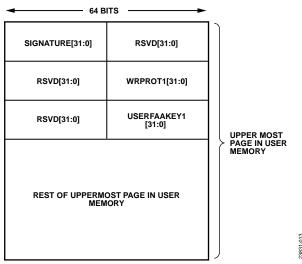

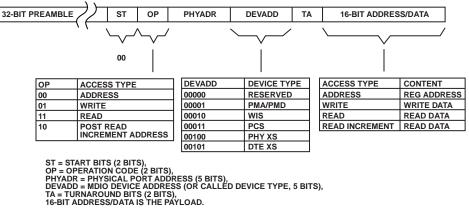

The device includes a management data input/output (MDIO) interface capable of operating up to 10 MHz. User programming is eased by incorporating physical address (PHYADR) and device address (DEVADD) hardware comparators. The nonerasable kernel code combined with flags in user flash allow user code to reliably switch between the two hardware independent flash blocks.

The ADuCM410 and ADuCM420 integrate a range of on-chip peripherals that can be configured under software control, as required in the application. These peripherals include two universal asynchronous receiver transmitters (UARTs), three I²C and three serial peripheral interface (SPI) serial input/output communication controllers, general-purpose inputs/outputs (GPIOs), a 32-element programmable logic array (PLA), five general-purpose timers, a wake-up timer (WUT), and a system watchdog timer (WDT). A 16-bit pulse-width modulation (PWM) with eight output channels is also provided.

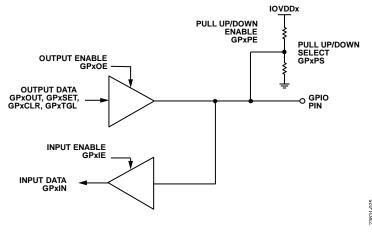

The GPIO pins (Px.x) power up in high impedance input mode. In output mode, the software chooses between open-drain mode and push/pull mode. The pull-up and pull-down resistors can be disabled and enabled in the software. The GPIO pins can be configured with different voltage levels according to the IOVDDx pin, such as 3.3 V, 1.8 V, and 1.2 V. In GPIO output mode, the inputs can remain enabled to monitor the GPIO pins. The GPIO pins can also be programmed to handle digital or analog peripheral signals, in which case, the pin characteristics are matched to the specific requirement.

A large support ecosystem is available for the Arm Cortex-M33 processor to ease product development of the ADuCM410 and ADuCM420. Access is via the Arm serial wire debug port. On-chip factory firmware supports in-circuit serial download via MDIO or  $I^2$ C. These features are incorporated into a low cost, quick start development system supporting this precision analog microcontroller.

Note that throughout this user guide, multifunction pins, such as P2.3/BM/PLAI10, are referred to either by the entire pin name or by a single function of the pin, for example, P2.3, when only that function is relevant.

#### MAIN FEATURES OF THE ADUCM410 AND ADUCM420

The analog-to-digital converter (ADC) includes the following features:

- Multichannel, 16-bit, 2 MSPS SAR ADC with 16-bit no missing codes (ADuCM410) or 12-bit no missing codes (ADuCM420)

- Low drift, on-chip voltage reference

- Voltage and current input measurements supported, including PGA with programmable gain setting (ADuCM410) and TIAs with programmable gain resistors (ADuCM410)

The digital-to-analog converters (DACs) include the following features:

- 12 VDACs that are 12-bit monotonic

- Low drift, on-chip 2.5 V voltage reference source with two buffered reference outputs

The ADuCM410 and ADuCM420 include four comparators with configurable hysteresis levels.

The ADuCM410 and ADuCM420 contain the following communication features:

- Two UART channels with industry-standard, 16450 UART peripheral and support for direct memory access (DMA).

- Three I<sup>2</sup>C channels with 2-byte transmit and receive first in, first out (FIFO) buffers for the master and slave, support for DMA, an automatic clock stretching option, and support for 3.4 Mbps, 1 Mbps, 400 kbps, and 100 kbps.

- Three SPIs with master or slave mode, separate 4-byte receive and transmit FIFOs, and receive and transmit DMA channels

- MDIO slave at up to 10 Mbps

- 16-bit, 8-channel PWM

- 12 GPIO pins with configurable input/output (I/O) level (3.3 V or 1.8V)

The processor operates using the following:

- Arm Cortex-M33 processor operating from an internal 160 MHz system clock

- 1 MB Flash/EE memory, 128 kB SRAM (ADuCM410) or 512 kB Flash/EE memory, 64 kB SRAM (ADuCM420)

- In-circuit download and debug via serial wire

- On-chip I<sup>2</sup>C or MDIO download capability

The on-chip peripherals include the following:

- Five general-purpose timers

- Wake-up timer

- Watchdog timer

- 32-element PLA

The ADuCM410 and ADuCM420 are packaged in a 5 mm  $\times$  5 mm, 81-ball CSP\_BGA package and 3.46 mm  $\times$  3.46 mm 64-ball WLCSP. The temperature range is  $-40^{\circ}$ C to  $+105^{\circ}$ C.

The ADuCM410 and ADuCM420 offer a low cost development system and third-party compiler and emulator tool support. The devices can be used in optical networking applications, such as 100 Gbps, 200 Gbps, and 400 Gbps optical transceivers.

### **CLOCKING ARCHITECTURE**

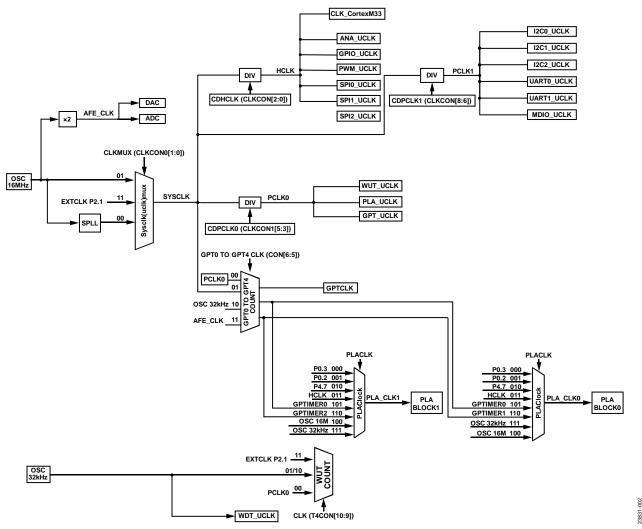

Figure 1. Clock Architecture Overview

#### **CLOCKING ARCHITECTURE OPERATION: SWITCHING CLOCK SETTINGS WHEN PLL CLOCK IS INCLUDED**

When the PLL is the source clock for any ADuCM410 and ADuCM420 block, follow these steps to change the clock divide ratio:  $\frac{1}{2} \frac{1}{2} \frac$

- 1. Set the internal oscillator as the source clock.

- 2. Configure the required clock divide coefficient.

- 3. Set PLL as the root clock again.

#### **PLL INTERRUPT**

Analog Devices recommends the user always enable the PLL interrupt source for the unlikely event that a PLL loss of lock error occurs. If the PLL loses lock, the risk of a system error is high, which may result in a hard fault or bus fault exception occurring.

The ADuCM410 and ADuCM420 PLL interrupt source triggers on the loss of lock. In this interrupt handler function, Analog Devices recommends first switching the system clock to the internal oscillator source. Then user code can recover as required, possibly via a software reset or alerting a host to a hardware error on the ADuCM410 and ADuCM420.

After a reset, the internal kernel program enables and selects the kernel as the high speed system clock (HCLK) source. Therefore, the first read of the CLKSTAT0 register likely shows both the SPLLUNLOCK and SPLLLOCK bits set. Before enabling the PLL interrupt source, clear these bits by writing 1 to the SPLLUNLOCKCLR and SPLLLOCKCLR bits of CLKSTAT0.

The following is example code to enable the PLL interrupts, and shows an example interrupt service routine:

```

pADI_CLK->CLKCON0 |=

BITM_CLOCK_CLKCON0_SPLLIE;

// Enable PLL interrupts

NVIC_EnableIRQ(PLL_IRQn);

// Enable PLL detection interrupt

void PLL_Int_Handler()

uint32_t ulPLLSTA = 0;

ulplLSTA = pADI_CLK->CLKSTAT0;

if ((ulplLSTA & BITM_CLOCK_CLKSTAT0_SPLLUNLOCK)

== BITM_CLOCK_CLKSTAT0_SPLLUNLOCK)

// PLL loss of lock error detected

// Change CPU clock source to Internal Oscillator

pADI_CLK->CLKCON0 &= 0xFFFC;

// Return to internal oscillator - PLL unstable

ucPLLLoss = 1;

// Set flag to indicate loss of PLL Lock error

if ((ulplLSTA & BITM_CLOCK_CLKSTATO_SPLLLOCK)

== BITM_CLOCK_CLKSTATO_SPLLLOCK)

// PLL lock detected

// Change CPU clock source to PLL - PLL is stable

pADI_CLK->CLKCON0 &= 0xFFFC;

pADI_CLK->CLKCON0 |= 0x1;

// PLL is stable

ucPLLLoss = 0;

// Set flag to indicate loss of PLL Lock error

pADI_CLK->CLKSTAT0 |=

// Clear PLL Lock/Unlock detection flags

BITM_CLOCK_CLKSTATO_SPLLLOCKCLR |

BITM_CLOCK_CLKSTAT0_SPLLUNLOCKCLR;

```

### **REGISTER SUMMARY: CLOCK GATING AND OTHER SETTINGS (CLOCK)**

**Table 3. Clock Register Summary**

| Address    | Name     | Description                            | Reset  | Access |

|------------|----------|----------------------------------------|--------|--------|

| 0x40060000 | CLKCON0  | Miscellaneous Clock Settings Register. | 0x043D | R/W    |

| 0x40060004 | CLKCON1  | Clock Dividers Register.               | 0x0048 | R/W    |

| 0x40060008 | CLKSTAT0 | Clock Status Register.                 | 0x0019 | R/W    |

### REGISTER DETAILS: CLOCK GATING AND OTHER SETTINGS (CLOCK)

### Miscellaneous Clock Settings Register

Address: 0x40060000, Reset: 0x043D, Name: CLKCON0

CLKCON0 is used to configure clock sources used by various blocks such as the core and memories as well as peripherals. All unused bits are read only, returning a value of 0.

Table 4. Bit Descriptions for CLKCON0

| Bits    | Bit Name      | Settings | Description                                                                                                                                             | Reset | Access |

|---------|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:12] | RESERVED      |          | Reserved.                                                                                                                                               | 0x0   | R      |

| [11:10] | ANAROOTCLKMUX |          | Clock Mux Select for ADC and DAC Blocks.                                                                                                                | 0x1   | R/W    |

|         |               | 00       | Reserved.                                                                                                                                               |       |        |

|         |               | 01       | 32 MHz Oscillator Clock. Only option allowed.                                                                                                           |       |        |

|         |               | 10       | Reserved.                                                                                                                                               |       |        |

|         |               | 11       | Reserved.                                                                                                                                               |       |        |

| 9       | SPLLIE        |          | PLL Unlock and Lock Interrupt Enable. If this bit is enabled, an interrupt is generated if the PLL transits from lock to unlock or from unlock to lock. | 0x0   | R/W    |

|         |               | 0        | PLL Interrupt Is Not Generated.                                                                                                                         |       |        |

|         |               | 1        | PLL Interrupt Is Generated.                                                                                                                             |       |        |

| [8:6]   | RESERVED      |          | Reserved.                                                                                                                                               | 0x0   | R/W    |

| [5:2]   | CLKOUT        |          | GPIO Clock Output Select. Used to select which clock is output on GPIO pin (P2.2). Implemented as a 16 to 1 mux.                                        | 0xF   | R/W    |

|         |               | 0000     | 16 MHz Internal High Frequency Oscillator.                                                                                                              |       |        |

|         |               | 0001     | HCLK                                                                                                                                                    |       |        |

|         |               | 0010     | Reserved.                                                                                                                                               |       |        |

|         |               | 0011     | 32 kHz Internal Oscillator                                                                                                                              |       |        |

|         |               | 0100     | HCLK                                                                                                                                                    |       |        |

|         |               | 0101     | Peripheral Clock 0 (PCLK0).                                                                                                                             |       |        |

|         |               | 0110     | Peripheral Clock 1 (PCLK1).                                                                                                                             |       |        |

|         |               | 0111     | Reserved.                                                                                                                                               |       |        |

|         |               | 1000     | Reserved.                                                                                                                                               |       |        |

|         |               | 1001     | Timer 0 Clock.                                                                                                                                          |       |        |

|         |               | 1010     | Wake-Up Timer Clock.                                                                                                                                    |       |        |

|         |               | 1011     | Timer 3 Clock.                                                                                                                                          |       |        |

|         |               | 1100     | HCLK.                                                                                                                                                   |       |        |

|         |               | 1101     | SPLL Clock.                                                                                                                                             |       |        |

|         |               | 1110,    | Reserved                                                                                                                                                |       |        |

|         |               | 1111     |                                                                                                                                                         |       |        |

| [1:0]   | CLKMUX        |          | Clock Mux Select. Determines HCLK clock source.                                                                                                         | 0x1   | R/W    |

|         |               | 00       | High Frequency Internal Oscillator.                                                                                                                     |       |        |

|         |               | 01       | System PLL is Selected (160 MHz).                                                                                                                       |       |        |

|         |               | 10       | Reserved.                                                                                                                                               |       |        |

|         |               | 11       | External GPIO Port is Selected (ECLKIN on P2.1).                                                                                                        |       |        |

### **Clock Dividers Register**

#### Address: 0x40060004, Reset: 0x0048, Name: CLKCON1

CLKCON1 is used to set the divide rates for the universal clock (UCLK) and PCLK0/PCLK1. This register can be written at any time. All unused bits are read only, returning a value of 0. Writing unused bits has no effect.

Analog Devices only guarantees operation for clock divider settings of  $\div 1$ ,  $\div 2$ ,  $\div 4$ , and  $\div 8$ .

Table 5. Bit Descriptions for CLKCON1

| Bits   | Bit Name | Settings | Description                                                                                  | Reset | Access |

|--------|----------|----------|----------------------------------------------------------------------------------------------|-------|--------|

| [15:9] | RESERVED |          | Reserved.                                                                                    | 0x00  | R      |

| [8:6]  | CDPCLK1  |          | PCLK1 Divide Bits. PCLK1 must be ≤HCLK.                                                      | 0x1   | R/W    |

|        |          | 000      | Divide by 1 (PCLK1 is Equal to Root Clock).                                                  |       |        |

|        |          | 001      | Divide by 2 (PCLK1 is Half the Frequency of Root Clock).                                     |       |        |

|        |          | 010      | Divide by 4 (PCLK1 is Quarter the Frequency of Root Clock, 40 MHz).                          |       |        |

|        |          | 011      | Divide by 8.                                                                                 |       |        |

|        |          | 100      | Divide by 16. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 101      | Divide by 32. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 110      | Divide by 64. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 111      | Divide by 128. Reserved. Analog Devices has not characterized for this clock divide setting. |       |        |

| [5:3]  | CDPCLK0  |          | PCLK0 Divide Bits. PCLK0 must be ≤HCLK.                                                      | 0x1   | R/W    |

|        |          | 000      | Divide by 1 (PCLK0 is Equal to Root Clock).                                                  |       |        |

|        |          | 001      | Divide by 2 (PCLK0 is Half the Frequency of Root Clock).                                     |       |        |

|        |          | 010      | Divide by 4 (PCLK0 is Quarter the Frequency of Root Clock, 40 MHz).                          |       |        |

|        |          | 011      | Divide by 8.                                                                                 |       |        |

|        |          | 100      | Divide by 16. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 101      | Divide by 32. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 110      | Divide by 64. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 111      | Divide by 128. Reserved. Analog Devices has not characterized for this clock divide setting. |       |        |

| [2:0]  | CDHCLK   |          | HCLK Divide Bits. HCLK must be ≥PCLKx.                                                       | 0x0   | R/W    |

|        |          | 000      | Divide by 1 (HCLK is Equal to Root Clock).                                                   |       |        |

|        |          | 001      | Divide by 2 (HCLK is Half the Frequency of Root Clock).                                      |       |        |

|        |          | 010      | Divide by 4 (HCLK is Quarter the Frequency of Root Clock).                                   |       |        |

|        |          | 011      | Divide by 8.                                                                                 |       |        |

|        |          | 100      | Divide by 16. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 101      | Divide by 32. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 110      | Divide by 64. Reserved. Analog Devices has not characterized for this clock divide setting.  |       |        |

|        |          | 111      | Divide by 128. Reserved. Analog Devices has not characterized for this clock divide setting. |       |        |

### **Clock Status Register**

Address: 0x40060008, Reset: 0x0019, Name: CLKSTAT0

CLKSTAT0 is used to monitor the PLL and oscillator status. With interrupts enabled, the user is free to run initialization code or idle the core while clock components stabilize.

Table 6. Bit Descriptions for CLKSTAT0

| Bits   | Bit Name      | Settings | Description                                                                                                                                                                                                                                     | Reset | Access |

|--------|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:5] | RESERVED      |          | Reserved.                                                                                                                                                                                                                                       | 0x0   | R      |

| 4      | SPLLUNLOCK    |          | System PLL Unlock Flag.                                                                                                                                                                                                                         | 0x1   | R      |

|        |               | 0        | No PLL Unlock Event Was Detected.                                                                                                                                                                                                               |       |        |

|        |               | 1        | A PLL Unlock Event Was Detected. Cleared by writing a 1 to SPLLUNLOCKCLR.                                                                                                                                                                       |       |        |

| 3      | SPLLLOCK      |          | System PLL Lock Flag.                                                                                                                                                                                                                           | 0x1   | R      |

|        |               | 0        | No PLL Lock Event Was Detected.                                                                                                                                                                                                                 |       |        |

|        |               | 1        | A PLL Lock Event Was Detected. Cleared by writing a 1 to SPLLLOCKCLR.                                                                                                                                                                           |       |        |

| 2      | SPLLUNLOCKCLR |          | System PLL Unlock. Writing a 1 to this bit clears the SPLLUNLOCK bit.                                                                                                                                                                           | 0x0   | R/W    |

| 1      | SPLLLOCKCLR   |          | System PLL Lock. Writing a 1 to this bit clears sticky status and SPLLOCK status bit.                                                                                                                                                           | 0x0   | R/W    |

| 0      | SPLLSTATUS    |          | System PLL Status. Indicates the current status of the PLL. Initially, the system PLL is unlocked. After a stabilization period, the PLL locks and is ready for use as the system clock source. This is a read only bit. A write has no effect. | 0x1   | R      |

|        |               | 0        | The PLL Is Not Locked or Not Properly Configured. The PLL is not ready for use as the system clock source.                                                                                                                                      |       |        |

|        |               | 1        | The PLL Is Locked and Is Ready for Use as the System Clock Source.                                                                                                                                                                              |       |        |

### **POWER MANAGEMENT UNIT**

#### **POWER MANAGEMENT UNIT FEATURES**

The power management unit (PMU) controls the different power modes of the ADuCM410 and ADuCM420.

Four power modes are available: active, core sleep, system sleep, and hibernate.

#### POWER MANAGEMENT UNIT OVERVIEW

The Cortex-M33 power saving modes are linked to the PMU modes and are described in this section. The PMU is in the always on section. Each mode gives a power reduction benefit with a corresponding reduction in functionality.

#### POWER MANAGEMENT UNIT OPERATION

The debug tools can prevent the Cortex-M33 from fully entering its power saving modes by setting bits in the debug logic. Only a power-on reset resets the debug logic. Therefore, the device must be power cycled after using serial wire debug with application code containing the wait for interrupt (WFI) instruction.

#### Power Mode: Active Mode (Mode 0)

The system is fully active. Memories and all user enabled peripherals are clocked, and the Cortex-M33 processor executes instructions. Note that the Cortex-M33 processor manages its internal clocks and can be in a partial clock gated state. This clock gating affects only the internal Cortex-M33 processing core. Automatic clock gating is used on all blocks. User code can use a WFI command to put the Cortex-M33 processor into a power saving mode (Mode 1, Mode 2, or Mode 3). The WFI instruction is independent of the power mode settings of the PMU.

When the ADuCM410 and ADuCM420 wake up from any of the low power modes (Mode 1 to Mode 3), the devices return to Mode 0.

#### Power Mode: Core Sleep Mode (Mode 1)

In core sleep mode, the system gates the clock to the Cortex-M33 core after the Cortex-M33 enters sleep mode. The rest of the system remains active. No instructions can be executed. However, DMA transfers can continue to occur between peripherals and memories. The Cortex-M33 processor HCLK is active, and the device wakes up using the nested vectored interrupt controller (NVIC).

#### Power Mode: System Sleep Mode (Mode 2)

In system sleep mode, the system gates the high speed system bus clock (HCLK) and the peripheral bus clocks (PCLK0 and PCLK1) after the Cortex-M33 enters sleep mode. The gating of these clocks stops all Arm high performance bus (AHB) activities and all peripherals attached to the Arm peripheral bus (APB). Peripheral clocks are all off, and they are no longer user programmable. The NVIC clock remains active, and the NVIC processes wake-up events.

#### **Power Mode: Hibernate Mode (Mode 3)**

In hibernate mode, the system disables power to all combinational logic and places sequential logic in retain mode. Because HCLK is stopped, the number of sources capable of waking up the system is restricted. A limited number of interrupts can wake the device from this mode (see Table 11).

Power Mode 1 to Power Mode 3 must be entered when the processor is not in an interrupt handler. If Power Mode 1 to Power Mode 3 are entered when the processor is in an interrupt handler, the power-down mode can only be exited by a reset or a higher priority interrupt source.

The following is example code of how to enter hibernate mode:

## **UG-1807**

## ADuCM410/ADuCM420 Hardware Reference Manual

#### **REGISTER SUMMARY: POWER MANAGEMENT UNIT**

Table 7. Power Management Register Summary

| Address    | Name   | Description               | Reset  | Access |

|------------|--------|---------------------------|--------|--------|

| 0x40005000 | PWRMOD | Power modes               | 0x0000 | RW     |

| 0x40005004 | PWRKEY | Key protection for PWRMOD | 0x0000 | RW     |

#### **REGISTER DETAILS: POWER MANAGEMENT UNIT**

#### **Power Modes Register**

Address: 0x40005000, Reset: 0x0000, Name: PWRMOD

Table 8. Bit Descriptions for PWRMOD

| Bits   | Bit Name | Settings | Description                                                                                                                                                                                                                                                       | Reset | Access |

|--------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:4] | RESERVED |          | Reserved.                                                                                                                                                                                                                                                         | 0x0   | R      |

| 3      | WICENACK |          | Wake-Up Controller Acknowledgment for Hibernate Mode (Mode 3).                                                                                                                                                                                                    | 0x0   | R      |

|        |          | 0        | Disable Sleep Deep.                                                                                                                                                                                                                                               |       |        |

|        |          | 1        | Enable Sleep Deep. Must be set to enter system sleep and hibernate modes.                                                                                                                                                                                         |       |        |

| 2      | RESERVED |          | Reserved.                                                                                                                                                                                                                                                         | 0x0   | R      |

| [1:0]  | PWRMOD   |          | Power Modes Control Bits. When read, these bits contain the last power mode value entered by user code. Note that, to place the Cortex in hibernate mode (Mode 3), the Cortex-M33 System Control Register (Address 0xE000ED10) must be configured to 0x4 or 0x06. | 0x0   | R/W    |

|        |          | 00       | Active Mode.                                                                                                                                                                                                                                                      |       |        |

|        |          | 01       | Core Sleep Mode.                                                                                                                                                                                                                                                  |       |        |

|        |          | 10       | System Sleep Mode.                                                                                                                                                                                                                                                |       |        |

|        |          | 11       | Hibernate Mode.                                                                                                                                                                                                                                                   |       |        |

#### **Key Protection for PWRMOD Register**

Address: 0x40005004, Reset: 0x0000, Name: PWRKEY

**Table 9. Bit Descriptions for PWRKEY**

| Bit(s) | Bit Name | Description                                                                                                                                                                                                                                                                                                       | Reset | Access |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:0] | PWRKEY   | Power control key register. The PWRMOD register is key protected. Two writes to the key are necessary to change the value in the PWRMOD register: first 0x4859, then 0xF27B. Then, write to the PWRMOD register. A write to any other register before writing to PWRMOD returns the protection to the lock state. | 0x0   | RW     |

### ARM CORTEX-M33 PROCESSOR

#### **ARM CORTEX-M33 PROCESSOR FEATURES**

The high performance features include the following:

- 1.5 Dhrystone MIPS/MHz

- Many instructions, including multiply, are single cycle.

- Optimized for single-cycle flash usage.

- Hardware division and fast digital signal processing (DSP) orientated multiply and accumulate.

The low power features include the following:

- Low standby current.

- Core implemented using advanced clock gating so that only the actively used logic consumes dynamic power.

- Low power features including architectural clock gating, sleep mode, and a power aware system with optional wake-up interrupt controller.

The advanced interrupt handling features include the following:

- The NVIC supports up to 480 interrupts, and eight levels of priority are available. The ADuCM410 and ADuCM420 support 74 of these interrupts. The vectored interrupt feature greatly reduces interrupt latency because software is not required to determine which interrupt handler to serve. In addition, software is not required to set up nested interrupt support.

- The Arm Cortex-M33 processor automatically pushes registers onto the stack at the entry interrupt and retrieves them at the exit interrupt. The pushing and retrieving reduce interrupt handling latency and allow interrupt handlers to be normal C functions.

- Dynamic priority control for each interrupt.

- Latency reduction using late arrival interrupt acceptance and tail chain interrupt entry.

- Immediate execution of a nonmaskable interrupt request for safety critical applications.

The system includes advanced fault handling features, including various exception types and fault status registers.

The ADuCM410 and ADuCM420 also have the following debug support features:

- Serial wire debug (SWD) interfaces.

- Flash patch and breakpoint unit for implementing breakpoints.

- Data watchpoint and trigger unit for implementing watchpoints trigger resources and system profiling. The ADuCM410 and ADuCM420 are limited to one hardware watchpoint. With only one comparator, the data watchpoint and trigger unit does not support data matching for watchpoint generation.

#### **ARM CORTEX-M33 PROCESSOR OVERVIEW**

The ADuCM410 and ADuCM420 contain an embedded Arm Cortex-M33 processor. The Arm Cortex-M33 processor provides a high performance, low cost platform that meets the system requirements of minimal memory implementation, reduced pin count, and low power consumption while delivering computational performance and system response to interrupts.

#### **ARM CORTEX-M33 PROCESSOR OPERATION**

Several Arm Cortex-M33 processor components are flexible in their implementation. This section details the actual implementation of these components in the ADuCM410 and ADuCM420.

#### Serial Wire Debug

The ADuCM410 and ADuCM420 support the serial wire interface via SWO, SWCLK, and SWDIO. The devices do not support the 5-wire Joint Action Test Group (JTAG) interface.

#### **ROM Table**

The ADuCM410 and ADuCM420 implement the default read only memory (ROM) table.

#### **Nested Vectored Interrupt Controller Interrupts (NVICs)**

The Arm Cortex-M33 processor includes an NVIC, which offers the following features:

- Nested interrupt support

- Vectored interrupt support

- Dynamic priority changes support

- Interrupt masking

In addition, the NVIC has a nonmaskable interrupt (NMI) input.

The NVIC is implemented on the ADuCM410 and ADuCM420, and more details are available in the System Exceptions and Peripheral Interrupts section.

#### Wake-Up Interrupt Controller

The ADuCM410 and ADuCM420 have a modified wake-up controller that provides the lowest possible power-down current. More details on this feature are available in the Power Management Unit section. It is not recommended to enter power saving mode while servicing an interrupt. However, if the device does enter power saving mode while servicing an interrupt, it can only wake up by a higher priority interrupt source.

### μDMA

The ADuCM410 and ADuCM420 implement the Arm  $\mu$ DMA. See the Direct Memory Access (DMA) Controller section for more details.

#### Floating-Point Unit (FPU)

The Cortex-M33 contains a single precision, floating-point computation unit.

The FPU adds 45 IEEE® 754<sup>™</sup>-2008-compatible, single-precision floating-point instructions. Using floating-point instructions usually yields an average of 10 times increase in performance over the equivalent software libraries.

Ensure the compiler is instructed to use the FPU for floating-point arithmetic (see the ADuCM410 and ADuCM420 evaluation kits for examples).

#### Peripheral Address Accesses Using a Cortex-M33 core

Unaligned peripheral address accesses are not supported on the Cortex-M33 core. Unaligned address accesses result in a usage exception fault. Access for a Cortex-M33 core is different compared to a Cortex-M3, which does not generate such an exception for unaligned address accesses.

An example code of an unaligned memory access follows:

```

R0 = 4

R1 = 0x40064001

STR R0, [R1]

```

When R1 = 0x20001001(SRAM location), there is no issue.

When R1 = 0x40064001, which is the PWMCON0 Byte 1 address, a usage fault exception occurs.

If using the C-based header file definitions provided with the Analog Devices evaluation software, the usage fault errors are not a concern.

#### ARM CORTEX-M33 PROCESSOR RELATED DOCUMENTS

The following list contains documentation related to the Arm Cortex-M3:

- Cortex-M33 Revision r1p0 Technical Reference Manual.

- ARMv8-M Architecture Reference Manual (DDI 0553)

- Arm Debug Interface Architecture Specification v5.

- PrimeCell μDMA Controller (PL230) Technical Reference Manual Revision r0p0 (DDI 0417)

### SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS

#### **CORTEX-M33 AND FAULT MANAGEMENT**

The ADuCM410 and ADuCM420 integrate an Arm Cortex-M33 processor, which supports several system exceptions and interrupts generated by peripherals. Table 10 lists the Arm Cortex-M33 processor system exceptions.

**Table 10. System Exceptions**

| Number  | Туре                    | Priority        | Description                                                                                                      |

|---------|-------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|

| 1       | Reset                   | -3 (highest)    | Any reset.                                                                                                       |

| 2       | NMI                     | -2              | Nonmaskable interrupt not connected on the ADuCM410 and ADuCM420.                                                |

| 3       | Hard fault              | -1              | All fault conditions if the corresponding fault handler is not enabled.                                          |

| 4       | Memory management fault | Programmable    | Access to invalid locations.                                                                                     |

| 5       | Bus fault               | Programmable    | Prefetch fault, memory access fault, data abort, and other address/memory related faults.                        |

| 6       | Usage fault             | Programmable    | Same as undefined instruction executed or invalid state transition attempt.                                      |

| 7 to 10 | Reserved                | Not applicable. | Not applicable.                                                                                                  |

| 11      | SVCALL                  | Programmable    | System supervisor call with SVC instruction. Used for system function calls.                                     |

| 12      | Debug monitor           | Programmable    | Debug monitor (breakpoint, watchpoint, or external debug requests).                                              |

| 13      | Reserved                | Not applicable  | Not applicable.                                                                                                  |

| 14      | PENDSV                  | Programmable    | Pending request for system service. Used for queuing system calls until other tasks and interrupts are serviced. |

| 15      | SYSTICK                 | Programmable    | System tick timer.                                                                                               |

The NVIC controls the peripheral interrupts and are listed in Table 11. All interrupt sources can wake up the device from core sleep mode (Mode 1). Only a limited number of interrupts can wake up the processor from the low power modes, system sleep and hibernate (Mode 2 and Mode 3), as shown in Table 11. When the device is woken up from Mode 2 or Mode 3, it returns to Mode 0. If the processor enters any power mode from Mode 1 to Mode 3 while the processor is in an interrupt handler, only an interrupt source with a higher priority than the current interrupt can wake up the device (higher value in the IPRx registers).

The following two steps are usually required to configure an interrupt:

- 1. Configure a peripheral to generate an interrupt request to the NVIC.

- 2. Configure the NVIC for that peripheral request.

**Table 11. Interrupt Vector Table**

| Interrupt<br>Number | Vector                                | Wake Up Processor from<br>Mode 1 | Wake Up Processor from Mode 2 or<br>Mode 3 |

|---------------------|---------------------------------------|----------------------------------|--------------------------------------------|

| 0                   | Wake-up timer                         | Yes                              | Yes                                        |

| 1                   | External Interrupt 0                  | Yes                              | Yes                                        |

| 2                   | External Interrupt 1                  | Yes                              | Yes                                        |

| 3                   | External Interrupt 2                  | Yes                              | Yes                                        |

| 4                   | External Interrupt 3                  | Yes                              | Yes                                        |

| 5                   | External Interrupt 4                  | Yes                              | Yes                                        |

| 6                   | External Interrupt 5                  | Yes                              | Yes                                        |

| 7                   | External Interrupt 6                  | Yes                              | Yes                                        |

| 8                   | External Interrupt 7                  | Yes                              | Yes                                        |

| 9                   | External Interrupt 8                  | Yes                              | Yes                                        |

| 10                  | External interrupt 9                  | Yes                              | Yes                                        |

| 11                  | Watchdog Timer                        | Yes                              | Yes                                        |

| 12                  | 16-Bit General-Purpose Timer 0 (GPT0) | Yes                              | No                                         |

| 13                  | 16-Bit General-Purpose Timer 1 (GPT1) | Yes                              | No                                         |

| 14                  | 16-Bit General-Purpose Timer 2 (GPT2) | Yes                              | No                                         |

| 15                  | 32-Bit General-Purpose Timer 0 (GPT3) | Yes                              | No                                         |

| 16                  | 32-Bit General-Purpose Timer 1 (GPT4) | Yes                              | No                                         |

| 17                  | MDIO                                  | Yes                              | No                                         |

| 18                  | Flash controller                      | Yes                              | No                                         |

| 19                  | UART Channel 0 (UART0)                | Yes                              | No                                         |

| Intermed            | T                                         | Waka Un Dua sassau fuana      | Welco Ha Duo cocco a fuoro Modo 2 ou       |

|---------------------|-------------------------------------------|-------------------------------|--------------------------------------------|

| Interrupt<br>Number | Vector                                    | Wake Up Processor from Mode 1 | Wake Up Processor from Mode 2 or<br>Mode 3 |

| 20                  | UART Channel 1 (UART1)                    | Yes                           | No                                         |

| 21                  | SPI Channel 0 (SPI0)                      | Yes                           | No                                         |

| 22                  | SPI Channel 1 (SPI1)                      | Yes                           | No                                         |

| 23                  | SPI Channel 2 (SPI2)                      | Yes                           | No                                         |

| 24                  | I <sup>2</sup> C Channel 0 (I2C0) slave   | Yes                           | No                                         |

| 25                  | I2C0 master                               | Yes                           | No                                         |

| 26                  | I <sup>2</sup> C Channel 1 (I2C1) slave   | Yes                           | No                                         |

| 27                  | I2C1 master                               | Yes                           | No                                         |

| 28                  | I <sup>2</sup> C Channel 2 (I2C2) slave   | Yes                           | No                                         |

| 29                  | I2C2 master                               | Yes                           | No                                         |

| 30                  | PLA Channel 0 (PLA0)                      | Yes                           | No                                         |

| 31                  | PLA Channel 1 (PLA1)                      | Yes                           | No                                         |

| 32                  | PLA Channel 2 (PLA2)                      | Yes                           | No                                         |

| 33                  | PLA Channel 3 (PLA3)                      | Yes                           | No                                         |

| 34                  | PWM trip                                  | Yes                           | No                                         |

| 35                  | PWM Pair 0 (IRQPWM0)                      | Yes                           | No                                         |

| 36                  | PWM Pair 1 (IRQPWM1)                      | Yes                           | No                                         |

| 37                  | PWM Pair 2 (IRQPWM2)                      | Yes                           | No                                         |

| 37                  | PWM Pair 3 (IRQPWM3)                      | Yes                           | No                                         |

| 39                  | SRAM error                                | Yes                           | No                                         |

| 40                  | DMA error                                 | Yes                           | No                                         |

| 41                  | DMA Channel 0 (SPI0 transmit) done        | Yes                           | No                                         |

| 42                  | DMA Channel 1 (SPI0 receive) done         | Yes                           | No                                         |

| 43                  | DMA Channel 2 (SPI1 transmit) done        | Yes                           | No                                         |

| 44                  | DMA Channel 3 (SPI1 receive) done         | Yes                           | No                                         |

| 45                  | DMA Channel 4 (SPI2 transmit) done        | Yes                           | No                                         |

| 46                  | DMA Channel 5 (SPI2 receive) done         | Yes                           | No                                         |

| 47                  | DMA Channel 6 (UART0 transmit) done       | Yes                           | No                                         |

| 48                  | DMA Channel 7 (UART0 receive) done        | Yes                           | No                                         |

| 49                  | DMA Channel 8 (UART1 transmit) done       | Yes                           | No                                         |

| 50                  | DMA Channel 9 (UART1 receive) done        | Yes                           | No                                         |

| 51                  | DMA Channel 10 (I2C0 slave transmit) done | Yes                           | No                                         |

| 52                  | DMA Channel 11 (I2C0 slave receive) done  | Yes                           | No                                         |

| 53                  | DMA Channel 12 (I2C0 master) done         | Yes                           | No                                         |

| 54                  | DMA Channel 13 (I2C1 Slave transmit) done | Yes                           | No                                         |

| 55                  | DMA Channel 14 (I2C1 slave receive) done  | Yes                           | No                                         |

| 56                  | DMA Channel 15 (I2C1 master) done         | Yes                           | No                                         |

| 57                  | DMA Channel 16 (I2C2 slave transmit) done | Yes                           | No                                         |

| 58                  | DMA Channel 17 (I2C2 slave receive) done  | Yes                           | No                                         |

| 59                  | DMA Channel 18 (I2C2 master) done         | Yes                           | No                                         |

| 60                  | DMA Channel 19 (MDIO transmit) done       | Yes                           | No                                         |

| 61                  | DMA Channel 20 (MDIO receive) done        | Yes                           | No                                         |

| 62                  | DMA Channel 21 (flash) done               | Yes                           | No                                         |

| 63                  | DMA Channel 22 (ADC) done                 | Yes                           | No                                         |

| 64                  | PLL                                       | Yes                           | No                                         |

| 65                  | High frequency oscillator                 | Yes                           | No                                         |

| 66                  | ADC                                       | Yes                           | No                                         |

| 67                  | Sequencer                                 | Yes                           | No                                         |

| 68                  | Comparator 0                              | Yes                           | No                                         |

| 69                  | Comparator 1                              | Yes                           | No                                         |

| 70                  | Comparator 2                              | Yes                           | No                                         |

| 71                  | Comparator 3                              | Yes                           | No                                         |

|                     | <u>'</u>                                  | J                             | 1                                          |

| Interrupt<br>Number | Vector           | Wake Up Processor from<br>Mode 1 | Wake Up Processor from Mode 2 or<br>Mode 3 |

|---------------------|------------------|----------------------------------|--------------------------------------------|

| 72                  | VDAC             | Yes                              | No                                         |

| 73                  | Reserved         | Not applicable                   | Not applicable                             |

| 74                  | Reserved         | Not applicable                   | Not applicable                             |

| 75                  | Reserved         | Not applicable                   | Not applicable                             |

| 76                  | Reserved         | Not applicable                   | Not applicable                             |

| 77                  | Reserved         | Not applicable                   | Not applicable                             |

| 78                  | Reserved         | Not applicable                   | Not applicable                             |

| 79                  | Reserved         | Not applicable                   | Not applicable                             |

| 80                  | Reserved         | Not applicable                   | Not applicable                             |

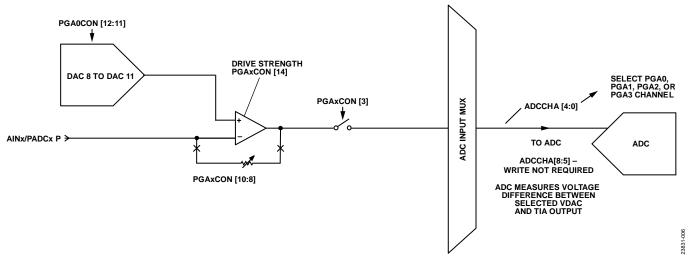

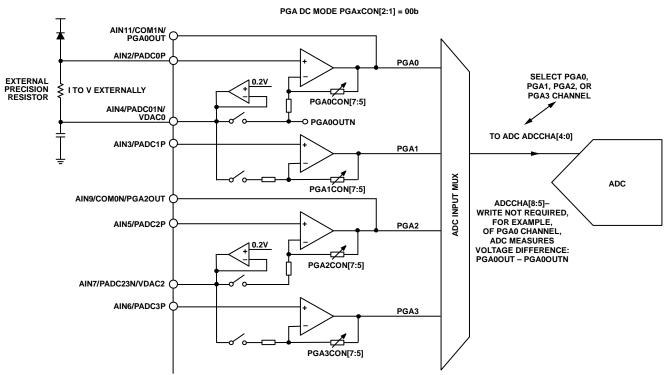

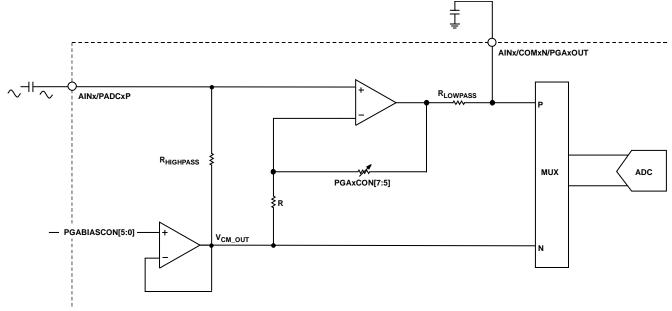

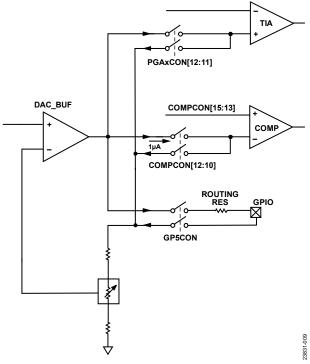

| 81                  | Reserved         | Not applicable                   | Not applicable                             |