One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## How to Set Up and Use the ADuCRF101

#### SCOPE

This user guide provides a detailed description of the ADuCRF101 functionality and features.

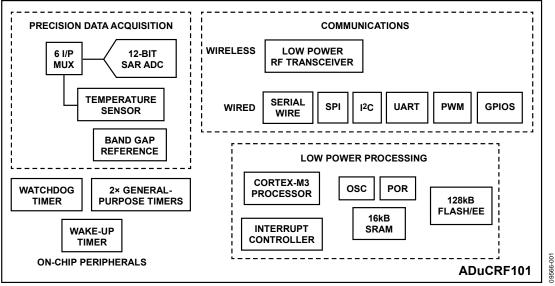

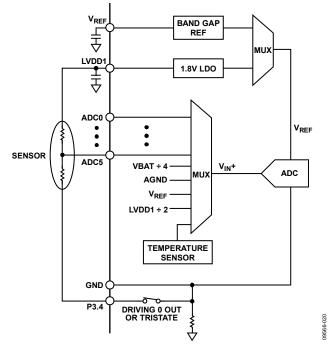

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

# TABLE OF CONTENTS

| Scope 1                                           |

|---------------------------------------------------|

| Functional Block Diagram 1                        |

| Revision History                                  |

| Using the ADuCRF101 User Guide                    |

| Number Notations                                  |

| Register Access Conventions 5                     |

| Acronyms and Abbreviations 5                      |

| Introduction to the ADuCRF101                     |

| Main Features of the ADuCRF101                    |

| Memory Organization                               |

| Cortex-M3 Processor                               |

| Cortex-M3 Processor Features9                     |

| Cortex-M3 Processor Overview9                     |

| Cortex-M3 Processor Operation9                    |

| Related Documents                                 |

| System Exceptions and Peripheral Interrupts11     |

| Pin and RF Transceiver Interrupts Configuration13 |

| Register Summary (Interrupts)13                   |

| Register Details (Interrupts)14                   |

| Clocking Architecture                             |

| Features                                          |

| Clocking Architecture Block Diagram               |

| Clocking Architecture Overview18                  |

| Clocking Architecture Operation19                 |

| Register Summary (Clock Control)19                |

| Register Details (Clock Control) 19               |

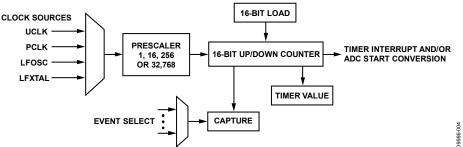

| General-Purpose Timers                            |

| General-Purpose Timers (Timer 0/Timer 1) Features |

| General-Purpose Timers Block Diagram              |

| General-Purpose Timers Overview                   |

| General-Purpose Timers Operation                  |

| Register Summary (Timer 0)24                      |

| Register Details (Timer 0)                        |

| Register Summary (Timer 1) 27                     |

| Register Details (Timer 1) 27                     |

| Wake-Up Timer                                     |

| Wake-Up Timer (Timer 2) Features                  |

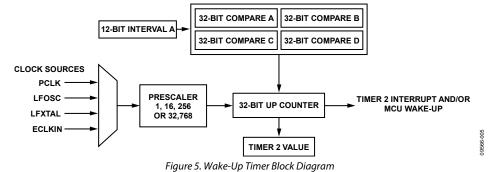

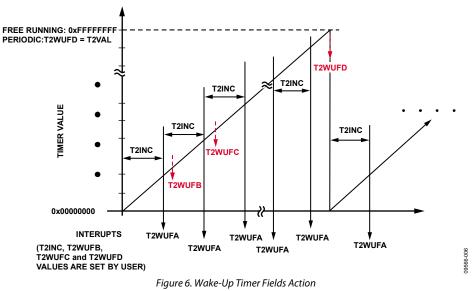

| Wake-Up Timer Block Diagram                       |

| Wake-Up Timer Overview                            |

| Wake-Up Timer Operation                           |

| Register Summary (Wake-Up Timer)                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Details (Wake-Up Timer)                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                               |

| Watchdog Timer                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                               |

| Watchdog Timer (Timer 3) Features                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                               |

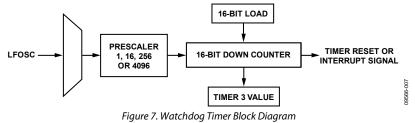

| Watchdog Timer Block Diagram                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                               |

| Watchdog Timer Overview                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                               |

| Watchdog Timer Operation                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                               |

| Register Summary (Watchdog Timer)                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                               |

| Register Details (Watchdog Timer)                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                               |

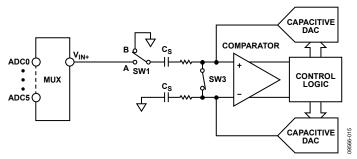

| ADC Circuit                                                                                                                                                                                                                                                                                                                      | 40                                                                                                                                                                                            |

| ADC Circuit Features                                                                                                                                                                                                                                                                                                             | 40                                                                                                                                                                                            |

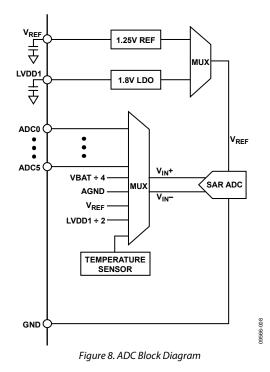

| ADC Block Diagram                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                               |

| ADC Circuit Overview                                                                                                                                                                                                                                                                                                             | 40                                                                                                                                                                                            |

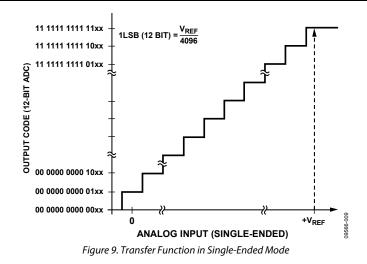

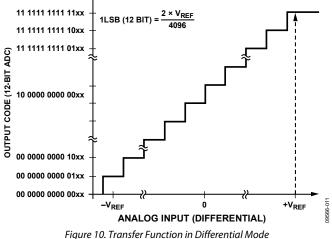

| Transfer Function                                                                                                                                                                                                                                                                                                                | 40                                                                                                                                                                                            |

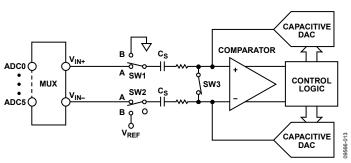

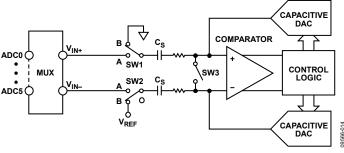

| Converter Operation                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                               |

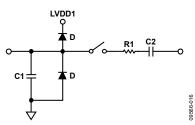

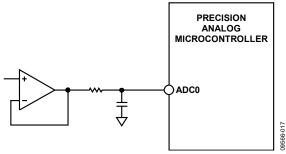

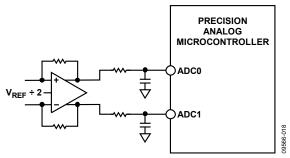

| Driving the Analog Inputs                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |

| ADC Reference Selection                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                               |

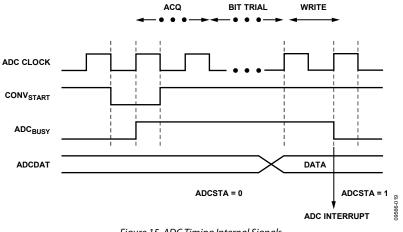

| Internal Signals                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                                                                            |

| ADC Operation                                                                                                                                                                                                                                                                                                                    | 45                                                                                                                                                                                            |

| Register Summary (Analog-to-Digital Converter)                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                               |

| Register Details (Analog-to-Digital Converter)                                                                                                                                                                                                                                                                                   | 46                                                                                                                                                                                            |

| Register Details (Analog-to-Digital Converter)<br>RF Transceiver                                                                                                                                                                                                                                                                 |                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                  | 49                                                                                                                                                                                            |

| RF Transceiver                                                                                                                                                                                                                                                                                                                   | 49<br>49                                                                                                                                                                                      |

| RF Transceiver<br>RF Transceiver Features                                                                                                                                                                                                                                                                                        | 49<br>49<br>50                                                                                                                                                                                |

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation                                                                                                                                                                                                                                                            | 49<br>49<br>50<br>55                                                                                                                                                                          |

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features                                                                                                                                                                                                                        |                                                                                                                                                                                               |

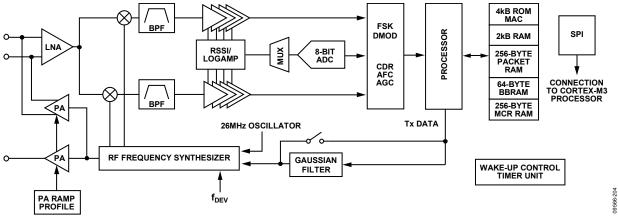

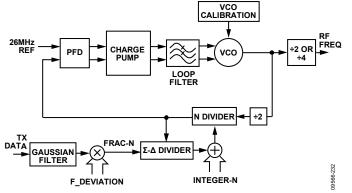

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description                                                                                                                                                                                                |                                                                                                                                                                                               |

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control                                                                                                                                                                               |                                                                                                                                                                                               |

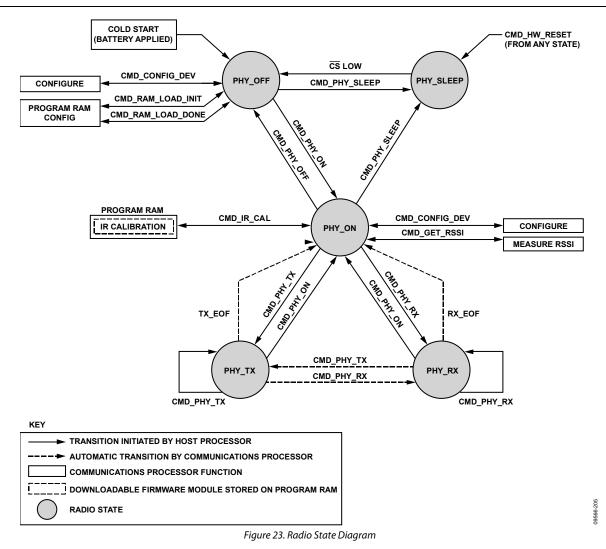

| RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States                                                                                                                                                                                 |                                                                                                                                                                                               |

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization                                                                                                                                             |                                                                                                                                                                                               |

| RF Transceiver Features<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands                                                                                                                        |                                                                                                                                                                                               |

| RF Transceiver Eeatures<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands<br>Automatic State Transitions                                                                                         |                                                                                                                                                                                               |

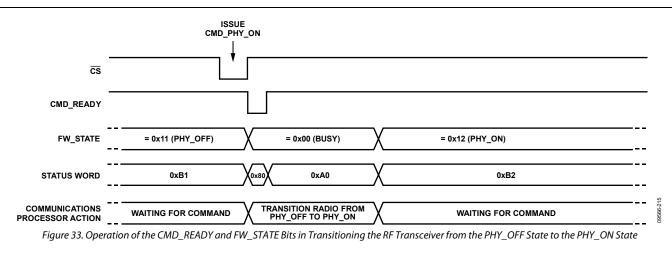

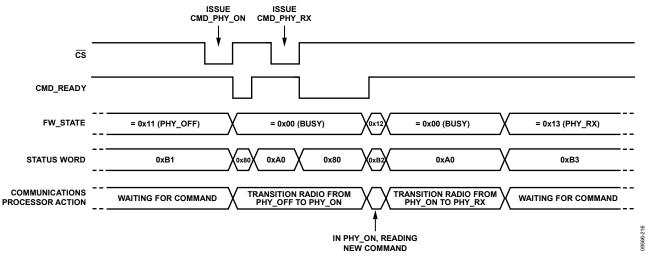

| RF Transceiver Features<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands<br>Automatic State Transitions<br>State Transition and Command Timing                                                  |                                                                                                                                                                                               |

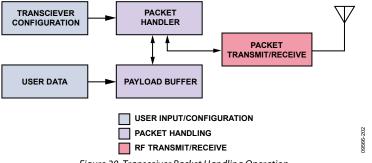

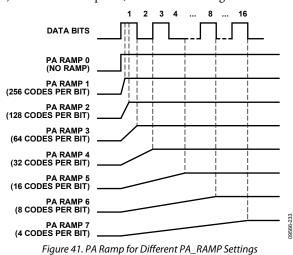

| RF Transceiver Features<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands<br>Automatic State Transitions<br>State Transition and Command Timing<br>Packet Mode                                   |                                                                                                                                                                                               |

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands<br>Automatic State Transitions<br>State Transition and Command Timing<br>Packet Mode<br>Preamble                                |                                                                                                                                                                                               |

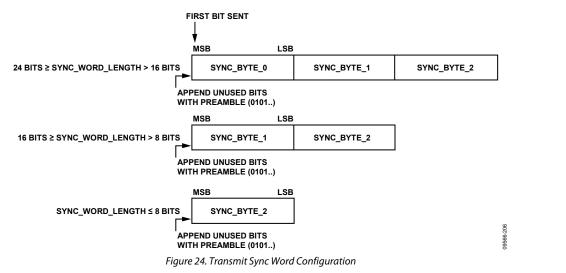

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands<br>Automatic State Transitions<br>State Transition and Command Timing<br>Packet Mode<br>Preamble<br>Sync Word                   |                                                                                                                                                                                               |

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands<br>Automatic State Transitions<br>State Transition and Command Timing<br>Packet Mode<br>Preamble<br>Sync Word<br>Payload        | 49<br>49<br>50<br>55<br>55<br>55<br>55<br>57<br>58<br>60<br>60<br>60<br>62<br>63<br>64<br>65<br>66                                                                                            |

| RF Transceiver<br>RF Transceiver Features<br>RF Transceiver Operation<br>RF Transceiver Advanced Features<br>Detailed Description<br>Radio Control<br>Radio States<br>Initialization<br>Commands<br>Automatic State Transitions<br>State Transition and Command Timing<br>Packet Mode<br>Preamble<br>Sync Word<br>Payload<br>CRC | 49         49         50         55         55         55         55         55         55         57         58         60         62         63         64         65         66         67 |

# ADuCRF101 User Guide

| Manchester Encoding                              | 68  |

|--------------------------------------------------|-----|

| Processor Interrupt Generation                   | 68  |

| RF Transceiver Memory Map                        | 70  |

| Memory Locations                                 | 70  |

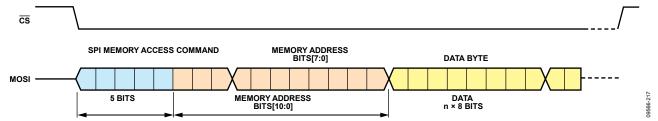

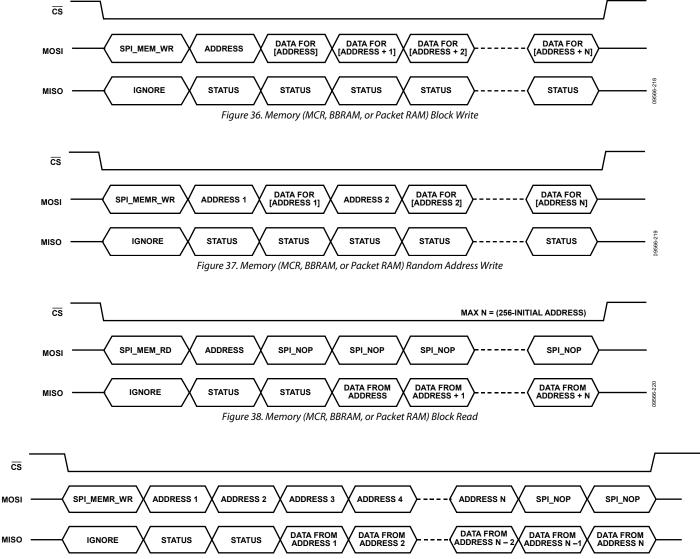

| SPI Interface                                    | 71  |

| Memory Access                                    | 73  |

| Low Power Modes                                  | 76  |

| Downloadable Firmware Modules                    | 76  |

| Radio Blocks                                     | 77  |

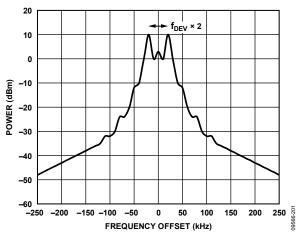

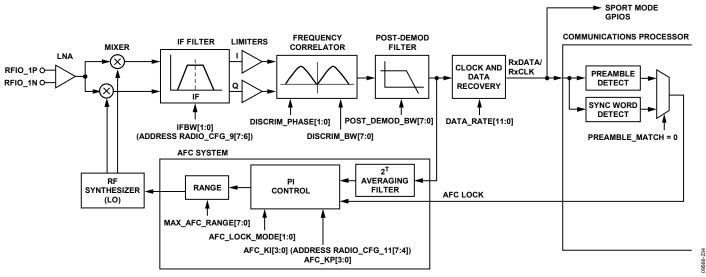

| 2FSK/GFSK/MSK/GMSK Demodulation                  | 81  |

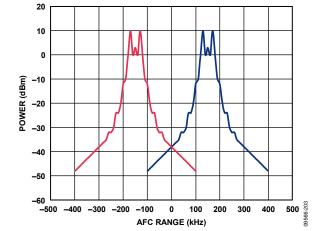

| AFC                                              | 82  |

| Peripheral Features                              | 85  |

| Applications Information                         | 85  |

| Command Reference                                | 88  |

| RF Transceiver Register Maps                     | 89  |

| MCR Register Description                         | 98  |

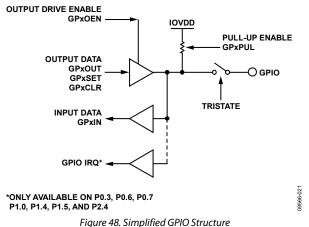

| Digital Input/Outputs                            | 101 |

| Digital I/O Features                             | 101 |

| Digital I/O Block Diagram                        | 101 |

| Digital I/O Overview                             | 101 |

| Digital I/O Operation                            | 101 |

| Digital Port Multiplex                           | 103 |

| Register Summary (General-Purpose Input Output). | 104 |

| Register Details (General-Purpose Input Output)  | 105 |

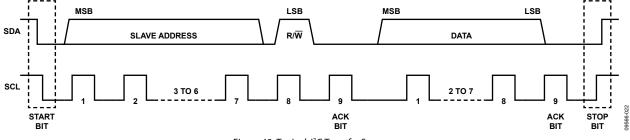

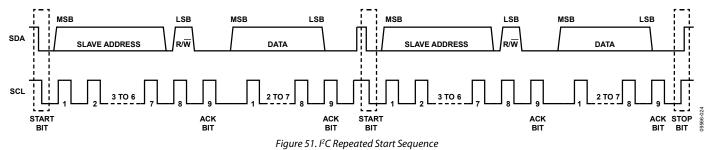

| I <sup>2</sup> C Serial Interface                | 113 |

| I <sup>2</sup> C Features                        | 113 |

| I <sup>2</sup> C Overview                        | 113 |

| I <sup>2</sup> C Operation                       | 113 |

| Register Summary (I <sup>2</sup> C)              | 117 |

| Register Details (I <sup>2</sup> C)              | 117 |

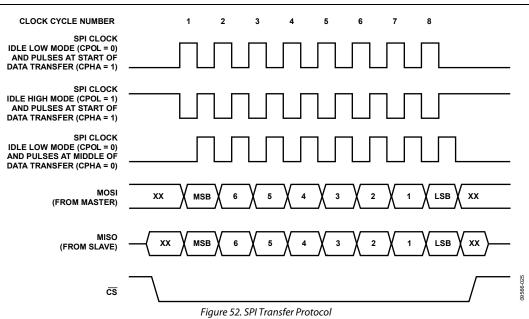

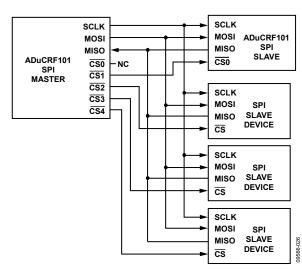

| Serial Peripheral Interfaces                     | 127 |

| SPI Features                                     | 127 |

| SPI Overview                                     | 127 |

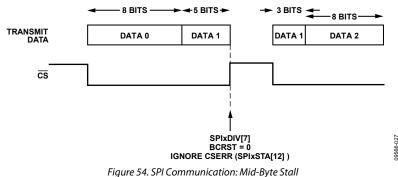

| SPI Operation                                    | 127 |

| SPI Interrupts                                   | 130 |

| SPI DMA                                          | 131 |

| SPI and Power-Down Modes                         | 132 |

| Other Considerations                             | 133 |

| Register Summary (Serial Peripheral Interface)   | 133 |

| Register Details (Serial Peripheral Interface)   | 133 |

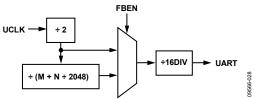

| UART Serial Interface                            | 142 |

| UART Features                                  | 142      |

|------------------------------------------------|----------|

| UART Overview                                  | 142      |

| UART Operation                                 | 142      |

| Programmed I/O Mode                            | 142      |

| DMA Mode                                       | 143      |

| Enable/Disable Bit                             | 143      |

| Interrupts                                     | 143      |

| Register Summary (UART)                        | 144      |

| Register Details (UART)                        | 144      |

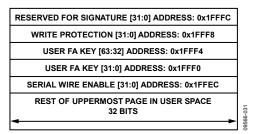

| Flash Controller                               | 149      |

| Flash Controller Features                      | 149      |

| Flash Controller Overview                      | 149      |

| Flash Memory Organization                      | 149      |

| Writing to Flash/EE Memory                     | 150      |

| Erasing Flash/EE Memory                        | 151      |

| Flash Controller Performance and Command Durat | tion 151 |

| Flash Protection                               | 151      |

| Flash Controller Failure Analysis Key          | 152      |

| Flash Integrity Signature feature              | 152      |

| Integrity of the Kernel                        | 153      |

| Abort Using Interrupts                         | 153      |

| Register Summary (Flash Controller)            | 154      |

| Register Details (Flash Controller)            | 155      |

| DMA Controller                                 | 163      |

| DMA Features                                   | 163      |

| DMA Overview                                   | 163      |

| DMA Operation                                  | 163      |

| Error Management                               | 163      |

| Interrupts                                     | 164      |

| DMA Priority                                   | 164      |

| Channel Control Data Structure                 | 164      |

| Register Summary (Direct Memory Access)        | 169      |

| Register Details (Direct Memory Access)        | 169      |

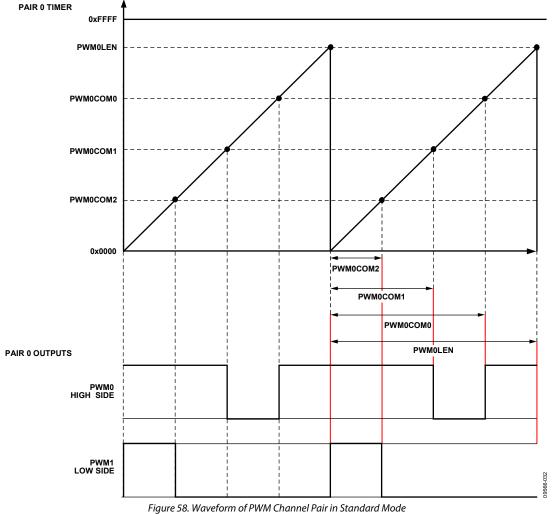

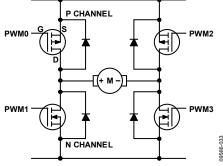

| PWM                                            | 182      |

| PWM features                                   | 182      |

| PWM Overview                                   | 182      |

| PWM Operation                                  | 182      |

| PWM Interrupt Generation                       | 185      |

| Register Summary (Pulse-Width Modulation)      | 186      |

| Register Details (Pulse-Width Modulation)      | 186      |

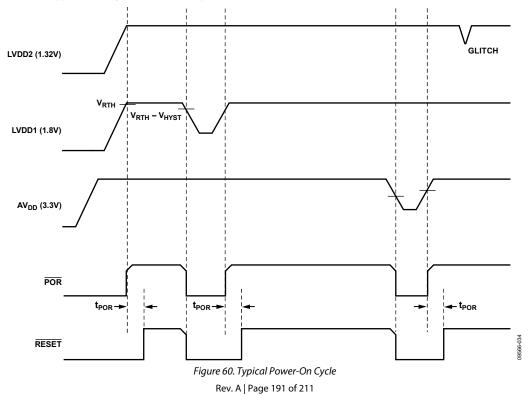

| Power Management Unit                          | 191      |

UG-231

# UG-231

| Power Management Unit Features           | 191 |

|------------------------------------------|-----|

| Power Supply Support Circuits Overview   | 191 |

| Programmable Power Modes Overview        | 192 |

| Programmable Power Modes Operation       | 193 |

| Register Summary (Power Management Unit) | 194 |

| Register Details (Power Management Unit) | 194 |

| Reset                                    | 196 |

| Reset Features                           | 196 |

| Reset Operation                          | 196 |

| Register Summary (Reset)                 | 196 |

#### **REVISION HISTORY**

11/14—Rev. 0 to Rev. A

4/13—Revision 0: Initial Version

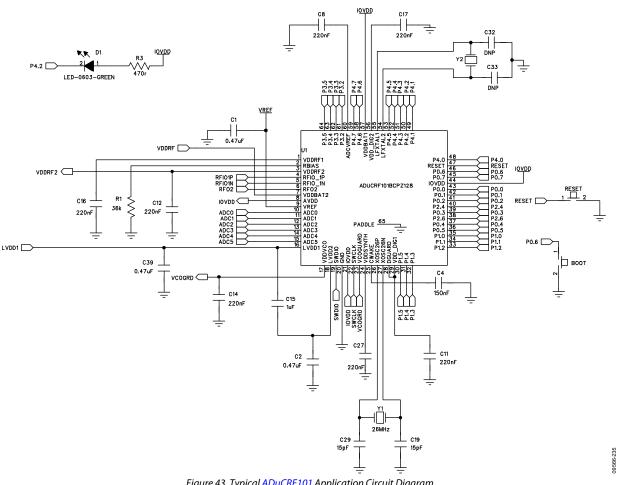

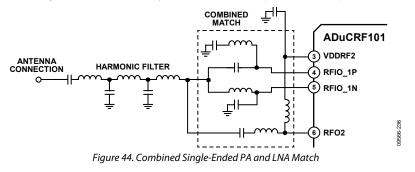

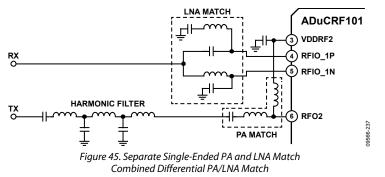

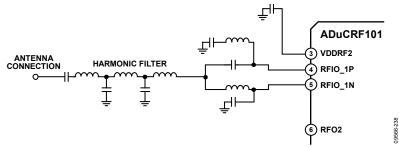

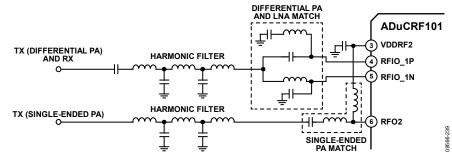

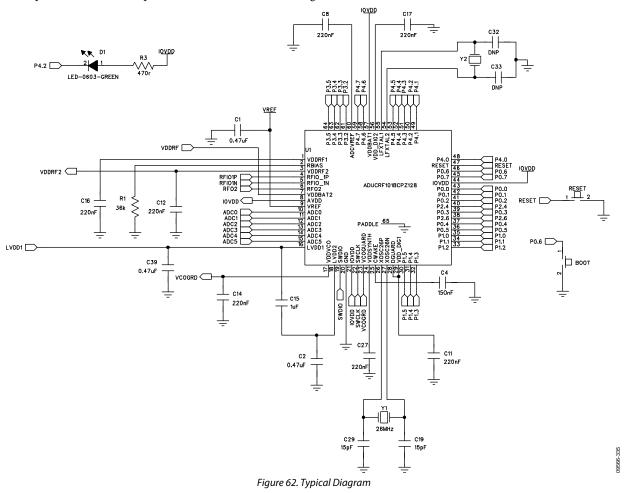

# ADuCRF101 User Guide Register Details (Reset) 197 Hardware Design Considerations 198 Pin Configuration and Function Descriptions 198 Power Supply and Ground 202 Serial Wire Debug Interface 203 In-Circuit Serial Download Access 203 External Crystal Oscillators 204 PA/LNA Matching 205

# USING THE ADuCRF101 USER GUIDE

#### NUMBER NOTATIONS

#### Table 1. Number Notations

| Notation | Description                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------|

| Bit N    | Bits are numbered in little endian format, that is, the least significant bit of a number is referred to as Bit 0. |

| V[X:Y]   | Bit field representation covering Bit X to Bit Y of a value or a field (V).                                        |

| 0xNN     | Hexadecimal (Base 16) numbers are preceded by the prefix 0x.                                                       |

| 0bNN     | Binary (Base 2) numbers are preceded by the prefix 0b.                                                             |

| NN       | Decimal (Base 10) are represented using no additional prefixes or suffixes.                                        |

#### **REGISTER ACCESS CONVENTIONS**

#### Table 2. Register Access Conventions

| Mode | Description                                                                               |

|------|-------------------------------------------------------------------------------------------|

| RW   | Memory location has read and write access.                                                |

| R    | Memory location is read access only. A read always returns 0, unless otherwise specified. |

| W    | Memory location is write access only.                                                     |

Note that register bit combinations not documented are reserved and should not be used.

#### ACRONYMS AND ABBREVIATIONS

| Table 3.             |                                                  |

|----------------------|--------------------------------------------------|

| Acronym/Abbreviation | Description                                      |

| ADC                  | Analog-to-digital converter                      |

| AFC                  | Automatic frequency control                      |

| ARM                  | Advanced RISC machine                            |

| CRC                  | Cyclic redundancy check                          |

| CTS                  | Clear to send                                    |

| DMA                  | Direct memory access                             |

| DMIPS                | Dhrystone million instructions per second (MIPS) |

| DWT                  | Data watch point and trigger                     |

| FPB                  | Flash patch and breakpoint                       |

| GPIO                 | General-purpose input and output                 |

| I <sup>2</sup> C     | Inter IC                                         |

| kB                   | Kilobyte                                         |

| LFSR                 | Linear feedback shift register                   |

| LSB                  | Least significant byte/bit                       |

| MMR                  | Memory mapped register                           |

| MSB                  | Most significant byte/bit                        |

| NMI                  | Nonmaskable interrupt                            |

| NVIC                 | Nested vectored interrupt controller             |

| PA                   | Power amplifier                                  |

| PWM                  | Pulse-width modulation                           |

| RISC                 | Reduced instruction set computer                 |

| Rx                   | Receive                                          |

| SAR                  | Successive approximation register                |

| SPI                  | Serial peripheral interface                      |

| SWD                  | Sync word detect/serial wire debug               |

| Тх                   | Transmit                                         |

| UART                 | Universal asynchronous transmitter               |

| WDT                  | Watch dog timer                                  |

| WUT                  | Wake-up timer                                    |

# **INTRODUCTION TO THE ADuCRF101**

The ADuCRF101 is a fully integrated data acquisition solution designed for low power wireless applications. It features a 12-bit ADC, a low power Cortex<sup>™</sup>-M3 processor from ARM<sup>®</sup>, a 431 MHz to 464 MHz and 862 MHz to 928 MHz RF transceiver, and Flash/EE memory packaged in a 9 mm × 9 mm LFCSP.

The acquisition section consists of a 12-bit ADC. The six inputs can be configured as single ended or differential. When configured in single-ended mode, they can be used for ratiometric measurements on sensors, powered from the internal LDO. An internal battery monitor channel and an on-chip temperature sensor are also available.

This wireless data acquisition system is designed to operate in battery-powered applications where low power is critical. The device can be configured in normal operating mode or different low power modes under direct program control. In flexi mode, any peripheral can operate and wake-up the device. In hibernate mode, the internal wake-up timer remains active. In shutdown mode, only an external interrupt can wake up the device.

The ADuCRF101 integrates a low power Cortex-M3 processor from ARM. It is a 32-bit RISC machine, offering up to 1.25 DMIPS peak performance. The Cortex-M3 processor also has a flexible 14-channel DMA controller supporting communication peripherals SPI, UART, and I<sup>2</sup>C. In addition, 128 kB of nonvolatile Flash/EE memory and 16 kB of SRAM are provided on-chip.

A 16 MHz on-chip oscillator generates the system clock. This clock can be internally divided for the processor to operate at a lower frequency thus saving power. A low power internal 32 kHz oscillator is available and can be used to clock the timers. There are two general-purpose timers, a wake-up timer and a system watchdog timer.

A range of communication peripherals can be configured as required in a specific application. These peripherals include UART, I<sup>2</sup>C, and SPI, GPIO ports, PWM, and RF transceiver.

The RF transceiver communicates in the 431 MHz to 464 MHz and 862 MHz to 928 MHz frequency bands using multiple configurations.

On-chip factory firmware supports in-circuit serial download via the UART while nonintrusive emulation and program download is also supported via the serial wire interface. These features are supported by the low cost development system.

The part operates from 2.2 V to 3.6 V and is specified over an industrial temperature range of -40 °C to +85 °C.

#### MAIN FEATURES OF THE ADuCRF101

#### Precision Data Acquisition

- Multichannel, 12-bit ADC.

- Ratiometric measurements supported.

- On-chip voltage reference and temperature sensor.

#### Low Power

- Operates directly from a battery.

- Supply range: 2.2 V to 3.6 V.

- Power consumption:

- 280 nA, in power-down mode, nonretained state.

- 1.9 µA, in power-down mode, processor memory, and RF transceiver memory retained.

- 210 µA/MHz, Cortex-M3 processor in active mode.

- 12.8 mA RF transceiver in receive mode; Cortex-M3 processor in power-down mode.

- 9 mA to 32 mA RF transceiver in transmit mode; Cortex-M3 processor in power-down mode.

#### Communication

- High performance RF transceiver:

- Frequency bands: 431 MHz to 464 MHz and 862 MHz to 928 MHz .

- Multiple data rates supported.

- Single-ended and differential PA with programmable output power.

- UART

- Industry standard, 16450 UART peripheral.

- Support for DMA.

# ADuCRF101 User Guide

- I<sup>2</sup>C

- 2-byte transmit and receive FIFOs for the master and slave.

- Support for DMA.

- SPI

- Master or slave mode with separate 4-byte Rx and Tx FIFOs.

- Rx and Tx DMA channels.

- 8-channel PWM.

- 28-pin GPIO port.

#### Processing

- ARM Cortex-M3 32-bit processor operating from an internal 16 MHz oscillator.

- 128 kB Flash/EE memory, 16 kB SRAM.

- In-circuit download and debug via serial wire.

- On-chip UART download capability.

#### **On-Chip Peripherals**

- Two general-purpose timers.

- Wake-up timer.

- Watchdog timer.

#### Packages and Temperature Range

• 64-lead LFCSP (9 mm  $\times$  9 mm) package –40 °C to 85 °C.

#### Tools

- Low cost development system.

- Third-party compiler and emulator tool support.

- Various protocol stacks available.

#### Applications

- Battery-powered wireless sensor.

- Medical telemetry systems.

- Industrial and home automation.

- Asset tracking.

- Security systems (access systems).

- Health and fitness applications.

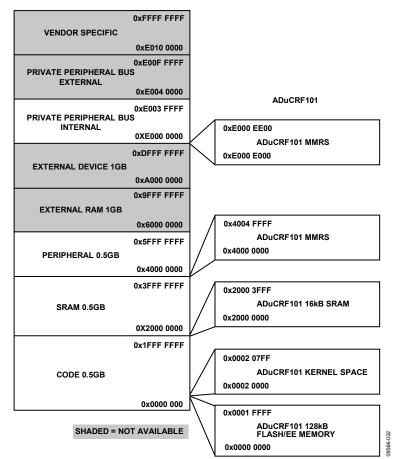

#### MEMORY ORGANIZATION

#### Features

- Cortex-M3 memory system features.

- Predefined memory map.

- Support for bit-band operation for atomic operations.

- Unaligned data access.

- ADuCRF101 on-chip peripherals are accessed via memory mapped registers, situated in the bit band region.

- User memory.

- 16 kB SRAM.

- 128 kB Flash.

- On-chip kernel for manufacturer data and in-circuit download.

Figure 2. Cortex-M3 Memory Map Diagram

# CORTEX-M3 PROCESSOR

### CORTEX-M3 PROCESSOR FEATURES

#### High Performance

- 1.25 DMIPS/MHz.

- Many instructions, including multiply, are single cycle.

- Separate data and instruction buses allow simultaneous data and instruction accesses to be performed.

- Optimized for single-cycle flash usage.

#### Low Power

- Low standby current.

- Core implemented using advanced clock gating so that only the actively used logic consumes dynamic power.

- Power-saving mode support (sleep and deep sleep modes). The design has separate clocks to allow unused parts of the processor to be stopped.

#### Advanced Interrupt-Handling

- The nested vectored interrupt controller (NVIC) supports up to 240 interrupts. The ADuCRF101 implements some of these. The vectored interrupt feature greatly reduces interrupt latency because there is no need for software to determine which interrupt handler to serve. In addition, there is no need to have software to set up nested interrupt support.

- The Cortex-M3 processor automatically pushes registers onto the stack at the entry interrupt and pops them back at the exit interrupt. This reduces interrupt handling latency and allows interrupt handlers to be normal C functions.

- Dynamic priority controls for each interrupt.

- Latency reduction using late arrival interrupt acceptance and tail-chain interrupt entry.

- Immediate execution of a nonmaskable interrupt request for safety-critical applications.

#### System Features

- Support for bit-band operation and unaligned data access.

- Advanced fault handling features include various exception types and fault status registers.

#### **Debug Support**

- Serial wire debug interfaces (SW-DP).

- Flash patch and breakpoint (FPB) unit for implementing breakpoints. Six active breakpoints are available.

- Data watchpoint and trigger (DWT) unit for implementing watchpoints. Two active watchpoints are available.

#### **CORTEX-M3 PROCESSOR OVERVIEW**

The ADuCRF101 contains an embedded ARM Cortex-M3 processor, Revision r2p0. The ARM Cortex-M3 provides a high performance, low-cost platform that meets the system requirements of minimal memory implementation, reduced pin count and low power consumption while delivering outstanding computational performance and exceptional system response to interrupts.

#### **CORTEX-M3 PROCESSOR OPERATION**

Several Cortex-M3 components are flexible in their implementation. This section details the actual implementation of these components in the ADuCRF101.

#### Serial Wire Debug (SW/JTAG-DP)

The ADuCRF101 only supports the serial wire interface via the SWCLK and SWDIO pins. It does not support the 5-wire JTAG interface.

#### **ROM Table**

The ADuCRF101 implements the default ROM table.

#### Nested Vectored Interrupt Controller Interrupts (NVIC)

The Cortex-M3 processor includes a nested vectored interrupt controller (NVIC) which offers several features:

- Nested interrupt support

- Vectored interrupt support

- Dynamic priority changes support

- Interrupt masking

In addition, the NVIC has a nonmaskable interrupt (NMI) input.

The NVIC is implemented on the ADuCRF101, and more details are available in the System Exceptions and Peripheral Interrupts section.

#### Wake-Up Interrupt Controller (WIC)

The ADuCRF101 has a modified WIC, which provides the lowest possible power-down current. This feature is transparent to the user and more details are available in the Power Management Unit section. It is not recommended to enter a power saving mode while servicing an interrupt. However, if the part does enter a power saving mode while servicing an interrupt it can only be woken up by a higher priority interrupt source.

#### μDMA

The ADuCRF101 implements the ARM µDMA. More details are available in the DMA Controller section.

#### **RELATED DOCUMENTS**

- Cortex-M3 Revision r2p0 Technical Reference Manual (DDI0337)

- Cortex-M3 Errata Notice: Cortex-M3/Cortex-M3 with ETM (AT420/AT425)

- ARMv7-M Architecture Reference Manual (DDI0403)

- ARMv7-M Architecture Reference Manual Errata Markup

- ARM Debug Interface v5 (IHI0031)

- PrimeCell µDMA Controller (PL230) Technical Reference Manual Revision r0p0 (DDI0417)

# SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS

The ADuCRF101 integrates a Cortex-M3 processor, which supports a number of system exceptions and interrupts generated by peripherals. Table 4 lists the Cortex-M3 system exceptions.

#### Table 4. System Exceptions

| Exception<br>Number | Туре                    | Priority     | Description                                                                                                       |

|---------------------|-------------------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| 1                   | Reset                   | –3 (highest) | Any reset                                                                                                         |

| 2                   | NMI                     | -2           | Nonmaskable interrupt connected to power supply monitor of ADuCRF101.                                             |

| 3                   | Hard fault              | -1           | All fault conditions, if the corresponding fault handler is not enabled.                                          |

| 4                   | Memory management fault | Programmable | Memory management fault; access to illegal locations.                                                             |

| 5                   | Bus fault               | Programmable | Prefetch fault, memory access fault, data abort, and other address/memory related faults.                         |

| 6                   | Usage fault             | Programmable | Faults such as undefined instruction executed or illegal state transition attempt.                                |

| 7 to 10             | Reserved                | N/A          |                                                                                                                   |

| 11                  | SVCall                  | Programmable | System service call with SVC instruction. Used for system function calls.                                         |

| 12                  | Debug monitor           | Programmable | Debug monitor (breakpoint, watchpoint, or external debug requests).                                               |

| 13                  | Reserved                | N/A          |                                                                                                                   |

| 14                  | PendSV                  | Programmable | Pendable request for system service. Used for queuing system calls until other tasks and interrupts are serviced. |

| 15                  | SYSTICK                 | Programmable | System tick timer.                                                                                                |

Reset is functional in any of the low power modes.

The nonmaskable interrupt (NMI) is connected to the power supply monitor of the ADuCRF101. The NMI wakes up the ADuCRF101 from Hibernate and Flexi modes. It is not available in shutdown mode.

The peripheral interrupts are controlled by the nested vectored interrupt controller and are listed in Table 5. Only a limited number of interrupts are capable of waking the processor up from hibernate or shutdown mode as shown in Table 5. All peripheral interrupts must also be configured in the corresponding peripheral. The RF transceiver and pin interrupts are configured in the external interrupt detection unit. See the Pin and RF Transceiver Interrupts Configuration section.

Two steps are normally required to configure an interrupt

- 1. Configure a peripheral to generate an interrupt request to the NVIC.

- 2. Configure the NVIC for that peripheral request.

#### Table 5. Peripherals Interrupts

|          | Vector                         |                                   |            |                | m             |

|----------|--------------------------------|-----------------------------------|------------|----------------|---------------|

| 0        |                                | Peripheral                        | Flexi Mode | Hibernate Mode | Shutdown Mode |

|          | Wake-up timer                  | Wake-up timer                     | Yes        | Yes            | No            |

| 1        | External Interrupt 0           | RF transceiver                    | Yes        | Yes            | Yes           |

| 2        | External Interrupt 1           | Pin                               | Yes        | Yes            | Yes           |

| 3        | External Interrupt 2           | Pin                               | Yes        | Yes            | No            |

| 4        | External Interrupt 3           | Pin                               | Yes        | Yes            | No            |

| 5        | External Interrupt 4           | Pin                               | Yes        | Yes            | No            |

| 6        | External Interrupt 5           | Pin                               | Yes        | Yes            | No            |

| 7        | External Interrupt 6           | Pin                               | Yes        | Yes            | No            |

| 8        | External Interrupt 7           | Pin                               | Yes        | Yes            | No            |

| 9        | External Interrupt 8           | RF transceiver                    | Yes        | Yes            | Yes           |

| 10       | Watchdog timer                 | Watchdog timer                    | Yes        | Yes            | No            |

| 11       | Reserved                       | Reserved                          | N/A        | N/A            | N/A           |

| 12       | Timer0                         | Timer0                            | Yes        | No             | No            |

| 13       | Timer1                         | Timer1                            | Yes        | No             | No            |

| 14       | ADC                            | ADC                               | Yes        | No             | No            |

| 15       | Flash controller               | Flash controller                  | Yes        | No             | No            |

| 16       | UART                           | UART                              | Yes        | No             | No            |

| 17       | SPI0                           | SPI0, interface to RF transceiver | Yes        | No             | No            |

| 18       | SPI1                           | SPI1, user SPI                    | Yes        | No             | No            |

| 19       | I <sup>2</sup> C slave         | l <sup>2</sup> C                  | Yes        | No             | No            |

| 20       | I <sup>2</sup> C master        | l <sup>2</sup> C                  | Yes        | No             | No            |

| 21 to 22 | Reserved                       | Reserved                          | N/A        | N/A            | N/A           |

| 23       | DMA error                      | DMA controller                    | Yes        | No             | No            |

| 24       | DMA SPI1 TX IRQ                | DMA controller                    | Yes        | No             | No            |

| 25       | DMA SPI1 RX IRQ                | DMA controller                    | Yes        | No             | No            |

| 26       | DMA UART TX IRQ                | DMA controller                    | Yes        | No             | No            |

| 27       | DMA UART RX IRQ                | DMA controller                    | Yes        | No             | No            |

| 28       | DMA I <sup>2</sup> C slave TX  | DMA controller                    | Yes        | No             | No            |

| 29       | DMA I <sup>2</sup> C slave RX  | DMA controller                    | Yes        | No             | No            |

| 30       | DMA I <sup>2</sup> C master TX | DMA controller                    | Yes        | No             | No            |

| 31       | DMA I <sup>2</sup> C master RX | DMA controller                    | Yes        | No             | No            |

| 32 to 34 | Reserved                       | Reserved                          | N/A        | N/A            | N/A           |

| 35       | ADC DMA                        | DMA controller                    | Yes        | No             | No            |

| 36       | DMA SPI0 TX IRQ                | DMA controller                    | Yes        | No             | No            |

| 37       | DMA SPIO RX IRQ                | DMA controller                    | Yes        | No             | No            |

|          | PWM_TRIP                       | PWM                               | Yes        | No             | No            |

|          | PWM0                           | PWM                               | Yes        | No             | No            |

|          | PWM1                           | PWM                               | Yes        | No             | No            |

|          | PWM2                           | PWM                               | Yes        | No             | No            |

| 42       | PWM3                           | PWM                               | Yes        | No             | No            |

The priority of the peripheral interrupts is programmable. Eight levels of priority are available.

Internally to the Cortex-M3 processor, the highest user-programmable priority (0) is treated as fourth priority, after a reset, NMI, and a hard fault.

Note that 0 is the default priority for all the programmable priorities. If the same priority level is assigned to two or more interrupts, their hardware priority (the lower the position number) determines the order in which the processor activates them. For example, if both SPI0 and SPI1 are Priority Level 1, then SPI0 has higher priority.

To enable an interrupt for any peripheral listed from 0 to 31 in Table 5, set the appropriate bit in the ISER0 register—ISER0 is a 32-bit register and each bit corresponds to the first 32 entries of Table 5.

For example, to enable ADC interrupt source in the NVIC, set ISER0[14] = 1. Similarly, to disable ADC interrupt, set ICER0[14] = 1.

To enable an interrupt for any peripheral numbered from 32 to 42 in Table 5, set the appropriate bit in the ISER1 register—ISER1 is a 32-bit register and ISER1 Bit 0 to Bit 10 correspond to the entries 32 to 42 of Table 5.

For example, to enable the PWM0 interrupt source in the NVIC, set ISER1[7] = 1. Similarly, to disable the PWM0 interrupt, set ICER1[7] = 1.

Table 6 lists the NVIC registers to enable and disable relevant interrupts and set the priority levels.

| Address    | Analog Devices Header File Name | Description                    | Access |

|------------|---------------------------------|--------------------------------|--------|

| 0xE000E100 | ISERO                           | Set IRQ 0 to IRQ 31 enable     | RW     |

| 0xE000E104 | ISER1                           | Set IRQ 32 to IRQ 42 enable    | RW     |

| 0xE000E180 | ICER0                           | Clear IRQ 0 to IRQ 31 enable   | RW     |

| 0xE000E184 | ICER1                           | Clear IRQ 32 to IRQ 42 enable  | RW     |

| 0xE000E200 | ISPRO                           | Set IRQ 0 to IRQ 31 pending    | RW     |

| 0xE000E204 | ISPR1                           | Set IRQ 32 to IRQ 42 pending   | RW     |

| 0xE000E280 | ICPRO                           | Clear IRQ 0 to IRQ 31 pending  | RW     |

| 0xE000E284 | ICPR1                           | Clear IRQ 32 to IRQ 42 pending | RW     |

| 0xE000E400 | IPRO                            | IRQ 0 to IRQ 3 priority        | RW     |

| 0xE000E404 | IPR1                            | IRQ 4 to IRQ 7 priority        | RW     |

| 0xE000E408 | IPR2                            | IRQ 8 to IRQ 11 priority       | RW     |

| 0xE000E40C | IPR3                            | IRQ 12 to IRQ 15 priority      | RW     |

| 0xE000E410 | IPR4                            | IRQ 16 to IRQ 19 priority      | RW     |

| 0xE000E414 | IPR5                            | IRQ 20 to IRQ 23 priority      | RW     |

| 0xE000E418 | IPR6                            | IRQ 24 to IRQ 27 priority      | RW     |

| 0xE000E41C | IPR7                            | IRQ 28 to IRQ 31 priority      | RW     |

| 0xE000E420 | IPR8                            | IRQ 32 to IRQ 35 priority      | RW     |

| 0xE000E424 | IPR9                            | IRQ 36 to IRQ 39 priority      | RW     |

| 0xE000E428 | IPR10                           | IRQ 40 to IRQ 42 priority      | RW     |

#### PIN AND RF TRANSCEIVER INTERRUPTS CONFIGURATION

Nine external interrupts are implemented. The two RF transceiver interrupts and seven pin interrupts can be separately configured to detect any combination of the following type of events:

- Edge: rising edge, falling edge, or both rising and falling edges. An interrupt signal (pulse) is sent to the NVIC upon detecting a transition from low to high, high to low, or on either high to low or low to high.

- Level: high or low. An interrupt signal is generated and remains asserted in the NVIC until the conditions generating the interrupt deassert. The level needs to be maintained for a minimum of one core clock cycle to be detected.

- These nine interrupt sources can wake-up the device when in hibernate mode. Only external interrupt 0, external interrupt 1, and external interrupt 8 (RF transceiver) can wake-up the device from shutdown mode.

External interrupt 0 and external interrupt 7 are used internally and are not available on a pin.

External interrupt 8 is also used internally and, while visible on an external pin, should only be used for monitoring purposes.

After an external interrupt has been asserted by the interrupt detection unit (IDU) an interrupt pulse to the Cortex-M3 processor is generated. Unless this external interrupt is cleared, subsequent interrupts on the same port are ignored by the IDU, and no further pulses are generated.

#### **REGISTER SUMMARY (INTERRUPTS)**

#### Table 7. Interrupts Register Summary

| Address    | Name   | Description                                 | Reset  | RW |

|------------|--------|---------------------------------------------|--------|----|

| 0x40002420 | EI0CFG | External Interrupt Configuration Register 0 | 0x0000 | RW |

| 0x40002424 | EI1CFG | External Interrupt Configuration Register 1 | 0x0000 | RW |

| 0x40002428 | EI2CFG | External Interrupt Configuration Register 2 | 0x0000 | RW |

| 0x40002430 | EICLR  | External Interrupts Clear Register          | 0x0000 | RW |

| 0x40002434 | NMICLR | NMI Clear Register                          | 0x00   | RW |

#### **REGISTER DETAILS (INTERRUPTS)**

#### External Interrupt Configuration Register 0

Address: 0x40002420, Reset: 0x0000, Name: EI0CFG

#### Table 8. Bit Descriptions for EI0CFG

| Bits    | Bit Name | Description                                | Reset | Access |

|---------|----------|--------------------------------------------|-------|--------|

| 15      | IRQ3EN   | External Interrupt 3 enable bit.           | 0x0   | RW     |

|         |          | 0: DIS. External Interrupt 3 disabled.     |       |        |

|         |          | 1: EN. External Interrupt 3 enabled.       |       |        |

| [14:12] | IRQ3MDE  | External Interrupt 3 detection mode.       | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                    |       |        |

|         |          | 001: FALL. Falling edge.                   |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge.   |       |        |

|         |          | 011: HIGHLEVEL. High level.                |       |        |

|         |          | 100: LOWLEVEL. Low level.                  |       |        |

| 11      | IRQ2EN   | External Interrupt 2 enable bit.           | 0x0   | RW     |

|         |          | 0: DIS. External Interrupt 2 disabled.     |       |        |

|         |          | 1: EN. External Interrupt 2 enabled.       |       |        |

| [10:8]  | IRQ2MDE  | External Interrupt 2 detection mode.       | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                    |       |        |

|         |          | 001: FALL. Falling edge.                   |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge.   |       |        |

|         |          | 011: HIGHLEVEL. High level.                |       |        |

|         |          | 100: LOWLEVEL. Low level.                  |       |        |

| 7       | IRQ1EN   | External Interrupt 1 enable bit.           | 0x0   | RW     |

|         |          | 0: DIS. External Interrupt 1 disabled.     |       |        |

|         |          | 1: EN. External Interrupt 1 enabled.       |       |        |

| [6:4]   | IRQ1MDE  | External Interrupt 1 detection mode.       | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                    |       |        |

|         |          | 001: FALL. Falling edge.                   |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge.   |       |        |

|         |          | 011: HIGHLEVEL. High level.                |       |        |

|         |          | 100: LOWLEVEL. Low level.                  |       |        |

| 3       | IRQ0EN   | External Interrupt 0 enable bit.           | 0x0   | RW     |

|         |          | 0: DIS. RF transceiver clock IRQ disabled. |       |        |

|         |          | 1: EN. RF transceiver clock IRQ enabled.   |       |        |

| [2:0]   | IRQ0MDE  | External Interrupt 0 detection mode.       | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                    |       |        |

|         |          | 001: FALL. Falling edge.                   |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge.   |       |        |

|         |          | 011: HIGHLEVEL. High level.                |       |        |

|         |          | 100: LOWLEVEL. Low level.                  |       |        |

#### External Interrupt Configuration Register 1

Address: 0x40002424, Reset: 0x0000, Name: EI1CFG

#### Table 9. Bit Descriptions for EI1CFG

| Bits    | Bit Name | Description                              | Reset | Access |

|---------|----------|------------------------------------------|-------|--------|

| 15      | IRQ7EN   | External Interrupt 7 enable bit.         | 0x0   | RW     |

|         |          | 0: DIS. External Interrupt 7 disabled.   |       |        |

|         |          | 1: EN. External Interrupt 7 enabled.     |       |        |

| [14:12] | IRQ7MDE  | External Interrupt 7 detection mode.     | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                  |       |        |

|         |          | 001: FALL. Falling edge.                 |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge. |       |        |

|         |          | 011: HIGHLEVEL. High level.              |       |        |

|         |          | 100: LOWLEVEL. Low level.                |       |        |

| 11      | IRQ6EN   | External Interrupt 6 enable bit.         | 0x0   | RW     |

|         |          | 0: DIS. External Interrupt 6 disabled.   |       |        |

|         |          | 1: EN. External Interrupt 6 enabled.     |       |        |

| [10:8]  | IRQ6MDE  | External Interrupt 6 detection mode.     | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                  |       |        |

|         |          | 001: FALL. Falling edge.                 |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge. |       |        |

|         |          | 011: HIGHLEVEL. High level.              |       |        |

|         |          | 100: LOWLEVEL. Low Level.                |       |        |

| 7       | IRQ5EN   | External Interrupt 5 enable bit.         | 0x0   | RW     |

|         |          | 0: DIS. External Interrupt 5 disabled.   |       |        |

|         |          | 1: EN. External Interrupt 5 enabled.     |       |        |

| [6:4]   | IRQ5MDE  | External Interrupt 5 detection mode.     | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                  |       |        |

|         |          | 001: FALL. Falling edge.                 |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge. |       |        |

|         |          | 011: HIGHLEVEL. High level.              |       |        |

|         |          | 100: LOWLEVEL. Low Level.                |       |        |

| 3       | IRQ4EN   | External Interrupt 4 enable bit.         | 0x0   | RW     |

|         |          | 0: DIS. External Interrupt 4 disabled.   |       |        |

|         |          | 1: EN. External Interrupt 4 enabled.     |       |        |

| [2:0]   | IRQ4MDE  | External Interrupt 4 detection mode.     | 0x0   | RW     |

|         |          | 000: RISE. Rising edge.                  |       |        |

|         |          | 001: FALL. Falling edge.                 |       |        |

|         |          | 010: RISEORFALL. Rising or falling edge. |       |        |

|         |          | 011: HIGHLEVEL. High level.              |       |        |

|         |          | 100: LOWLEVEL. Low Level.                |       |        |

#### External Interrupt Configuration Register 2

Address: 0x40002428, Reset: 0x0000, Name: EI2CFG

#### Table 10. Bit Descriptions for EI2CFG

| Bits   | Bit Name | Description                                            | Reset | Access |

|--------|----------|--------------------------------------------------------|-------|--------|

| [15:4] | RESERVED | Reserved.                                              | 0x000 | R      |

| 3      | IRQ8EN   | External Interrupt 8 (RF transceiver) enable bit.      | 0x0   | RW     |

|        |          | 0: DIS. RF transceiver IRQ disabled.                   |       |        |

|        |          | 1: EN. RF transceiver IRQ enabled.                     |       |        |

| [2:0]  | IRQ8MDE  | External Interrupt 8 (RF transceiver ) detection mode. | 0x0   | RW     |

|        |          | 000: RISE. Rising edge.                                |       |        |

|        |          | 001: FALL. Falling edge.                               |       |        |

|        |          | 010: RISEORFALL. Rising or falling edge.               |       |        |

|        |          | 011: HIGHLEVEL. High level.                            |       |        |

|        |          | 100: LOWLEVEL. Low level.                              |       |        |

#### External Interrupts Clear Register

Address: 0x40002430, Reset: 0x0000, Name: EICLR

#### Table 11. Bit Descriptions for EICLR

| Bits   | Bit Name | Description                                      | Reset | Access |

|--------|----------|--------------------------------------------------|-------|--------|

| [15:9] | RESERVED | Reserved.                                        | 0x00  | R      |

| 8      | IRQ8     | External Interrupt 8 (RF transceiver) clear bit. | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 7      | IRQ7     | External Interrupt 7 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 6      | IRQ6     | External Interrupt 6 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 5      | IRQ5     | External Interrupt 5 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 4      | IRQ4     | External Interrupt 4 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 3      | IRQ3     | External Interrupt 3 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 2      | IRQ2     | External Interrupt 2 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 1      | IRQ1     | External Interrupt 1 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

| 0      | IRQ0     | External Interrupt 0 clear bit.                  | 0x0   | RW     |

|        |          | Notes: Cleared automatically by hardware.        |       |        |

|        |          | 1: CLR. Clear an internal interrupt flag.        |       |        |

#### NMI Clear Register

Address: 0x40002434, Reset: 0x00, Name: NMICLR

#### Table 12. Bit Descriptions for NMICLR

| Bits  | Bit Name | Description                                                            | Reset | Access |

|-------|----------|------------------------------------------------------------------------|-------|--------|

| [7:1] | RESERVED | Reserved.                                                              | 0x00  | R      |

| 0     | CLEAR    | NMI clear bit.                                                         | 0x0   | RW     |

|       |          | Notes: Cleared automatically by hardware.                              |       |        |

|       |          | 1: EN. Clear an internal interrupt flag when the NMI interrupt is set. |       |        |

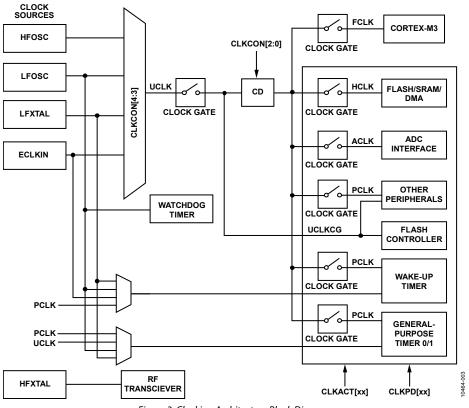

# **CLOCKING ARCHITECTURE**

#### FEATURES

- The ADuCRF101 integrates two on-chip oscillators and circuitry for two external crystals:

- HFOSC is a 16 MHz internal oscillator, used in active and flexi mode.

- LFOSC is a 32 kHz, low power internal oscillator, on at all times except at reset and in shutdown mode.

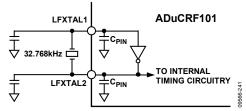

- LFXTAL is an optional 32 kHz external crystal, which can be used for more accurate timer clocking.

- HFXTAL is a 26 MHz external crystal, used to set the RF transceiver communication frequency. (connect to XOSC26P and XOSC26N pin).

- Power saving clock mechanism: clocks to individual peripherals can be disabled when that peripheral is not being used.

#### **CLOCKING ARCHITECTURE BLOCK DIAGRAM**

Figure 3. Clocking Architecture Block Diagram

#### **CLOCKING ARCHITECTURE OVERVIEW**

Three of the clock sources, HFOSC, LFOSC, and LFXTAL, can be used as system clocks. An external clock on P0.5 (ECLKIN) can also be used for test purposes.

Internally the system clock is divided into five clocks:

- FCLK for the core

- HCLK for the Flash, SRAM, and DMA

- ACLK for the ADC interface

- PCLK for the other peripherals.

- UCLK system clock

Figure 3 shows all the clocks available and includes clock gates for power management. More details on the clock gates can be found in the Power Management Unit section.

At power-up, the core executes from the 16 MHz internal oscillator. User code can select the clock source for the system clock and can divide the clock by a factor of  $2^{CD}$ , where CD is the clock divider bits (CLKCON[2:0]). This allows slower code execution and reduced power consumption.

UCLK is also passed to some of the serial peripherals so that the timings are not affected by CD changes.

For test purposes, the two internal oscillators, external crystal or UCLK can be brought out to P0.4 (ECLKOUT).

An external clock on P0.5 (ECKLIN) can also be used as the system clock: P0.5 must be configured first as a clock input and the external clock applied to P0.5 before switching clock source in the clock control register (CLKCON).

#### **REGISTER SUMMARY (CLOCK CONTROL)**

| Address    | Name    | Description                                   | Reset  | RW |

|------------|---------|-----------------------------------------------|--------|----|

| 0x40002000 | CLKCON  | System Clocking Architecture Control Register | 0x0000 | RW |

| 0x40002410 | XOSCCON | Crystal Oscillator Control Register           | 0x00   | RW |

| 0x40002480 | CLKACT  | Clock in Active Mode Enable Register          | 0x3FFF | RW |

| 0x40002484 | CLKPD   | Clock in Power-Down Mode Enable Register      | 0x3FFF | RW |

#### **REGISTER DETAILS (CLOCK CONTROL)**

#### System Clocking Architecture Control Register

Address: 0x40002000, Reset: 0x0000, Name: CLKCON

#### Table 14. Bit Descriptions for CLKCON

| Bits   | Bit Name | Description                                                                                                  | Reset | Access |

|--------|----------|--------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:8] | RESERVED | Reserved.                                                                                                    | 0x00  | R      |

| [7:5]  | CLKOUT   | GPIO output clock multiplexer select bits.                                                                   | 0x0   | RW     |

|        |          | 000: UCLKCG.                                                                                                 |       |        |

|        |          | 001: UCLK.                                                                                                   |       |        |

|        |          | 010: PCLK.                                                                                                   |       |        |

|        |          | 101: HFOSC.                                                                                                  |       |        |

|        |          | 110: LFOSC.                                                                                                  |       |        |

|        |          | 111: LFXTAL.                                                                                                 |       |        |

| [4:3]  | CLKMUX   | Digital subsystem clock source select bits.                                                                  | 0x0   | RW     |

|        |          | Notes: These bits select the clock source for the system. The recommended and default clock source is HFOSC. |       |        |

|        |          | 00: HFOSC. 16 MHz internal oscillator.                                                                       |       |        |

|        |          | 01: LFXTAL. 32.768 kHz external crystal.                                                                     |       |        |

|        |          | 10: LFOSC. 32.768 kHz internal oscillator.                                                                   |       |        |

|        |          | 11: ECLKIN. External clock on P0.5.                                                                          |       |        |

| [2:0]  | CD       | Clock divide bits.                                                                                           | 0x0   | RW     |

|        |          | 000: DIV1.                                                                                                   |       |        |

|        |          | 001: DIV2.                                                                                                   |       |        |

|        |          | 010: DIV4.                                                                                                   |       |        |

|        |          | 011: DIV8.                                                                                                   |       |        |

|        |          | 100: DIV16.                                                                                                  |       |        |

|        |          | 101: DIV32.                                                                                                  |       |        |

|        |          | 110: DIV64.                                                                                                  |       |        |

|        |          | 111: DIV128.                                                                                                 |       |        |

#### Crystal Oscillator Control Register

Address: 0x40002410, Reset: 0x00, Name: XOSCCON

#### Table 15. Bit Descriptions for XOSCCON

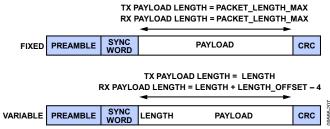

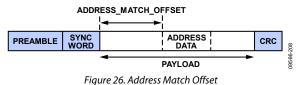

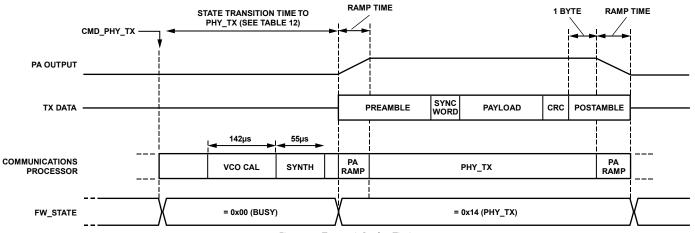

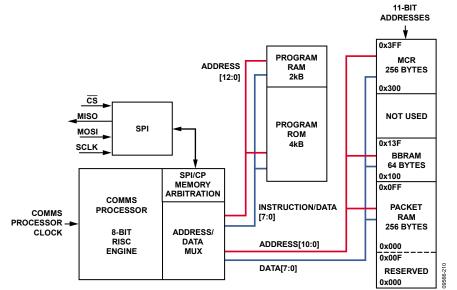

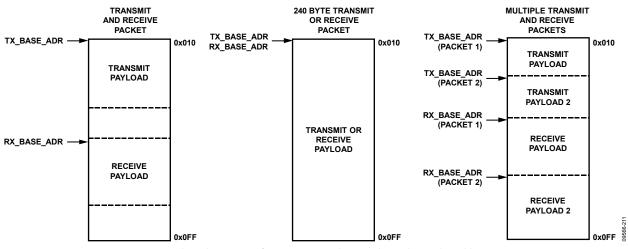

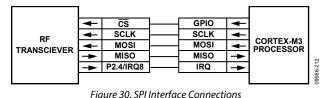

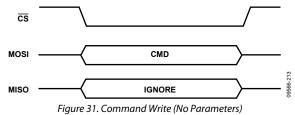

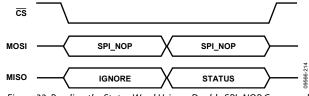

| Bits  | Bit Name | Description                                            | Reset | Access |