# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

## Reliability Report

**Report Title:** Qualification Test Report

**Report Type:** See Attached

**Date:** See Attached

Wafer Process: PHEMT-E

**QTR: 11014**

**Rev: 04**

**HMC756**

**HMC757**

**HMC949**

**HMC950**

**HMC952**

**HMC965**

**HMC995**

Note: This qualification was designed to evaluate the pHEMT-E process. The package type is only specific to the LP4 which was tested by the HMC757LP4. Other package qualifications are available at <a href="https://www.Hittite.com">www.Hittite.com</a>.

**Wafer Process: PHEMT-E**

**QTR:** 11014

**Rev: 04**

#### Introduction

This Reliability test is designed to satisfy the reliability requirements designated by Hittite Microwave Corporation for Hittite's PHEMT-E process. The testing is devised to simulate exposure to environments the product may experience during assembly, test, and life in the end user application. The pass/fail criteria are dependent upon DC and critical RF parameters determined by the appropriate catalog specifications. A complete data sheet for the HMC757LP4E can be found at www.hittite.com.

#### **General Description of Qualification Vehicle**

The HMC757LP 4E is a three stage GaAs pHEMT MMIC 1 Watt Power Amplifier which operates between 16 and 24 GHz. The HMC757LP 4E provides 20.5 dB of gain, and 27.5 dBm of saturated output power and 21% PAE from a +5V supply. The RF I/Os are DC blocked and matched to 50 Ohms. The 4x4mm plastic package eliminates the need for wire bonding, and is compatible with surface mount manufacturing techniques.

**Sample Selection:** All devices used were from finished goods and met acceptance test requirements.

#### **Reliability Tests:**

Initial Characteristics – 70 Devices were electrically tested at room temperature for DC and critical RF parameters.

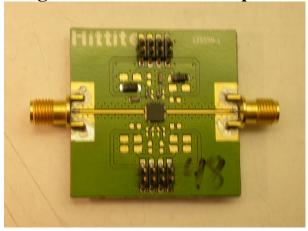

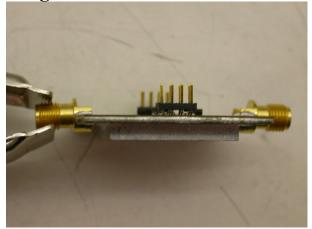

<u>High Temperature Operating Life (HTOL)</u> – 70 Devices were subjected to 1000 hours of accelerated operating life test. The devices were biased at 5V, 400mA per unit (2.0W) on product evaluation boards in a convection oven set at 125°C. Figures 1 through 3 show the evaluation board used for the HTOL testing.

<u>Post Stress Electrical Test</u> – 70 Post 1000 hour HTOL devices were electrically tested at room temperature for DC and critical RF parameters.

**Wafer Process: PHEMT-E**

**QTR:** 11014

**Rev: 04**

### **HMC757LP4E Evaluation Test Board**

Figure 1: Eval Board Top View

Figure 2: Eval Board Bottom View

Figure 3: Eval Board Side View

**Wafer Process: PHEMT-E**

**QTR:** 11014

**Rev: 04**

#### **Summary of Results/Conclusions**

All testing is complete. The device meets the requirements for Hittite Reliability Testing.

| TEST                                | QTY<br>IN | QTY<br>OUT | PASS/FAIL | NOTES |

|-------------------------------------|-----------|------------|-----------|-------|

| Initial Electrical Characterization | 70        | 70         | Pass      |       |

| 1000 hour of RF HTOL                | 70        | 70         | Completed |       |

| Post HTOL Electrical Test           | 70        | 70         | Pass      |       |

Failure rate (FIT) calculations using 85°C as the device maximum use temperature and 125°C as the device HTOL temperature resulted in a FIT rate of 472 FIT or a MTTF of 4.88x10<sup>6</sup> hours (559 years) at a 90% confidence level (CL). See Appendix for FIT / MTTF calculations.

**Wafer Process: PHEMT-E**

QTR: 11014

**Rev: 04**

### **Appendix**

#### FIT / MTTF Calculation

Stress conditions:

Qty of Parts Tested = 70 Stress Ambient Temp = 125°C Max Use Ambient Temp = 85°C Activation Energy = 1.3eV

$AF = \exp\left[\left(\frac{E_A}{k}\right) \cdot \left(\left(\frac{1}{T_{USE}}\right) - \left(\frac{1}{T_{STRESS}}\right)\right)\right], \text{ AF=69.7}$ Acceleration Factor (AF):

Calculating the Upper Confidence Bound Failure Rate at 90% CL:

$$\lambda_{CL} = \frac{\chi^2_{\%CL,2f+2} \cdot 10^9}{2 \cdot t \cdot ss \cdot AF}$$

, at 90% CL,

$\lambda_{90\%} = \frac{4.80*109 2*1000*70*69.7}{4.88\times10^6} = 472 \text{ FIT}, \text{ or } 4.88\times10^6 \text{ hours at the maximum use}$

temp of 85°C