# 40V, 2.1A Low Dropout Adjustable Linear Regulator with Monitoring and Cable Drop Compensation

### **FEATURES**

- Wide Input Voltage Range: 1.4V to 40V

- 1 Resistor Sets Output Voltage: 0.4V to 32V

- Output Current: 2.1A

- ±1% Tolerance Over Line, Load and Temperature

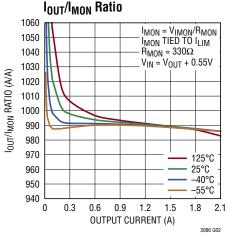

- Output Current Monitor:  $I_{MON} = I_{OUT}/1000$

- Temperature Monitor with Programmable Thermal Limit

- Programmable Cable Drop Compensation

- Parallel Multiple Devices for Higher Current

- Dropout Voltage: 330mV

- 1 Capacitor Soft-Starts Output and Decreases Noise

- Low Output Noise: 40µV<sub>RMS</sub> (10Hz to 100kHz)

- Precision, Programmable External Current Limit

- Power Good Flag with Programmable Threshold

- Ceramic Output Capacitors: 10µF Minimum

- Quiescent Current in Shutdown: <1µA

- Reverse-Battery, -Current and -Output Protection

- Available in 16-Lead TSSOP

### ENHANCED PRODUCT FEATURES

- Supports defense and aerospace applications (AQEC standard)

- Military temperature range (-55°C to 125°C)

- Controlled manufacturing baseline

- One assembly/test site

- One fabrication site

- Product change notification

- Qualification data available on request

### DESCRIPTION

The LT®3086-EP is a multi-feature, low dropout, low noise 2.1A linear regulator that operates over a 1.4V to 40V input supply range. Dropout voltage at 2.1A is typically 330mV. One resistor sets output voltage from 0.4V to 32V. Output voltage tolerance is guaranteed to ±1% over line, load and temperature. The LT3086-EP is stable with ceramic output capacitors, requiring a minimum of 10µF.

The LT3086-EP's programmable cable drop compensation cancels output voltage errors caused by resistive connections to the load. A master/slave configuration allows paralleling of multiple devices for higher load current and heat spreading without external ballast resistor requirements.

Output current and temperature monitoring along with a power good flag provide system diagnostic and debug capability. Internal fault circuitry includes thermal shutdown and current limit with foldback. Thermal limit and current limit are also externally programmable.

The LT3086-EP is available in the thermally enhanced 16-Lead TSSOP package. Additional application and technical information can be found in the LT3086 data sheet.

All registered trademarks and trademarks are the property of their respective owners.

## **APPLICATIONS**

- Programmable Linear Regulator

- Post Regulator for Switching Supplies

- USB Power Supplies

- High Reliability Power Supplies

## **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                            |

|-----------------------------------------------------|

| IN Pin Voltage±45V                                  |

| OUT Pin Voltage±36V                                 |

| Input-to-Output Differential Voltage (Note 2)±45V   |

| SET Pin Voltage0.3, 36V                             |

| SHDN Pin Voltage±45V                                |

| CDC Pin (Internally Clamped, Current into Pin)<8mA  |

| I <sub>MON</sub> Pin Voltage0.3, 7V                 |

| I <sub>LIM</sub> Pin Voltage–0.3, 2V                |

| TRACK Pin Voltage –0.3, Internally Clamped at 1.25V |

| TEMP Pin Voltage0V, 5V                              |

| PWRGD Pin Voltage0.3, 36V                           |

| R <sub>PWRGD</sub> Pin Voltage0.3, 36V              |

| Output Short-Circuit Duration Indefinite            |

| Operating Junction Temperature (Notes 3, 5, 12)     |

| EP-Grade55°C to 125°C                               |

| Storage Temperature Range65 to 150°C                |

| Lead Temperature (Soldering, 10 sec)                |

| (TSSOP)300°C                                        |

|                                                     |

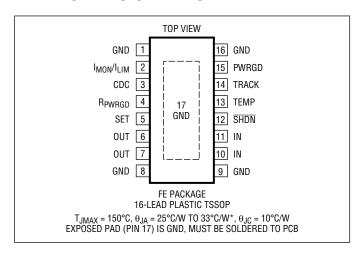

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | PART MARKING | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|--------------|-----------------------|-------------------|

| LT3086FE#Z-EP    | 3086FE-EP    | 16-Lead Plastic TSSOP | –55°C to 125°C    |

| LT3086FE#TRZ-EP  | 3086FE-EP    | 16-Lead Plastic TSSOP | –55°C to 125°C    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ .

| PARAMETER                                                                             |                                      | CONDITIONS                                                                                                                                                                                                                                       |   | MIN                              | TYP                                  | MAX                                | UNITS                      |

|---------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------|--------------------------------------|------------------------------------|----------------------------|

| Minimum Input Voltage (N                                                              | ote 4)                               | $I_{LOAD} = 2.1A$ , $\Delta V_{OUT} = -1\%$                                                                                                                                                                                                      | • |                                  | 1.4                                  | 1.55                               | V                          |

| Reference Voltage<br>(Notes 3, 5)                                                     | V <sub>SET</sub>                     | 1.55V < V <sub>IN</sub> < 40V, 1mA < I <sub>LOAD</sub> < 2.1A (T <sub>J</sub> < 125°C)                                                                                                                                                           | • | 396                              | 400                                  | 404                                | mV                         |

| Reference Current                                                                     | I <sub>SET</sub>                     | 1.55V < V <sub>IN</sub> < 40V, 1mA < I <sub>LOAD</sub> < 2.1A                                                                                                                                                                                    | • | 49.5                             | 50                                   | 50.5                               | μА                         |

| Line Regulation                                                                       | V <sub>SET</sub><br>I <sub>SET</sub> | V <sub>IN</sub> = 1.55V to 40V, I <sub>LOAD</sub> = 1mA (T <sub>J</sub> < 125°C)<br>V <sub>IN</sub> = 1.55V to 40V, I <sub>LOAD</sub> = 1mA                                                                                                      | • | -0.12                            | 0.1<br>-0.03                         | 0.8                                | mV<br>μA                   |

| Load Regulation<br>(Notes 6, 7)                                                       | V <sub>SET</sub><br>I <sub>SET</sub> | $I_{LOAD}$ = 1mA to 2.1A, $V_{IN}$ = $V_{OUT}$ + 0.55V (T <sub>J</sub> < 125°C)<br>$I_{LOAD}$ = 1mA to 2.1A, $V_{IN}$ = $V_{OUT}$ + 0.55V (T <sub>J</sub> < 125°C)                                                                               | • |                                  | 0.25<br>0.02                         | 1<br>0.08                          | mV<br>μA                   |

| Minimum Load Current (No                                                              | ote 16)                              |                                                                                                                                                                                                                                                  | • |                                  |                                      | 1                                  | mA                         |

| Dropout Voltage<br>V <sub>IN</sub> = V <sub>OUT(NOMINAL)</sub> , (Notes 7, 8)         |                                      | I <sub>LOAD</sub> = 1mA                                                                                                                                                                                                                          | • |                                  | 10                                   | 65<br>100                          | mV<br>mV                   |

|                                                                                       |                                      | I <sub>LOAD</sub> = 100mA                                                                                                                                                                                                                        | • |                                  | 100                                  | 135<br>160                         | mV<br>mV                   |

|                                                                                       |                                      | $I_{LOAD} = 500 \text{mA}$                                                                                                                                                                                                                       | • |                                  | 150                                  | 195<br>235                         | mV<br>mV                   |

|                                                                                       |                                      | I <sub>LOAD</sub> = 1.5A                                                                                                                                                                                                                         | • |                                  | 260                                  | 335<br>425                         | mV<br>mV                   |

|                                                                                       |                                      | I <sub>LOAD</sub> = 2.1A                                                                                                                                                                                                                         | • |                                  | 330                                  | 415<br>540                         | mV<br>mV                   |

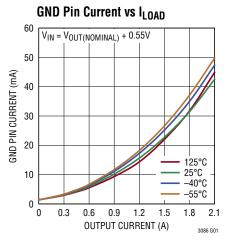

| GND Pin Current<br>V <sub>IN</sub> = V <sub>OUT(NOMINAL)</sub> + 0.55                 | V, (Notes 7, 9)                      | $\begin{split} I_{LOAD} &= 0 \mu A \\ I_{LOAD} &= 1 m A \\ I_{LOAD} &= 100 m A \\ I_{LOAD} &= 500 m A \\ I_{LOAD} &= 1.5 A \\ I_{LOAD} &= 2.1 A \end{split}$                                                                                     | • |                                  | 1.2<br>1.3<br>1.8<br>4.5<br>23<br>44 | 2.4<br>2.6<br>3.6<br>9<br>46<br>88 | mA<br>mA<br>mA<br>mA<br>mA |

| Quiescent Current in Shutdown                                                         |                                      | V <sub>IN</sub> = 40V, V <sub>SHDN</sub> = 0V                                                                                                                                                                                                    |   |                                  | 0.1                                  | 1                                  | μА                         |

| Output Voltage Noise                                                                  |                                      | C <sub>SET</sub> = 0.01μF , C <sub>OUT</sub> = 10μF, I <sub>LOAD</sub> = 2.1A<br>V <sub>OUT</sub> = 5V, BW = 10Hz to 100kHz                                                                                                                      |   |                                  | 40                                   |                                    | μV <sub>RMS</sub>          |

| Shutdown Threshold                                                                    |                                      | V <sub>OUT</sub> = Off to On<br>V <sub>OUT</sub> = On to Off                                                                                                                                                                                     | • | 1.12<br>0.85                     | 1.22<br>1.03                         | 1.32                               | V                          |

| SHDN Pin Current (Note 10<br>1.55V < V <sub>IN</sub> < 40V                            | 0)                                   | V <sub>SHDN</sub> = 0V<br>V <sub>SHDN</sub> = 40V                                                                                                                                                                                                | • |                                  | 15                                   | 1<br>35                            | μA<br>μA                   |

| TEMP Voltage (Note 13)                                                                |                                      | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 125°C                                                                                                                                                                                                  |   |                                  | 0.25<br>1.25                         |                                    | V                          |

| TEMP Error (Note 13)                                                                  |                                      | 0°C < T <sub>J</sub> < 125°C, I <sub>TEMP</sub> = 0<br>0°C < T <sub>J</sub> < 125°C, I <sub>TEMP</sub> = 0μA to 80μA                                                                                                                             |   | -0.09<br>-0.1                    |                                      | 0.09                               | V                          |

| I <sub>TEMP</sub> Thermal Limit Currer                                                | nt Threshold                         | 25°C < T <sub>J</sub> < 125°C                                                                                                                                                                                                                    |   | 95                               | 100                                  | 105                                | μA                         |

| I <sub>MON</sub> Output Current<br>V <sub>IN</sub> = V <sub>OUT(NOMINAL)</sub> + 0.55 | V (Note 15)                          | $\begin{array}{l} I_{LOAD} = 20 mA,  R_{MON} = 1 k\Omega \\ I_{LOAD} = 500 mA,  R_{MON} = 330 \Omega \\ I_{LOAD} = 1 A,  R_{MON} = 330 \Omega \\ I_{LOAD} = 1.5 A,  R_{MON} = 330 \Omega \\ I_{LOAD} = 2.1 A,  R_{MON} = 330 \Omega \end{array}$ | • | 5<br>440<br>0.95<br>1.43<br>2.02 | 20<br>500<br>1.00<br>1.50<br>2.10    | 75<br>560<br>1.05<br>1.57<br>2.18  | μΑ<br>μΑ<br>mA<br>mA       |

| Output Current Sharing Err                                                            |                                      | $R_{MON} = 330\Omega$ , $I_{OUT(MASTER)} = 2.1A$                                                                                                                                                                                                 |   | -10                              | 0                                    | 10                                 | %                          |

| TRACK Pin Pull-Up Current                                                             |                                      | V <sub>TRACK</sub> = 750mV                                                                                                                                                                                                                       | • | 7                                | 15                                   | 25                                 | μA                         |

| R <sub>PWRGD</sub> Reference Voltage                                                  |                                      | 1.55V < V <sub>IN</sub> < 40V                                                                                                                                                                                                                    | • | 390                              | 400                                  | 410                                | mV                         |

| R <sub>PWRGD</sub> Reference Current                                                  |                                      | 1.55V < V <sub>IN</sub> < 40V                                                                                                                                                                                                                    | • | 48.75                            | 50                                   | 51.25                              | μA                         |

| R <sub>PWRGD</sub> Reference Voltage                                                  | Hysteresis                           | 1.55V < V <sub>IN</sub> < 40V                                                                                                                                                                                                                    |   |                                  | 2.4                                  |                                    | mV                         |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| PARAMETER                                       | CONDITIONS                                                                                                    |   | MIN        | TYP   | MAX   | UNITS  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---|------------|-------|-------|--------|

| R <sub>PWRGD</sub> Reference Current Hysteresis | 1.55V < V <sub>IN</sub> < 40V                                                                                 |   |            | 300   |       | nA     |

| PWRGD V <sub>OL</sub>                           | I <sub>PWRGD</sub> = 200μA (Fault Condition)                                                                  | • |            | 55    | 200   | mV     |

| PWRGD Internal Time Delay                       | V <sub>OL</sub> TO V <sub>OH</sub> (Rising Edge)                                                              | • | 8          | 17    | 25    | μs     |

| PWRGD Pin Leakage Current                       | V <sub>PWGRD</sub> = 32V, V <sub>RPWGRD</sub> = 500mV                                                         | • |            |       | 1     | μА     |

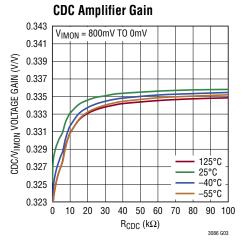

| CDC Reference Voltage                           | 1.55V < V <sub>IN</sub> < 40V, I <sub>MON</sub> = 0V                                                          | • | 390        | 400   | 410   | mV     |

| CDC/V <sub>IMON</sub> Voltage Gain              | $1.55V < V_{IN} < 40V, 0 < I_{CDC} < 20\mu A, V_{IMON} = 800 mV to 0$                                         | • | 0.320      | 0.333 | 0.343 | V/V    |

| Ripple Rejection                                | $V_{IN} = 1.9V \text{ (AVG)}, V_{RIPPLE} = 0.5V_{P-P}, V_{OUT} = 1V$<br>$f_{RIPPLE} = 120Hz, I_{LOAD} = 2.1A$ |   | 65         | 80    |       | dB     |

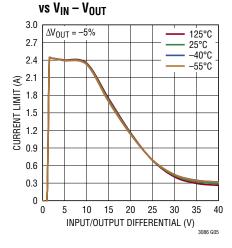

| Internal Current Limit                          | $V_{IN} = 1.55V$<br>$V_{IN} = V_{OUT(NOMINAL)} + 0.55V$ (Notes 7, 12), $\Delta V_{OUT} = -5\%$                | • | 2.2<br>2.2 | 2.4   | 2.9   | A<br>A |

| I <sub>LIM</sub> Threshold Voltage              | 1.55V < V <sub>IN</sub> < 40V                                                                                 | • | 775        | 800   | 825   | mV     |

| Input Reverse-Leakage Current                   | $V_{IN} = -40V, V_{OUT} = 0$                                                                                  | • |            |       | 2     | mA     |

| Reverse-Output Current (Note 11)                | $V_{OUT} = 32V, V_{IN} = 0, V_{\overline{SHDN}} = 0$                                                          |   |            | 1     | 10    | μA     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Absolute maximum input-to-output differential voltage is not achievable with all combinations of rated IN pin and OUT pin voltages. With the IN pin at 45V, the OUT pin may not be pulled below 0V. The total IN to OUT differential voltage must not exceed ±45V.

**Note 3:** The LT3086-EP is tested and specified under pulse load conditions such that  $T_J \cong T_A$ . The LT3086-EP is 100% tested over the  $-55^{\circ}$ C to 125°C operating junction temperature range. High junction temperatures degrade operating lifetimes. Operating lifetime is derated at junction temperatures greater than 125°C.

**Note 4:** The LT3086-EP is tested and specified for these conditions with the SET pin connected to the OUT pin,  $V_{OUT} = 0.4V$ .

**Note 5:** Maximum junction temperature limits operating conditions. The regulated output voltage specification does not apply for all possible combinations of input voltage and output current. Limit the output current range if operating at large input-to-output voltage differentials. Limit the input-to-output voltage differential if operating at maximum output current. Current limit foldback limits the maximum output current as a function of input-to-output voltage. See Current Limit vs  $V_{\text{IN}} - V_{\text{OUT}}$  in the Typical Performance Characteristics section.

Note 6: Load regulation is Kelvin-sensed at the package.

**Note 7:** To satisfy minimum input voltage requirements, the LT3086-EP is tested and specified for these conditions with a 32k resistor between OUT and SET for a 2V output voltage.

**Note 8:** Dropout voltage is the minimum input-to-output voltage differential needed to maintain regulation at a specified output current. In dropout, the output voltage equals:  $(V_{IN} - V_{DROPOUT})$ . For low output voltages and certain load conditions, minimum input voltage requirements limit dropout voltage. See the Minimum Input Voltage curve in the Typical Performance Characteristics section.

**Note 9:** GND pin current is tested with  $V_{IN} = V_{OUT(NOMINAL)} + 0.55V$  and PWRGD pin floating. GND pin current increases in dropout. See GND pin current curves in the Typical Performance Characteristics section and the LT3086 data sheet.

Note 10: SHDN pin current flows into the SHDN pin.

**Note 11:** Reverse-output current is tested with the IN pin grounded and the OUT pin forced to a voltage. The current flows into the OUT pin and out of the GND pin.

**Note 12:** The IC includes overtemperature protection circuitry that protects the device during momentary overload conditions. Junction temperature exceeds 125°C when the overtemperature circuitry is active unless thermal limit is externally set by loading the TEMP pin. Continuous operation above the specified maximum junction temperature may impair device reliability.

**Note 13:** The TEMP output voltage represents the average die temperature next to the power transistor while the center of the transistor can be significantly hotter during high power conditions. Due to power dissipation and temperature gradients across the die, the TEMP output voltage measurement does not guarantee that absolute maximum junction temperature is not exceeded.

Note 14: Output current sharing error is the difference in output currents of a slave relative to its master when two LT3086-EP regulators are paralleled. The device is tested as a slave with  $V_{TRACK}=0.693V,\ R_{MON}=330\Omega$  and  $V_{SET}=0.4V,$  conditions when an ideal master is outputting 2.1A. The specification limits account for the slave output tracking error from 2.1A and the worst-case error that can be contributed by a master: the maximum deviation of  $V_{SET}$  from 0.4V and  $I_{MON}$  from 2.1mA.

**Note 15:** The LT3086-EP is tested and specified for these conditions with the  $I_{MON}$  and  $I_{LIM}$  pins tied together.

Note 16: The LT3086-EP requires a minimum load current to ensure proper regulation and stability.

### TYPICAL PERFORMANCE CHARACTERISTICS

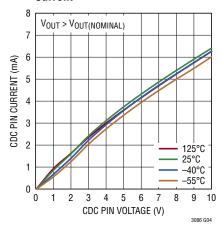

#### CDC Pin Internal Clamp Fault Current

## Internal Current Limit

### PIN FUNCTIONS (TSSOP)

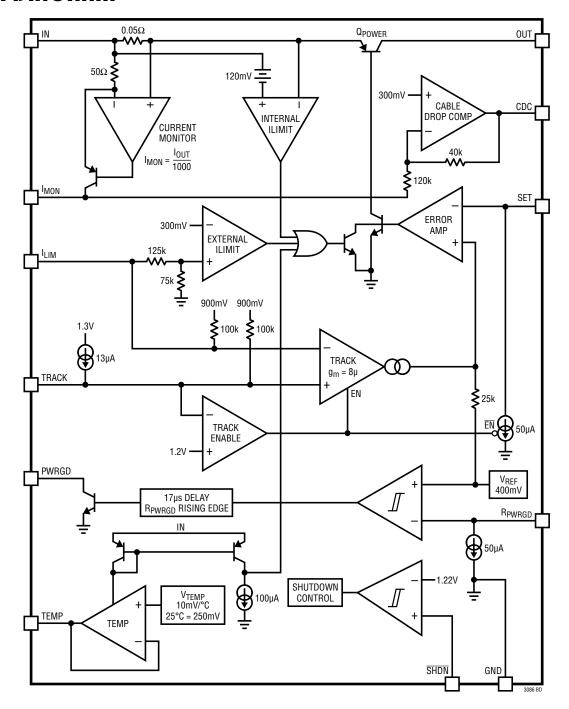

**GND** (Pins 1, 8, 9, 16, Exposed Pad Pin 17): Ground. The exposed pad of the TSSOP package is an electrical connection to GND. To ensure proper electrical and thermal performance, tie the exposed pad or tab directly to the remaining GND pins of the relevant package and the PCB ground. GND pin current is typically 1.2mA at zero load and increases to about 44mA at full load.

**I**<sub>LIM</sub> (**Pin 2**): External Current Limit Programming. This pin externally programs current limit if connected to  $I_{MON}$  and a resistor to GND. Current limit activates if the voltage at  $I_{LIM}$  equals 0.8V. Current limit equals: 1000 • (0.8V/R<sub>MON</sub>). An internal clamp typically limits the  $I_{LIM}$  voltage to 1V. If external current limit is set to less than 1A, connect a series 1k-10nF network in parallel with the  $R_{MON}$  resistor for stability. Internal current limit foldback overrides externally programmed current limit if  $V_{IN} - V_{OUT}$  differential voltage is excessive. If external current limit programming is not used, then ground this pin.

$I_{MON}$  (Pin 2): Output Current Monitor. This pin sources a current equal to 1/1000 of output load current. Connecting a resistor from  $I_{MON}$  to GND programs a load current dependent voltage for monitoring by an ADC. If  $I_{MON}$  connects to  $I_{LIM}$ , current limit is externally programmable.

**CDC** (**Pin 3**): Cable Drop Compensation. Connecting a single resistor ( $R_{CDC}$ ) between the CDC and SET pins provides programmable cable drop compensation that cancels output voltage errors caused by resistive connections to the load. A resistor ( $R_{MON}$ ) from  $I_{MON}$  to GND is also required to enable Cable Drop Compensation. Choose  $R_{MON}$  first based on required current limit.

$R_{MON} = 0.8V \bullet 1000/I_{LIM}$

Calculate the value of R<sub>CDC</sub> with this formula:

$R_{CDC} = (R_{MON} \cdot R_{SET})/(3000 \cdot R_{WIRE})$

where  $R_{WIRE}$  is the total cable or wire resistance to and from the load. From a practical application standpoint, LTC recommends limiting cable drop compensation to 20% of  $V_{OUT}$  for applications needing good regulation. The limiting factor is variations in wire temperature as copper wire resistance changes about 19% for a 50°C temperature change. If output regulation requirements

are loose (e.g., when using a secondary regulator), cable drop compensation of up to 50% may be used.

**RPWRGD** (**Pin 4**): Power Good Threshold Voltage Programming. This pin is the input to the power good comparator. Connecting a resistor between OUT and RPWRGD programs an adjustable power good threshold voltage. The threshold voltage is 0.4V on the RPWRGD pin, and a 50 $\mu$ A current source is connected from RPWRGD to GND. If the voltage at RPWRGD is less than 0.4V, the PWRGD flag asserts and pulls low. If the voltage at RPWRGD is greater than 0.4V, the PWRGD flag de-asserts and becomes high impedance. For most applications, PWRGD is pulled high with a pull-up resistor. Calculate the value of RPWRGD with this formula:

$R_{PWRGD} = (X \bullet V_{OUT(NOMINAL)} - 0.4V)/50\mu A$  where X is normally in the 85% to 95% range.

A 17 $\mu$ s deglitching filter suppresses false tripping of the PWRGD flag at the rising edge of PWRGD with instant reset. Hysteresis at the R<sub>PWRGD</sub> pin is typically 0.6% on the 0.4V threshold and the 50 $\mu$ A current source.

**SET (Pin 5):** Output Voltage Programming. This pin is the error amplifier's inverting terminal. It regulates to 0.4V and a 50µA current source is connected from SET to GND. Connecting a single resistor from OUT to SET programs output voltage. Calculate the value of the required resistor from the formula:

$$R_{SET} = (V_{OUT} - 0.4V)/50\mu A$$

Connecting a capacitor in parallel with R<sub>SET</sub> provides output voltage soft-start capability, improves transient response and decreases output voltage noise.

The LT3086-EP error amplifier design is configured so that the regulator always operates in unity-gain.

**OUT (Pins 6, 7):** Output. These pin(s) supply power to the load. Connect all OUT pins together on the DHD and FE packages for proper operation. Stability requirements demand a minimum  $10\mu\text{F}$  ceramic output capacitor with an ESR less than  $100\text{m}\Omega$  to prevent oscillations. Large load transients require larger output capacitance to limit peak voltage transients. Permissible output voltage range is 0.4V to 32V. **The LT3086-EP requires a 1mA minimum load current to ensure proper regulation and stability.**

Rev. 0

## PIN FUNCTIONS (TSSOP)

**IN (Pins 10, 11):** Input. These pin(s) supply power to the device. Connect all IN pins together for proper operation. The LT3086-EP requires a local IN bypass capacitor if it is located more than a few inches from the main input filter capacitor. In general, battery output impedance rises with frequency, so adding a bypass capacitor in battery powered circuits is advisable. A 10μF minimum input capacitor generally suffices. The IN pin(s) withstand a reverse voltage of 45V. The device limits current flow and no negative voltage appears at OUT. The device protects itself and the load against batteries that are plugged in backwards.

SHDN (Pin 12): Shutdown/UVLO. Pulling the SHDN pin typically below 1V puts the LT3086-EP into a low power state and turns the output off. Quiescent current in shutdown is typically less than 1μA. The SHDN pin turn-on threshold is typically 1.22V. This pin may either be used as a shutdown function or as an undervoltage lockout function. If using this pin as an undervoltage lockout function, use a resistor divider between IN and GND with the tap point tied to SHDN. If using the pin as a shutdown function, drive the pin with either logic or an open-collector/drain with a pull-up resistor. The resistor supplies the pull-up current to the open-collector/drain logic, normally several microamperes, and the SHDN pin current, typically less than 10μA at 6V. If unused, connect the SHDN pin to IN.

**TEMP (Pin 13):** Die Junction Temperature. This pin outputs a voltage indicating the LT3086-EP average die junction temperature. At 25°C, this pin typically outputs 250mV. The TEMP pin slope equals 10mV/°C so that at 125°C, this pin typically outputs 1.25V. This pin does not read temperatures less than 0°C. The TEMP pin is not meant to be an accurate temperature sensor, but is useful for debug, monitoring and calculating thermal resistance of the package mounted to the PCB. The TEMP pin also incorporates the ability to program a thermal limit temperature lower than the internal typical thermal shutdown temperature of 165°C. Tying a resistor from TEMP to GND

programs the thermal limit temperature with a  $100\mu A$  trip point. Calculate the value of the resistor from the formula:

$$R_{TEMP} = \frac{\left(T_{SHDN} \bullet \frac{10mV}{^{\circ}C}\right)}{100\mu A}$$

where  $T_{SHDN}$  is the desired die thermal limit temperature.

There are several degrees of hysteresis in the thermal shutdown that cycles the regulator output on and off. Limit the capacitance on the TEMP pin to less than 100pF. To prevent saturation in the TEMP output device, ensure that  $V_{\text{IN}}$  is higher than  $V_{\text{TEMP}}$  by 250mV.

**TRACK (Pin 14):** Track pin for paralleling. The TRACK pin allows multiple LT3086-EPs to be paralleled in a master/ slave(s) configuration for higher output current applications. This also allows heat to be spread out on the PCB. This circuit technique does not require ballast resistors and does not degrade load regulation. Tying the TRACK pin of the slave device(s) to the  $I_{MON}/I_{LIM}$  pins of the master device enables this function. If the TRACK function is unused, TRACK is in a default clamped high state. A TRACK pin voltage below 1.2V on slave device (s) shuts off the internal  $50\mu$ A reference current at SET such that only the  $50\mu$ A reference current of the master device is active. All SET pins must be tied together in a master/ slave configuration.

**PWRGD (Pin 15):** Power Good Flag. The PWRGD pin is an open-collector logic pin connected to the output of the power good comparator. PWRGD asserts low if the  $R_{PWRGD}$  pin is less than 400mV. The maximum low output level of 200mV over temperature is defined for 200 $\mu$ A of sink current. If  $R_{PWRGD}$  is greater than 400mV, the PWRGD pin de-asserts and becomes high impedance. The PWRGD pin may be pulled to 36V without damaging any internal circuitry regardless of the input voltage.

# **BLOCK DIAGRAM**

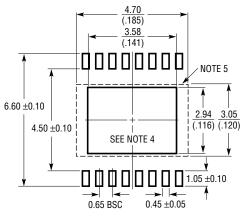

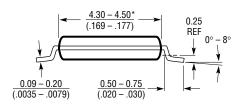

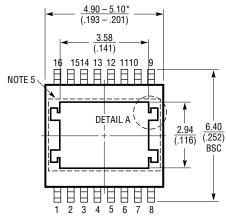

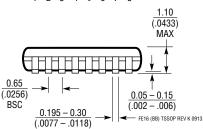

### PACKAGE DESCRIPTION

#### FE Package 16-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1663 Rev K) **Exposed Pad Variation BB**

RECOMMENDED SOLDER PAD LAYOUT

- 1. CONTROLLING DIMENSION: MILLIMETERS

- 2. DIMENSIONS ARE IN MILLIMETERS

- 3. DRAWING NOT TO SCALE

- 4. RECOMMENDED MINIMUM PCB METAL SIZE FOR EXPOSED PAD ATTACHMENT

- 5. BOTTOM EXPOSED PADDLE MAY HAVE METAL PROTRUSION IN THIS AREA. THIS REGION MUST BE FREE OF ANY EXPOSED TRACES OR VIAS ON PBC LAYOUT

TYP

\*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.150mm (.006") PER SIDE

DETAIL A IS THE PART OF THE LEAD FRAME FEATURE FOR REFERENCE ONLY

NO MEASUREMENT PURPOSE