### DICE/DWF SPECIFICATION

## LTC1530 High Power Synchronous Switching Regulator Controller

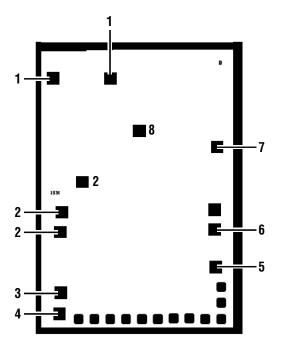

#### PAD FUNCTION

| 1. | P <sub>VCC</sub>   |

|----|--------------------|

| 2. | GND                |

| 3. | V <sub>SENSE</sub> |

| 4. | COMP               |

| 5. | I <sub>MAX</sub>   |

| 6. | I <sub>FB</sub>    |

| 7. | G2                 |

| 8. | G1                 |

#### **DIE CROSS REFERENCE**

| LTC <sup>®</sup> Finished | Order       |

|---------------------------|-------------|

| Part Number               | Part Number |

| LTC <sup>®</sup> 1530     | LTC1530DICE |

| LTC1530                   | LTC1530DWF* |

Please refer to ADI standard product data sheet for other applicable product information. \*DWF = DICE in wafer form.

101mils × 70mils, 12mils thick. Backside metal: Alloyed gold layer Backside potential: Connect to GND

All registered trademarks and trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage                 |                         |

|--------------------------------|-------------------------|

| PV <sub>CC</sub>               | 14V                     |

| Input Voltage                  |                         |

| I <sub>FB</sub> (Note 2)       | PV <sub>CC</sub> + 0.3V |

| I <sub>MAX</sub>               | –0.3V to 14V            |

| IFB Input Current (Notes 2, 3) | –100mA                  |

# DICE/DWF SPECIFICATION

# LTC1530

### **DICE/DWF ELECTRICAL TEST LIMITS** $T_A = 25^{\circ}C$ . PV<sub>CC</sub> = 12V, unless otherwise noted.

| SYMBOL                          | PARAMETER                         | CONDITIONS                        | MIN   | MAX   | UNITS    |

|---------------------------------|-----------------------------------|-----------------------------------|-------|-------|----------|

| PV <sub>CC</sub>                | Supply Voltage                    | (Note 6)                          |       | 13.2  | V        |

| V <sub>UVLO</sub>               | Undervoltage Lockout Voltage      | (Note 7)                          |       | 3.75  | V        |

| V <sub>SENSE</sub>              | Internal Feedback Voltage         | (Note 4)                          | 1.223 | 1.247 | V        |

| IPVCC                           | Quiescent Current                 | COMP = 0.5V, V <sub>FB</sub> = 5V |       | 1.4   | mA       |

|                                 | Shutdown Supply Current           | COMP = 0 (Note 8)                 |       | 80    | μA       |

| f <sub>OSC</sub>                | Internal Oscillator Frequency     |                                   | 250   | 350   | kHz      |

| G <sub>ERR</sub>                | Error Amplifier Open-Loop DC Gain | (Note 5)                          | 40    |       | dB       |

| <b>9</b> mERR                   | Error Amplifier Transconductance  | (Note 5)                          | 1.6   | 2.8   | millimho |

| I <sub>MAX</sub>                | I <sub>MAX</sub> Sink Current     | V <sub>IMAX</sub> = 5V            | 170   | 230   | μA       |

| V <sub>SHDN</sub>               | Shutdown Threshold Voltage        | Measured at COMP Pin (Note 7)     | 100   |       | mV       |

| t <sub>r</sub> , t <sub>f</sub> | Driver Rise and Fall Time         |                                   |       | 140   | ns       |

| t <sub>NOL</sub>                | Driver Nonoverlap Time            |                                   | 30    |       | ns       |

| DC <sub>MAX</sub>               | Maximum G1 Duty Cycle             |                                   | 81    |       | %        |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** If I<sub>FB</sub> is taken below GND, it is clamped by an internal diode. This pin handles input currents  $\leq$  100mA below GND without latch-up. In the positive direction, it is not clamped to PV<sub>CC</sub>.

**Note 3:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

**Note 4:** The LTC1530 is tested in an op amp feedback loop which regulates  $V_{SENSE}$  based on  $V_{COMP}$  = 2V for the error amplifier.

Note 5: The Open-loop DC gain and transconductance from the  $V_{FB}$  pin to the COMP pin are  $G_{ERR}$  and  $g_{mERR}$  respectively.

**Note 6:** The total voltage from the  $PV_{CC}$  pin to the GND pin must be  $\ge 8V$  for the current limit protection circuit to be active.

Note 7: G1 and G2 begin to switch once  $\mathsf{PV}_{CC}$  is  $\geq$  the undervoltage lockout threshold voltage.

Note 8: The LTC1530 enters shutdown if COMP is pulled low.

Wafer level testing is performed per the indicated specifications for dice. Considerable differences in performance can often be observed for dice versus packaged units due to the influences of packaging and assembly on certain devices and/or parameters. Please consult factory for more information on dice performance and lot qualifications via lot sampling test procedures.

Dice data sheet subject to change. Please consult factory for current revision in production.

I.D.No. 66-13-1530