#### LTC3546EUFD

## DESCRIPTION

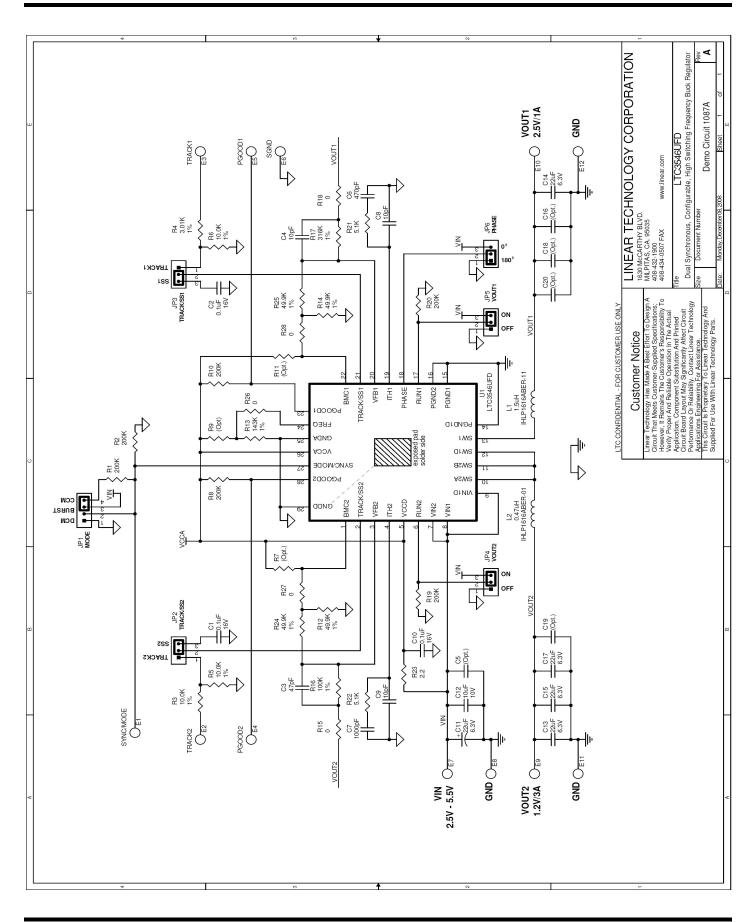

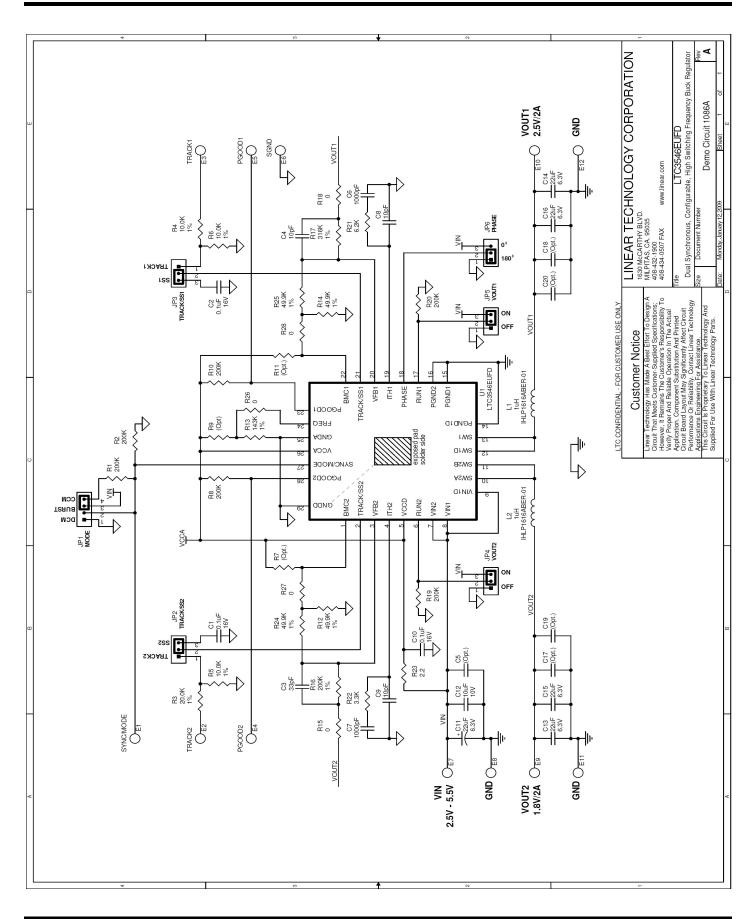

Demonstration circuits 1086/7A are dual synchronous, configurable, high switching frequency buck regulators featuring the LTC3546EUFD. The two different demonstration circuits show the current partitioning capability of the LTC3546EUFD to create either two 2A outputs (DC1086A) or one 3A and one 1A output (DC1087A), just by changing a single pin connection.

The main features of the board are separate RUN, soft start and PGOOD pins for each output and a Mode selector that allow the converter to run in CCM, DCM or Burst Mode operation. Synchronization to an external clock is also possible through some minor component changes. Both boards have an input voltage range of 2.5V to 5.5V. In Burst Mode operation, the DC supply current is typically only 240 $\mu$ A at no load, and less than 1 $\mu$ A in shutdown. The entire circuit, including the output capacitors, fit within a 0.95" X 0.6" area on the top layer and is only 1.2mm high. The package style for the LTC3456EUFD is a 4mm x 5mm plastic QFN.

The LTC3546EUFD datasheet gives a complete description of the part, operation and application information and must be read in conjunction with this quick start guide for demo circuits 1086/7A.

# Design files for this circuit board are available. Call the LTC factory.

Burst Mode is a trademark of Linear Technology Corporation

| PARAMETER                   | CONDITION                                            | DC1086A     |          | DC1087A  |          |

|-----------------------------|------------------------------------------------------|-------------|----------|----------|----------|

|                             |                                                      | Vout1       | Vout2    | Vout1    | Vout2    |

| Input Voltage Range         |                                                      | 2.5V – 5.5V |          |          |          |

| Maximum Output Current      | V <sub>IN</sub> = 2.5V to 5.5V                       | 2A          | 2A       | 1A       | 3A       |

| Output Voltage              | $V_{IN}$ = 2.8V to 5.5V, $I_{OUT}$ = 0A to max. load | 2.5V ±2%    | 1.8V ±2% | 2.5V ±2% | 1.2V ±2% |

| Nominal Switching Frequency | $R_{\tau} = 143 k\Omega$                             | 1500kHz     |          |          |          |

| Typical Efficiency          | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = Full load   | 87%         | 83%*     | 87%*     | 77%*     |

|                             | $V_{IN}$ = 3.3V, $I_{OUT}$ = Full load               | 86%**       |          | 87%*     |          |

| See Figures 3 – 6           | $V_{IN}$ = 2.5V, $I_{OUT}$ = Full load               |             | 79%*     |          | 74%*     |

Table 1. Performance Summary  $(T_A = 25^{\circ}C)$

$^{*}\mbox{Up}$  to 2% higher efficiency is possible with alternative higher profile inductors – see Table 2

# **OPERATING PRINCIPLES**

A unique feature of the LTC3546EUFD is the flexible current partitioning. The LTC3546EUFD has two independently regulated outputs that can deliver up to 2A and 1A due to the 90m $\Omega$  and 180m $\Omega$  internal power MOSFET switches. An additional 1A output, with 180m $\Omega$  internal power MOSFET switches, can be paralleled to either of

the outputs to produce either a 3A/1A or a 2A/2A dual output regulator. This external connection is internally detected and the dependent output is automatically gated in accordance to the connected output — nothing more is required.

# **QUICK START PROCEDURE**

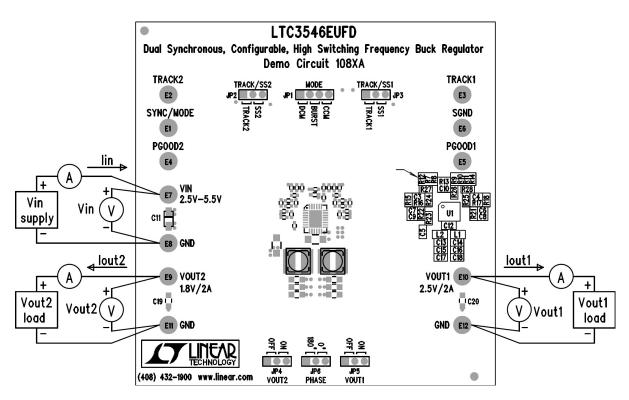

Demonstration circuits 1086/7A are easy to set up to evaluate the performance of the LTC3546EUFD. Refer to 0 for proper measurement equipment setup and follow the procedure below:

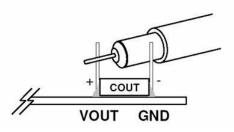

**NOTE:** When measuring the input or output voltage ripple, care must be taken to avoid a long ground lead on the oscilloscope probe. Measure the input or output voltage ripple by touching the probe tip directly across the input or output ceramic capacitors. See Figure 2 for proper scope probe technique.

1. Place jumpers in the following positions:

| JP1 | CCM <b>JP2</b> | SS2 |      |

|-----|----------------|-----|------|

| JP3 | SS1            | JP4 | ON   |

| JP5 | ON             | JP6 | 180° |

2. With power off, connect the input power supply to  $V_{\mbox{\tiny IN}}$  and GND.

3. Turn on the power at the input.

**NOTE:** Make sure that the input voltage does not exceed 5.5V.

4. Check for the proper output voltages.

V<sub>0UT1</sub> = 2.450V to 2.550V (Both DC1086/7A)

$V_{out2} = 1.764V$  to 1.836V (DC1086A)

$V_{0UT2} = 1.176V$  to 1.224V (DC1087A)

**NOTE:** If there is no output, temporarily disconnect the load to make sure that the load is not set too high.

5. Once the proper output voltages are established, adjust the loads within the operating range and observe the output voltage regulation, ripple voltage, efficiency and other parameters.

Figure 1. Proper Measurement Equipment Setup

Figure 2. Measuring Input or Output Ripple Directly Across Ceramic Capacitor

#### **OPTIONS**

The demonstration circuits 1086/7 are optimized for low profile with a maximum component height of 1.2mm. This height limitation affects the inductor selection and can limit the circuit efficiency. If a higher efficiency is required and the height limitation can be relaxed, alternative inductors can be selected. In the list of a few alternative components to improve overall efficiency is given in Table 2.

Table 2. Alternative inductor selections for improved efficiency

|                                  | DC1086A           |                   | DC1087A           |                   |                                            |

|----------------------------------|-------------------|-------------------|-------------------|-------------------|--------------------------------------------|

| MANUFACTURER                     | V <sub>OUT1</sub> | V <sub>OUT2</sub> | V <sub>out1</sub> | V <sub>OUT2</sub> | COMMENTS                                   |

| Würth Electronik - PD2-MS Series | 1.2 µH            | 1.2 µH            | 0.56 µH           | 1.7 µH            | 5mm x 6mm x 2mm high                       |

| Cooper Bussmann – SDxx Series    | SD20 -<br>1.2 μΗ  | SD20 - 1.2<br>μΗ  | SD25 -<br>0.47 μΗ | SD12 -<br>1.5 μΗ  | 5.2mm x 5.2mm, height determined by series |

| Sumida – CDRH4D29LD Series       | 1.5 µH            | 1.5 µH            | 0.8 µH            | 2.2 µH            | 4.9mm x 4.9mm x 3mm high                   |

## FREQUENCY SYNCHRONIZATION

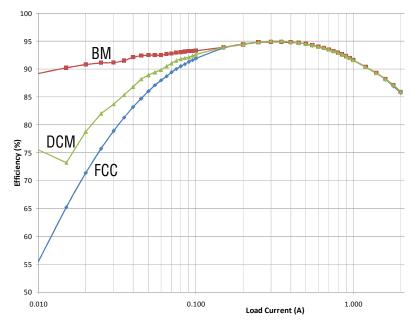

Demonstration circuits 1086/7A's Mode selector allows the converter to run in CCM, DCM or Burst Mode operation by changing position of jumper JP1. For synchronizing to an external clock source, however, some bench modification is needed. Refer to Table 3 and to the data sheet for more details. Please note that the LTC3546EUFD will operate in DCM mode when synchronized to an external clock.

Table 3. Free Running and Synchronized Operation Options

|                                | FREQ PIN COMPONENTS |       | MODE SELECTOR                          |  |

|--------------------------------|---------------------|-------|----------------------------------------|--|

| CONFIGURATION                  | R13                 | R26   | JP1                                    |  |

| Free Running                   | 143kΩ               | 0Ω    | CCM, DCM or Burst Mode                 |  |

| Synchronized to External Clock | 100pF               | 200kΩ | CCM and clock applied to Sync/Mode pin |  |

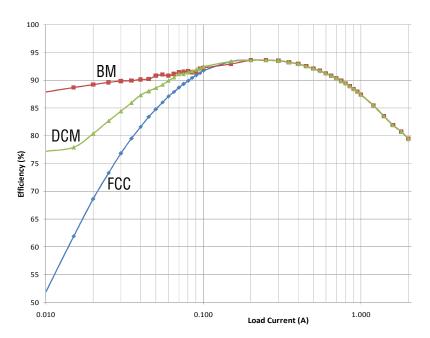

Figure 3. Efficiency vs. load current for different operating modes, DC1086A,  $V_{IN} = 3.3V$ ,  $V_{outri} = 2.5V$

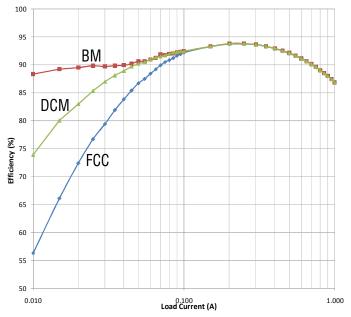

Figure 4. Efficiency vs. load current for different operating modes, DC1086A,  $V_{IN} = 2.5V$ ,  $V_{OUT2} = 1.8V$

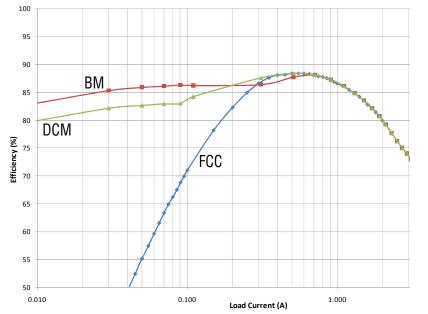

Figure 5. Efficiency vs. load current for different operating modes, DC1087A,  $V_{\mu}$  = 3.3V,  $V_{\alpha\mu\tau}$  = 2.5V

Figure 6. Efficiency vs. load current for different operating modes, DC1087A,  $V_{IN} = 2.5V$ ,  $V_{OUT2} = 1.2V$

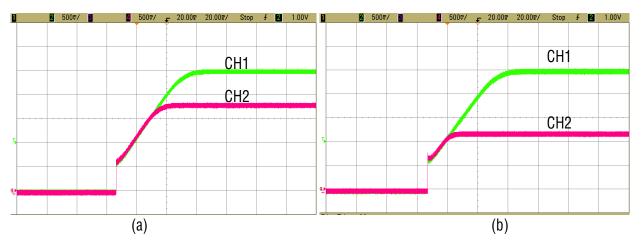

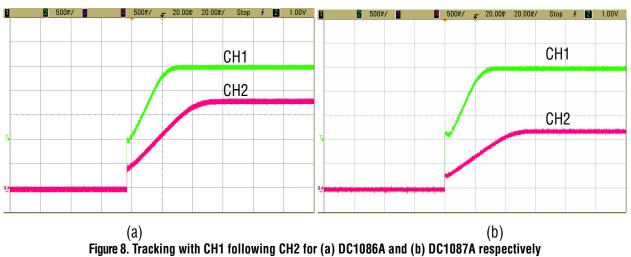

## TRACKING BETWEEN CHANNELS

It is possible to have either of the two output channels act as master to the other channel during startup. In this configuration, the other channel will either ramp coincidental to the master (if it is a lower output voltage), or ramp in a similarly scaled manner. For Demonstration Circuits 1086/7A this is accomplished by tying the output of the Master channel to the Track pin of the opposite channel, and changing the appropriate jumper (JP2 or JP3) to the track position. Please refer to Table 4 and the datasheet for more detail.

|               | CHANNEL CONFIGURATION |       | JUMPER SELECTION |        | EXTERNAL CONNECTION       |

|---------------|-----------------------|-------|------------------|--------|---------------------------|

| TRACKING MODE | MASTER                | SLAVE | JP2              | JP3    |                           |

| Coincidental  | CH1                   | CH2   | TRACK2           | SS1    | Vout1 connected to TRACK2 |

| Scaled ramp   | CH2                   | CH1   | SS2              | TRACK1 | Vout2 connected to TRACK1 |

#### Table 4. Configuration for Tracking between Channels

Figure 7. Tracking with CH2 following CH1 for (a) DC1086A and (b) DC1087A respectively

7