# Surge Stopper IC Protects Loads From >500V Power Supply Surges

Electronic equipment is vulnerable to surges applied to system power supplies, which can affect associated loads and cause system and component failure. To combat this, a recently-introduced "surge stopper" IC interfaces between a system power supply and its loads, protecting against input voltage surges.

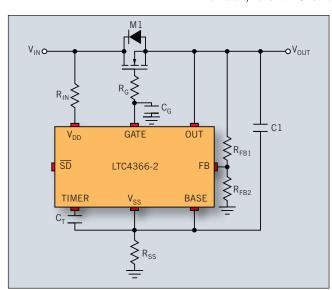

he LTC4366 protects against surges by controlling the gate of an external N-channel MOSFET so that it can absorb the surge and protect the loads. Normally, the IC and MOSFET allow the power supply to service its loads with minimal insertion loss. However, if the power supply input receives a surge voltage, the LTC4366 (*Fig. 1*) and MOSFET clamp the voltage applied to the loads to protect from damage or failure. It is intended for automotive, avionic and industrial applications with an operating temperature range of -40°C to +150°C.

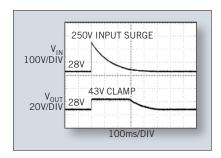

An  $R_{SS}$  resistor in its return line ( $V_{SS}$ ) isolates the LTC4366 and allows it to float up with the system supply input ( $V_{IN}$ ). Thus, the LTC4366 protects systems that continuously operate above 100V, or require protection from extremely high voltage transients (>200V). Its topology, external MOSFET, and external voltage dropping resistor ( $R_{SS}$ ) allow it to float. The upper voltage protection limit depends on the  $R_{IN}$  resistor value and the selected MOSFET's ability to handle the power dissipated during an input voltage surge. As an example, *Fig. 2* shows a 250V input surge and the corresponding clamped output produced by the LTC4366 circuit.

This floating topology allows the LTC4366 to operate from 9V to >500V inputs. Its adjustable, well-regulated output clamp voltage provides flexibility to control the clamped output voltage level without affecting system operation. This lowers costs for low voltage applications, because it eliminates the need for high-voltage rated components downstream.

There are two LTC4366 versions that differ in their response to faults. After a fault, the LTC4366-1 latches off while the LTC4366-2 will auto-retry. The

LTC4366-1 and MOSFET will remain off after a fault until the  $\overline{\text{SD}}$  pin is toggled low and then high. After clearing the fault, the LTC4366-1 GATE turns the MOSFET on again. In contrast, the LTC4366-2 waits 9 seconds, then automatically clears the fault and restarts. During a fault, strong sink current pull-down (>150mA) on the GATE pin ensures fast response time.

An adjustable fault timer limits power dissipation in the external MOSFET. During a fault it uses a current source to charge the capacitor  $(C_T)$  on the TIMER pin  $(Fig.\ I)$ , which allows use of lower rated SOA (safe operating area) MOSFETs. Inrush current limiting eliminates current spikes propagating through the MOSFET to the output during power-up by controlling the GATE pin slew rate.

When shut down,the LTC4366 turns off the MOSFET by tying the GATE and OUT pins together with a switched resistor to reduce current consumption to less an  $20\mu A$ . In automotive applications, the low shutdown current minimizes the battery's discharge when parked for long periods.

Fig. 1. Typical LTC4366-2 28V input circuit.

Fig. 2. LTC4366 output voltage is clamped at 43V with a 250V power supply input surge.

Also, it offers additional power savings for improved battery life in portable applications.

#### THREE MODES

The LTC4366 has three operating modes: start, run and regulate (the surge). In run and regulate modes, the IC receives most of its power from the output, so the MOSFET isolates the surge from the IC's power pins. This allows surge voltages up to the breakdown voltage of the external MOSFET.

In the start mode, a  $15\mu A$  trickle current flows through  $R_{IN}$ , with half used to charge the gate with the other half used as bias current. As the GATE pin charges, the external MOSFET brings up the OUT pin. This leads to the run mode where the output is high enough to power a charge pump that operates the MOSFET's gate 12V above its source voltage.

Once the LTC4366 is powered up, it is ready to protect the load against an overvoltage transient. This is accomplished in the regulate mode with an overvoltage regulation amplifier, referenced to a 1.23V source. If the voltage drop across the upper feedback resistor,  $R_{\rm FB1}$ , exceeds 1.23V, the regulation amplifier pulls the gate down to move the  $R_{\rm FB1}$  voltage back to 1.23V. This allows the ratio of  $R_{\rm FB1}/R_{\rm FB2}$  to set the clamp voltage.

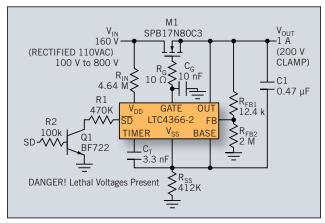

Fig. 3. This circuit has a potential 100V to 800V  ${

m V}_{IN}$  operating range, limited by the MOSFET's breakdown voltage.

During surge regulation, the excess voltage is dropped across the MOSFET. To prevent overheating the MOSFET, the LTC4366 limits the overvoltage regulation time using an internal timer connected to the TIMER pin. The TIMER is charged with  $9\mu A$  until the pin exceeds 2.8V. At that point it sets an overvoltage fault, the MOSFET turns off, and the IC enters a 9 second MOSFET cool-down period. During cool-down, the GATE pin voltage is pulled to the OUT pin.

At the beginning of start-up, during shutdown, or after an overvoltage fault, the GATE pin is clamped to the OUT pin, thereby shutting off the MOSFET. This allows the  $V_{SS}$  and OUT pins to be pulled to ground by the output load and  $R_{SS}$ . Under this condition the  $V_{DD}$  pin is clamped with a 12V shunt regulator to  $V_{SS}$ . The full supply voltage minus 12V is then impressed on  $R_{IN}$ , which sets the shunt current. The shunt current can be as high as 10mA - several orders of magnitude higher than the typical  $9\mu A$   $V_{DD}$  pin quiescent current.

#### OVERVOLTAGE FAULT

Normally, the external MOSFET is fully on, powering the load with very little voltage drop. As the input voltage increases, the OUT voltage also increases until it reaches a regulation point ( $V_{REG}$ ). From that point, any further voltage increase is dropped across the MOSFET. The MOSFET is still on, so the LTC4366 allows uninterrupted operation during a short overvoltage event.

The LTC4366 includes two shunt regulators coupled with the external voltage dropping resistors,  $R_{SS}$  and  $R_{IN}$ , to generate internal supply rails at the  $V_{DD}$  and OUT pins. These shunt-regulated rails enable overvoltage protection from unlimited high voltage transients, regardless of the voltage rating of the LTC4366's internal circuitry.

When the output is at the  $V_{REG}$  regulation point a timer starts, preventing excessive MOSFET heating. Normally, the TIMER pin is held low with a 1.8 $\mu$ A pull-down current. During regulation, the TIMER pin charges with 9 $\mu$ A. If the regulation point is held long enough for the TIMER pin to reach 2.8V, the IC generates an overvoltage fault.

After an overvoltage fault, the IC allows the FET to cool down and self-starts (LTC4366-2), or remains latched off

until the  $\overline{SD}$  pin activates a shutdown followed by a startup command (LTC4366-1). The nine second cool-down allows a very low pulsed power duty cycle.

The proper rating for the  $R_{SS}$  resistor (Fig. 1) is an important consideration. During an overvoltage event, the OUT pin is at the regulation voltage ( $V_{REG}$ ), and the voltage across  $R_{SS}$  is  $V_{REG}$  minus 5.7V. Large differences between minimum supply voltage and the regulation voltage may require a high wattage  $R_{SS}$ .

The full supply voltage minus 12V can appear across  $R_{\rm IN}$  during overvoltage cool-down. Normally,  $R_{\rm IN}$  is several times larger than  $R_{\rm SS}$ , reducing  $R_{\rm IN}$ 's power and size requirements.

## **MOSFET SELECTION**

The external MOSFET's important parameters are:

- On-resistance (R<sub>DS(ON)</sub>)

- Maximum drain-source voltage (V<sub>(BR)DSS</sub>),

- Threshold voltage

- SOA

The maximum allowable drain-source voltage must be higher than the supply voltage. If the output is shorted to

ground or during an overvoltage event, the full supply voltage appears across the MOSFET. Applications with supplies less than 12V require a logic-level MOSFET, whereas a standard threshold MOSFET is sufficient above 12V.

The SOA of the MOSFET must encompass all fault conditions. In normal operation, the MOSFET is fully on, dissipating very little power. High voltage drop across the MOSFET can occur in these cases. For reliable operation, consider the MOSFET SOA current large videous consideration.

sider the MOSFET SOA curves along with selection of the fault timer capacitor ( $C_T$ ) that controls cool-down.

High impedances of the  $\overline{SD}$ ,  $V_{DD}$ , and GATE pin circuits make them susceptible to ground leakages. For example, a leakage to ground on  $\overline{SD}$  will activate the shutdown mode if it is over 1.6µA. Therefore, provide adequate spacing away from grounded traces and add conformal coating to exposed pins, which lowers the risk of leakage current.

It is important to put bypass capacitor, C1, as close as possible to the OUT and  $V_{SS}$  pins. The  $R_{G}$  resistor should be close to the MOSFET's gate pin, which limits parasitic trace capacitance that can cause MOSFET self-oscillation.

The FB pin is sensitive to parasitic capacitance when the regulation loop is closed. One result from this capacitive loading is output oscillations during overvoltage regulation. For best results, place resistors  $R_{\rm FB1}$  and  $R_{\rm FB2}$  close to the FB pin and minimize PCB traces leading to that pin.

#### HIGH VOLTAGE APPLICATION

The circuit in Fig.~3 accepts 110VAC (rectified to 160V) and protects the load from accidental connection to 220VAC by

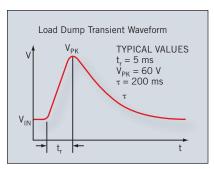

Fig. 5. Typical load dump waveform.

limiting the output to less than 200V. The circuit has a 100V to 800V  $V_{\rm IN}$  operating range where the MOSFET breakdown voltage limits the maximum input voltage. An internal charge pump has a 0.47 $\mu$ F bypass capacitor (C1) that provides good noise immunity from voltage transients.

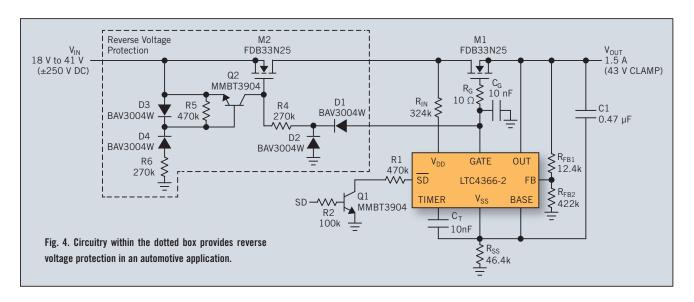

## 28V VEHICLE APPLICATION

The circuit shown in Fig. 4 provides reverse voltage protection for an auto-

motive application. There are three modes to this circuit:

- MOSFET turn on when the input is 18V to 41V

- Output clamp to 43V when more than 43V appears at the input

- Reverse voltage protection when up to –250V DC is present at the input

Circuitry in Fig. 4 (dotted box) provides reverse voltage protection. When a positive voltage is first applied to the input, D3 and the forward biased base-collector junction of Q2 allow the gate of M2 to follow the input voltage minus a two diode drop. The body diode of M2 transmits power to the LTC4366. Once powered up, the LTC4366 enhances the gate of M1 and M2. The M1 and M2 MOSFETs provide a low impedance path to the load. During overvoltages, D1 blocks excessive positive voltage from the input supply passing to the LTC4366's GATE. D4 eliminates current flow through R6 when the input is positive. D3 prevents emitter base breakdown of Q2 when the input is powering up. During negative input voltages, Q2 turns on when current from R6 develops a forward diode drop on R5. Q2 holds the gate of M2 at the input voltage that turns M2 off. **७**

## ■ HIGH VOLTAGE SURGES

# **AUTOMOTIVE, INDUSTRIAL AND AVIONIC APPLICATIONS**

commonly encounter high voltage power supply spikes with durations ranging from a few microseconds to hundreds of milliseconds. System electronics must survive these transient voltage spikes and also reliably ride through the event.

When long wires distribute power, severe transients can generate load steps (abrupt changes in load current). Negative load steps happen when load current drops from a high to a low value. Negative changes in current (dl/dt) cause the wire's parasitic inductance to generate a positive-going high voltage spike that can damage neighboring devices on the same wire.

Fast load switching by relays, switch contacts and solid state load switching produce high dl/dt. Corroded connections between a power source and load can lead to an abrupt current interruption and a high dl/dt. For example, automo-

tive load dumps occur where there is a sudden break in the battery connection caused by vibration and corroded terminals.

Load dump causes a voltage surge that stays elevated for hundreds of milliseconds, as shown in *Fig. 5*. According to the Society of Automotive Engineers (SAE), the transient may be as high as 125V. A typical load dump profile has a rise time of 5 ms, and decaying exponentially with a time constant of 200ms. Regeneration in solenoids and motors can cause similar events in industrial systems.

These transients pose a difficult challenge for designers trying to protect sensitive electronics. This protection has been achieved using bulky capacitors, TVS diodes and fuses, but discrete solutions consume a lot of real estate. An improved approach is the use of an IC like the LTC4366, that is specifically intended to clamp input voltages and protect against surges and transients.