## LTC6561 DICE/DWF

#### Four-Channel Multiplexed Transimpedance Amplifier with Output Multiplexing

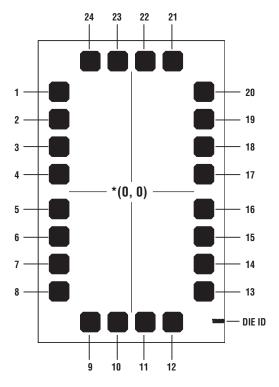

Die Size: 36mils (914.4µm)× 55mils (1397µm) Bond Pad Size: 4mils (102µm)× 4mils (102µm) Bond Pad Opening: 3.2mils (82µm)× 3.2mils (82µm) Bond Pad Metal Thickness: 0.29mils (7.4µm) Wafer Saw Street Width: 2.4mils (61µm) Wafer/Die Thickness: 8mils (200µm) Backside Metal: None Backside Potential: V<sup>-</sup>

| PAD # | PAD NAME          | X COORDINATE (µm) | Y COORDINATE (µm) |

|-------|-------------------|-------------------|-------------------|

| 1     | CHSEL1            | 417.9             | 303.24            |

| 2     | V <sub>CCO</sub>  | 302.9             | 303.24            |

| 3     | CHSELO            | 187.9             | 303.24            |

| 4     | V <sub>CC1</sub>  | 72.9              | 303.24            |

| 5     | V <sub>REF1</sub> | -72.9             | 303.24            |

| 6     | GND               | -187.9            | 303.24            |

| 7     | IN1               | -302.9            | 303.24            |

| 8     | GND               | -417.9            | 303.24            |

| 9     | IN2               | -546.21           | 172.5             |

| 10    | V <sub>REF2</sub> | -546.21           | 57.5              |

| 11    | V <sub>REF3</sub> | -546.21           | -57.5             |

| 12    | IN3               | -546.21           | -172.5            |

| 13    | GND               | -417.9            | -303.24           |

| 14    | IN4               | -302.9            | -303.24           |

| 15    | GND               | -187.9            | -303.24           |

| 16    | V <sub>REF4</sub> | -72.9             | -303.24           |

| 17    | V <sub>CC2</sub>  | 72.9              | -303.24           |

| 18    | 0_MUX             | 187.9             | -303.24           |

| 19    | V <sub>CCO</sub>  | 302.9             | -303.24           |

| 20    | DNC               | 417.9             | -303.24           |

| 21    | OUTTERM           | 546.21            | -172.5            |

| 22    | GND               | 546.21            | -57.5             |

| 23    | GND               | 546.21            | 57.5              |

| 24    | OUT               | 546.21            | 172.5             |

All registered trademarks and trademarks are the property of their respective owners.

#### FEATURES

- 220MHz 3dB Bandwidth with 2pF Input Capacitance

- Single-Ended Output

- 74kΩ Transimpedance Gain

- 4.8pA/√Hz Input Current Noise Density at 200MHz (2pF)

- 64nA<sub>RMS</sub> Integrated Input Current Noise Over 200MHz (2pF)

- Linear Input Range OµA to 30µA

- Overload Current > ±400mA Peak

- Fast Overload Recovery 12ns, 1mA

- Fast Channel Switchover < 50ns</p>

- Single 5V Supply

- 200mW Power Dissipation for 4 Channels

- 2V<sub>P-P</sub> Output Swing on 100Ω Load

- Output MUX Combines Multiple 4-Channel Devices to Create 4, 8,12,16, 24, 32 Channel Solutions

#### **APPLICATIONS**

- LIDAR Receiver

- Industrial Imaging

### DESCRIPTION

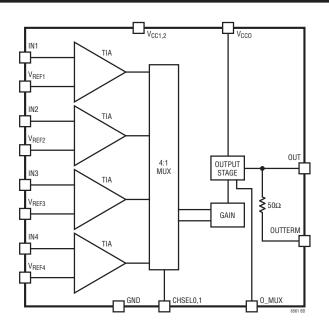

The LTC<sup>®</sup>6561 is a low-noise, four-channel, transimpedance amplifier (TIA) with 220MHz bandwidth. The LTC6561 multi-channel transimpedance amplifier's low noise, high transimpedance, and low power dissipation are ideal for LIDAR receivers using Avalanche Photodiodes (APDs). The amplifier features  $74k\Omega$  transimpedance gain and  $30\mu$ A linear input current range. Using an APD input circuit with a total capacitance of 2pF, the input current noise density is  $4.8 \text{pA}/\sqrt{\text{Hz}}$  at 200MHz. With lower capacitance, noise and bandwidth improve further. Only a 5V single supply

is needed and the device consumes only 200mW. Utilizing the internal 4-to-1 MUX along with the LTC6561's output MUX; multiple 4-channel LTC6561 devices can be combined to directly interface with 12-, 16- and 32-channel APD arrays. The LTC6561's fast overload recovery and fast channel switchover make it well suited for LIDAR receivers with multiple APDs. Its single-ended output can swing  $2V_{P-P}$  on a 100 $\Omega$  load while its low impedance op amp style output can drive back-terminated  $50\Omega$  cables.

#### **ABSOLUTE MAXIMUM RATINGS** (Note 1)

Total Supply Voltage (V<sub>CC1</sub>, V<sub>CC2</sub>, V<sub>CC0</sub> to GND).....5.5V Input Voltage (CHSELO, CHSEL1, O\_MUX).....-0.3V to 5.5V Amplifier Reference Current (V<sub>RFF1</sub>, V<sub>RFF2</sub>, V<sub>BFE3</sub>, V<sub>BFF4</sub>).....±10mA Amplifier Input Current (IN1, IN2, IN3, IN4) ...... ±400mA RMS ±2A Transient (10ns)

| Amplifier Output Current (OUT, OUT | ITERM)+80mA    |

|------------------------------------|----------------|

| Operating Temperature Range        |                |

| LTC6561                            | –40°C to 125°C |

| Storage Temperature Range          | –65°C to 150°C |

| Junction Temperature               | 150°C          |

| -                                  |                |

### DIE CROSS REFERENCE

| FINISHED PART NUMBER ORDE | ER PART NUMBER |

|---------------------------|----------------|

| LTC6561 LTC65             | 561 DICE/DWF   |

Please refer to ADI standard LTC6561 product data sheet for other applicable product information and typical performance information.

#### **AC ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{CC1,2} = V_{CC0} = 5V$ , $0_MUX = 0V$ , GND = 0V, $Z_{LOAD} = 100\Omega$ . Output taken from OUT pin.

| SYMBOL               | PARAMETER                             | CONDITIONS                                             | MIN | ТҮР | MAX | UNITS             |

|----------------------|---------------------------------------|--------------------------------------------------------|-----|-----|-----|-------------------|

| BW                   | –3dB Bandwidth                        | 200mV <sub>P-P,OUT</sub> and C <sub>IN,TOT</sub> = 2pF |     | 220 |     | MHz               |

| R <sub>T</sub>       | Small Signal Transimpedance           | Ι <sub>IN</sub> < 2μΑ <sub>Ρ-Ρ</sub>                   | 63  | 74  | 85  | kΩ                |

| R <sub>IN</sub>      | Input Resistance                      | f = 100kHz                                             |     | 236 |     | Ω                 |

| R <sub>OUT</sub>     | Output Resistance                     | f = 100kHz                                             |     | 3   |     | Ω                 |

| I <sub>n</sub>       | Input Current Noise Density           | $f = 100MHz, C_{IN,TOT} = 2pF$                         |     | 4.3 |     | pA/√Hz            |

|                      |                                       | $f = 200MHz, C_{IN,TOT} = 2pF$                         |     | 4.8 |     | pA/√Hz            |

|                      | Integrated Input Current Noise        | f = 0.1MHz to 100MHz, C <sub>IN,TOT</sub> = 2pF        |     | 43  |     | nA <sub>RMS</sub> |

|                      |                                       | $f = 0.1 MHz$ to 200MHz, $C_{IN,TOT} = 2pF$            |     | 64  |     | nA <sub>RMS</sub> |

|                      | Adjacent Channel to Channel Isolation | f = 100MHz                                             |     | -45 |     | dB                |

|                      | Non Adjacent Channel Isolation        | f = 100MHz                                             |     | -65 |     | dB                |

| t <sub>RECOVER</sub> | Overload Recovery Time                | Input Pulse <1mA                                       |     | 12  |     | ns                |

| t <sub>SWITCH</sub>  | Channel Switchover Time               |                                                        |     | 50  |     | ns                |

# **DC ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{CC1,2} = V_{CC0} = 5V$ , $0_MUX = 0V$ , GND = 0V, $Z_{LOAD} = 100\Omega$ . Output taken from OUT pin.

| SYMBOL                    | PARAMETER                                                             | CONDITIONS                                                       | MIN          | ТҮР          | MAX          | UNITS            |

|---------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------|--------------|--------------|--------------|------------------|

| IN1,2,3,4 Pins            | and V <sub>REF1,2,3,4</sub> Pins                                      |                                                                  |              |              |              |                  |

| V <sub>IN</sub>           | Input Bias Voltage                                                    | Active Channel<br>Inactive Channel                               | 1.43<br>0.78 | 1.55<br>0.93 | 1.64<br>1.38 | V<br>V           |

| V <sub>REF</sub>          | Input Reference Voltage                                               | Active Channel<br>Inactive Channel                               | 1.43<br>1.34 | 1.55<br>1.50 | 1.63<br>1.67 | V<br>V           |

| Offset                    | V <sub>IN</sub> – V <sub>REF</sub>                                    | Active Channel<br>Inactive Channel                               | -12<br>-741  |              | 12<br>116    | mV<br>mV         |

| OUT Pin                   |                                                                       | · · ·                                                            |              |              |              |                  |

| V <sub>OUT</sub>          | Output Default Voltage                                                | O_MUX = 0V (Output Enabled)<br>O_MUX = 3.3V, Standalone Device   | 0.83<br>0.32 | 1.10<br>0.60 | 1.47<br>0.88 | V<br>V           |

| OVR                       | Output Voltage Range                                                  | I <sub>IN</sub> Current Range = 0 to -50µA                       | 1.22         | 1.90         | 2.58         | V <sub>P-P</sub> |

| OUTTERM                   | Internal Series Resistor for Optional Output                          |                                                                  | 44           | 56           | 70.8         | Ω                |

| CHSELO, CHSE              | L1, O_MUX Pins with Internal Pull-Down Resis                          | tors                                                             |              |              |              | ·                |

| V <sub>IL</sub>           |                                                                       |                                                                  |              |              | 0.7          | V                |

| V <sub>IH</sub>           |                                                                       |                                                                  | 1.5          |              |              | V                |

| IIL                       | Pin Voltage = 0.7V                                                    |                                                                  | 16.9         | 20.7         | 26.0         | μA               |

| IIH                       | Pin Voltage = 1.5V                                                    |                                                                  | 37           | 47           | 57           | μA               |

| C <sub>IN</sub>           |                                                                       |                                                                  |              | 1.5          |              | pF               |

| R <sub>IN</sub>           |                                                                       |                                                                  | 22           | 29           | 35           | kΩ               |

| Power Supply              |                                                                       |                                                                  |              |              |              | <u> </u>         |

| V <sub>S</sub>            | Operating Supply Range                                                |                                                                  | 4.75         | 5            | 5.25         | V                |

| I <sub>CC1,2</sub>        | Input Supply Current                                                  | V <sub>CC1</sub> & V <sub>CC2</sub> are Internally Tied Together | 29           | 36.3         | 44           | mA               |

| I <sub>CCO</sub>          | Output Supply Current                                                 | Both V <sub>CCO</sub> Pins are Internally Tied Together          | 1.8          | 2.3          | 2.8          | mA               |

| Is                        | Total Supply Current (I <sub>S(VCC1,2)</sub> + I <sub>S(VCC0)</sub> ) |                                                                  | 30.8         | 38.6         | 46.8         | mA               |

| PSRR(V <sub>CC1,2</sub> ) | Input Power Supply Rejection Ratio                                    | V <sub>CC1,2</sub> = 4.75V to 5.25V, V <sub>CC0</sub> = 5V       | 21           | 25           |              | dB               |

| PSRR(V <sub>CC0</sub> )   | Output Power Supply Rejection Ratio                                   | $V_{CC0} = 4.75V$ to 5.25V, $V_{CC1,2} = 5V$                     | 34           | 40           |              | dB               |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All measurement were conducted in the dark.

#### PAD FUNCTIONS

**CHSEL1:** MSB for Channel Selection. CMOS input. The CHSEL1 pad has a  $29k\Omega$  internal pull-down resistor. Default value is OV.

$V_{CCO}$ : Positive Power Supply for the Output Stage. Typically 5V.  $V_{CCO}$  can be tied to  $V_{CC1}$  or  $V_{CC2}$  for single supply operation. Between the positive supply and ground, bypass capacitors of 1000pF and 0.1µF should be placed as close to the part as possible.  $V_{CCO}$  pads are internally tied together.

**CHSELO:** LSB for Channel Selection. CMOS input. The CHSELO pad has a  $29k\Omega$  internal pull-down resistor. Default value is OV.

$V_{CC1}, V_{CC2}$ : Positive Power Supply. Typically 5V. Between the positive supply and ground, bypass capacitors of 1000pF and 0.1µF should be placed as close to the part as possible.  $V_{CC1}$  and  $V_{CC2}$  are internally tied together.

**V<sub>REF1</sub>**, **V<sub>REF2</sub>**, **V<sub>REF3</sub>**, **V<sub>REF4</sub>**: Reference Voltage Pad for Transimpedance Amplifier in Channel 1, 2, 3, and 4 Respectively. This pad sets the input DC voltage for each transimpedance amplifier. The V<sub>REF</sub> pad has a Thevenin equivalent resistance of approximately 1.4k and can be overdriven by an external voltage. If no voltage is applied

to  $V_{REF}$ , it will float to a default voltage of approximately 1.55V on a 5V supply. Each  $V_{REF}$  pad should be bypassed with a high quality ceramic bypass capacitor of at least 0.1µF. The bypass cap should be located close to its  $V_{REF}$  pad.

GND: Negative Power Supply. Normally tied to ground.

**IN1, IN2, IN3, IN4:** Input Pad for Transimpedance Amplifier for Channels 1, 2, 3, and 4 Respectively. This pad is internally biased to 1.55V.

**O\_MUX:** Output MUX. CMOS Input. This pad is functional when multiple LTC6561s are combined at the output. When O\_MUX is low, the output is enabled. When O\_MUX is high, all 4 inputs are decoupled from the output. Default value is OV. This MUX pad is ineffective unless a 2nd LTC6561 is DC-coupled at the output. See Applications section on how to use O\_MUX to expand the channel count with multiple LTC6561's. The O\_MUX pad has a  $29k\Omega$  internal pull-down resistor.

DNC: Do not connect.

OUTTERM: TIA Output with an Internal Series  $50\Omega$  Resistor.

**OUT:** TIA Output without an internal series  $50\Omega$  Resistor.

#### **BLOCK DIAGRAM**

Wafer level testing is performed per indicated specifications for dice. Considerable differences in performance can often be observed for dice versus packaged units due to the influences of packaging and assembly on certain devices and/or parameters. Please consult factory for more information on dice performance and lot qualifications via lot sampling test procedures.

Dice data sheet subject to change. Please consult factory for current revision in production.

I.D.No. 66-13-6561