## **FEATURES**

- 600MHz –3dB Bandwidth with 0.5pF Input Capacitance

- Differential Output with Up to 2V<sub>P-P</sub> Swing into 100Ω

Differential Load

- Built-In High-Speed ADC Driver with Output MUX

- Selectable 22.2/16.7/11.1/5.55k $\Omega$  Transimpedance Gain

- 1.8pA/3.7pA√Hz Input Current Noise Density 100MHz/600MHz (0.5pF)

- 65nA<sub>RMS</sub> Integrated Input-Referred Current Noise Over 600MHz (0.5pF)

- Large Linear Input Current Range 0µA to 90µA

- Large Transient Overload Current >1A Peak

- Fast Overload Recovery: 2.5ns

- Fast Channel Switching: 10ns

- Power Dissipation: 194mW to 325mW on 3.3V, Varies with Output Mode (13mW in Shutdown)

- Output MUX allows multiple LTC6563s to Create 8, 12, 16 ... 32 Channel Solutions

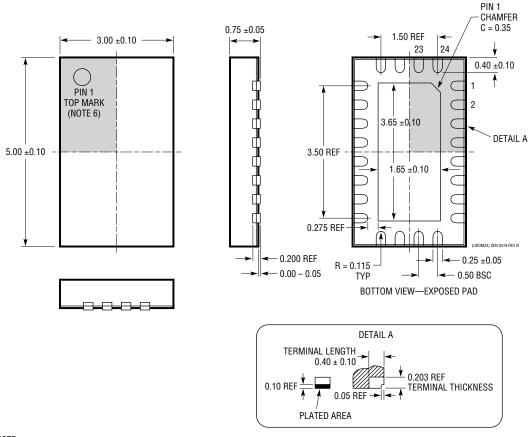

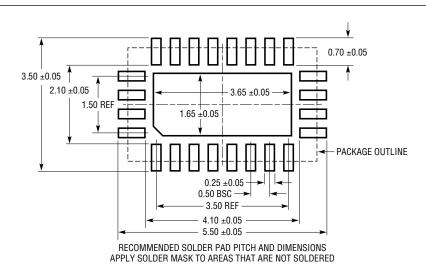

- 3mm × 5mm, 24-Lead QFN Package, Wettable Flanks

- AECQ-100 Grade 1 Qualified (Pending)

## **APPLICATIONS**

- Automotive LIDAR Receiver

- Industrial LIDAR Receiver

# Four-Channel Transimpedance Amplifier with Output Multiplexing

## DESCRIPTION

The LTC®6563 is a low-noise four-channel transimpedance amplifier (TIA) with 600MHz bandwidth. The LTC6563 TIA's low noise, wide linear range, and low power dissipation are ideal for LIDAR receivers using Avalanche photodiodes (APDs) and photodiodes (PDs). The amplifier features selectable 22.2/16.7/11.1/5.55k $\Omega$  Transimpedance gain (RT) and 90µA linear input current range. Using an APD with a total input capacitance of 0.5pF, the input current noise density is  $1.8pA/\sqrt{Hz}$  at 100MHz and  $3.7pA/\sqrt{Hz}$ at 600MHz. The LTC6563 consumes between 194mW and 325mW on a 3.3V supply depending on output mode. An internal 4-to-1 MUX simplifies the system design. In addition, external multiplexing capability allows channel expansion up to 64 channels, saving space and power. Fast overload recovery and fast channel switchover make the LTC6563 well suited for LIDAR receivers with multiple APDs. The built-in high-speed differential ADC driver can swing as much as  $2V_{P-P}$  while driving into  $100\Omega$  external differential load.

The LTC6563 is packaged in a 3mm  $\times$  5mm 24-pin exposed pad QFN package with wettable flanks.

All registered trademarks and trademarks are the property of their respective owners.

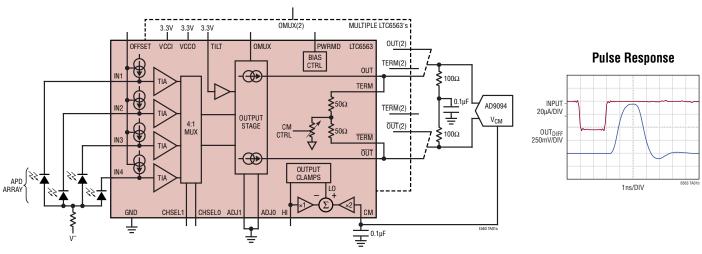

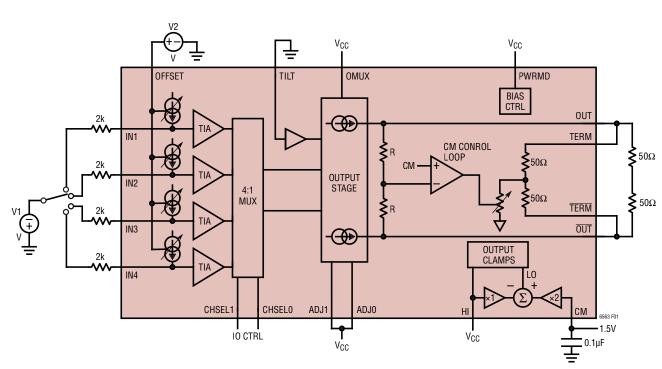

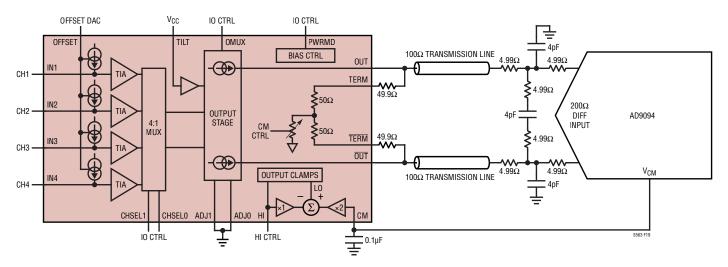

## TYPICAL APPLICATION

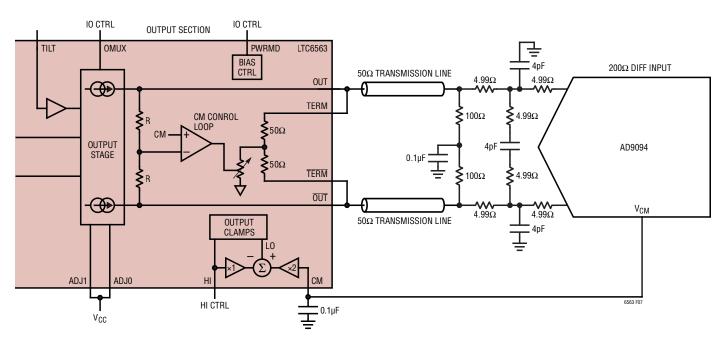

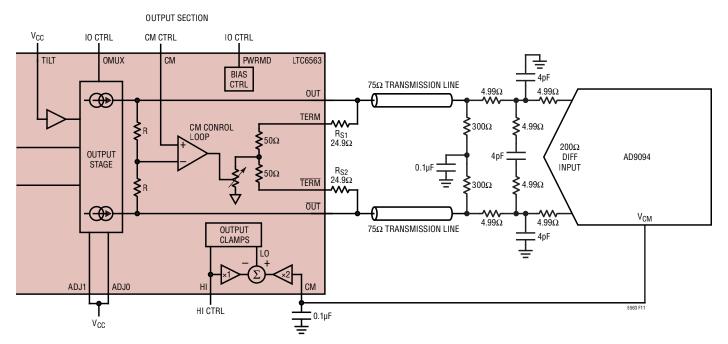

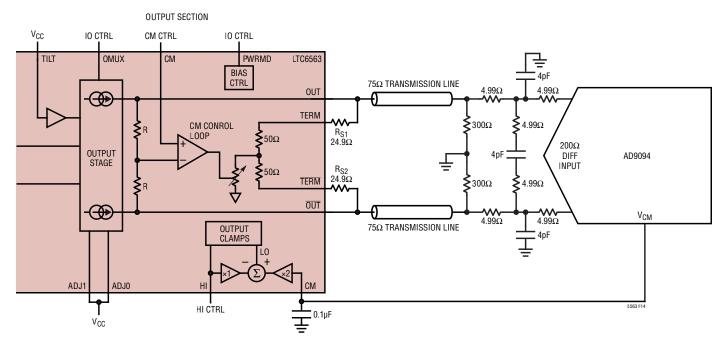

Typical Application with DC-Coupled Inputs Driving an ADC

Rev. 0

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Total Supply Voltage:                      |

|--------------------------------------------|

| V <sub>CCI</sub> to GND3.6V                |

| V <sub>CCO</sub> to GND3.6V                |

| Input Current (CHSELO, CHSEL1, ADJO, ADJ1, |

| PWRMD, OMUX, CM, HI, OFFSET, TILT)±10mA    |

| Amplifier Inputs (IN1, IN2, IN3, IN4):     |

| Voltage0.3V to 3.6V                        |

| Current 10µA/-400mA <sub>RMS</sub>         |

| Current (Note 5)–1A Transient              |

| Amplifier Outputs (OUT, OUT):              |

| Voltage0.3V to 3.6V                        |

| Current ±100mA                             |

| Amplifier Output Termination (TERM, TERM): |

| Voltage0.3V to 3.6V                        |

| Current72mA/6mA                            |

| Operating Temperature Range:               |

| LTC6563I (Note 2)40°C to 85°C              |

| LTC6563H (Note 3)40°C to 125°C             |

| Storage Temperature Range65°C to 150°C     |

| Junction Temperature                       |

|                                            |

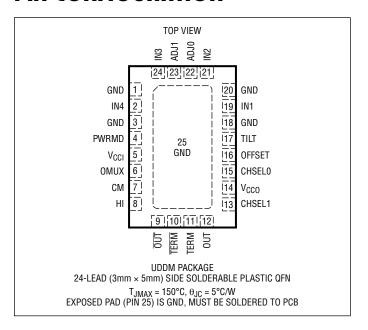

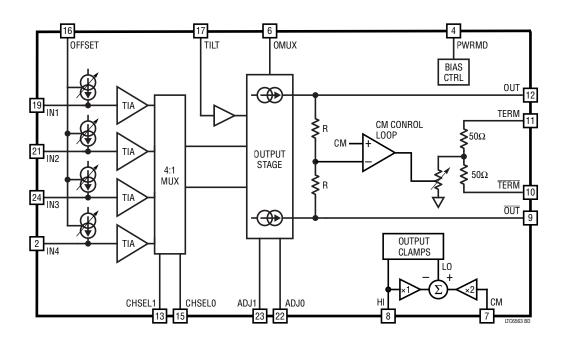

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION                             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|-------------------------------------------------|-------------------|

| LTC6563IUDDM#PBF | LTC6563IUDDM#TRPBF | LHMH          | 24-Lead (3mm × 5mm) Side Solderable Plastic QFN | -40°C to 85°C     |

| LTC6563HUDDM#PBF | LTC6563HUDDM#TRPBF | LHMH          | 24-Lead (3mm × 5mm) Side Solderable Plastic QFN | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**RC ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ , ADJ0 = ADJ1 = PWRMD = OMUX =  $V_{CCI}$  = HI =  $V_{CCO}$  = 3.3V, TILT = OFFSET = 0,  $V_{CM}$  = 1.5V. All other input pins are floating unless stated otherwise.  $V_{OUTCM}$  is defined as (OUT + OUT)/2 and  $V_{OUTDIFF}$  is defined as (OUT - OUT),  $R_{L_EXT}$  = 100 $\Omega$  differential, OUT connected to TERM and OUT connected to TERM.

| SYMBOL                         | PARAMETER                              | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MIN                        | TYP                                          | MAX                         | UNITS                                                                                                 |

|--------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------|

| BW                             | -3dB Bandwidth                         | 200mV <sub>P-P,OUT</sub> and C <sub>IN,TOT</sub> = 0.5pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            | 600                                          |                             | MHz                                                                                                   |

| SR                             | Slew Rate                              | $C_{IN,TOT} = 0.5pF$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | 3000                                         |                             | V/us                                                                                                  |

| t <sub>R</sub> /t <sub>F</sub> | Rise/Fall Time                         | $C_{IN,TOT} = 0.5pF$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | 0.6                                          |                             | ns                                                                                                    |

| R <sub>T</sub> Differential    | Small Signal Transimpedance            | $I_{IN} < 2\mu A_{P-P}$ , ADJ00<br>$I_{IN} < 2\mu A_{P-P}$ , ADJ01<br>$I_{IN} < 2\mu A_{P-P}$ , ADJ10<br>$I_{IN} < 2\mu A_{P-P}$ , ADJ11                                                                                                                                                                                                                                                                                                                                                                                   | 4.9<br>9.6<br>14.1<br>18.1 | 5.55<br>11.1<br>16.7<br>22.2                 | 6.5<br>12.5<br>18.2<br>23.4 | kΩ<br>kΩ<br>kΩ<br>kΩ                                                                                  |

| TCR <sub>T</sub>               | Transimpedance Temperature Coefficient | $I_{IN} < 2\mu A_{P-P}$ , ADJ00<br>$I_{IN} < 2\mu A_{P-P}$ , ADJ01<br>$I_{IN} < 2\mu A_{P-P}$ , ADJ10<br>$I_{IN} < 2\mu A_{P-P}$ , ADJ11                                                                                                                                                                                                                                                                                                                                                                                   |                            | -0.00125<br>-0.00246<br>-0.00403<br>-0.00609 |                             | kΩ/°C<br>kΩ/°C<br>kΩ/°C<br>kΩ/°C                                                                      |

| R <sub>IN</sub>                | Input Impedance                        | f = 100kHz Active Channel<br>f = 100kHz Inactive Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            | 225<br>409                                   |                             | Ω<br>Ω                                                                                                |

| R <sub>TERM_DIFF</sub>         | Internal Diff Termination Impedance    | Measured from TERM to TERMBAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | 100                                          |                             | Ω                                                                                                     |

| I <sub>n</sub>                 | Input Current Noise Density            | $ \begin{split} & \text{f} = 100\text{MHz},  \text{C}_{\text{IN\_TOT}} = 0.5\text{pF} \\ & \text{f} = 200\text{MHz},  \text{C}_{\text{IN\_TOT}} = 0.5\text{pF} \\ & \text{f} = 300\text{MHz},  \text{C}_{\text{IN\_TOT}} = 0.5\text{pF} \\ & \text{f} = 400\text{MHz},  \text{C}_{\text{IN\_TOT}} = 0.5\text{pF} \\ & \text{f} = 500\text{MHz},  \text{C}_{\text{IN\_TOT}} = 0.5\text{pF} \\ & \text{f} = 600\text{MHz},  \text{C}_{\text{IN\_TOT}} = 0.5\text{pF} \\ \end{aligned} $                                      |                            | 1.8<br>2.3<br>2.5<br>3<br>3.4<br>3.7         |                             | pA/√Hz<br>pA/√Hz<br>pA/√Hz<br>pA/√Hz<br>pA/√Hz<br>pA/√Hz                                              |

|                                | Integrated Input Current Noise         | $ \begin{array}{l} f = 0.1 \text{MHz to } 100 \text{MHz}, \ C_{\text{IN\_TOT}} = 0.5 \text{pF} \\ f = 0.1 \text{MHz to } 200 \text{MHz}, \ C_{\text{IN\_TOT}} = 0.5 \text{pF} \\ f = 0.1 \text{MHz to } 300 \text{MHz}, \ C_{\text{IN\_TOT}} = 0.5 \text{pF} \\ f = 0.1 \text{MHz to } 400 \text{MHz}, \ C_{\text{IN\_TOT}} = 0.5 \text{pF} \\ f = 0.1 \text{MHz to } 500 \text{MHz}, \ C_{\text{IN\_TOT}} = 0.5 \text{pF} \\ f = 0.1 \text{MHz to } 600 \text{MHz}, \ C_{\text{IN\_TOT}} = 0.5 \text{pF} \\ \end{array} $ |                            | 19<br>27<br>36<br>45<br>55<br>65             |                             | nA <sub>RMS</sub><br>nA <sub>RMS</sub><br>nA <sub>RMS</sub><br>nA <sub>RMS</sub><br>nA <sub>RMS</sub> |

| t <sub>RECOVER</sub>           | Overload Recovery and Pulse Extension  | $I_{IN} = -4\text{mA}$ , $C_{IN\_TOT} = 0.5\text{pF}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            | 2.5                                          |                             | ns                                                                                                    |

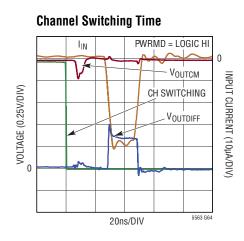

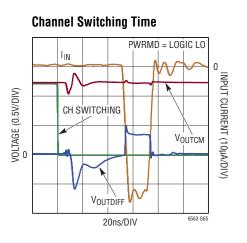

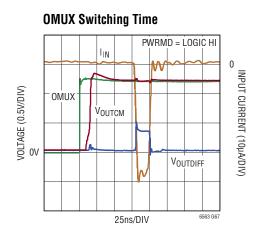

| t <sub>CH_SWITCH</sub>         | Channel Switching Time                 | Any Channel to Any Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | 10                                           |                             | ns                                                                                                    |

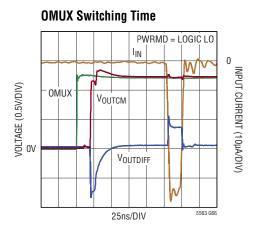

| t <sub>OMUX_SWITCH</sub>       | Output MUX Switching Time              | OMUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | 20                                           |                             | ns                                                                                                    |

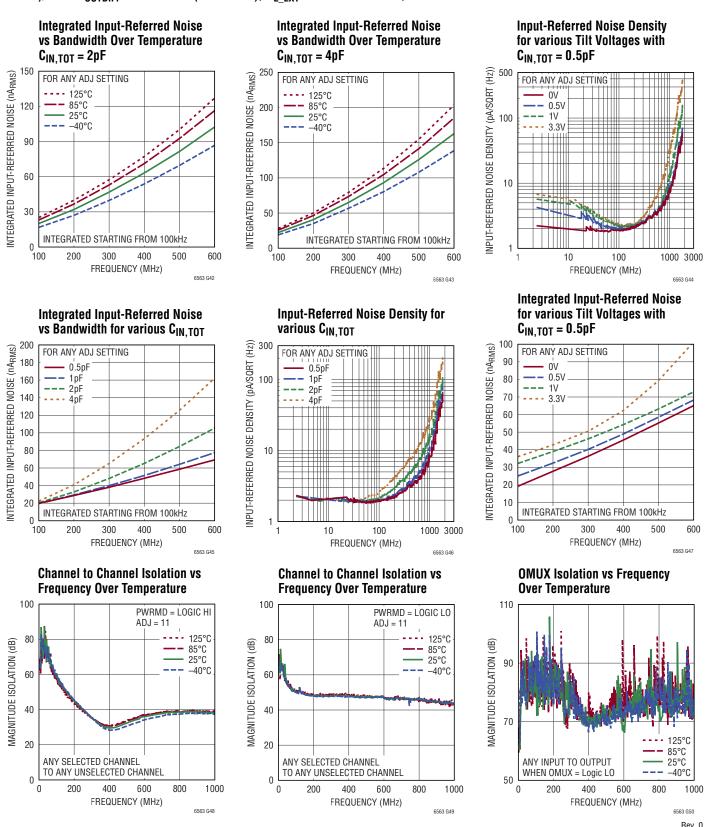

| Isolation                      | Channel to Channel Isolation           | 400MHz, PWRMD = Logic Low, Selected Channel to Any Unselected Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            | 48                                           |                             | dB                                                                                                    |

**DC ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ , ADJ0 = ADJ1 = PWRMD = OMUX =  $V_{CCI}$  = HI =  $V_{CCO}$  = 3.3V, TILT = OFFSET = 0,  $V_{CM}$  = 1.5V. All other input pins are floating unless stated otherwise.  $V_{OUTCM}$  is defined as (OUT + OUT)/2 and  $V_{OUTDIFF}$  is defined as (OUT - OUT),  $R_{L_EXT}$  =  $100\Omega$  differential, OUT connected to TERM and OUT connected to TERM.

| SYMBOL                   | PARAMETER                                                     | CONDITIONS                         | MIN      | TYP        | MAX | UNITS    |

|--------------------------|---------------------------------------------------------------|------------------------------------|----------|------------|-----|----------|

| IN1, IN2, IN3, II        | N4 Pins                                                       |                                    |          |            |     |          |

| V <sub>IN</sub>          | Input Bias Voltage                                            | Active Channel<br>Inactive Channel |          | 0.8<br>0.7 |     | V        |

| I <sub>IN</sub>          | DC Input Current Range                                        | Tilt = 0V<br>Tilt = 3.3V           | 40<br>90 |            |     | μΑ<br>μΑ |

| OUT and OUT P            | ns                                                            |                                    |          |            |     |          |

| V <sub>OCM_DEFAULT</sub> | Default Output Common-Mode Voltage                            | ADJ = 00                           |          | 0.9        |     | V        |

| $\overline{V_{OOD}}$     | Differential Output Offset Voltage                            | $I_{IN} = 0\mu A$                  | -75      | ±10        | 75  | mV       |

| TCV <sub>OOD</sub>       | Differential Output Offset Voltage<br>Temperature Coefficient | $I_{IN} = 0\mu A$ ,                |          | -0.044     |     | mV/°C    |

**DC ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ , ADJ0 = ADJ1 = PWRMD = OMUX =  $V_{CCI}$  = HI =  $V_{CCQ}$  = 3.3V, TILT = OFFSET = 0,  $V_{CM}$  = 1.5V. All other input pins are floating unless stated otherwise.  $V_{OUTCM}$  is defined as (OUT + OUT)/2 and  $V_{OUTDIFF}$  is defined as (OUT - OUT),  $R_{L_EXT}$  = 100 $\Omega$  differential, OUT connected to TERM and OUT connected to  $\overline{TERM}$ .

| SYMBOL                      | PARAMETER                                                                      | CONDITIONS                                                                                                   |   | MIN             | TYP                 | MAX             | UNITS            |

|-----------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---|-----------------|---------------------|-----------------|------------------|

| V <sub>SWINGDIFF</sub>      | Differential Output Voltage Swing                                              | $I_{IN} = 0$ to $-200\mu A$ , Tilt = 3.3V                                                                    | • | 1.13<br>1.03    | 1.50                |                 | V <sub>P-P</sub> |

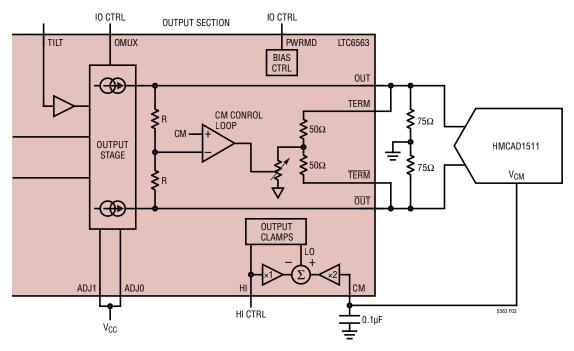

|                             |                                                                                | $I_{IN}$ = 0 to -90μA, Tilt = 3.3V, $R_{L\_EXT}$ = 75Ω SE on Each Output with Center Grounded (see Figure 3) |   |                 | 2.4                 |                 | V <sub>P-P</sub> |

| V <sub>OUTLOW</sub>         | Output Voltage Swing Low                                                       | Single-Ended Measurement, $I_{IN}$ = 0 to -200 $\mu$ A, Tilt = 3.3V                                          |   |                 | 1.02                |                 | V                |

| V <sub>OUTHIGH</sub>        | Output Voltage Swing High                                                      | Single-Ended Measurement, $I_{IN}$ = 0 to -200 $\mu$ A, Tilt = 3.3V                                          |   |                 | 2.2                 |                 | V                |

| V <sub>COMPLIANCE</sub>     | Output Voltage Compliance                                                      | Single-Ended Measurement, $I_{IN}$ = 0 to -200 $\mu$ A, Tilt = 3.3V                                          |   | 2.0             | V <sub>CCO</sub> -1 |                 | V                |

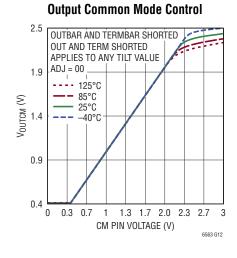

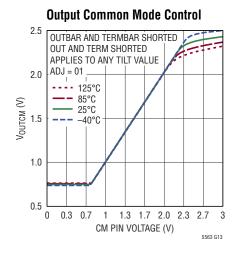

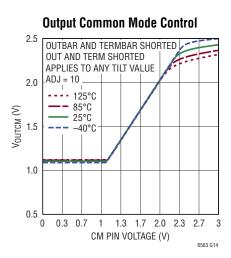

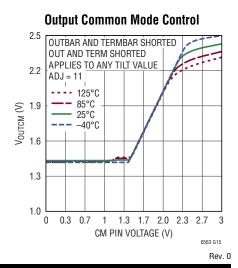

| <b>Output Common</b>        | Mode Voltage Control ( <sub>CM</sub> Pin)                                      |                                                                                                              |   |                 |                     |                 |                  |

| A <sub>CM</sub>             | CM Pin Voltage Gain, CM Pin to<br>Differential OUT                             | V <sub>CM</sub> = 1.5V to 1.7V                                                                               |   | 0.95            | 1                   | 1.05            | V/V              |

| TCAV <sub>CM</sub>          | A <sub>CM</sub> Temperature Coefficient                                        |                                                                                                              |   |                 | 9.3                 |                 | (μV/V)/°C        |

| V <sub>CM_DEFAULT</sub>     | Default CM Pin Voltage                                                         |                                                                                                              |   |                 | 0.9                 |                 | V                |

| V <sub>CM_OS</sub>          | Common Mode Offset Voltage                                                     | V <sub>OUTCM</sub> – V <sub>CM</sub>                                                                         |   | -50             | 10                  | 20              | mV               |

| TCV <sub>CM_OS</sub>        | Common Mode Offset Voltage<br>Temperature Coefficient                          | V <sub>OUTCM</sub> - V <sub>CM</sub>                                                                         |   |                 | -0.021              |                 | mV/°C            |

| V <sub>OUTCM_MIN</sub>      | V <sub>OUTCM</sub> Minimum Voltage                                             | V <sub>CM</sub> = 0V, ADJ00                                                                                  |   |                 | 0.38                | 0.43            | V                |

| V <sub>OUTCM_MAX</sub>      | V <sub>OUTCM</sub> Maximum Voltage                                             | V <sub>CM</sub> = 2.6V, ADJ11                                                                                |   | 2.2             | 2.3                 |                 | V                |

| R <sub>CM</sub>             | CM Pin Input Resistance                                                        |                                                                                                              |   |                 | 16.3                |                 | kΩ               |

| C <sub>CM</sub>             | CM Pin Input Capacitance                                                       |                                                                                                              |   |                 | 1.5                 |                 | pF               |

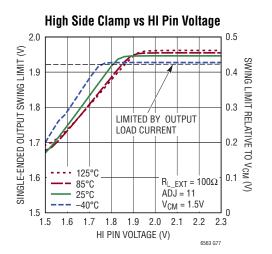

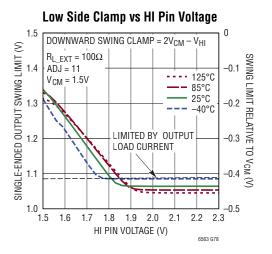

| Output Clamping             | (HI Pin) See Note 4                                                            |                                                                                                              | • |                 |                     |                 |                  |

| V <sub>HI_DEFAULT</sub>     | Default HI Pin Voltage                                                         |                                                                                                              |   |                 | 1.8                 |                 | V                |

| V <sub>HI_VOS</sub>         | High Side Clamp Offset Voltage                                                 | $V_{OUT(MAX)} - V_{HI}$ , HI = 1.7V, $I_{IN} = -200\mu A$                                                    |   | -160            | -65                 | 25              | mV               |

| V <sub>LO_VOS</sub>         | Low Side Clamp Offset Voltage                                                  | $V_{OUTBAR(MIN)}$ $-(2 \cdot V_{CM} - V_{HI})$ , HI = 1.7V, $I_{IN} = -200\mu A$                             |   | <del>-</del> 50 | 50                  | 150             | mV               |

| R <sub>HI</sub>             | HI Pin Input Impedance                                                         |                                                                                                              |   |                 | 13.6                |                 | kΩ               |

| CHI                         | HI Pin Input Capacitance                                                       |                                                                                                              |   |                 | 1.5                 |                 | pF               |

| <b>Input Current Ca</b>     | ncellation (OFFSET Pin)                                                        |                                                                                                              |   |                 |                     |                 |                  |

| V <sub>OFFSET_DEFAULT</sub> | Default OFFSET Pin Voltage                                                     |                                                                                                              |   |                 | 0                   |                 | V                |

| I <sub>CANCEL_MIN</sub>     | Minimum Input Cancellation Current                                             | V <sub>OFFSET</sub> = 0V                                                                                     |   |                 | 0                   |                 | μА               |

| I <sub>CANCEL_MAX</sub>     | Maximum Input Cancellation Current                                             | V <sub>OFFSET</sub> = 3.3V, Tilt = 3.3V                                                                      |   | 200             | 240                 |                 | μА               |

| G <sub>OFFSET</sub>         | OFFSET Pin Transconductance<br>(OFFSET Pin Voltage to Input Offset<br>Current) | $V_{OFFSET} = 0.2V$ to 0.4V, $I_{IN} = -40\mu A$                                                             |   | -145            | -110                | <del>-</del> 75 | μA/V             |

| R <sub>OFFSET</sub>         | OFFSET Pin Impedance                                                           |                                                                                                              |   |                 | 6.6                 |                 | kΩ               |

| ts_offset                   | Offset Voltage to Output Settling                                              | 1% of Final Value, I <sub>IN</sub> = −40μA                                                                   |   |                 | 100                 |                 | ns               |

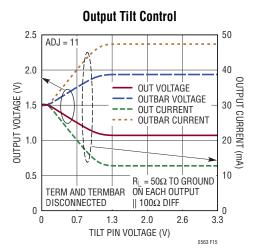

| Output Offset (TI           | ILT Pin)                                                                       |                                                                                                              |   |                 |                     |                 |                  |

| V <sub>TILT_DEFAULT</sub>   | Default Tilt Pin Voltage                                                       |                                                                                                              |   |                 | 2                   |                 | mV               |

| A <sub>TILT</sub>           | TILT Pin Slope, TILT to Differential Out                                       | V <sub>TILT</sub> = 0.2V to 0.4V                                                                             |   | -1.25           | -1                  | -0.7            | V/V              |

| TCA <sub>TILT</sub>         | A <sub>TILT</sub> Temperature Coefficient                                      | V <sub>TILT</sub> = 0.2V to 0.4V                                                                             |   |                 | -680                |                 | (μV/V)/°C        |

| R <sub>TILT</sub>           | TILT Pin Input Impedance                                                       |                                                                                                              |   |                 | 22.7                |                 | kΩ               |

**DC ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25\,^{\circ}\text{C}$ , ADJ0 = ADJ1 = PWRMD = OMUX =  $V_{CCI}$  = HI =  $V_{CCO}$  = 3.3V, TILT = OFFSET = 0,  $V_{CM}$  = 1.5V. All other input pins are floating unless stated otherwise.  $V_{OUTCM}$  is defined as (OUT + OUT)/2 and  $V_{OUTDIFF}$  is defined as (OUT – OUT),  $R_{L\_EXT}$  = 100 $\Omega$  differential, OUT connected to TERM and OUT connected to TERM.

| SYMBOL                     | PARAMETER                                                               | CONDITIONS                                                      |   | MIN  | TYP  | MAX            | UNITS    |

|----------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|---|------|------|----------------|----------|

| ADJO, ADJ1, CH             | SELO, CHSEL1 Pins with Internal Pull-D                                  | Jown Resistors                                                  |   |      | ,    |                | _        |

| $\overline{V_{IL}}$        | Input Low Voltage                                                       |                                                                 |   |      |      | 0.8            | V        |

| $\overline{V_{IH}}$        | Input High Voltage                                                      |                                                                 |   | 2.4  |      |                | V        |

| I <sub>IL</sub>            | Input Low Current                                                       | Pin Voltage = 0.8V                                              |   |      | 3.8  |                | μА       |

| I <sub>IH</sub>            | Input High Current                                                      | Pin Voltage = 2.4V                                              |   |      | 7.2  |                | μА       |

| C <sub>IN</sub>            | Pin Input Capacitance                                                   |                                                                 |   |      | 1.5  |                | pF       |

| R <sub>IN</sub>            | Pin Input Impedance                                                     | To GND                                                          |   |      | 218  |                | kΩ       |

| OMUX, PWRMD                | , Pins with Internal Pull-Up Resistors                                  |                                                                 |   |      |      |                |          |

| $V_{IL}$                   | Input Low Voltage                                                       |                                                                 |   |      |      | 0.8            | V        |

| $\overline{V_{IH}}$        | Input High Voltage                                                      |                                                                 |   | 2.4  |      |                | V        |

| I <sub>IL</sub>            | Input Low Current                                                       | Pin Voltage = 0.8V                                              |   |      | -12  |                | μА       |

| I <sub>IH</sub>            | Input High Current                                                      | Pin Voltage = 2.4V                                              |   |      | -8.6 |                | μA       |

| C <sub>IN</sub>            | Pin Input Capacitance                                                   |                                                                 |   |      | 1.5  |                | pF       |

| R <sub>IN</sub>            | Pin Input Impedance                                                     | To V <sub>CCI</sub>                                             |   |      | 208  |                | kΩ       |

| Power Supply               |                                                                         |                                                                 | ' |      |      |                |          |

| $\overline{V_S}$           | Operating Supply Range                                                  |                                                                 |   | 3.15 | 3.3  | 3.45           | V        |

| I <sub>VCCI</sub>          | Input Supply Current                                                    | Any Adjust Setting                                              | • | 27.8 | 34   | 39.4<br>40.4   | mA<br>mA |

| I <sub>VCCI_SHUTDOWN</sub> | Input Supply Current                                                    | PWRMD = OMUX = Logic Low                                        | • |      | 4.5  | 5.5<br>6       | mA<br>mA |

| I <sub>VCCO</sub>          | Output Supply Current                                                   | ADJ1 = Logic High, ADJ0 = Logic High<br>V <sub>CM</sub> = 1.50V | • | 49.4 | 64.5 | 81<br>82       | mA<br>mA |

|                            |                                                                         | ADJ1 = Logic High, ADJ0 = Logic Low<br>V <sub>CM</sub> = 1.25V  | • |      | 51.5 | 64.9<br>65.9   | mA<br>mA |

|                            |                                                                         | ADJ1 = Logic Low, ADJ0 = Logic High V <sub>CM</sub> = 1.0V      | • |      | 38   | 48<br>49       | mA<br>mA |

|                            |                                                                         | ADJ1 = Logic Low, ADJ0 = Logic Low<br>V <sub>CM</sub> = 0.75V   | • |      | 24.5 | 30.8<br>31.8   | mA<br>mA |

| I <sub>VCCO_SHUTDOWN</sub> | Output Supply Current                                                   | PWRMD = OMUX = Logic Low                                        | • |      | 0.1  | 0.2<br>0.22    | mA<br>mA |

| Is                         | Total Supply Current (I <sub>S(VCCI)</sub> + I <sub>S(VCCO)</sub> )     | ADJ1 = Logic High, ADJ0 = Logic High<br>V <sub>CM</sub> = 1.50V | • |      | 98.5 | 120.4<br>122.4 | mA<br>mA |

|                            | , ,                                                                     | ADJ1 = Logic High, ADJ0 = Logic High<br>V <sub>CM</sub> = 1.25V | • |      | 85.5 | 104.3<br>106.3 | mA<br>mA |

|                            |                                                                         | ADJ1 = Logic Low, ADJ0 = Logic High V <sub>CM</sub> = 1.0V      | • |      | 72   | 87.4<br>89.4   | mA<br>mA |

|                            |                                                                         | ADJ1 = Logic Low, ADJ0 = Logic Low<br>V <sub>CM</sub> = 0.75V   | • |      | 58.5 | 70.2<br>72.2   | mA<br>mA |

| I <sub>S_SHUTDOWN</sub>    | Total Supply Current (I <sub>S(VCCI)</sub> + I <sub>S(VCCO)</sub> )     | PWRMD = OMUX = Logic Low                                        | • |      | 4.6  | 5.8<br>6.3     | mA<br>mA |

| PSRR(V <sub>CCI</sub> )    | Input Power Supply Rejection Ratio $(\Delta V_{OUT}/\Delta V_{CCI})$    | $V_{CCI} = 3.15V \text{ to } 3.45V, V_{CCO} = 3.3V$             |   | 33   | 36   |                | dB       |

| PSRR(V <sub>CCO</sub> )    | Output Power Supply Rejection Ratio ( $\Delta V_{OUT}/\Delta V_{CCO}$ ) | $V_{CCO} = 3.15V \text{ to } 3.45V, V_{CCI} = 3.3V$             |   | 35   | 38   |                | dB       |

## DC ELECTRICAL CHARACTERISTICS

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC6563I is guaranteed to meet specified performance from -40°C to 85°C.

3.2 3.6

6563 G01

**Note 3:** The LTC6563H is guaranteed to meet specified performance from -40°C to 125°C.

**Note 4:** HI pin voltage should be at least 0.2V higher than V<sub>CM</sub>.

**Note 5:** This parameter is specified by design and/or characterization and is not tested in production.

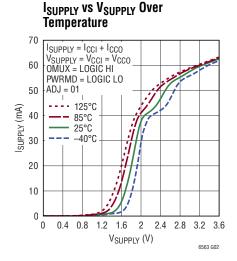

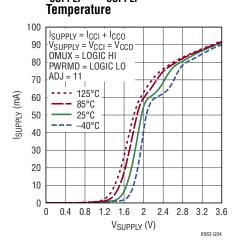

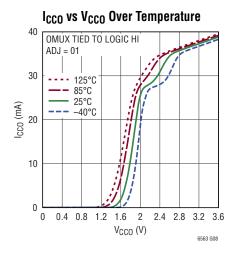

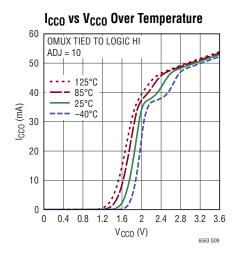

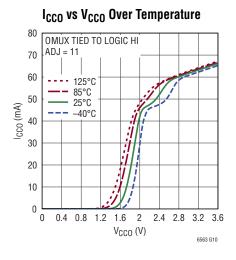

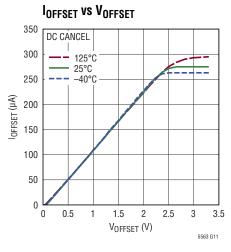

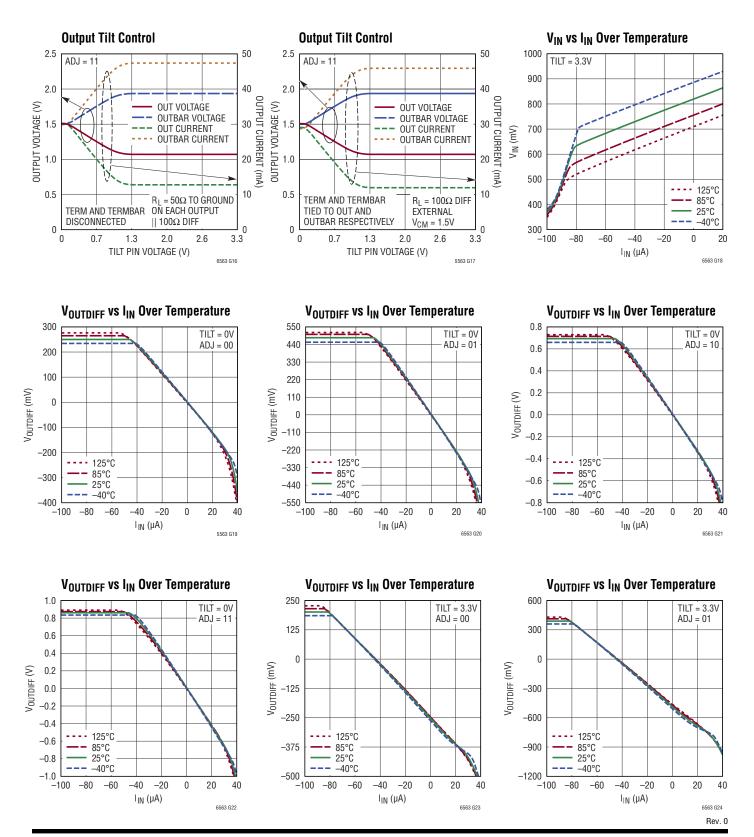

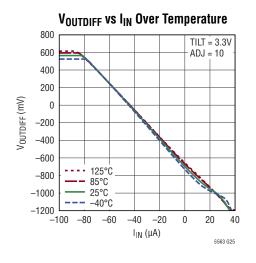

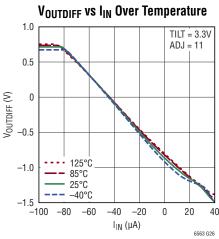

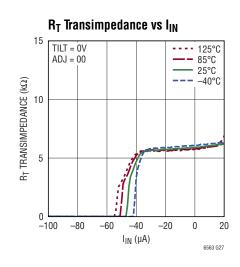

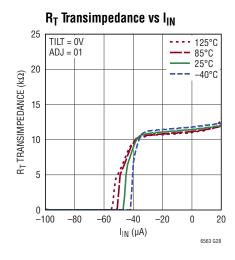

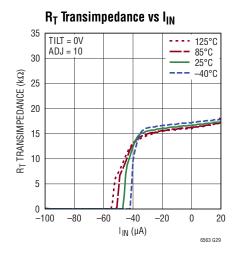

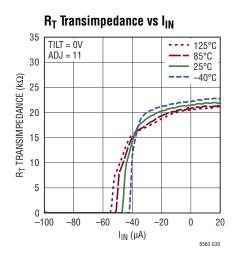

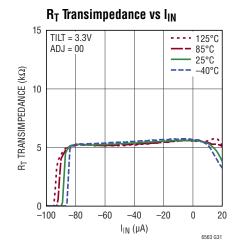

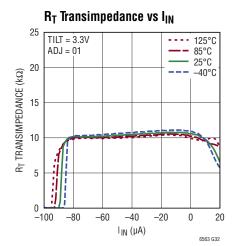

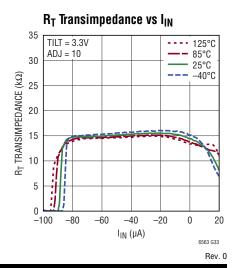

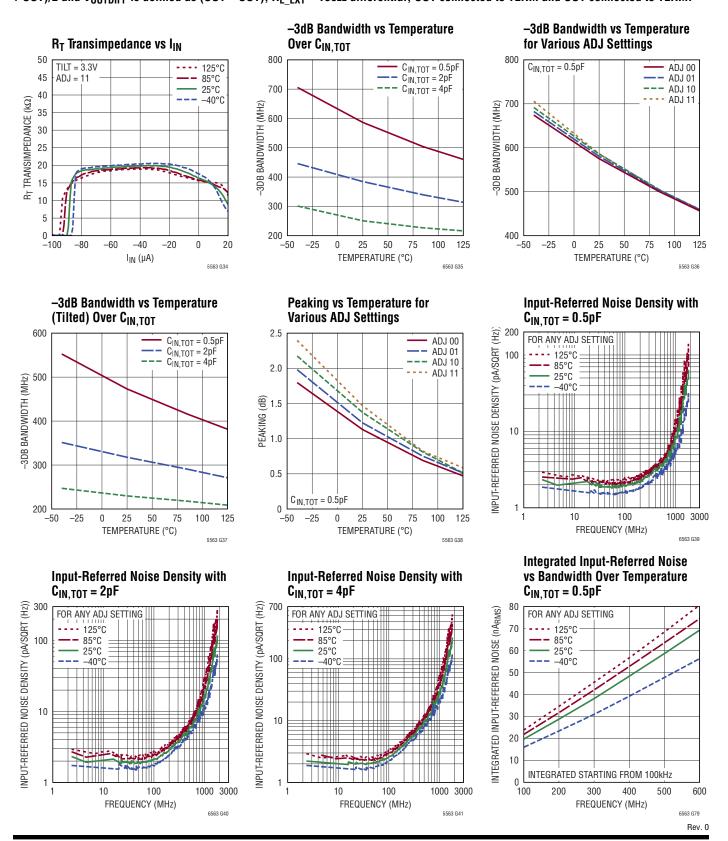

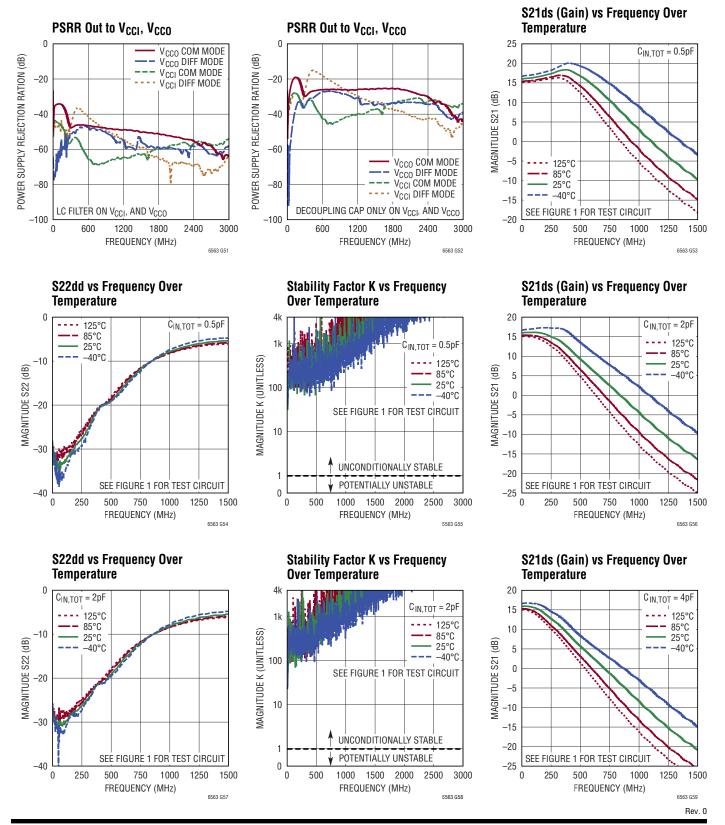

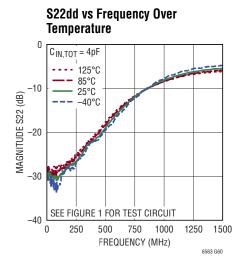

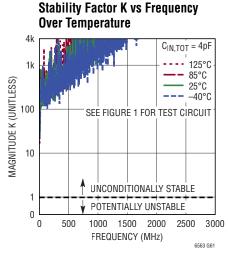

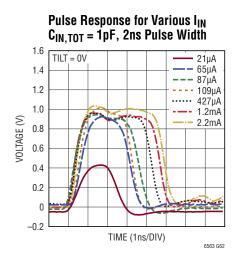

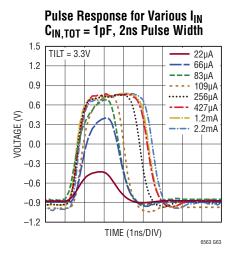

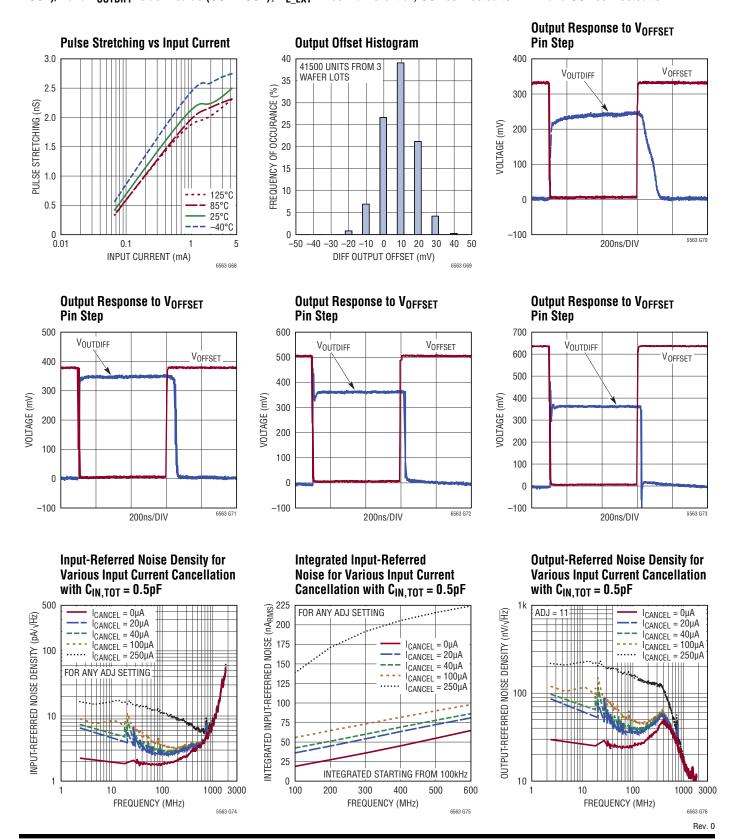

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSELO = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT -  $\overline{OUT}$ ),  $R_{L}$  EXT =  $100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to  $\overline{TERM}$ .

#### ISUPPLY VS VSUPPLY Over **Temperature** 50 I<sub>SUPPLY</sub> = I<sub>CCI</sub> + I<sub>CCO</sub> V<sub>SUPPLY</sub> = V<sub>CCI</sub> = V<sub>CCO</sub> OMUX = LOGIC HI 40 PWRMD = LOGIC LO ADJ = 0035 --- 125°C 30 **−−** 85°C 25 - 25°C - -40°C 20 15 10 5

V<sub>SUPPLY</sub> (V)

ISUPPLY VS VSUPPLY Over

0 0.4 0.8 1.2 1.6 2 2.4 2.8

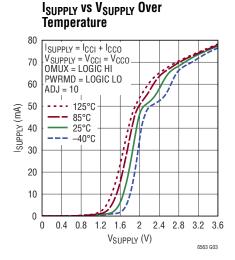

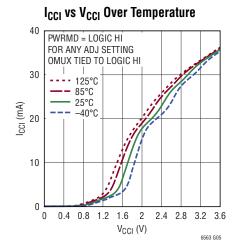

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT -  $\overline{OUT}$ ),  $R_{L_EXT} = 100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to TERM.

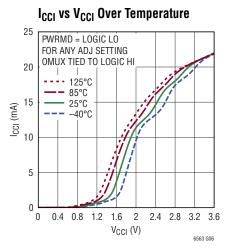

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT -  $\overline{OUT}$ ),  $R_{L}$  EXT =  $100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to  $\overline{TERM}$ .

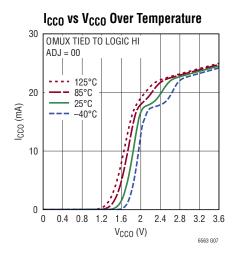

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT -  $\overline{OUT}$ ),  $R_{L,EXT} = 100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to TERM.

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT -  $\overline{OUT}$ ),  $R_{L_EXT} = 100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to TERM.

## **TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 = $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V. $V_{OUTCM}$ is defined as (OUT + $\overline{OUT}$ )/2 and $V_{OUTDIFF}$ is defined as (OUT - $\overline{OUT}$ ), $R_{L_EXT} = 100\Omega$ differential, OUT connected to TERM and $\overline{OUT}$ connected to TERM.

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT -  $\overline{OUT}$ ),  $R_{L}$  EXT =  $100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to  $\overline{TERM}$ .

## **TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = 0FFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 = $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V. $V_{OUTCM}$ is defined as (OUT + $\overline{OUT}$ )/2 and $V_{OUTDIFF}$ is defined as (OUT - $\overline{OUT}$ ), $R_{L_EXT} = 100\Omega$ differential, OUT connected to TERM and $\overline{OUT}$ connected to TERM.

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT -  $\overline{OUT}$ ),  $R_{L_EXT} = 100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to TERM.

**TYPICAL PERFORMANCE CHARACTERISTICS** Unless otherwise noted specifications are at CHSEL0 = TILT = OFFSET = 0V, HI = CHSEL1 = PWRMD = ADJ0 = ADJ1 =  $V_{CCI} = V_{CCO} = 3.3V$ , and CM = 1.5V.  $V_{OUTCM}$  is defined as (OUT +  $\overline{OUT}$ )/2 and  $V_{OUTDIFF}$  is defined as (OUT –  $\overline{OUT}$ ),  $R_{L_EXT} = 100\Omega$  differential, OUT connected to TERM and  $\overline{OUT}$  connected to  $\overline{TERM}$ .

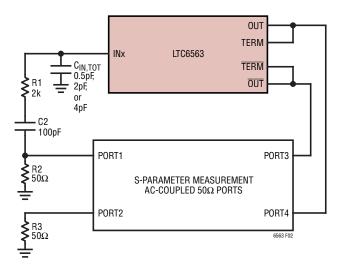

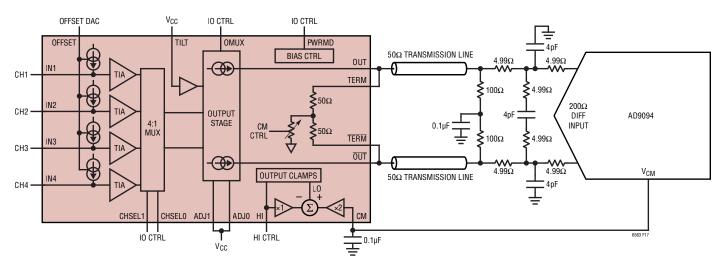

Figure 1. Electrical Characterization Test Circuit

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 2. S-Parameters Test Circuit

Figure 3. Driving HMCAD1511 (ADJ11, Tilt = 3.3V, CM = 0.9V, FS =  $2.4V_{P-P}$ )

## PIN FUNCTIONS

**GND** (Pins 1, 3, 18, 20, Exposed Pad Pin 25): Negative Power Supply. Normally tied to ground. All GND pins and the exposed pad must be tied to the same voltage. The exposed pad (pin 25) should have multiple via holes to the underlying ground plane for low inductance and good heat transfer.

**IN4**, **IN1**, **IN2**, **IN3** (**Pin 2**, **Pin 19**, **Pin 21**, **Pin 24**,): Input pins for the transimpedance amplifier for channels 4, 1, 2, and 3 respectively. The active channel is internally biased to 0.8V. See the Applications Information section for specific recommendation.

**PWRMD (Pin 4):** Power mode is a CMOS input for controlling the power consumption. The PWRMD pin has a 208k internal pull-up resistor to  $V_{CCI}$ . Default value is 3.3V.

$V_{CCI}$  (Pin 5): Positive power supply for the input stages. Typically, 3.3V. A series ferrite bead such as the MPZ1005A331ETD25 should be used and bypass capacitor of 680pF and 0.1µF should be placed as close to the part as possible between  $V_{CCI}$  and ground.

**OMUX (Pin 6):** Output MUX is a CMOS input for controlling the output multiplexing function. The OMUX pin has internal 208k pull-up resistor to  $V_{CCI}$ . Default value is 3.3V.

**CM** (**Pin 7**): Output Common Mode Reference Voltage. The voltage on this pin sets the output common mode voltage level. On a 3.3V supply, the CM pin floats to a default 0.9V. The CM pin has an input impedance of  $16.3k\Omega$ . The CM pin should be bypassed with a high-quality ceramic capacitor of at least  $0.01\mu F$ .

**HI (Pin 8):** High Side Clamp Voltage. The voltage applied to the HI pin sets the upper voltage limit to  $\overline{\text{OUT}}$  and  $\overline{\text{OUT}}$  pins. The HI voltage also limits the lower voltage swing on both output pins to  $2V_{CM}-HI$ , for symmetrical clamping around the CM voltage. On a 3.3V supply, the HI pin will

float to a default 1.8V. The HI pin has an input impedance of 13.6k $\Omega$ . The HI pin should be bypassed with a high-quality ceramic capacitor of at least 0.01 $\mu$ F.

OUT, OUT (Pin 9, Pin 12): Differential Output Pins. For voltage mode output, connect OUT to TERM and OUT to TERM. For current mode output or when using external load resistors, float TERM and TERM.

**TERM**, **TERM** (**Pin 10**, **Pin 11**): Internal Termination. These pins have  $50\Omega$  load resistors coupled to GND and are intended to connect to the differential output pins.

**CHSEL1, CHSEL0 (Pin 13, Pin 15):** MSB and LSB for Channel Selection. These pins are CMOS inputs with internal 218k pull-down resistors to GND.

$V_{CCO}$  (Pin 14): Positive power supply for the output stage. Typically, 3.3V.  $V_{CCO}$  can be tied to  $V_{CCI}$  for single supply operation. A series ferrite bead such as the MPZ1005A331ETD25 should be used and bypass capacitors of 680pF and 0.1μF should be placed as close as possible between  $V_{CCO}$  and ground.

**OFFSET (Pin 16):** Input Offset Adjust. This pin accepts a voltage input that controls current sources on each input pin. These current sources can be used to cancel DC currents flowing into the detector. The OFFSET pin has an internal pull-down resistor to GND.

**TILT (Pin 17):** Output Differential Offset. The voltage on this pin controls the outputs' differential offset. The TILT pin has an internal 22.7k pull-down resistor to GND.

**ADJO**, **ADJ1** (Pin 22, Pin 23): LSB and MSB for output gain and current adjusts. The adjust pins set the output stage quiescent current and current gain. See Applications Information section to optimize the ADC interface. These pins are CMOS inputs with internal 218k pull-down resistors to GND.

## **BLOCK DIAGRAM**

## **OPERATION**

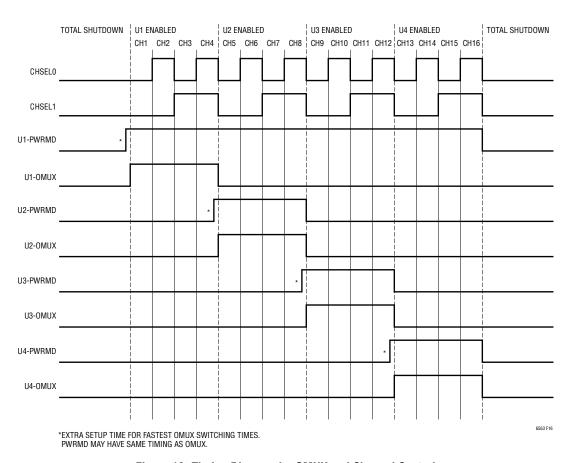

The LTC6563 is a four channel transimpedance amplifier with an integrated 4-to-1 multiplexer and ADC driver stage. Each of the transimpedance amplifiers converts an input current to an output voltage. The integrated 4:1 multiplexer simplifies the system design while saving space and power. In addition, output multiplexing is possible by using the OMUX pin. This allows multiple 4-channel LTC6563 devices to be combined. 8, 12, 16 ... 32 input channels are easily multiplexed into a single differential output.

The LTC6563 is optimized to drive high speed differential input analog-to-digital converters (ADCs).  $\overline{OUT}$  and OUT have single-ended swings from as low as about 180mV to about  $V_{CCO}-1V$ . The LTC6563 provides four modes of output drive for matching input swing of high-speed ADCs.

The tilt feature allows the output stage to offset to take advantage of the full differential input range of the ADCs. The outputs have programmable clamps that limit the

output swing in saturation events. These clamps provide protection to the front end of the ADC. The HI pin sets the maximum swing, while a symmetric minimum swing limit is set up internally.

In typical LIDAR applications, the LTC6563 amplifies the output current of an APD. APD are biased near breakdown to achieve high current gain. Under intense optical illumination, they can conduct large currents, often in excess of 1A. The LTC6563 survives and quickly recovers from large overload currents of this magnitude. During recover, any TIA is blinded from subsequent pulses. The LTC6563 recovers from 1mA saturation events in less than 2.5ns without phase reversal, minimizing this form of data loss.

Ambient light is problematic for LIDAR receiver chains. The DC current can easily saturate the linear range of any TIA. The LTC6563 provides a control for DC cancelation to the inputs and can cancel up to  $200\mu A$  of DC current. The DC cancelation is designed to minimizing additive noise.

#### **Output Offset and Current Control**

The output stage of the LTC6563 has many options. The ADJ1 and ADJ0 pins provide four options for the output current drive. The output voltage swing is dependent on the adjust setting, the external differential termination resistor, and the Tilt input. The purpose of the Tilt input is to offset the DC output voltages, thereby increasing the full output swing of the TIA for unipolar inputs. Output TILT is essential for the ADC as the input from the photodetector is unipolar. To maximize the input swing of the ADC, the DC value of OUT is offset low while the DC value of OUT is offset high. This allows the LTC6563 to maximize the full dynamic range of the ADC. These pins should be connected to low noise inputs.

LTC6563 transimpedance gain (RT) consists of the overall gain from the multi-stages involved in producing the output for a given input current. The output is differential and ½ RT is achieved if only one of the outputs is utilized.

It is possible to change the transimpedance gain (RT) by changing  $R_{L\_EXT}$  as shown in Table 1, and Table 2. Also, since the ADJ pins respond in less than 100ns, these pins can be used for on the fly gain switching if the application needs that. An example would be to reduce the TIA gain if an overly strong signal is received by the LTC6563. It's important to note the following regarding gain adjustment:

- The linear input current range (40μA with no Tilt, 90μA with full Tilt) is not affected by these changes.

- R<sub>LDIFF</sub> refers to the total load seen by the differential output(s) whereas R<sub>L\_EXT</sub> is the external differential load. Refer to Figure 17 to Figure 19 to see examples of various external single-ended load ( $50\Omega$ ,  $75\Omega$ , and  $100\Omega$ ) illustrated.

Table 1. Output Stage when Tilt Pin = OV, OUT Connected to TERM and  $\overline{OUT}$  Connected to  $\overline{TERM}^1$

| IIN (μA) | ADJ1 | ADJ0 | OUT (mA) | OUTBAR (mA) | $R_T(\Omega)$ $R_{L\_EXT} = 100\Omega \text{ DIFF}$ | $R_T(\Omega)$ $R_{L\_EXT} = 200\Omega \text{ DIFF}$ | $R_T(\Omega)$ $R_{L\_EXT} = OPEN$ |

|----------|------|------|----------|-------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------|

| 0        | 0    | 0    | 7        | 7           | 5.55k                                               | 7.4k                                                | 11.1k                             |

|          | 0    | 1    | 14       | 14          | 11.1k                                               | 14.8k                                               | 22.2k                             |

|          | 1    | 0    | 21       | 21          | 16.65k                                              | 22.2k                                               | 33.3k                             |

|          | 1    | 1    | 28       | 28          | 22.2k                                               | 29.6k                                               | 44.4k                             |

| 45       | 0    | 0    | 12       | 2           | 5.55k                                               | 7.4k                                                | 11.1k                             |

|          | 0    | 1    | 24       | 4           | 11.1k                                               | 14.8k                                               | 22.2k                             |

|          | 1    | 0    | 36       | 6           | 16.65k                                              | 22.2k                                               | 33.3k                             |

|          | 1    | 1    | 48       | 8           | 22.2k                                               | 29.6k                                               | 44.4k                             |

$<sup>^{1}</sup>$  Output voltage compliance to be observed at higher R<sub>L EXT</sub> and higher ADJ settings.

Table 2. Output Stage when Tilt Pin =  $V_{CC}$ , OUT Connected to TERM and  $\overline{OUT}$  Connected to  $\overline{TERM}^1$

| IIN (μA) | ADJ1 | ADJ0 | OUT (mA) | OUTBAR (mA) | $R_T(\Omega)$ $R_{L\_EXT} = 100\Omega \text{ DIFF}$ | $R_T(\Omega)$ $R_{L\_EXT} = 200\Omega \text{ DIFF}$ | $R_T(\Omega)$ $R_{L\_EXT} = OPEN$ |

|----------|------|------|----------|-------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------|

| 0        | 0    | 0    | 2        | 12          | 5.55k                                               | 7.4k                                                | 11.1k                             |

|          | 0    | 1    | 4        | 24          | 11.1k                                               | 14.8k                                               | 22.2k                             |

|          | 1    | 0    | 6        | 36          | 16.65k                                              | 22.2k                                               | 33.3k                             |

|          | 1    | 1    | 8        | 48          | 22.2k                                               | 29.6k                                               | 44.4k                             |

| 90       | 0    | 0    | 12       | 2           | 5.55k                                               | 7.4k                                                | 11.1k                             |

|          | 0    | 1    | 24       | 4           | 11.1k                                               | 14.8k                                               | 22.2k                             |

|          | 1    | 0    | 36       | 6           | 16.65k                                              | 22.2k                                               | 33.3k                             |

|          | 1    | 1    | 48       | 8           | 22.2k                                               | 29.6k                                               | 44.4k                             |

$<sup>^{1}</sup>$  Output voltage compliance to be observed at higher R<sub>L EXT</sub> and higher ADJ settings.

- Increasing R<sub>I DIFF</sub> slightly reduces the signal bandwidth.

- Output voltage compliance (V<sub>COMPLIANCE</sub>) to be observed relative to R<sub>LDIFF</sub>, ADJ settings, and CM voltage. Here is an example where output voltage compliance is violated:

$$R_{LDIFF}=100\Omega,\ Tilt=V_{CC},\ ADJ1=1,\ ADJ0=0,\ CM=1.7V,\ I_{IN}=90\mu A$$

Output Voltage (max) =

$$V_{CM} + \frac{|I_{OUT} - I_{OUTBAR}|}{2} \cdot \frac{R_{LDIFF}}{2}$$

Referring to Table 2 to read output current values:

Output Voltage (max) =

$$1.7V + \frac{|36\text{mA} - 6\text{mA}|}{2} \cdot \frac{100\Omega}{2} = 2.45V!$$

The maximum output voltage must remain below  $V_{CCO}-1V$  (~2.3V) to comply with the  $V_{COMPLIANCE}$  rating. Possible remedies are reducing output current(s) by using lower power ADJ settings, reducing the input APD current, reducing the differential load, or reducing the CM voltage.

#### **Power Considerations**

The LTC6563 has many power modes of operation. The state of the PWRMD, OMUX and ADJ pins will dictate the amount of current the LTC6563 will draw. Multiple power modes are offered to allow the user to select the

appropriate one based upon the application while minimizing power dissipation.

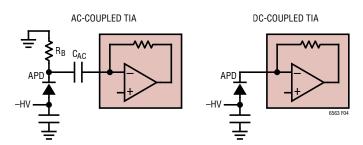

#### Coupling the TIA Input – AC vs DC

Although the LTC6563 can AC-couple to the detector, best performance is achieved when DC-coupled to a negatively biased APD. DC-coupling reduces component count while allowing a DC current path from the APD. The LTC6563 OFFSET feature is designed to cancel DC currents. The maximum performance for switching speeds and saturation recovery occurs in this DC-coupled configuration.

When AC-coupling to the TIA input,  $R_B$ , is needed to establish a bias point for the detector. It is worth noting that  $R_B$  is a parallel path with the TIA for the APD current to flow through and it will impact the effective signal chain output gain.

This value of the biasing resistor and AC-coupling capacitor,  $C_{AC}$ , can potentially create a long time-constant.  $C_{AC}$  is chosen based on the reactance at the frequency of interest. However,  $R_B$  ideally should be large to avoid stealing

Figure 4. AC-Coupled Detector Circuit

Table 3. LTC6563 Power Dissipation Modes. X = Don't Care

| PWRMD | OMUX | ADJ1 | ADJ0 | I <sub>VCCI</sub> (mA) | I <sub>VCCO</sub> (mA) | I <sub>TOTAL</sub> (mA)                              | DESCRIPTION                                                                                                               |

|-------|------|------|------|------------------------|------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 0     | 0    | Χ    | Χ    | 4.5                    | 0.1                    | 4.6                                                  | LTC6563 shutdown.                                                                                                         |

| 0     | 1    | 0    | 0    | 21                     | 24.5                   | 45.5                                                 | LTC6563 enabled, non-selected inputs powered down, CM pin control                                                         |

| 0     | 1    | 0    | 1    | 21                     | 38                     | 38 59 disabled. This setting appropriate for a Respo | disabled. This setting appropriate for a Responder device in a multi-chip/                                                |

| 0     | 1    | 1    | 0    | 21                     | 51.5                   | 72.5                                                 | a main channel approation.                                                                                                |

| 0     | 1    | 1    | 1    | 21                     | 64.5                   | 85.5                                                 |                                                                                                                           |

| 1     | 0    | Χ    | Χ    | 35                     | 0.1                    | 35.1                                                 | LTC6563 deselected (outputs stage off), non-selected inputs powered up.                                                   |

| 1     | 1    | 0    | 0    | 34                     | 24.5                   | 58.5                                                 | LTC6563 enabled, non-selected inputs powered up, CM pin control active                                                    |

| 1     | 1    | 0    | 1    | 34                     | 38                     | 72                                                   | in setting output CM voltage. This setting appropriate for a Controller device in a multi-chip/multi-channel application. |

| 1     | 1    | 1    | 0    | 34                     | 51.5                   | 85.5                                                 | aconocini a maia omprinaia onamoi appiloation.                                                                            |

| 1     | 1    | 1    | 1    | 34                     | 64.5                   | 98.5                                                 |                                                                                                                           |

Rev. 0

current from the TIA path from APD signal. On one hand large  $R_B$  causes large RC time constants, while low  $R_B$  reduces the effective gain of the APD.

Another negative impact of this RC network is in the case for saturation events. When a large signal is received from the APD, this event will charge  $C_{AC}$ . This will negatively move the input bias of the TIAs and change the TIAs input impedance to transimpedance  $14k\Omega$ . This  $14k\Omega$  coupled with  $R_B$  and  $C_{AC}$  time constant will add the saturation recover time. Practical values of 100pF  $C_{AC}$  and  $R_B$  of  $2.2k\Omega$  will have large saturation recovery times >1µs with >50mA input signals. This effectively blinds the signal chain for the next input signal.

#### **Channel Selection**

There are four TIA inputs to the LTC6563. The active channel is selected using two channel selection bits CHSEL0 and CHSEL1. When a channel is changed and PWRMD is high, an output glitch takes <10ns to settle. When PWRMD is low and a channel is changed, an output glitch takes <500ns to settle. Inactive channels have 30dB of channel to channel isolation at 400MHz when PWRMD pin is high. When PWRMD is low the channel isolation is increased to more than 48dB.

**Table 4. Channel Selection**

| CHSEL1 | CHSELO | OMUX | ACTIVE CHANNEL |

|--------|--------|------|----------------|

| 0      | 0      | 1    | 1              |

| 0      | 1      | 1    | 2              |

| 1      | 0      | 1    | 3              |

| 1      | 1      | 1    | 4              |

| X      | Х      | 0    | Hi-Z           |

#### **DC Input Cancelation**

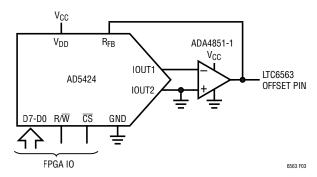

The LTC6563 features a voltage controlled current source for DC input current cancelation with minimal noise impact. Identical currents are applied to each TIA input. The maximum current cancelation is  $200\mu A$ . The OFFSET pin was designed to accommodate external closed loop design for fast settling and fast switching times. See  $I_{OFFSET}$  vs  $V_{OFFSET}$  curve for the transfer function. It is recommended to use a high-speed DAC to control the OFFSET pin.

Figure 5. Recommended DC Cancel Circuit

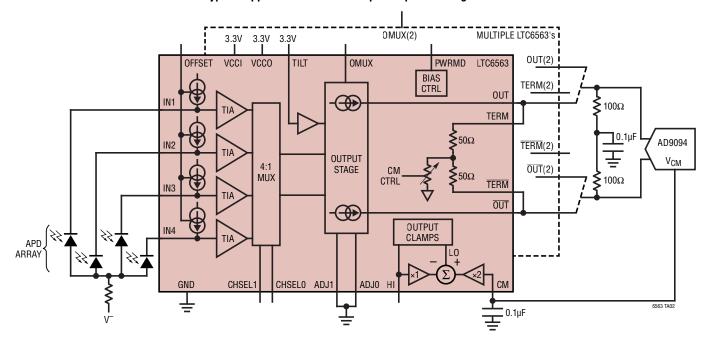

#### **Output MUXing**

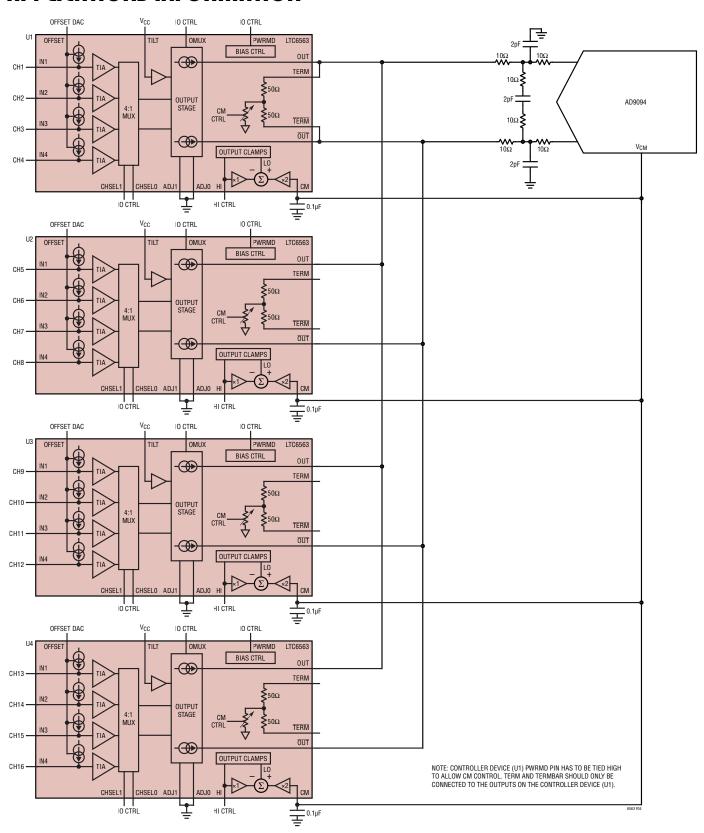

Refer to Figure 6 schematic. The output multiplexing (OMUX) requires at least one additional LTC6563 devices to operate in a Controller/Responder relationship. To multiplex multiple LTC6563's they need to share a DC connection at their outputs. The controller LTC6563 (U1) output stage needs to be connected to the internal termination resistors. For the CM control to function, the controller PWRMD pin must remain HIGH during the time any of the inputs of all the parallel network are enabled. That is because the CM servo loop is disabled if PWRMD is deasserted (low). The controller LTC6563 output circuit (U1) will control the common mode for all the multiplexing. All CM pins (U1-U4) are to be connected to the common mode of the ADC. If the output clamping feature (HI pin) is implemented, all CM pins (U1-U4) need to be connected to the same voltage for proper operation. Also, tie all HI pins (U1-U4) together and apply the required clamping voltage to them. The HI pin is used to set the high side clamp voltage at outputs. Internal circuity generates a symmetric low side clamp voltage with respect to the common mode voltage V<sub>CM</sub>.

Maximum output high side voltage = HI pin voltage

Minimum output low side voltage =  $V_{CM} - (HI - V_{CM}) = 2V_{CM} - HI$

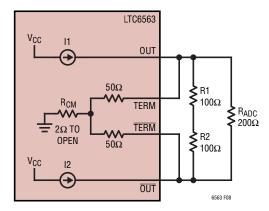

#### **Setting the Output CM Voltage**

The LTC6563 can set the output Common Mode (CM) voltage using the CM input pin provided on the device.

Figure 6. Typical Application with Multiplexed Outputs

In applications where the LTC6563 is to drive an ADC, this is useful in matching the TIA output(s) to the ADC analog input CM. This effectively eliminates the need for a separate ADC-driver which saves cost, power, as well as board complexity and real estate.

The CM servo loop operates by varying the CM CTRL variable resistor internal to the LTC6563 such that  $V_{CMO}$ , average of  $V_{OUT}$  and  $V_{OUTBAR}$  voltages or  $(V_{OUT} + V_{OUTBAR})/2$ , matches the voltage applied to the CM. The loop will NOT function unless two conditions are met:

- 1. PWRMD must be set HI to activate the CM circuit.

- 2. OUT and OUT must have a DC connection to TERM and TERM respectively.

The internal  $50\Omega$  resistor(s) on the TERM and  $\overline{\text{TERM}}$  pins provide a current path for CM servo functionality and serve as the load for the LTC6563's current mode output. Driving  $50\Omega$  terminated transmission lines or other impedance-matched loads is easily done using these internal resistors.

When using the output MUXing capability with multiple LTC6563's, such as the schematic shown in Figure 6, only one pair of TERM and TERMBAR pins should be connected

to the OUT and OUT. The device with the connected TERM and TERM will then set the CM for the MUX'ed devices.

#### **Determining the CM Range**

CM servo loop's voltage range is easily calculated using Ohm's law, as the output circuit can be described as a pair of current sources and a resistor network (see Figure 8). The amount of current supplied by the OUT and OUT current sources is determined by the ADJ setting, and the impedance at the output pins is determined by the internal and external resistor networks. These factors will determine the range of possible DC voltages at the outputs.

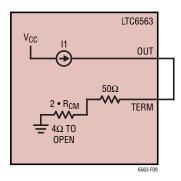

Figure 8. Equivalent Circuit for Driving an ADC with no GND (CM Referenced) External Load

Figure 7. Typical Connection for CM Control/ADC Driving

In order to simplify the analysis, an intuitive way to look at the output loading is to examine its equivalent half-circuit as shown in Figure 9. With the half-circuit method, any impedance that is shared between the two halves appears as double its original value (e.g.  $R_{CM}$  appears as 2 •  $R_{CM}$  below).

Figure 9. CM Half-Circuit Equivalent for a Non-Grounded External Load

The internal CM CTRL resistance varies from about  $2\Omega$  to essentially an open circuit. At the lower end of the CM CTRL resistance,  $R_{CM}$ , the output CM voltage will be at the minimum it can reach. And at the higher end of  $R_{CM}$ , it will be at the maximum it can reach.

The external CM resistance can also vary greatly, depending on whether any external loads are terminated differentially or to GND.

#### **Detailed Example 1: Differential Termination ONLY**

With an external load connected, the output CM current splits between the internal TERM pin and the external load. However, with the configuration shown in Figure 7 and simplified in Figure 8, with no external CM DC current path to ground, the entire output CM current must flow through the internal TERM resistor(s).

In Figure 8, the external loading by the ADC and the cable termination network of R1, and R2 has no effect on the CM loading of the LTC6563. The range of output CM voltage will be as follows:

$$V_{CMO} = I_0 \bullet (50\Omega + 2R_{CM}) \tag{1}$$

For the ADJ setting of 00 where Io is 7mA (see Table 1 and Table 5) here is the computation of min  $V_{CMO}$  possible (corresponding to  $R_{CM} = 2\Omega$ ):

$$V_{CMO}$$

(minimum) = 7mA • (50 $\Omega$  + 2 • 2 $\Omega$ ) = 380mV (2)

At the other extreme of  $V_{CMO}$  when  $R_{CM}$  opens, the output CM voltage will only be limited to the LTC6563 output compliance voltage which is about 1V below  $V_{CC}$  (or about 2.3V with  $V_{CC}=3.3V$ ).

Naturally, if the ADJ setting is changed, the  $V_{CMO}$  range will vary accordingly. Table 5 shows the minimum computed output CM voltage, output full scale swing, and TIA gain (RT) for various ADJ settings applied to the circuit in Figure 7.

For a higher Transimpedance gain (RT) or higher ADC FS swing, higher ADJ output current settings can be chosen. Summary of how ADJ affects the TIA gain and differential output voltage swing is tabulated in Table 5.

Here is a sample calculation of the values in Table 5 (50 $\Omega$  Net diff load, full tilt) for ADJ 00 as an illustration:

- a. Output current values (ADJ 00) with max input current of 90µA (from Table 2): 12mA, 2mA

- b. Net diff output load:  $50\Omega$  ( $25\Omega$  on each output)

RT Calculation: RT( $k\Omega$ ) =

c.

$$\frac{25\Omega[(12\text{mA} - 2\text{mA}) - (2\text{mA} - 12\text{mA})]}{90\text{uA}} = 5.56\text{k}\Omega$$

Table 5. CM Minimum Voltage and Other Operating Performance Values for Various ADJ Settings of Figure 7

| ADJ1 | ADJ0 | CM/AVERAGE OUTPUT<br>CURRENT I <sub>O</sub> (mA) | RT (kΩ) | ADC FS DIFF VOLTAGE<br>SWING WITH FULL<br>TILT (mV <sub>P-P</sub> ) | MIN CM VOLTAGE (mV) |

|------|------|--------------------------------------------------|---------|---------------------------------------------------------------------|---------------------|

| 0    | 0    | 7                                                | 5.6     | 500                                                                 | 380                 |

| 0    | 1    | 14                                               | 11.1    | 1000                                                                | 756                 |

| 1    | 0    | 21                                               | 16.7    | 1500                                                                | 1134                |

| 1    | 1    | 28                                               | 22.2    | 2000                                                                | 1512                |

Rev. 0

- d. ADC FS diff voltage calculation =  $90\mu A \cdot 5.56k\Omega = 500mV_{P-P}$

- e. In CM/Average Output Current (from Table 1): 7mA

- f.  $V_{CMO}$  (minimum) =  $I_0 \cdot (50\Omega + 2 \cdot 2\Omega) = 380$ mV where  $I_0 = 7$ mA,  $50\Omega$  is the TERM internal resistance, and the  $2\Omega$  is the internal  $R_{CM}$  minimum value

The data in Table 5 can be used to examine the real-world problem of driving the AD9094 ADC, the input requirements of which are shown below:

Differential Input Voltage Range:  $1.44V_{P-P}$  to  $2.16V_{P-P}$  (programmable)

Common Mode Voltage: 1.43V

As can be seen from Table 5, operating the LTC6563 with ADJ 10 falls in the range of the required AD9094 FS swing voltage  $(1.44V_{P-P})$  to  $2.16V_{P-P}$ , and also complies with the required AD9094 CM voltage (1.43V) by allowing an output CM voltage as low as 1.13V. Therefore, ADJ 10 is an appropriate setting for driving the AD9094.

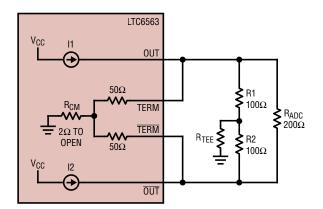

#### Detailed Example 2: Lowering the CM Voltage with a Tee Resistor or External DC Termination to Ground

Adding a path to ground from the center of the load resistors (R1, and R2) can lower the CM voltage. This can be in the form of grounding the middle of R1, and R2, or alternatively adding a TEE resistor to ground to avoid

dropping the CM voltage too low. This technique (shown in Figure 10) allows for more flexibility in aligning the TIA to an ADC or a given differential load and ADJ setting.

The TEE resistor will appear as double its value in the half-circuit. The equivalent CM load and CM voltage can be written as:

$$V_{CMO} = I_0 \cdot [(50\Omega + 2R_{CM})||(R1 + 2R_{TFF})]$$

(3)

Note that adding  $R_{TEE}$  to the schematic only affects the CM parameters of the circuit and has no bearing on the differential voltage swing and the resulting transimpedance gain of the circuit. A shunt capacitor to ground across  $R_{TEE}$  can be added to ensure no spurious AC signal appears at this node.

For the particular case of Figure 7 schematic modified to include  $R_{TEE}=20\Omega$  with ADJ = 11 ( $I_0=28\text{mA}$  from Table 1), the AD9094 CM voltage requirement (1.43V) would be easily satisfied since the CM servo loop would be able to adjust the output CM from 1.1V minimum (with  $R_{CM}=2\Omega$ , previously 1.51V minimum from Table 5 without  $R_{TEE}$ ) to >2.3V (device output compliance volage) maximum using Equation 3.

#### **Operation without Internal CM Servo Loop**

There may be applications where the CM servo loop function built into the LTC6563 is not needed, as would be the case if the TIA output is not used to drive an ADC.

Figure 10. TEE Resistor Loading (Left) and Its Equivalent CM Half-Circuit (Right)

Under these conditions, the following pin settings should be used:

- 1. TERM and TERM should be left floating.

- An external circuit capable of sinking the output current must be used. This task is most easily accomplished by providing external termination to ground.

- 3. The CM pin *must* be tied to the expected output CM voltage. The output clamps levels are calculated from CM and HI pins, so failure to set the CM pin properly may result in undesired signal clamping.

When the TERM and  $\overline{\text{TERM}}$  pins are left floating, the output CM voltage will be solely a function of the LTC6563 ADJ setting and the external CM load. For example, with ADJ11 setting (I<sub>0</sub> = 28mA) and 50 $\Omega$  to ground on each output, the output CM voltage will be:

$$V_{CMO} = I_0 \bullet R_{LOAD CM} = 28mA \bullet 50\Omega = 1.4V$$

(4)

With the CM servo loop function disabled, the LTC6563's CM pin should be tied to a voltage that is close to the expected CM value (1.4V in the example stated just above). The output clamp circuit assumes that CM is equal to the actual output CM voltage. If this is not the case, the clamping voltage set by the HI pin will be miscalculated, and undesired signal clipping may result. For this

purpose, a replica  $V_{CMO}$  voltage can simply be generated off the device  $V_{CC}$  pin using  $k\Omega$  range voltage division resistors.

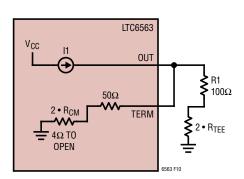

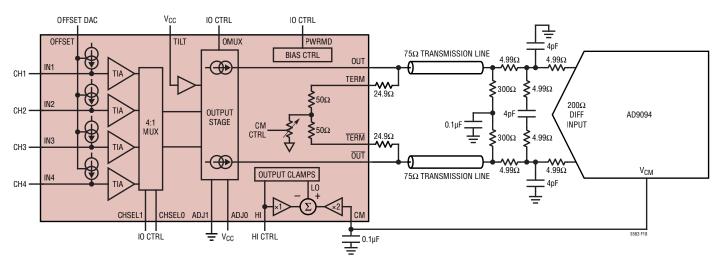

#### **Increasing Output Impedance**

It may be desirable to change the output termination impedance in order to adjust the output signal amplitude. In addition, the flexibility of LTC6563's output structure allows for impedance matching to a variety of different loads or transmission line impedances, which is critical for high speed signal integrity. In the following example, the output circuit will be modified to present a  $75\Omega$  source impedance for driving a  $75\Omega$  transmission line and ADC load.

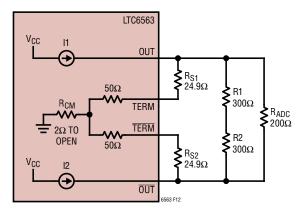

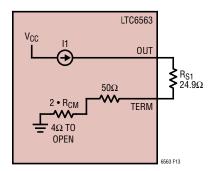

Consider the configuration shown in Figure 11 schematic. The output impedance of the LTC6563 is raised to  $75\Omega$  by adding  $24.9\Omega$  resistors in series with the internal  $50\Omega$  TERM resistors. The TIA now presents an output impedance that matches the  $75\Omega$  transmission line as well as the net ADC-side SE impedance. The transmission line ADC-side impedance can be calculated by:

$$((200\Omega/2) + (2 \cdot 4.99) || 300 \Omega) = 80\Omega.$$

Let's now take a look at the output CM voltage that pertains to the schematic of Figure 11, simplified in Figure 12:

Figure 11. Increasing Diff Load Resistance and Matching to  $75\Omega$

Rev. 0

Figure 12. TIA 75 $\Omega$  Matched Load Equivalent Circuit

As in the previous cases, for analysis purposes, it is useful to break the output load circuit into its equivalent half-circuit to compute how the CM voltage is affected, as shown in Figure 13.

Figure 13. CM Half-Circuit Equivalent Circuit for  $75\Omega$  Load

As before, the CM circuit is not affected by the R1, R2 or the ADC differential input impedance of  $200\Omega$ . The output CM will be given by:

$$V_{CMO} = I_0 \cdot (24.9\Omega + 50\Omega + 2R_{CM})$$

(5)

So, in addition to raising the TIA output impedance,  $R_{S1}$  and  $R_{S2}$  also contribute to an increase in the minimum output CM voltage.

Table 6 shows the computed minimum CM voltage, TIA gain (RT), and ADC FS diff voltage swing for various ADJ settings applied to the Figure 11 configuration.

Here is a sample calculation of the values in Table 6, related to the Figure 11 schematic, for ADJ 00 as an illustration:

- a. Output current values (ADJ 00) with max input current of 90µA (from Table 2): 12mA, 2mA

- b. Net diff output load:  $75\Omega$  (37.5 $\Omega$  on each output) RT Calculation: RT(k $\Omega$ ) =

$$\frac{\text{c. }}{90\mu\text{A}}\frac{37.5\Omega[(12\text{mA}-2\text{mA})-(2\text{mA}-12\text{mA})]}{90\mu\text{A}}=8.3\text{k}\Omega$$

- d. ADC FS diff voltage calculation =  $90\mu$ A  $8.3k\Omega$  = 750mV<sub>P-P</sub>

- e. IO CM / Average Output Current (from Table 1): 7mA

- f.  $V_{CMO}$  (minimum) =  $I_0 \cdot (24.9\Omega + 50\Omega + 2 \cdot 2\Omega) = 553$ mV, where  $I_0 = 7$ mA,  $24.9\Omega$  is the resistors in series with the TERM pin,  $50\Omega$  is the TERM internal resistance, and the  $2\Omega$  is the internal  $R_{CM}$  minimum value

In the Figure 11 schematic and tabulated results in Table 6, the ADJ 11 setting's Min CM voltage is too high to be usable. Thus, the technique of lowering CM voltage (Detailed Example 2) discussed earlier can be employed

Table 6. CM Minimum Voltage and Other Operating Performance Values for Various ADJ Settings of Figure 11

| ADJ1 | ADJ0 | CM/AVERAGE OUTPUT<br>CURRENT I <sub>O</sub> (ma) | RT (kΩ) | ADC FS DIFF VOLTAGE<br>SWING WITH FULL<br>TILT (mV <sub>P-P</sub> ) | MIN CM VOLTAGE (mV) |

|------|------|--------------------------------------------------|---------|---------------------------------------------------------------------|---------------------|

| 0    | 0    | 7                                                | 8.3     | 750                                                                 | 553                 |

| 0    | 1    | 14                                               | 16.7    | 1500                                                                | 1106                |

| 1    | 0    | 21                                               | 25.0    | 2250*                                                               | 1659                |