|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                              |                                           |                 |          |      | ICL VI    | SION     | REC       | ORD                |                              |                             |                                              |                                                   |                                         |                                |                       |               |      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------|-------------------------------------------|-----------------|----------|------|-----------|----------|-----------|--------------------|------------------------------|-----------------------------|----------------------------------------------|---------------------------------------------------|-----------------------------------------|--------------------------------|-----------------------|---------------|------|

| REV           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                              |                                           |                 |          |      | DESC      | RIPT     | TION      |                    |                              |                             |                                              |                                                   |                                         |                                |                       | DAT           | Έ    |

| 0             | INIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TIAL RI    | ELEASE                                                       |                                           |                 |          |      |           |          |           |                    |                              |                             |                                              |                                                   |                                         |                                | Ар                    | or. 27,       | 2009 |

| А             | Pages 1 through 12, changed title from RH1185MK to RH1185AMK.<br>Page 3, Re-formatted the Absolute Maximum Rating for the Thermal Resistance Junction to Case,<br>TO-3 Control Area from 1DEGC/W to 1°C/W and the Power Transistor from 3 DEGC/W to 3°C/W.<br>Page 10, removed REF Pin Shutdown Current from Tables I and Table II Electrical Characteristics.<br>PARAGRAPH 3.1. STATES "Positive Adjustable Regulator".<br>Corrected Typo To State "Negative Adjustable Regulator". |            |                                                              |                                           |                 |          |      |           |          | М         | ay 6, 2            | 2011                         |                             |                                              |                                                   |                                         |                                |                       |               |      |

| B             | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | nd 11, rer                                                   |                                           |                 |          |      |           |          |           | Table              | I and                        | Table                       | e II Eld                                     | ectrica                                           | al                                      |                                |                       | June 2<br>201 |      |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                              |                                           |                 |          |      |           |          |           |                    |                              |                             |                                              |                                                   |                                         |                                |                       |               |      |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | C                                                            | A1171                                     | <u>ON·</u>      | ELF      | CTR  | OST 4     | TIC      | DISC      | HAR                | GFS                          | ENSI                        | TIVE                                         | 2 PA F                                            | 21                                      |                                |                       |               |      |

| REVIS         | SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PAG        | CA<br>E NO.                                                  | AUTI                                      | <u>ON:</u><br>2 | ELE<br>3 | CTR( | OSTA<br>5 | TIC<br>6 | DISC<br>7 | HAR<br>8           | GE S<br>9                    | <b>ENSI</b><br>10           | TIVE                                         | <b>PAF</b>                                        | T                                       |                                |                       |               |      |

| INDE          | EX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REV        | E NO.<br>ISION                                               | AUTI<br>1<br>B                            |                 |          |      |           |          |           |                    |                              |                             | 1                                            | -                                                 | RT                                      |                                |                       |               |      |

| INDE<br>REVIS | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION<br>E NO.                                      | 1                                         | 2               | 3        | 4    | 5         | 6        | 7         | 8                  | 9                            | 10                          | 11                                           | 12                                                | RT                                      |                                |                       |               |      |

| INDE          | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION                                               | 1                                         | 2               | 3        | 4    | 5         | 6        | 7         | 8                  | 9<br>B                       | 10<br>B                     | 11<br>B                                      | 12<br>B                                           |                                         |                                |                       |               |      |

| INDE<br>REVIS | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION<br>E NO.<br>ISION                             | 1<br>B                                    | 2               | 3        | 4    | 5         | 6        | 7         | 8                  | 9<br>B                       | 10<br>B<br>EAR              | 11<br>B<br>TECH                              | 12<br>B<br>NOL                                    | OGY                                     |                                | PORAT                 | ΓΙΟΝ          |      |

| INDE<br>REVIS | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION<br>E NO.<br>ISION<br>O                        | 1<br>B<br>RIG                             | 2               | 3        | 4    | 5         | 6        | 7         | 8<br>B             | 9<br>B<br>LIN                | 10<br>B<br>EAR              | 11<br>B                                      | 12<br>B<br>NOL                                    | OGY                                     |                                |                       | ΓION          |      |

| INDE<br>REVIS | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION<br>E NO.<br>ISION<br>O<br>D                   | 1<br>B                                    | 2               | 3        | 4    | 5         | 6        | 7         | 8<br>B             | 9<br>B                       | 10<br>B<br>EAR              | 11<br>B<br>TECH                              | 12<br>B<br>NOL<br>TAS,                            | OGY                                     | FORN                           | JIA                   | ΓION          |      |

| INDE<br>REVIS | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION<br>E NO.<br>ISION<br>O<br>Di<br>El<br>M       | 1<br>B<br>PRIG<br>SGN<br>NGR<br>MFG       | 2               | 3        | 4    | 5         | 6        | 7         | 8<br>B<br>TIT      | 9<br>B<br>LIN                | 10<br>B<br>EAR<br>M         | 11<br>B<br>TECH<br>AILPI'<br>IICRO<br>K, Neg | 12<br>Β<br>NOL<br>ΓAS,<br>CIRC                    | OGY<br>CALI<br>CUIT,                    | FORN<br>LINE<br>lator v        | JIA                   |               |      |

| REVIS         | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION<br>E NO.<br>ISION<br>O<br>Di<br>EI<br>M       | I<br>B<br>PRIG<br>SGN<br>NGR<br>AFG<br>CM | 2               | 3        | 4    | 5         | 6        | 7         | 8<br>B<br>TIT<br>R | 9<br>B<br>LIN<br>LE:<br>H118 | 10<br>B<br>EAR<br>M<br>5AMK | 11<br>B<br>TECH<br>AILPI<br>UCRO<br>K, Neg   | 12<br>B<br>NOL<br>TAS,<br>CIRC<br>gative<br>Curre | OGY<br>CALI<br>CUIT,<br>Regul<br>nt Lin | FORN<br>LINE<br>lator v<br>nit | VIA<br>AR,<br>vith Ac | ljusta        | ble  |

| INDE<br>REVIS | EX<br>SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV<br>PAG | E NO.<br>ISION<br>E NO.<br>ISION<br>O<br>Do<br>Do<br>El<br>M | 1<br>B<br>PRIG<br>SGN<br>NGR<br>MFG       | 2               | 3        | 4    | 5         | 6        | 7         | 8<br>B<br>TIT      | 9<br>B<br>LIN<br>LE:<br>H118 | 10<br>B<br>EAR<br>M<br>5AMK | 11<br>B<br>TECH<br>AILPI'<br>IICRO<br>K, Neg | 12<br>B<br>NOL<br>TAS,<br>CIRC<br>gative<br>Curre | OGY<br>CALI<br>CUIT,<br>Regul<br>nt Lin | FORN<br>LINE<br>lator v<br>nit | MA<br>AR,<br>vith Ac  | ljusta        |      |

# FOR OFFICIAL USE ONLY

## 1.0 SCOPE:

1.1 This specification defines the performance and test requirements for a microcircuit processed to a space level manufacturing flow.

### 2.0 APPLICABLE DOCUMENTS:

2.1 Government Specifications and Standards: the following documents listed in the Department of Defense Index of Specifications and Standards, of the issue in effect on the date of solicitation, form a part of this specification to the extent specified herein.

**SPECIFICATIONS:**

| MIL-PRF-38535 | Integrated Circuits (Microcircuits) Manufacturing, General Specification for |

|---------------|------------------------------------------------------------------------------|

| MIL-STD-883   | Test Method and Procedures for Microcircuits                                 |

| MIL-STD-1835  | Microcircuits Case Outlines                                                  |

2.2 Order of Precedence: In the event of a conflict between the documents referenced herein and the contents of this specification, the order of precedence shall be this specification, MIL-PRF-38535 and other referenced specifications.

### 3.0 **REQUIREMENTS**:

- 3.1 General Description: This specification details the requirements for the RH1185AMK, 3A LOW DROPOUT NEGATIVE ADJUSTABLE REGULATOR, processed to space level manufacturing flow.

- 3.2 Part Number:

- 3.2.1 RH1185AMK (TO3 METAL CAN, 4 LEADS)

- 3.3 Part Marking Includes:

- a. LTC Logo

- b. LTC Part Number (See Paragraph 3.2)

- c. Date Code

- d. Serial Number

- e. ESD Identifier per MIL-PRF-38535, Appendix A

| 3.4 | The Absolute Maximum Ratings (Note 1)                                                                                                        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

|     | Input Voltage                                                                                                                                |

|     | Input - Output Differential                                                                                                                  |

|     | FB Voltage                                                                                                                                   |

|     | REF Voltage                                                                                                                                  |

|     | Output Voltage                                                                                                                               |

|     | Output Reverse Voltage                                                                                                                       |

|     | Operating Ambient Temperature Range                                                                                                          |

|     | Operating Junction Temperature Range                                                                                                         |

|     | Control Section $\cdot \cdot \cdot$          |

|     | Power Transistor Section $\cdot \cdot \cdot$ |

|     | Storage Temperature Range $$                                                                                                                 |

|     | Lead Temperature (Soldering, 10 sec)                                                                                                         |

|     | Thermal Resistance Junction to Case                                                                                                          |

|     | TO-3 Control Area                                                                                                                            |

|     | Power Transistor                                                                                                                             |

|     |                                                                                                                                              |

- 3.5 Electrostatic discharge sensitivity, ESDS, shall be Class 2.

- 3.6 Electrical Performance Characteristics: The electrical performance characteristics shall be as specified in Table I and **Table II.**

- 3.7 Electrical Test Requirements: Screening requirements shall be in accordance with 4.1 herein, MIL-STD-883, Method 5004, and as specified in **Table IV** herein.

- 3.8 Burn-In Requirement:

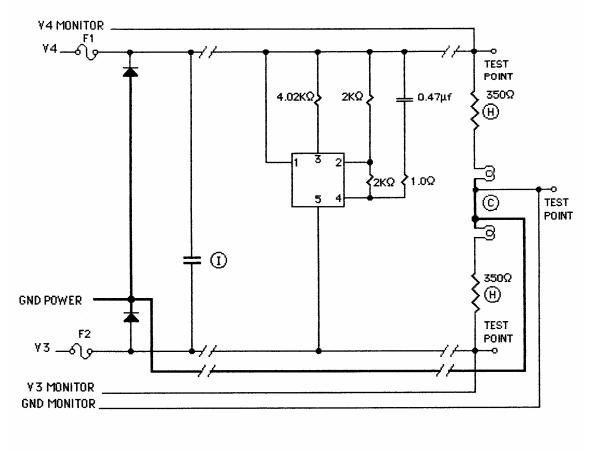

3.8.1 (TO3, 4 Leads): Static Burn-in, Figure 3.

- 3.9 Delta Limit Requirement: Delta limit parameters are specified in **Table III** herein, are calculated after each burn-in, and the delta rejects are included in the PDA calculation.

- 3.10 Design, Construction, and Physical Dimensions: Detail design, construction, physical dimensions, and electrical requirements shall be specified herein.

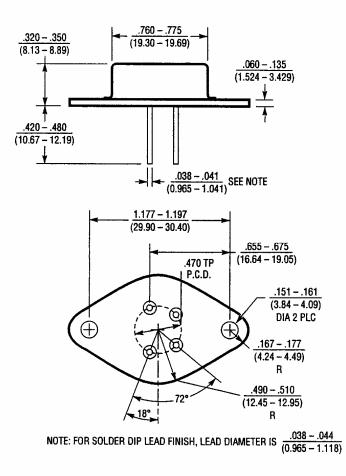

- 3.10.1 Mechanical / Packaging Requirements: Case outlines and dimensions are in accordance with Figure 1.

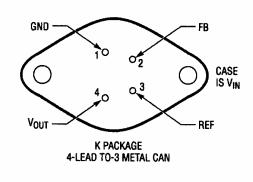

- 3.10.2 Terminal Connections: The terminal connections shall be as specified in Figure 2.

- 3.10.3 Lead Material and Finish: The lead material and finish shall be Alloy 52 for device option 1 with hot solder dip (Finish letter A) in accordance with MIL-PRF-38535.

- 3.11 Radiation Hardness Assurance (RHA):

- 3.11.1 The manufacturer shall perform a lot sample test as an internal process monitor for total dose radiation tolerance. The sample test is performed with MIL-STD-883 TM1019 Condition A as a guideline.

- 3.11.2 For guaranteed radiation performance to MIL-STD-883, Method 1019, total dose irradiation, the manufacturer will provide certified RAD testing and report through an independent test laboratory when required as a customer purchase order line item.

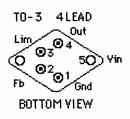

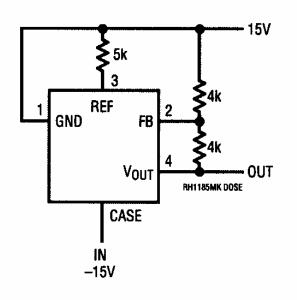

- 3.11.3 Total dose bias circuit is specified in Figure 4.

- 3.12 Wafer Lot Acceptance: Wafer lot acceptance shall be in accordance with MIL-PRF-38535, Appendix A, except for the following: Topside glassivation thickness shall be a minimum of 4KÅ.

- 3.13 Wafer Lot Acceptance Report: SEM is performed per MIL-STD-883, Method 2018 and copies of SEM photographs shall be supplied with the Wafer Lot Acceptance Report as part of a Space Data Pack when specified as a customer purchase order line item.

#### 4.0 VERIFICATION (QUALITY ASSURANCE PROVISIONS)

- 4.1 <u>Quality Assurance Provisions</u>: Quality Assurance provisions shall be in accordance with MIL-PRF-38535. Linear Technology is a QML certified company and all Rad Hard candidates are assembled on qualified Class S manufacturing lines.

- 4.2 <u>Sampling and Inspection</u>: Sampling and Inspection shall be in accordance with MIL-STD-883, Method 5005 with QML allowed and TRB approved deviations in conjunction with paragraphs 3.1.1, 3.2.1, and 3.4 of the test method.

- 4.3 <u>Screening</u>: Screening requirements shall be in accordance with MIL-STD-883, Method 5004 with QML allowed and TRB approved deviations in conjunction with paragraphs 3.1, 3.1.1, and 3.4 of the test method. Electrical testing shall be as specified in Table IV herein.

- 4.3.1 Analysis of catastrophic (open/short) failures from burn-in will be conducted only when a lot fails the burn-in or re-burn-in PDA requirements.

- 4.4 <u>Quality Conformance Inspection</u>: Quality conformance inspection shall be in accordance with 4.2 and 4.3 herein and as follows:

- 4.4.1 Group A Inspection: Group A inspection shall be performed in accordance with 4.1 herein, per MIL-STD-883, Method 5005, and specified in Table IV herein.

- 4.4.2 Group B Inspection: When purchased, a full Group B is performed on an inspection lot. As a minimum, Subgroups 1-4 plus 6 are performed on every assembly lot, and Subgroup B2 (Resistance to Solvents / Mark Permanency) and Subgroup B3 (Solderability) are performed prior to the first shipment from any inspection lot and Attributes provided when a Full Space Data Pack is ordered. Subgroup B5 (Operating Life) is performed on each wafer lot. This subgroup may or may not be from devices built in the same package style as the current inspection lot. Attributes and variables data for this subgroup will be provided upon request at no charge.

| 4.4.2.1 | Group B, Subgroup $2c = 10\%$ | Group B, Subgroup 5 = *5%<br>(*per wafer or inspection lot |  |  |  |

|---------|-------------------------------|------------------------------------------------------------|--|--|--|

|         | Group B, Subgroup 3 = 10%     | whichever is the larger quantity)                          |  |  |  |

|         | Group B, Subgroup $4 = 5\%$   | Group B, subgroup 6 = 15%                                  |  |  |  |

4.4.2.2 All footnotes pertaining to Table IIa in MIL-STD-883, Method 5005 apply. The quantity (accept number) of all other subgroups are per MIL-STD-883, Method 5005, Table IIa.

4.4.3 Group D Inspection: When purchased, a full Group D is performed on an inspection lot. As a minimum, periodic full Group D sampling is performed on each package family for each assembly location every 26 weeks. A generic Group D Summary is provided when a full Space Data Pack is ordered.

- 4.4.3.1 Group D, Subgroups 3, 4 and 5 = 15% each (Sample Size Series).

- 4.4.3.2 All footnotes pertaining to Table IV in MIL-STD-883, Method 5005 apply. The quantity (accept number) or sample number and accept number of all other subgroups are per MIL-STD-883, Method 5005, Table IV.

- 4.5 Source Inspection:

- 4.5.1 The manufacturer will coordinate Source Inspection at wafer lot acceptance and pre-seal internal visual.

- 4.5.2 The procuring activity has the right to perform source inspection at the supplier's facility prior to shipment for each lot of deliverables when specified as a customer purchase order line item. This may include wafer lot acceptance and final data review.

- 4.6 Deliverable Data: Deliverable data that will ship with devices when a Space Data Pack is ordered:

- 4.6.1 Lot Serial Number Sheets identifying all devices accepted through final inspection by serial number.

- 4.6.2 100% attributes (completed lot specific traveler; includes Group A Summary)

- 4.6.3 Burn-In Variables Data and Deltas (if applicable)

- 4.6.4 Group B2, B3, and B5 Attributes (Variables data, if performed on lot shipping)

- 4.6.5 Generic Group D data (4.4.3 herein)

- 4.6.6 SEM photographs (3.13 herein)

- 4.6.7 Wafer Lot Acceptance Report (3.13 herein)

- 4.6.8 X-Ray Negatives and Radiographic Report

- 4.6.9 A copy of outside test laboratory radiation report if ordered

- 4.6.10 Certificate of Conformance certifying that the devices meet all the requirements of this specification and have successfully completed the mandatory tests and inspections herein.

Note: Items 4.6.1 and 4.6.10 will be delivered as a minimum, with each shipment. This is noted on the Purchase Order Review Form as "No Charge Data".

5.0 Packaging Requirements: Packaging shall be in accordance with Appendix A of MIL-PRF-38535. All devices shall be packaged in conductive material or packaged in anti-static material with an external conductive field shielding barrier.

#### (K) TO3 / 4 LEADS CASE OUTLINE

# TERMINAL CONNECTIONS <u>TO3 / 4 LEAD METAL CAN</u>

#### STATIC BURN-IN CIRCUIT TO3 METAL CAN / 4 LEADS

NOTES:

- Unless otherwise specified, component tolerances shall be per military specification.

- 2. Tj = 163°C maximum.

- 3. Ta = 150 ℃.

- 4. Burn-in voltages: ¥4 = +15¥ to +16.5¥ ¥3 = -15¥ to -16.5¥

## TOTAL DOSE BIAS CIRCUIT

0.01

| PARAMETER AND CONDITIONS                                                                                                                                                                                                      | MIN                  | T <sub>A</sub> = 25°C<br>TYP | MAX                    | SUB-<br>GROUP |                      | T <sub>a</sub> ≤ 125°C<br>Typ Max | SUB-<br>GROUP                        | UNITS       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------|------------------------|---------------|----------------------|-----------------------------------|--------------------------------------|-------------|

| Reference Voltage (At FB Pin)                                                                                                                                                                                                 |                      | 2.37                         |                        |               |                      | 2.37                              |                                      | v           |

| Reference Voltage Tolerence (At FB Pin) (Note 2) $V_{IN} - V_{OUT} = 5V$ , $V_{OUT} = V_{REF}$                                                                                                                                | -1.0                 | 0.3                          | 1.0                    | 1             |                      |                                   |                                      | %           |

| $\begin{array}{l} \mbox{Reference Voltage Tolerance} \\ V_{IN}-V_{OUT}=1.2V \ to \ V_{IN}=30V, \\ 1mA\leq I_{OUT}\leq 3A, \\ P_D\leq 25W \ (Note \ 6), \ V_{OUT}=5V, \\ T_{MIN}\leq T_J\leq T_{MAX} \ (Note \ 9) \end{array}$ |                      |                              |                        |               | -2.5                 | 2.5                               | 2, 3                                 | %           |

| Feedback Pin Bias Current, V <sub>OUT</sub> = V <sub>REF</sub>                                                                                                                                                                |                      | 0.7                          | 2                      | 1             |                      | 2                                 | 2, 3                                 | μA          |

| Dropout Voltage (Note 3)<br>I <sub>OUT</sub> = 0.5A, V <sub>OUT</sub> = 5V<br>I <sub>OUT</sub> = 3A, V <sub>OUT</sub> = 5V                                                                                                    |                      | 0.2<br>0.67                  | 0.37<br>1              | 1             |                      | 0.55<br>1.4                       | 2, 3<br>2, 3                         | v<br>v      |

| Load Regulation (Note 7) $I_{OUT} = 5mA$ to 3A,<br>V <sub>IN</sub> – V <sub>OUT</sub> = 1.5V to 10V, V <sub>OUT</sub> = 5V                                                                                                    |                      | 0.05                         | 0.3                    | 1             |                      | 0.8                               | 2, 3                                 | %           |

| Line Regulation (Note 7)<br>$V_{IN} - V_{OUT} = 1V$ to 20V, $V_{OUT} = 5V$                                                                                                                                                    |                      | 0.002                        | 0.01                   | 1             |                      | 0.03                              | 2, 3                                 | %/V         |

| Minimum Input Votlage (Note 4)<br>I <sub>OUT</sub> = 1A, V <sub>OUT</sub> = V <sub>REF</sub><br>I <sub>OUT</sub> = 3A, V <sub>OUT</sub> = V <sub>REF</sub>                                                                    |                      | ·                            | 3 <i>.</i> 9<br>4.4    | 1             |                      |                                   |                                      | V<br>V      |

| $\begin{array}{l} \mbox{Internal Current Limit (See Graph for Guaranteed Curve) (Note 12) \\ 1.5V \leq V_{IN} - V_{OUT} \leq 10V \\ V_{IN} - V_{OUT} = 15V \\ V_{IN} - V_{OUT} = 20V \\ V_{IN} - V_{OUT} = 30V \end{array}$   | 3.3<br>2<br>1<br>0.2 | 3.6<br>3<br>1.7<br>0.4       | 4.2<br>4.2<br>2.6<br>1 | 1<br>1<br>1   | 3.1<br>2<br>1<br>0.2 | 4.4<br>4.3<br>3<br>1.1            | 2, 3<br>2, 3<br>2, 3<br>2, 3<br>2, 3 | A<br>A<br>A |

| External Current Limit (Note 11)<br>R <sub>LIM</sub> = 5k, V <sub>OUT</sub> = 1V<br>R <sub>LIM</sub> = 15k, V <sub>OUT</sub> = 1V                                                                                             | 2.7<br>0.9           | 3<br>1                       | 3.3<br>1.1             | 1             | 2.5<br>0.8           | 3.5<br>1.2                        | 2, 3<br>2, 3                         | A           |

|                                                                                                                                                                                                                               |                      | 2.5                          | 3.5                    | 1             |                      | 3.5                               | 2, 3                                 | mA          |

| Supply Current Change With Load $V_{IN} - V_{OUT} = V_{SAT}$ (Note 10) $V_{IN} - V_{OUT} \ge 2V$                                                                                                                              |                      | 1 1111 1 1011                | 25<br>15               | 1             |                      | 40<br>25                          | 2, 3<br>2, 3                         | mA<br>mA    |

| Thermal Regulation<br>V <sub>IN</sub> – V <sub>OUT</sub> = 10V, I <sub>OUT</sub> = 5mA to 2A                                                                                                                                  |                      |                              |                        |               |                      | 0.014                             |                                      | %/W         |

|                                                                                                                                                                                                                               | 1                    |                              |                        | 1             |                      |                                   |                                      |             |

## TABLE I: ELECTRICAL CHARACTERISTICS (PRE-IRRADIATION)

## ALL NOTES ON NEXT PAGE.

Reference Voltage Temperature Coefficient (Note 8)

%/°C

## TABLE II: ELECTRICAL CHARACTERISTICS (POST-IRRADIATION)

| PARAMETER AND CONDITONS                                                          | 10KRAD(Si)<br>Min Max |            | 20KRAD(Si) |              | 50KRAD(Si) |             | 100KRAD(Si) |            | 200KRAD(Si) |            | [            |

|----------------------------------------------------------------------------------|-----------------------|------------|------------|--------------|------------|-------------|-------------|------------|-------------|------------|--------------|

|                                                                                  | MIN                   | MAA        | MIN        | MAX          | MIN        | MAX         | MIN         | MAX        | MIN         | MAX        | UNITS        |

| Reference Voltage Tolerance                                                      |                       | 10         | 1.0        |              | 4.5        |             |             |            |             | _          |              |

| $V_{IN} - V_{OUT} = 5V, V_{OUT} = V_{REF}$                                       | -1.2                  | 1.2        | -1.2       | 1.2          | -1.5       | 1.5         | -1.5        | 1.5        | 2           | 2          | %            |

| Reference Voltage Tolerance                                                      |                       | •          |            | -            |            |             |             |            |             |            |              |

| $V_{IN} - V_{OUT} = 1.2V$ to $V_{IN} = 30V$ ,                                    | 3                     | 3          | 3          | 3            | -3.2       | 3.2         | -3.5        | 3.5        | -4          | 4          | %            |

| $1mA \le I_{OUT} \le 3A$ ,<br>$P_D \le 25W$ (Note 6), $V_{OUT} = 5V$ ,           |                       |            |            |              |            |             | ·           |            |             |            |              |

| $T_{MIN} \le T_J \le T_{MAX}$ (Note 9)                                           |                       |            |            |              |            |             |             |            |             |            |              |

| Feedback PIn Bias Current, V <sub>OUT</sub> = V <sub>REF</sub>                   |                       | 2          |            | 2            |            | 2.5         |             | 3          |             | 3          | μA           |

| Dropout Voltage (Note 3)                                                         |                       |            |            |              |            |             |             |            |             |            |              |

| $I_{0UT} = 0.5A, V_{0UT} = 5V$                                                   |                       | 0.4        |            | 0.4          |            | 0.4         |             | 0.425      |             | 0.45       | l v          |

| $I_{OUT} = 3A, V_{OUT} = 5V$                                                     |                       | 1          |            | 1            |            | 1           |             | 1.05       |             | 1.1        | İ V          |

| Load Regulation (Note 7) IOUT = 5mA to 3A                                        |                       |            |            |              |            |             |             |            |             |            |              |

| $V_{IN} - V_{OUT} = 1.5V$ to 10V, $V_{OUT} = 5V$                                 |                       | 0.3        |            | 0.4          |            | 0.5         |             | 0.8        |             | 1          | %            |

| Line Regulation, Absolute Value (Note 7)                                         |                       |            |            |              | 1          |             |             |            |             |            |              |

| V <sub>IN</sub> – V <sub>OUT</sub> = 1V to 20V, V <sub>OUT</sub> = 5V            |                       | 0.01       |            | 0.01         |            | 0.01        |             | 0.02       |             | 0.05       | %/V          |

| Minimum Input Voltage (Note 4)                                                   |                       |            |            |              |            |             |             |            |             |            |              |

| $I_{OUT} = 1A$ , $V_{OUT} = V_{REF}$                                             |                       | 3.9        |            | 3.9          |            | 3.9         |             | 4          |             | 4          | v            |

| $I_{OUT} = 3A, V_{OUT} = V_{REF}$                                                |                       | 4.4        |            | 4.4          |            | 4.4         |             | 4.5        |             | 4.5        | V            |

| Internal Current Limit (Note 12)                                                 |                       |            |            |              |            |             |             |            |             |            |              |

| $1.5V \le V_{IN} - V_{OUT} \le 10V$                                              | 3.3                   | 4.3        | 3.3        | 4.3          | 3.3        | 4.4         | 3.3         | 4.55       | 3.3         | 4.75       | A            |

| $V_{IN} - V_{OUT} = 15V$                                                         | 2                     | 4.3        | 2          | 4.3          | 2          | 4.35        | 2           | 4.5        | 2           | 4.7        | A            |

| V <sub>IN</sub> V <sub>OUT</sub> = 20V<br>V <sub>IN</sub> V <sub>OUT</sub> = 30V | 1 0.2                 | 2.7<br>1   | 1 0.2      | 2.75<br>1.15 | 0.2        | 2.85<br>1.3 | 0.2         | 3.1        | 1           | 3.3<br>2   | A            |

|                                                                                  | 0.2                   |            | 0.2        | 1.15         | 0.2        | 1.3         | 0.2         | 1.6        | 0.2         | 2          | <u>A</u>     |

| External Current Limit (Note 11)                                                 | 2.7                   | 3.3        | 2.7        | 3.4          | 0.7        | 95          | .07         | 07         | 07          |            |              |

| R <sub>LIM</sub> = 5k<br>R <sub>LIM</sub> = 15k                                  | 0.9                   | 3.3<br>1.1 | 0.9        | 3.4<br>1.25  | 2.7<br>0.9 | 3.5<br>1.4  | 2.7         | 3.7<br>1.6 | 2.7<br>0.9  | 3.9<br>1.9 | A   A        |

| Quiescent Supply Current                                                         | 0.0                   | 1.1        | 0.5        | 1.20         | 0.5        | 1.7         | 0.5         | 1.0        | 0.9         | 1.3        |              |

| $I_{OUT} = 5$ mA, $V_{OUT} = V_{REF}$ , $4V \le V_{IN} \le 25V$                  |                       | 3.5        |            | 3.5          |            | 3.5         |             | 3.5        |             | 3.5        | mA           |

| Supply Current Change With Load                                                  |                       | 0.0        |            | 0.0          |            | 0.0         |             | 0.0        |             | 0.0        |              |

| VIN - VOUT = VSAT                                                                |                       | -25        |            | 27           |            | 30          |             | 35         |             | 45         | mA/A         |

| $V_{IN} - V_{OUT} \ge 2V$                                                        |                       | 15         |            | 16           |            | 18          |             | 35<br>21   |             | 40<br>27   | mava<br>ma/a |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Reference voltage is guaranteed both at nominal conditions (no load, 25°C) and at worst-case conditions of load, line, power and temperature.

**Note 3:** Dropout voltage is tested by reducing input voltage until the output drops 1% below its nominal value. Tests are done at 0.5A and 3A. The power transistor looks basically like a pure resistance in this range so that minimum differential at any intermediate current can be calculated by interpolation;  $V_{DROPOUT} = 0.25V + 0.25\Omega \cdot I_{OUT}$ . For load current other than 0.5A and 3.0A, see graph in LT1185 data sheet.

**Note 4:** "Minimum input voltage" is limited by base emitter voltage drive of the power transistor section, not saturation as measured in Note 3. For output voltages below 4V, "minimum input voltage" specification may limit dropout voltage before transistor saturation limitation.

**Note 5:** Supply current is measured on the ground pin, and does not include load current, R<sub>LIM</sub>, or output divider current.

**Note 6:** The 25W power level is guaranteed for an input-output voltage of 8.3V to 17V. At lower voltages the 3A limit applies, and at higher voltages the internal power limiting may restrict regulator power below 25W. See graph of Internal Current Limit in LT1185 data sheet.

**Note 7:** Line and load regulation are measured on a pulse basis with a pulse width of  $\approx$ 2ms, to minimize heating. DC regulation will be affected by thermal regulation and temperature coefficient of the reference. See the Applications Information section of LT1185 data sheet for details.

Note 8: Guaranteed by design and correlation to other tests, but not tested.

**Note 9:**  $T_{JMIN} = -55^{\circ}$ C for the RH1185AMK. Power transistor area and control circuit area have different maximum junction temperatures. Control area limit is  $T_{JMAX} = 150^{\circ}$ C for the RH1185AMK. Power area limit is 175°C for RH1185AMK.

Note 10:  $V_{SAT}$  is the maximum specified dropout voltage; 0.25V + 0.25 $\Omega$  • 1<sub>OUT</sub>.

Note 11: Current limit is programmed with a resistor from REF pin to GND pin. The value is  $15k \cdot A/I$ -limit.

Note 12: For  $V_{IN}-V_{OUT}$  = 1.5V,  $V_{IN}$  = 5V and  $V_{OUT}$  = 3.5V. For all other current limit tests,  $V_{OUT}$  = 1.0V

# TABLE III: POST BURN-IN ENDPOINTS AND DELTA LIMIT REQUIREMENTS $T_A = 25^{\circ}C$

| PARAMETER and CONDITIONS            | ENDPOIN | T LIMIT | DELTA I |        |       |

|-------------------------------------|---------|---------|---------|--------|-------|

|                                     | MIN     | MAX     | MIN     | MAX    | UNITS |

| Reference Voltage, V <sub>REF</sub> |         |         |         |        |       |

| $Vin = 7.4V$ , $Vout = V_{REF}$     | 2.346   | 2.394   | -0.040  | +0.040 | V     |

## TABLE IV: ELECTRICAL TEST REQUIREMENTS

| MIL-STD-883 TEST REQUIREMENTS                                          | SUBGROUP |

|------------------------------------------------------------------------|----------|

| FINAL ELECTRICAL TEST REQUIREMENTS (METHOD 5004)                       | 1*, 2, 3 |

| GROUP A TEST REQUIREMENTS (METHOD 5005)                                | 1, 2, 3  |

| GROUP B AND D FOR CLASS S ENDPOINT ELECTRICAL PARAMETERS (METHOD 5005) | 1, 2, 3  |

\*PDA APPLIES TO SUBGROUP 1; SEE PDA TEST NOTE.

PDA TEST NOTE: The PDA is specified as 5% based on failures from Group A, Subgroup 1, tests after cooldown as the final electrical test in accordance with method 5004 of MIL-STD-883. The verified failures of Group A, Subgroup 1 and delta rejects after burn-in divided by the total number of devices submitted for burn-in in that lot shall be used to determine the percent for the lot. Linear Technology Corporation reserves the right to test to tighter limits than those given.