# Mobile AMD Athlon<sup>™</sup> and Mobile AMD Duron<sup>™</sup>

# Processor System Requirements

Notice: This document has been released under a Non-Disclosure Agreement to:

| Name:    |  |

|----------|--|

| Company: |  |

| NDA #:   |  |

Сору #: \_\_\_\_\_

Publication Identification Number: 24106A August, 2000

Publication # 24106 Rev: A Issue Date: August 2000

#### © 2000 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo, AMD Athlon, AMD Duron, and combinations thereof, and AMD PowerNow! are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc.

Windows is a registered trademark, and Windows 95, Windows 98 and Windows 2000 are trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

24106A-August 2000

Contents

Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processor System Requirements

| Revision Historyix                                                                                             |

|----------------------------------------------------------------------------------------------------------------|

| Purpose                                                                                                        |

| References 2                                                                                                   |

| Critical Differences                                                                                           |

| Performance States and AMD PowerNow!™ Technology 4                                                             |

| Mobile AMD Athlon <sup>™</sup> and AMD Duron <sup>™</sup> Processor Notebook                                   |

| System Hardware Requirements                                                                                   |

| Voltage ID (VID) Mux7                                                                                          |

| Deterministic Power Up of K7VCC and Sleep<br>Voltages                                                          |

| Mobile AMD Athlon <sup>™</sup> Processor Model 5 (K7VCC)<br>DC to DC Control for Notebook PCs                  |

| VID[4:0] Control Requirements During C0, C1<br>and C2                                                          |

| Power-up and Sleep Voltages                                                                                    |

| Mobile AMD Duron <sup>™</sup> Processor Model 3 13                                                             |

| Mobile AMD Athlon <sup>™</sup> Processor Model 6 and<br>Mobile AMD Duron <sup>™</sup> Processor Model 7 13     |

| VID[4:0] Output Voltage Tolerance                                                                              |

| DC to DC Power Converters 14                                                                                   |

| VID[4:0] Codes Used 16                                                                                         |

| Processor Temperature Sensor                                                                                   |

| Mobile AMD Athlon <sup>™</sup> Processor Model 6 and the<br>Mobile AMD Duron <sup>™</sup> Processor Model 7 17 |

| Mobile AMD Duron <sup>™</sup> Processor Model 3 17                                                             |

| Performance States for Mobile AMD Duron <sup>™</sup> Processor<br>Model 3                                      |

| Power on Demand Enabled with THERM# 19                                                                         |

| FID[3:0] Output Pins                                                                                           |

| Thermal Requirements    21                                                                                     |

|                                                                                                                |

| BIOS Requirements                                                                                              |

| VID[4:0] codes 23                                                                                              |

Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements

| Chipset, Processor, and ACPI Table Entry Configuration 23                         |

|-----------------------------------------------------------------------------------|

| BIOS Requirements for Mobile AMD Duron <sup>TM</sup> Processor                    |

| Model 3                                                                           |

| BIOS Requirements for Mobile AMD Athlon <sup>™</sup> Processor                    |

| Model 6 and Mobile AMD Duron <sup>™</sup> Processor Model 7 32                    |

| ACPI Thermal Zone Implementation for Mobile                                       |

| AMD Athlon <sup>TM</sup> and AMD Duron <sup>TM</sup> Processor $\ldots \ldots 32$ |

| Appendix A: ACPI state transitions                                                |

| C1 Processor Halted: Caches Snoopable                                             |

| C2 Processor Power State: Stop Grant, Caches                                      |

| Snoopable                                                                         |

| C3 Processor Power State: Stop Grant Caches NOT                                   |

| Snoopable                                                                         |

| STP_AGP# and AGP_BUSY# and Stopping the                                           |

| AGP Clock During C3                                                               |

| S1 Sleep State (Power On Suspend / Stand by)                                      |

| S3 Sleep State Support (Suspend to RAM/Stand by) 41                               |

| ACPI S4 (Suspend to Disk, Hibernate) Support                                      |

| ACPI S5 (Soft Off, Shutdown) Support                                              |

| Appendix B: ACPI Required Registers 45                                            |

| ACPI Required Registers in Northbridges                                           |

| ACPI Required Registers in Southbridges                                           |

| System Reset Register                                                             |

|                                                                                   |

| Appendix C: Standard Power Sequencing Guidelines 47                               |

24106A-August 2000

Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processor System Requirements

# **List of Figures**

| Figure 1. | VID[4:0] Control of K7VCC Block Diagram                            | 8  |

|-----------|--------------------------------------------------------------------|----|

| Figure 2. | Deterministic Power-up Sequence for K7VCC<br>Timing Diagram        | 9  |

| Figure 3. | AMD PowerNow! <sup>TM</sup> Technology Conceptual Block<br>Diagram | 20 |

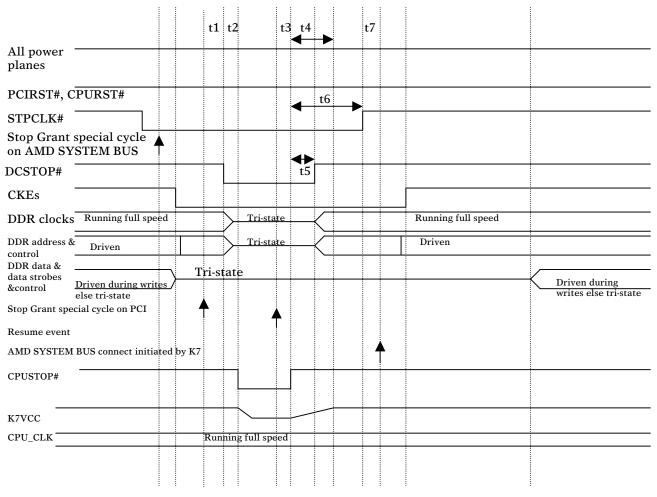

| Figure 4. | C3 State with Processor Voltage Reduction Timing<br>Diagram        | 7  |

# **List of Tables**

| Table 1. | Summary of Critical Features/Differences Between<br>Mobile AMD Processors                    |

|----------|----------------------------------------------------------------------------------------------|

| Table 2. | Power-up Timing Requirements 11                                                              |

| Table 3. | VID Codes used by Mobile AMD Athlon <sup>™</sup> and<br>AMD Duron <sup>™</sup> Processors 16 |

| Table 4. | Recommended Transistors for Accurate<br>Temperature Control 17                               |

| Table 5. | STPCLK# Processor Throttling Performance States 19                                           |

| Table 6. | Chipset, Processor, and ACPI Table Configuration<br>by the BIOS to Enable ACPI State Support |

| Table 7. | C3 Timing                                                                                    |

Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements

#

# **Revision History**

| Date        | Rev | Description     |

|-------------|-----|-----------------|

| August 2000 | Α   | Initial Release |

24106A-August 2000

# **Application** Note

# Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements

Unless otherwise noted, the information in this application note pertains to all processors in the Mobile AMD Athlon<sup>™</sup> and Mobile AMD Duron<sup>™</sup> families, which include the Mobile AMD Athlon processor (Model 6) and the Mobile AMD Duron processor (Models 3 and 7).

# Purpose

The purpose of this document is to specify system level power management requirements for Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processor-based notebooks. The scope includes motherboard implementation details and BIOS/Software usage of chipset features.

Because of the critical time to market pressure for Mobile AMD Athlon and Mobile AMD Duron processor-based systems, prototype systems have not been developed to test out the requirements in this document: these required features will be tested as part of the development cycle of the first Mobile AMD Athlon and Mobile AMD Duron processor-based notebooks. Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements

# References

This document specifies mobile system requirements which are in addition to the general requirements. For more details on the general requirements, see the *Motherboard PGA Design Guide*, order #90009

For more information about the Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processor families, refer to the following:

- Mobile AMD Duron<sup>™</sup> Processor Model 3 Data Sheet, order # 23979

- *Mobile AMD Duron™ Processor Model 7 Data Sheet*, order # 24068

- Socket A Mobile AMD Athlon<sup>™</sup> Processor Data Sheet, order # 90050

- Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processors Thermal Design Application Note, order # TBD

- The ACPI specification, *Advanced Configuration and Interface Specification* Revision 1.0b February 2, 1999

# **Critical Differences**

There are several key differences between Mobile AMD Athlon and Mobile AMD Duron processors and Mobile AMD-K6<sup>®</sup> processors that system designers must be aware of. A direct comparison between different Mobile AMD Athlon and Mobile AMD Duron processors can be found in Table 1, "Summary of Critical Features/Differences Between Mobile AMD Processors," on page 5.

- 1. Processor RESET# and RESET# (PCI RESET#) to the Northbridge are always asserted together. If a RESET# signal to Mobile AMD Athlon and Mobile AMD Duron processors is asserted without asserting RESET# to the Northbridge, the AMD system bus will not connect, and the system will hang. Port 92h and KBC initiated resets must be routed to INIT#.

- 2. Mobile AMD Athlon and Mobile AMD Duron processor's 100 MHz input clock and the Northbridge's input clock for the AMD system bus interface can NEVER be stopped while in the working state (S0/C [0-3]) or the S1 sleep state. This CPUCLK to Mobile AMD Athlon and Mobile AMD Duron processor and the Northbridge is stopped (powered off) during S3 and deeper sleep states.

- 3. Mobile AMD Athlon and Mobile AMD Duron processors do not achieve significant power savings when they execute a Halt instruction, or issue a stop grant special cycle in response to STPCLK# assertion.

- 4. Mobile AMD Athlon and Mobile AMD Duron processors do achieve significant power savings after the AMD system bus is disconnected in response to a Halt special cycle or Stop Grant special cycle. The BIOS must enable halt and stop grant disconnect features in the Northbridge.

- 5. When the AMD system bus is disconnected, Mobile AMD Athlon and Mobile AMD Duron processor's caches cannot be snooped. AMD system bus must be temporarily reconnected to allow bus master accesses to memory that require cache snoops during C1, C2, and throttling.

- 6. For the Mobile AMD Athlon and Mobile AMD Duron processors, it is required that all of the VID[4:0] outputs of the processor be used to select the processor's core voltage.

The VID[4:0] codes defined for the Mobile AMD Athlon and Mobile AMD Duron processors must be used. This is discussed later in this document.

- 7. The Mobile AMD Athlon and Mobile AMD Duron processors dictates its startup frequency. The Mobile AMD Duron processor Model 3's operational Frequency Identification (FID) code dictates the frequency of the Mobile AMD Duron processor core clock grid. The motherboard does not dictate the frequency at which the processor will startup or run (as was the case for the AMD-K6 processor).

- 8. The Mobile AMD Athlon and Mobile AMD Duron processor core voltage (K7VCC) also powers the AMD system bus and the I/O driver cells for the AMD system bus in the Northbridge. Therefore, the Northbridge current consumption must be taken into account when sizing the K7VCC DC to DC power converter.

# **Performance States and AMD PowerNow!™ Technology**

Processor performance states are combinations of processor core voltage and core frequency that allow the processor's power consumption to be dynamically reduced when its full computing power (performance) is not required by the applications being run. Performance states can be changed dynamically to allow processor performance to match the demand of the applications being run. Performance states can also be used as part of the thermal management strategy for the system, and to allow the user to specify a preference for silence, or runtime versus performance.

AMD PowerNow! technology is supported by the Mobile AMD Athlon processor Model 6 and the Mobile AMD Duron processor Model 7. AMD PowerNow! technology software enables the most optimal usage of processor performance states.

AMD PowerNow! technology can also be adapted to optimize battery life and performance of Mobile AMD Duron processors with a Model 3 core and/or chipsets that do not support dynamic processor performance state transitions. For these systems, clock throttling can be used to allow performance on demand for optimal user experience. For these systems, AMD PowerNow! technology may have a different name since voltage and frequency changes are not used.

#### Table 1. Summary of Critical Features/Differences Between Mobile AMD Processors

|                                                                                                                                                                                           | Mobile<br>AMD Duron™<br>Processor Model 3 | Mobile<br>AMD Duron™<br>Processor Model 7        | Mobile<br>AMD Athlon™<br>Processor Model 6       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Integrated L2                                                                                                                                                                             | 64 Kbytes                                 | 64 Kbytes                                        | 256 Kbytes                                       |

| On-die Thermal Diode                                                                                                                                                                      | No                                        | Yes                                              | Yes                                              |

| Supports AMD system bus FID Change protocol for dynamic voltage and frequency changes.                                                                                                    | No                                        | Yes                                              | Yes                                              |

| AMD System Bus Data Rate 200 MHz<br>(100 MHz reference clock)                                                                                                                             | Yes                                       | Yes                                              | Yes                                              |

| Power-up/C3/S1 sleep processor core and<br>AMD System Bus voltage when<br>disconnected <b>+/- 100 mV</b> . This is enforced<br>by the motherboard with a VID MUX. Refer<br>to section 2.1 | 1.4 V (investigating<br>lower voltages)   | 1.1 V (investigating<br>voltages down to<br>1.0) | 1.1 V (investigating<br>voltages down to<br>1.0) |

| Start-up Voltage (Dictated by the processor's VID[4:0] outputs.)                                                                                                                          | Operational voltage                       | 1.2 V +/- 100 mV                                 | 1.2 V +/- 100 mV                                 |

Notes:

1) For maximum processor current consumption, and thermal design power targets for Mobile AMD Duron processors refer to the appropriate Mobile AMD Duron processor data sheet.

2) The operational voltages listed for Mobile AMD Athlon processor Model 6 and Mobile AMD Duron processor Model 7 are nominal. With AMD PowerNow! technology, the actual voltage that these processors run at will be determined by software based on processor utilization and user preference.

*3)* For Mobile AMD Athlon processor Model 6and Mobile AMD Duron processor Model 7, the start-up voltage and frequency are changed to operational voltage and frequency under software control.

4) Below 1.300 V, the Mobile AMD Athlon and Mobile AMD Duron processor's DC to DC converter output can be incremented/decremented in 25 mV steps.

5) Power-up and Sleep voltages for Mobile AMD Athlon and Mobile AMD Duron processors are contingent on the chipset also supporting AMD system bus voltages at these levels when the AMD system bus interface is disconnected. Processor data sheets will specify exact operating and sleep voltages supported by the processor.

6) CPUID extended function 8000\_0007h - Advanced Power Management Feature Flags indicate the presence of mobile features: Thermal Diode, frequency, and voltage control mechanisms as indicated in the table above. These features are present in Mobile AMD Athlon processor Model 6 and Mobile AMD Duron processor Model 7.

7) The VID[4:0] codes for all versions of Mobile AMD processors (Mobile AMD Duron processor Model 3, Mobile AMD Duron processor Model 7 and Mobile AMD Athlon processor Model 6) are the same.

8) The FID codes for all versions of Mobile AMD Athlon and Mobile AMD Duron processors are the same.

#### Table 1. Summary of Critical Features/Differences Between Mobile AMD Processors (continued)

|                                                                                                                                                                 | Mobile<br>AMD Duron™<br>Processor Model 3 | Mobile<br>AMD Duron™<br>Processor Model 7                                                                            | Mobile<br>AMD Athlon™<br>Processor Model 6                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Operational processor core and<br>AMD system bus voltage <b>+/- 100 mV.</b><br><i>Refer to the processor data sheet for exact</i><br><i>operating voltages.</i> | 1.5 V to 1.3 V (under investigation)      | 1.2 V (committed)<br>(investigating<br>voltages down to<br>1.0) Note voltages<br>above 1.2 volts are<br>also likely. | 1.2 V (committed)<br>(investigating<br>voltages down to<br>1.0) Note voltages<br>above 1.2 volts are<br>also likely. |

| Start-up Frequency (Dictated by the processor.)                                                                                                                 | Maximum<br>frequency                      | 500 MHz                                                                                                              | 500 MHz                                                                                                              |

| CPUID                                                                                                                                                           | 630                                       | 670 (tentative)                                                                                                      | 660                                                                                                                  |

| Stop Grant Divisor                                                                                                                                              | 128                                       | 512                                                                                                                  | 512                                                                                                                  |

#### Notes:

1) For maximum processor current consumption, and thermal design power targets for Mobile AMD Duron processors refer to the appropriate Mobile AMD Duron processor data sheet.

2) The operational voltages listed for Mobile AMD Athlon processor Model 6 and Mobile AMD Duron processor Model 7 are nominal. With AMD PowerNow! technology, the actual voltage that these processors run at will be determined by software based on processor utilization and user preference.

*3)* For Mobile AMD Athlon processor Model 6and Mobile AMD Duron processor Model 7, the start-up voltage and frequency are changed to operational voltage and frequency under software control.

4) Below 1.300 V, the Mobile AMD Athlon and Mobile AMD Duron processor's DC to DC converter output can be incremented/decremented in 25 mV steps.

5) Power-up and Sleep voltages for Mobile AMD Athlon and Mobile AMD Duron processors are contingent on the chipset also supporting AMD system bus voltages at these levels when the AMD system bus interface is disconnected. Processor data sheets will specify exact operating and sleep voltages supported by the processor.

6) CPUID extended function 8000\_0007h - Advanced Power Management Feature Flags indicate the presence of mobile features: Thermal Diode, frequency, and voltage control mechanisms as indicated in the table above. These features are present in Mobile AMD Athlon processor Model 6 and Mobile AMD Duron processor Model 7.

7) The VID[4:0] codes for all versions of Mobile AMD processors (Mobile AMD Duron processor Model 3, Mobile AMD Duron processor Model 7 and Mobile AMD Athlon processor Model 6) are the same.

8) The FID codes for all versions of Mobile AMD Athlon and Mobile AMD Duron processors are the same.

# Voltage ID (VID) Mux

Mobile AMD Duron processor Model 3 notebooks require a Voltage ID (VID) Mux to be implemented at the motherboard level.

The purposes of the VID Mux are:

- 1. Provide a deterministic (power-up) core voltage to the Mobile AMD Duron processor Model 3 before it is capable of driving its VID[4:0] outputs to select its startup voltage.

- 2. Reduce the core voltage of Mobile AMD Duron processor Model 3 during the C3 processor state and the S1 sleep state. This is required because the Mobile AMD Duron processor Model 3 has significant static power dissipation, which can be significantly reduced during the C3 and S1 states by reducing Mobile AMD Duron processor Model 3's core voltage.

- 3. Allow the processor to control its core voltage during the C0, C1, and C2 processor states. This is required to enable AMD PowerNow! technology / processor driver / operating system control of processor power states.

- 4. To isolate Mobile AMD Duron processor Model 3's VID[4:0] outputs from voltages above 2.5 volts.

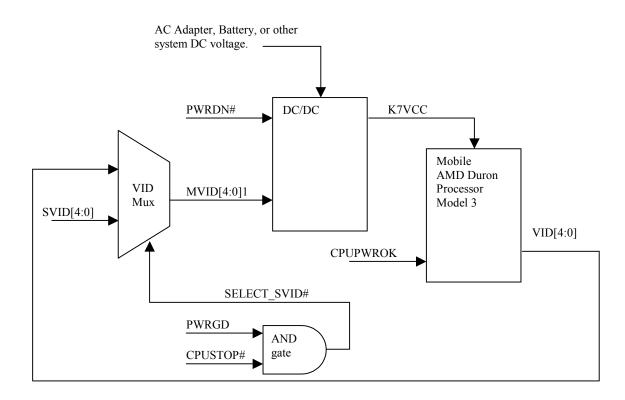

**Deterministic Power Up of K7VCC and Sleep Voltages** K7VCC is the name used throughout this document for the main voltage rail that power Mobile AMD Athlon and Mobile AMD Duron processors. K7VCC powers both the core and I/O of Mobile AMD Athlon and Mobile AMD Duron processors. The following block diagram and timing diagram show conceptually how a notebook PC will be implemented to use Mobile AMD Duron processor's VID[4:0] outputs to control K7VCC during C0, C1 and C2, and how the VID Mux drives a "sleep VID" to the processor DC to DC power converter so that K7VCC is at a deterministic power-up and sleep voltage level at power on and during C3 and S1. Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements

#### Figure 1. VID[4:0] Control of K7VCC Block Diagram

Mobile AMD Athlon™ Processor Model 5 (K7VCC) DC to DC Control for Notebook PCs **CPUPWROK** This is driven high to K7VCC after the core voltage is stable at the power-up voltage. Mobile AMD Athlon and Mobile AMD Duron processors use CPUPWROK to set various power-up defaults including the start-up VID[4:0] value.

**VID**[4:0] is the operational VID driven by Mobile AMD Athlon processor Model 5 to control the level of K7VCC. Mobile AMD Athlon processor Model 5 only drives VID[4:0] to the startup voltage after CPUPWROK to Mobile AMD Athlon processor Model 5 is asserted. VID[4:0] are controlled as specified in the Mobile AMD Athlon processor Model 5 specification. Note: that since the VID[4:0] outputs of Mobile AMD Athlon processor Model 5 are 2.5 volt tolerant open drain outputs, external pullups to +2.5 volts are needed, and voltage level shifting may be needed if the VID MUX or equivalent requires greater than 2.5 volts for VIH.

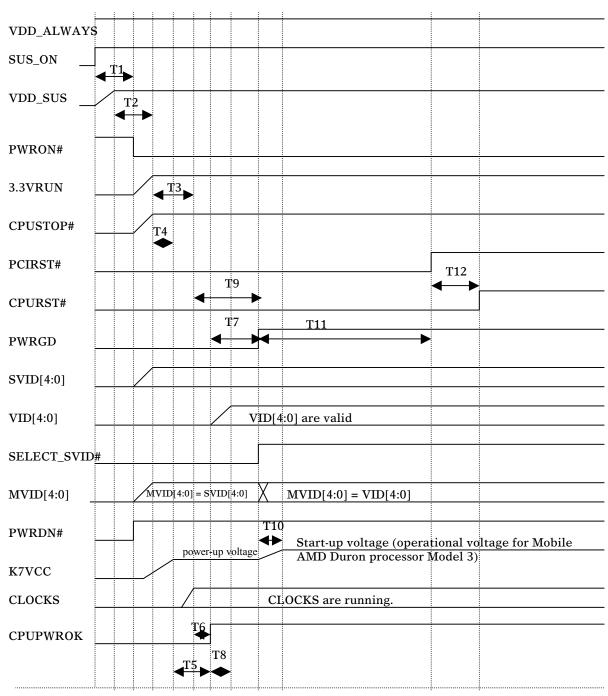

Figure 2. Deterministic Power-up Sequence for K7VCC Timing Diagram

**SVID**[4:0] is the Sleep VID set with resistors on the motherboard to dictate the level of K7VCC during:

- 1. Power on before CPUPWRGD (CPU Power Good) is asserted.

- 2. The C3 processor state and

- 3. The S1 sleep state

**MVID**[4:0] is the Multiplexed VID outputs of the VID Mux that are driven as inputs to the DC to DC.

**SELECT\_SVID#** acts as the select control input for the VID Mux.

0= MVID[4:0] = SVID[4:0]

1 = MVID[4:0] = VID[4:0]

**CPUSTOP#** is a signal from the Southbridge that is driven low during the C3 and S1 sleep states so that SVID[4:0] will be driven to the DC to DC converter on the MVID[4:0] inputs to the DC to DC power converter.

**PWRGD** is the combination of all of the power good indications for the power rails in the system that are powered when the system is operational. This signal ensures that the SVID[4:0] drives the DC to DC power converter before K7VCC is at a level where Mobile AMD Athlon and Mobile AMD Duron processors can deterministically drive their VID[4:0] outputs. This signal also goes to the Southbridge. When asserted, the Southbridge begins its power on reset count for CPURESET# and PCI RESET#.

**PWRDN#** is a control input that when asserted causes the DC to DC power converter to shut off its outputs, and enter a low power sleep state. PWRDN# ensures that the processor is only powered during the S0 and S1 states.

10

#### Table 2. Power-up Timing Requirements

|          |                                                                                                                                                                                                                                                                                                                                                                                            | Minimum        | Maximum         |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|--|

| T1       | Delay between turning on the "Suspend" planes (SUS_ON high) to turning on "Run" planes (PWRON# low).                                                                                                                                                                                                                                                                                       | 0 ns           |                 |  |

| T2       | Suspend Voltage Planes are within specification before "Run" voltage planes are within specification.                                                                                                                                                                                                                                                                                      | 0 μs           |                 |  |

| T3       | 3.3VRUN within specification to all clocks from the clock synthesis chip running within specification. This is based on the spec for existing Mobile AMD Athlon and Mobile AMD Duron processor clock synthesis chips.                                                                                                                                                                      |                | 3.0 ms          |  |

| T4       | 3.3VRUN within spec to K7VCC within spec of the power-up voltage specified by SVID[4:0] as strapped on the motherboard.                                                                                                                                                                                                                                                                    | 0 μs           |                 |  |

| T5       | K7VCC within specification at power-up voltage level before CPUPWROK is asserted. This applies to VDDA as well.                                                                                                                                                                                                                                                                            | 100 µs         |                 |  |

| T6       | Mobile AMD Athlon and Mobile AMD Duron processor 100 MHz processor clock input must be at 100 MHz and within specification prior to CPUPWROK assertion.                                                                                                                                                                                                                                    | 100 µs         |                 |  |

| T7       | CPUPWROK assertion to PWRGD assertion.                                                                                                                                                                                                                                                                                                                                                     | 20 ns          |                 |  |

| T8       | CPUPWROK assertion to VID[4:0] being driven to the startup-VID by Mobile<br>AMD Athlon and Mobile AMD Duron processors. Note: since VID[4:0] are 2.5 V<br>tolerant open drain outputs of Mobile AMD Athlon and Mobile AMD Duron<br>processors, transitioning to the startup VID may take longer than 20ns depending<br>on the implementation of the 2.5 V isolation and VID MUX circuitry. |                | 20 ns           |  |

| Notes:   |                                                                                                                                                                                                                                                                                                                                                                                            |                |                 |  |

| 1)<br>2) | The delay between PWRGD going active and PCIRST# deassertion is 1.8 milliseconds for curre<br>The delay between PCIRST# deassertion and CPURST# deassertion is 1.5 microseconds for cur<br>could be 0ns.                                                                                                                                                                                   | •              |                 |  |

| 3)       | COUID DE ONS.<br>CPURST# is never asserted without PCIRST# also being asserted. Therefore the CPURST# duration is always greater than 1.5<br>milliseconds, and the Northbridge is always reset when the processor is reset.                                                                                                                                                                |                |                 |  |

| 4)       | The names and polarity of the signals used to turn on the power supplies will vary by chipset a here is the general timing relationship between signals.                                                                                                                                                                                                                                   | nd system. Whe | at is important |  |

|          | Mobile AMD Athlon and Mobile AMD Duron processors have a "ring" oscillator that runs from a fixed 2.5volt supply (VDDA).<br>This VDDA input to the Mobile AMD Athlon and Mobile AMD Duron processors have the same timing requirements as K7VCC.                                                                                                                                           |                |                 |  |

|          | CPURST# is required to be asserted before CPUPWROK is asserted. In practice CPURST# should be held low by the Southbridge before the "RUN" planes are turned on.                                                                                                                                                                                                                           |                |                 |  |

| 7)       | DC to DC converters may take several microseconds to significantly change their output voltage in response to changes in their VID[4:0] inputs. Therefore, if it takes several nanoseconds (even 100) to transition between the power-up VID and the startup VID, the voltage output of the DC to DC converter will not change quickly enough to bring K7VCC out of spec.                  |                |                 |  |

| 8)       | Timing for resume from S3 (Suspend to RAM) is the same as power-up timing except that the "Suspend Voltage" planes remain powered throughout S3. PCI RESET# and CPU RESET# are asserted throughout S3.                                                                                                                                                                                     |                |                 |  |

| 9)       | P) Refer to "Appendix C: Standard Power Sequencing Guidelines" on page 47 for definition and description of ALWAYS, RUN, and SUS power planes.                                                                                                                                                                                                                                             |                |                 |  |

| 10)      | PWRDN# is functionally the inverse of PWRON#.                                                                                                                                                                                                                                                                                                                                              |                |                 |  |

#### Table 2. Power-up Timing Requirements (continued)

|     |                                                                         | Minimum | Maximum |

|-----|-------------------------------------------------------------------------|---------|---------|

| T9  | All system clocks must be running within spec before PWRGD is asserted. | 100 µs  |         |

| T10 | K7VCC transition time from power-up voltage to start-up voltage.        |         | 100 µs  |

| T11 | PWRGD assertion to PCIRST# de-assertion.                                | 1.0 ms  |         |

| T12 | PCIRST# deassertion to CPURST# de-assertion.                            | 0 ns    |         |

#### Notes:

2) The delay between PCIRST# deassertion and CPURST# deassertion is 1.5 microseconds for current AMD chipsets. This delay could be 0ns.

3) CPURST# is never asserted without PCIRST# also being asserted. Therefore the CPURST# duration is always greater than 1.5 milliseconds, and the Northbridge is always reset when the processor is reset.

4) The names and polarity of the signals used to turn on the power supplies will vary by chipset and system. What is important here is the general timing relationship between signals.

5) Mobile AMD Athlon and Mobile AMD Duron processors have a "ring" oscillator that runs from a fixed 2.5volt supply (VDDA). This VDDA input to the Mobile AMD Athlon and Mobile AMD Duron processors have the same timing requirements as K7VCC.

- 6) CPURST# is required to be asserted before CPUPWROK is asserted. In practice CPURST# should be held low by the Southbridge before the "RUN" planes are turned on.

- 7) DC to DC converters may take several microseconds to significantly change their output voltage in response to changes in their VID[4:0] inputs. Therefore, if it takes several nanoseconds (even 100) to transition between the power-up VID and the startup VID, the voltage output of the DC to DC converter will not change quickly enough to bring K7VCC out of spec.

- 8) Timing for resume from S3 (Suspend to RAM) is the same as power-up timing except that the "Suspend Voltage" planes remain powered throughout S3. PCI RESET# and CPU RESET# are asserted throughout S3.

- 9) Refer to "Appendix C: Standard Power Sequencing Guidelines" on page 47 for definition and description of ALWAYS, RUN, and SUS power planes.

- 10) PWRDN# is functionally the inverse of PWRON#.

#### VID[4:0] Control Requirements During C0, C1 and C2

It is required that the Mobile AMD Athlon and Mobile AMD Duron processor's VID[4:0] Outputs control the Mobile AMD Athlon and Mobile AMD Duron processor core voltage during C0, C1 and C2.

As described in the previous section, the VID MUX on the motherboard passes the VID[4:0] outputs of the Mobile AMD Athlon and Mobile AMD Duron processor to the Mobile AMD Athlon and Mobile AMD Duron processor core voltage DC to DC during the C0, C1, and C2 states. It is required that all of the VID[4:0] outputs of Mobile AMD Athlon and Mobile AMD Duron processors are used for Mobile AMD Athlon and Mobile AMD Duron processor-based notebooks. This is required for compatibility with future processor drivers or operating systems that will control Processor Performance States (processor voltage and frequency) in a processor-specific manner that does not vary from system to system. This is also

<sup>1)</sup> The delay between PWRGD going active and PCIRST# deassertion is 1.8 milliseconds for current AMD chipsets.

24106A-August 2000

required for optimal power management of Mobile AMD Athlon and Mobile AMD Duron processor-based notebooks.

# **Power-up and Sleep Voltages**

|                                                                                          | The motherboard must be capable of configuring the power-up<br>and sleep voltages from 1.3 V to 1.0 V +/- 100 mV. Note: 1.0 V is<br>in support of the Mobile AMD Duron processor Model 7 and the<br>Mobile AMD Athlon processor Model 6. Because the Mobile<br>AMD Athlon and Mobile AMD Duron processor's DC to DC<br>power converter is capable of selecting voltages in increments<br>of 25 mV, and because the sleep voltage for future Mobile<br>AMD Athlon and Mobile AMD Duron processors is not<br>currently known, the most optimized motherboards will allow<br>for configuring the power-up/sleep voltages in 25 mV<br>increments. |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mobile AMD Duron™<br>Processor Model 3                                                   | The Power-up and sleep voltage for Mobile AMD Duron processor Model 3 versions is determined by the processor and the chipset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                          | The Mobile AMD Duron processor Model 3 power up and sleep voltage is 1.3V +/- 100 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Mobile AMD Athlon™<br>Processor Model 6<br>and Mobile<br>AMD Duron™<br>Processor Model 7 | The power-up and sleep voltages for Mobile AMD Athlon processor Model 6 and Mobile AMD Duron processor Model 7 are $1.0 \text{ V}$ +/- 100 mV. Note: this is the goal and has not yet been proven; therefore, the motherboard must have stuffing options to select higher voltages.                                                                                                                                                                                                                                                                                                                                                           |

Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements

# VID[4:0] Output Voltage Tolerance

The motherboard is required to prevent Mobile AMD Athlon and Mobile AMD Duron processor's VID[4:0] outputs from being pulled to voltages above 2.5 volts. Refer to the Socket A Mobile AMD Athlon<sup>™</sup> Processor Data Sheet for the voltage tolerance of all Mobile AMD Athlon and Mobile AMD Duron processor I/O. There are many ways to implement voltage translation; some logic families support this directly. One potential implementation can be found in the AMD Athlon processor PGA design guide, this was implemented for desktop PCs; it is up to the OEM/ODM to determine if this solution is optimal for notebook PCs.

# **DC to DC Power Converters**

DC to DC power converters must support dynamic voltage transition requirements to enable AMD PowerNow! technology processor performance state transitions in Mobile AMD Athlon and Mobile AMD Duron processor notebooks, and to enable transitions between sleep and operating voltages as controlled by the system using the VID Mux. AMD has a recommended DC to DC design and specification for Mobile AMD Duron processors. Refer to the *Mobile AMD Athlon*<sup>TM</sup> Processor Power Module Design Guide, publication #24125.

Some of the requirements for this Mobile AMD Athlon and Mobile AMD Duron processor's DC to DC power converters which are met by AMD's recommended solution include:

- 1. It must be capable of generating all of the voltages that Mobile AMD Athlon and Mobile AMD Duron processors can operate at.

- 2. It must be capable of continuously supplying Mobile AMD Athlon and Mobile AMD Duron processor maximum current load PLUS the maximum current drawn by the AMD system bus interface on the Northbridge that is also powered by voltage rail that powers Mobile AMD Athlon and Mobile AMD Duron processors (K7VCC). The DC to DC power converters supplying K7VCC in systems capable of supporting the highest frequency Mobile AMD Athlon and Mobile AMD Duron processors are required to be capable of continuously supplying 22 Amps of K7VCC.

- 3. It should be high efficiency (greater than 90%) when the AMD system bus is connected (the processor is consuming 5Watts or more).

- 4. The DC to DC power converter is required to transition between the lowest and highest voltage selectable by VID[4:0] within 100 microseconds. Note: the Mobile AMD Athlon processor Model 6 and the Mobile AMD Duron processors Model 3 and Model 7 is in the equivalent of a Stop Grant state when VID[4:0] changes occur. See the processor data sheet for Stop Grant current. Also note: transitions from higher voltages to lower voltages are not required to complete in 100 microseconds because operation at lower frequencies can occur at higher than the minimum required voltage.

- 5. A power good indication signal is required for K7VCC (CPU core voltage) which:

- a. Is required not to de-assert based on VID[4:0] dictated voltage transitions. De-assertation of this K7VCC power good will cause the system to reset and is therefore not allowed in response to VID[4:0] dictated transitions.

- b. Has a threshold for assertion and de-assertion lower than the minimum voltage that will ever be selected for Mobile AMD Athlon and Mobile AMD Duron processors. A voltage threshold of 0.9 Volts is therefore recommended.

- c. During initial power-on, this power good signal must not assert until after K7VCC has reached the level specified by the VID[4:0]. This requirement must be verified by system characterization. A delay of 10 milliseconds from K7VCC reaching 0.9 volts to assertion of the K7VCC power good indication signal is recommended and will satisfy this requirement.

- d. This power good indication signal is open collector, and active high (pulled up on the motherboard). This signal is actively driven low when K7VCC is below 0.9 volts.

- e. The *AMD Athlon PGA Design Guide* has a circuit which is recommended for K7VCC power good.

# VID[4:0] Codes Used

It is a requirement that the DC to DC power converter used for K7VCC in Mobile AMD Athlon and Mobile AMD Duron processor-based notebook uses the following VID codes. This is required for compatibility with future Microsoft processor drivers and operating systems that will support processor performance states (voltage and frequency combinations) in a processor specific manner. Supporting these VID codes is also required to enable optimal power management for Mobile AMD Athlon and Mobile AMD Duron processors. These VID codes are used by all versions of Mobile AMD Duron processors, Model 3 and Model 7, and Mobile AMD Athlon processors, Model 5 and Model 6.

The VID codes used by Mobile AMD Athlon and Mobile AMD Duron processor and associated DC to DC power converters for K7VCC core voltage are:

| VID[4:0] | Voltage selected | VID[4:0] | Voltage selected |

|----------|------------------|----------|------------------|

| 00000    | 2.000 V          | 10000    | 1.275 V          |

| 00001    | 1.950 V          | 10001    | 1.250 V          |

| 00010    | 1.900 V          | 10010    | 1.225 V          |

| 00011    | 1.850 V          | 10011    | 1.200 V          |

| 00100    | 1.800 V          | 10100    | 1.175 V          |

| 00101    | 1.750 V          | 10101    | 1.150 V          |

| 00110    | 1.700 V          | 10110    | 1.125 V          |

| 00111    | 1.650 V          | 10111    | 1.100 V          |

| 01000    | 1.600 V          | 11000    | 1.075 V          |

| 01001    | 1.550 V          | 11001    | 1.050 V          |

| 01010    | 1.500 V          | 11010    | 1.025 V          |

| 01011    | 1.450 V          | 11011    | 1.000 V          |

| 01100    | 1.400 V          | 11100    | 0.975 V          |

| 01101    | 1.350 V          | 11101    | 0.950 V          |

Table 3. VID Codes used by Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processors

| VID[4:0] | Voltage selected | VID[4:0] | Voltage selected |

|----------|------------------|----------|------------------|

| 01110    | 1.300 V          | 11110    | 0.925 V          |

| 01111    | Shutdown         | 11111    | Shutdown         |

### Table 3. VID Codes used by Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processors (continued)

# **Processor Temperature Sensor**

|                                                                                              | Manufacturer                                                                                                                                                                                                                                                            | Model Number                                                                                                            |                                                |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Table 4. Recommended Transistors for Accurate Temperature Control                            |                                                                                                                                                                                                                                                                         |                                                                                                                         |                                                |

|                                                                                              | Per the 1617 data sheet, Maxim<br>transistors for this purpose:                                                                                                                                                                                                         | has tested the follo                                                                                                    | owing                                          |

|                                                                                              | "Temperature accuracy depe<br>quality, diode-connected sma                                                                                                                                                                                                              |                                                                                                                         |                                                |

| Mobile AMD Duron™<br>Processor Model 3                                                       | The Mobile AMD Duron processor I<br>die diode for measuring the process<br>SOT23 packaged transistor should<br>1617 temperature sensor (or equiva-<br>in the design such that it can be<br>processor and used to measure the<br>the Maxim 1617 data sheet:              | sor's temperature. A di<br>d be used with the M<br>alent), and should be p<br>e thermally coupled                       | screte<br>AXIM<br>placed<br>to the             |

| Mobile AMD Athlon™<br>Processor Model 6<br>and the Mobile<br>AMD Duron™<br>Processor Model 7 | The Mobile AMD Athlon process<br>AMD Duron processor Model 7 bo<br>measuring the processor's tempera<br>use the Maxim 1617 "Remote/Loca<br>SMBus Serial Interface" (or equi-<br>sensor) to read the processor's on-<br>can read the processor's thermat<br>temperature. | th have an on-die dio<br>ature. Motherboards s<br>al Temperature Senso<br>valent/similar temper<br>die diode. The Maxin | de for<br>should<br>r with<br>rature<br>n 1617 |

|                                                                                              | Using the Maxim 1617 (or simila<br>sensor, a notebook can be designed<br>have an on-die thermal diode and pr<br>on-die thermal diode. Refer to the<br>details of the 1617.                                                                                              | d to support processor<br>rocessors that do not h                                                                       | rs that<br>ave an                              |

| Manufacturer                | Model Number |

|-----------------------------|--------------|

| Central Semiconductor (USA) | CMPT3904     |

| Motorola (USA)              | MMBT3904     |

| Manufacturer                 | Model Number  |

|------------------------------|---------------|

| National Semiconductor (USA) | MMBT3904      |

| Rohm Semiconductor (Japan)   | SST3904       |

| Samsung (Korea)              | KST3904-TF    |

| Siemens (Germany)            | SMBT3904      |

| Zetex (England)              | FMMT3904CT-ND |

Table 4. Recommended Transistors for Accurate Temperature Control

This approach leads to the possibility of using the on-die diode with the Mobile AMD Athlon processor Model 6 and the Mobile AMD Duron processor Model 7 versions. The OEM/ODM can choose to implement an alternate solution for monitoring the temperature of a Mobile AMD Duron processor Model 3, but should consider the migration path to using the on-die thermal diode that will be present on the Mobile AMD Athlon processor Model 6 and the Mobile AMD Duron processor Model 7 versions.

# Performance States for Mobile AMD Duron<sup>™</sup> Processor Model 3

The Mobile AMD Duron processor Model 3 does not support dynamic core voltage and frequency changes. The AMD system bus FID Change protocol mechanism that allows dynamic processor core voltage and frequency changes is supported only by the Mobile AMD Athlon processor Model 6 and the Mobile AMD Duron processor Model 7.

Not all Mobile AMD Athlon and Mobile AMD Duron processor Northbridges support the AMD system bus FID Change protocol mechanism, for example, some Mobile AMD Duron processor Northbridges intended for use in Desktop PCs.

Notebooks that use Mobile AMD Duron processor Model 3 or chipsets that do not support the AMD system bus FID\_Change protocol should implement the following alternate method for enabling the "power on demand" functionality of AMD PowerNow! technology automatic mode. The alternate method for enabling power on demand utilizes throttling of the processor with STPCLK#. Without such a mechanism, battery powered run time of a Mobile AMD Duron processor Model 3 24106A-August 2000

Mobile AMD Athlon<sup>™</sup> and AMD Duron<sup>™</sup> Processor System Requirements

based notebook will be significantly reduced under many operating scenarios.

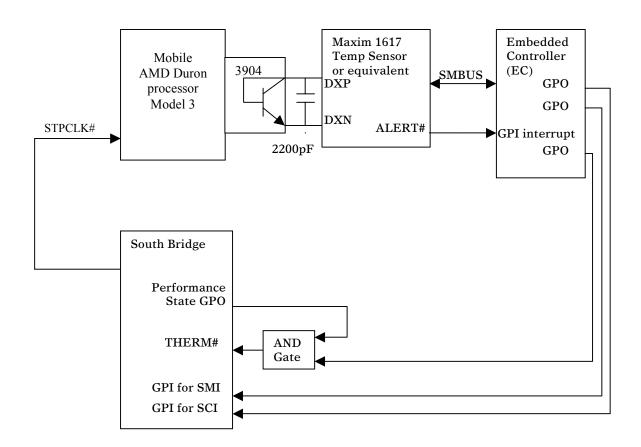

Power on Demand<br/>Enabled with<br/>THERM#Conceptual Block Diagram of implementation that allows<br/>AMD PowerNow! technology power on demand automatic mode<br/>functionality by throttling the processor with STPCLK# instead<br/>of dynamic voltage and frequency changes (for Mobile<br/>AMD Duron processor Model 3).

The AMD PowerNow! technology or similar driver can use a Southbridge GPIO to assert the THERM# input to the Southbridge. Processor performance states can be implemented as follows with throttling. The number of performance states implemented is system specific:

| Performance State                                                                | Performance                            | Performance State GPO |  |  |

|----------------------------------------------------------------------------------|----------------------------------------|-----------------------|--|--|

| 0                                                                                | Highest: (no throttling)               | Driven high           |  |  |

| 1                                                                                | Throttle 1/8 <sup>th</sup> of the time | Low                   |  |  |

| 2                                                                                | Throttle 1/4th of the time             | Low                   |  |  |

| 3                                                                                | Throttle 3/8ths of the time            | Low                   |  |  |

| 4                                                                                | Throttle 1/2 of the time               | Low                   |  |  |

| 5                                                                                | Throttle 5/8ths of the time            | Low                   |  |  |

| 6                                                                                | Throttle 3/4ths of the time            | Low                   |  |  |

| 7                                                                                | Lowest: Throttle 7/8ths of the time    | Low                   |  |  |

| <i>Notes:</i><br>A Southbridge-specific register programs throttling duty cycle. |                                        |                       |  |  |

#### Table 5. STPCLK# Processor Throttling Performance States

24106A-August 2000

#### Figure 3. AMD PowerNow!™ Technology Conceptual Block Diagram

#### Notes:

- 1) AMD PowerNow! technology software would program the THERM# clock throttling duty cycle and then drive the GPO low to force AMD PowerNow! technology throttling.

- 2) THERM# throttling is not the same as clock throttling used by the operating system for ACPI thermal zone throttling. ACPI thermal zone throttling is controlled by the operating system when the BIOS indicates (with \_PSV) that the processor has reached a temperature at that the operating system should use throttling to control the processor's temperature. ACPI uses the ACPI defined Processor Control (P\_CNT) for throttling the processor. An entirely different non-operating system owned register is used for AMD PowerNow! technology throttling with the Mobile AMD Duron processor Model 3 version.

# FID[3:0] Output Pins

- 1. The FID[3:0] outputs are driven to the Northbridge and must be isolated from voltages above 2.5 volts.

- 2. Refer to the Northbridge data sheet to determine which Northbridge pins the processor FID[3:0] outputs will be muxed onto.

- 3. The Northbridge only samples its FID[3:0] inputs on the deassertion of RESET#. (RESET# to the Northbridge is functionally the same as the PCI RESET# signal).

- 4. The Northbridge uses the FID[3:0] sampled on the deassertion of RESET# to determine what the AMD system bus SIP (Serial Initialization Protocol) stream should be for the processor's reported frequency.

- 5. For dynamic voltage and frequency changes, the FID[3:0] pins do not transmit new information to the Northbridge. The AMD system bus FID Change Special cycle is used for this purpose. Refer to the Socket A Mobile AMD Athlon processor Data Sheet for more details on the AMD system bus FID Change special cycle.

- 6. Refer to the Mobile AMD Athlon and Mobile AMD Duron processor data sheets for the FID code definitions.

## **Thermal Requirements**

Mobile AMD Athlon and Mobile AMD Duron processor-based systems are required to have thermal solutions which can keep the processor and all other system components within their specified operating temperatures given a processor power of 24W for thermal design purposes. For more details refer to the *Mobile AMD Athlon<sup>TM</sup> and AMD Duron<sup>TM</sup> Processor Thermal Design Application Note*, document #TBD.

Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements

# **BIOS Requirements**

This section is limited to Mobile AMD Athlon<sup>TM</sup> and AMD Duron<sup>TM</sup> Processor Power Management requirements for Mobile AMD Athlon and Mobile AMD Duron processor BIOS.

# VID[4:0] codes

These codes are specified in the section entitled *VID*[4:0] Codes Used on page 16.

## **Chipset, Processor, and ACPI Table Entry Configuration**

In an ACPI controlled system, transitions between ACPI defined power states are controlled by the operating system. Table 6, "Chipset, Processor, and ACPI Table Configuration by the BIOS to Enable ACPI State Support," on page 24 defines:

- a. which registers the BIOS must configure in the processor and in the chipset

- b. which ACPI defined table entries must be provided by the BIOS to enable the use of the ACPI states listed.

The specific intent is to enable optimal power savings based on the use of the ACPI defined processor power states C1, C2, and C3. Additionally, this table identifies which registers are used by the operating system to force transitions between the ACPI working state and the rest of the ACPI states that are supported by the system.

It is intended that there will be a chipset specific document to accompany the document that provides all of the chipset specific register programming information that is not included in the far-right column of Table 6, "Chipset, Processor, and ACPI Table Configuration by the BIOS to Enable ACPI State Support," on page 24

| Mobile AMD Athlon™ and AMD Duron™ Processor System Requirements |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

24106A-August 2000

### Table 6. Chipset, Processor, and ACPI Table Configuration by the BIOS to Enable ACPI State Support

| ACPI State Name/ Properties /<br>Operating System name                                                                    | ltem<br># | Function and BIOS Responsibility                                                                                                                                                                                                                                                                                                                                                                                                                    | BIOS supplied ACPI Table<br>entry/object/control method                                                                                                           | Chipset-<br>specific<br>register info |

|---------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                                                                                                                           | 1         | Enable AMD system bus disconnect on Halt                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                 |                                       |

| C1 / Halt caches snoopable.<br>ACPI places the processor into the<br>C1 state by executing the HLT (halt<br>instruction). | 2         | Mobile AMD Duron processor Model 3: BIOS<br>must program the ClkCtL MSR (C001_001Bh) as<br>follows to select a halt disconnect divisor of 128<br>and stop grant divisor of 128.<br>Program ClkCtL MSR to 32'h2006_9223<br>Mobile AMD Athlon processor Model 6 and<br>Mobile AMD Duron processor Model 7: BIOS<br>must program the ClkCtL MSR (C001_001Bh) to<br>32'h6007_9263 that selects a Hlt divisor of 128<br>and a stop grant divisor of 512. | _                                                                                                                                                                 | _                                     |

|                                                                                                                           | 3         | Fixed ACPI Description Table Fixed Feature<br>Flag: PROC_C1                                                                                                                                                                                                                                                                                                                                                                                         | BIOS builds the Fixed ACPI<br>Description Table before loading<br>the operating system. The<br>PROC_C1 fixed feature flag in this<br>table is set to a 1 by BIOS. | _                                     |

#### Notes:

1) The Item # field is used to correlate a chipset specific file to this table. VIA, ALI, etc., specific information is in a separate file to accompany this document as appropriate.

2) Unless otherwise specified BIOS configures the registers/tables during the POST routine and these settings are not changed during system operation.

3) Enabling the C3 processor state requires that the Mobile AMD Athlon and Mobile AMD Duron processor's Northbridge properly implements the ACPI defined PM2 CNT register bit 0 of that is the ARB\_DIS (arbiter disable) bit. When the ACPI driver sets the ARB\_DIS bit, the Northbridge must stop granting bus masters access to system memory (as the processor caches cannot be snooped during C3. Once the Northbridge has disconnected the AMD system bus in response to a stop grant special cycle when the ARB\_DIS bit is set, the Northbridge is not allowed to initiate AMD system bus re-connect, the processor will initiate AMD system bus re-connect once a resume event occurs and STPCLK# has been de-asserted.

4) Reducing the Mobile AMD Athlon and Mobile AMD Duron processor's core voltage during C3 is strongly recommended as it significantly reduces the Mobile AMD Athlon and Mobile AMD Duron processor's static power consumption and therefore contributes to system cooling and extended battery powered run-time.

| ACPI State Name/ Properties /<br>Operating System name          | ltem<br># | Function and BIOS Responsibility                                                                                                                                                | BIOS supplied ACPI Table<br>entry/object/control method                                                                           | Chipset-<br>specific<br>register info |

|-----------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                                                                 | 4         | Enable the operating system use of the C2 processor power state.                                                                                                                | BIOS specifies a P_LVL2_LAT of                                                                                                    |                                       |

|                                                                 |           |                                                                                                                                                                                 | 5µs for Mobile AMD Duron<br>processor Model 3                                                                                     |                                       |

| C2 / Stop Grant caches snoopable.                               |           |                                                                                                                                                                                 | 15µs for Mobile AMD Athlon<br>processor Model 6 and Mobile<br>AMD Duron processor Model 7 in<br>the Fixed ACPI Description Table. | -                                     |

| ACPI places the processor into the C2 state by reading the ACPI | 5         | Enable AMD system bus disconnect on Stop<br>Grant                                                                                                                               | -                                                                                                                                 |                                       |

| defined P_LVL2 register.                                        | 6         | Enable SDRAM/DDR power-down mode when<br>memory is idle/ Enable self refresh when<br>memory is idle.                                                                            | -                                                                                                                                 |                                       |

|                                                                 | 7         | Mobile AMD Duron processor Model 3/ Mobile<br>AMD Athlon processor Model 6/ Mobile<br>AMD Duron processor Model 7 ClkCtL MSR was<br>already configured by BIOS in item 2 above. | -                                                                                                                                 | _                                     |

#### Notes:

1) The Item # field is used to correlate a chipset specific file to this table. VIA, ALI, etc., specific information is in a separate file to accompany this document as appropriate.

2) Unless otherwise specified BIOS configures the registers/tables during the POST routine and these settings are not changed during system operation.

3) Enabling the C3 processor state requires that the Mobile AMD Athlon and Mobile AMD Duron processor's Northbridge properly implements the ACPI defined PM2\_CNT register bit 0 of that is the ARB\_DIS (arbiter disable) bit. When the ACPI driver sets the ARB\_DIS bit, the Northbridge must stop granting bus masters access to system memory (as the processor caches cannot be snooped during C3. Once the Northbridge has disconnected the AMD system bus in response to a stop grant special cycle when the ARB\_DIS bit is set, the Northbridge is not allowed to initiate AMD system bus re-connect, the processor will initiate AMD system bus re-connect once a resume event occurs and STPCLK# has been de-asserted.

Reducing the Mobile AMD Athlon and Mobile AMD Duron processor's core voltage during C3 is strongly recommended as it significantly reduces the Mobile AMD Athlon and Mobile AMD Duron processor's static power consumption and therefore contributes to system cooling and extended battery powered run-time. 4)

24106A-August 2000

| ACPI State Name/ Properties /<br>Operating System name                                                                                                                        | ltem<br># | Function and BIOS Responsibility                                                                                                                                                | BIOS supplied ACPI Table<br>entry/object/control method                                                                                                       | Chipset-<br>specific<br>register info |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| C3 / Stop Grant caches not<br>snoopable                                                                                                                                       | 8         | Mobile AMD Duron processor Model 3/ Mobile<br>AMD Athlon processor Model 6/ Mobile<br>AMD Duron processor Model 7 ClkCtL MSR was<br>already configured by BIOS in item 2 above. | _                                                                                                                                                             | _                                     |

| ACPI:                                                                                                                                                                         |           |                                                                                                                                                                                 | BIOS specifies a P_LVL3_LAT of                                                                                                                                |                                       |

| <ol> <li>writes a 1 to the PM2_CNT<br/>register bit 0 (ARB_DIS) in the<br/>Northbridge before entry into C3.<br/>(The operating system does this<br/>for C3 only.)</li> </ol> | 9         | Enable the operating system use of the C3                                                                                                                                       | a) 200µs to 900µs in the Fixed ACPI<br>Description Table. If the chipset<br>and system supports C3 and the<br>processor voltage will be<br>reduced during C3. |                                       |

| 2) Places the processor into the C3<br>state by reading the ACPI defined<br>P_LVL3 register.                                                                                  |           | processor power state.                                                                                                                                                          | b) 15µs if the chipset/system does<br>not support reducing the<br>processor voltage during C3.                                                                | _                                     |