# STR73x Microcontroller Reference Manual

Rev. 1

September 2005

# **REFERENCE MANUAL**

# STR73x MICROCONTROLLER FAMILY

#### **1 INTRODUCTION**

This Reference Manual provides complete information for application developers on how to use the STR73x Microcontroller memory and peripherals.

For Ordering Information, Mechanical and Electrical Device Characteristics please refer to the STR73x Preliminary Data.

For information on programming, erasing and protection of the internal Flash memory please refer to the STR7 Flash Programming Reference Manual

For information on the ARM7TDMI core please refer to the ARM7TDMI Technical Reference Manual.

# **Related documents:**

#### Available from www.arm.com:

ARM7TDMI Technical Reference Manual

#### Available from www.st.com:

STR73xF Preliminary Data

STR7 Flash Programming Reference Manual

\_

| 1 INTRODUCTION |                |                                          |

|----------------|----------------|------------------------------------------|

| ∠ w∈<br>2.1    |                |                                          |

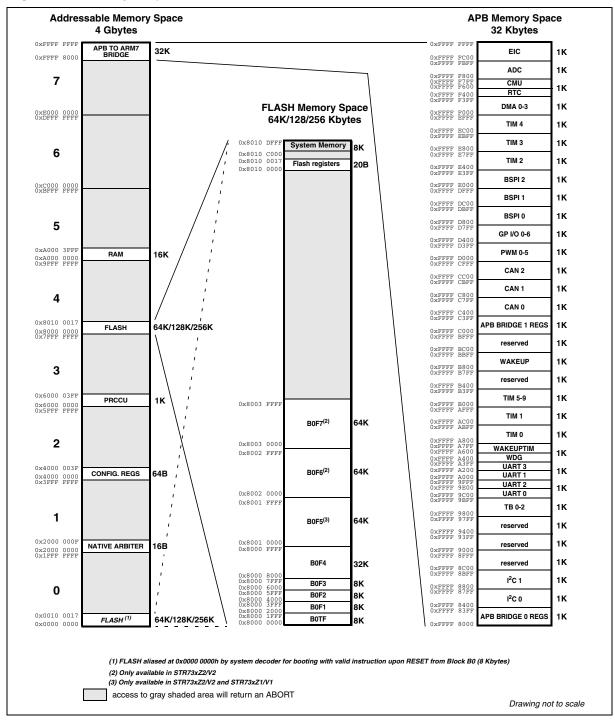

| 2.1            | 2.1.1          | Memory Map                               |

|                | 2.1.1          | Boot Memory                              |

|                | 2.1.3          | RAM                                      |

|                | 2.1.4          | Flash                                    |

| 2.2            |                | Configuration                            |

|                | 2.2.1          | SystemMemory Boot Mode                   |

| 3 POV          |                | SET AND CLOCKS                           |

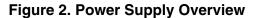

| 3.1            |                | er Supply                                |

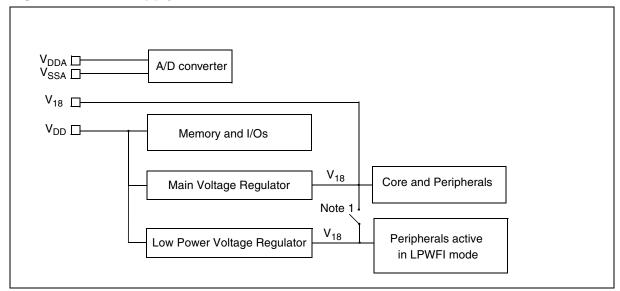

| 3.2            |                | t                                        |

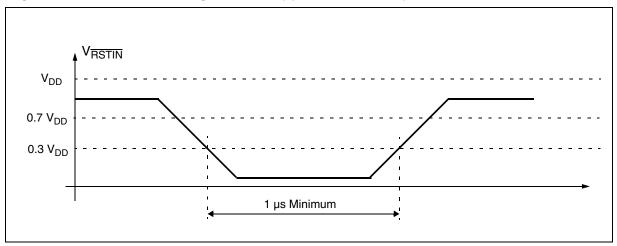

|                | 3.2.1          | Reset Pin Timing                         |

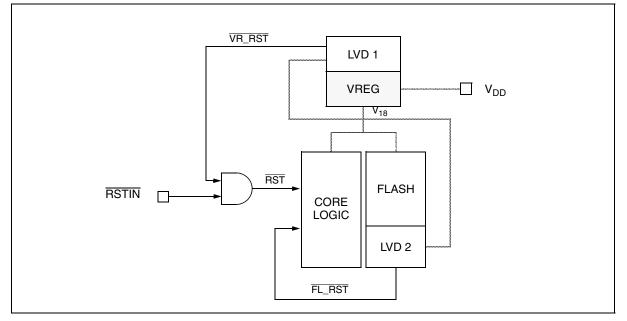

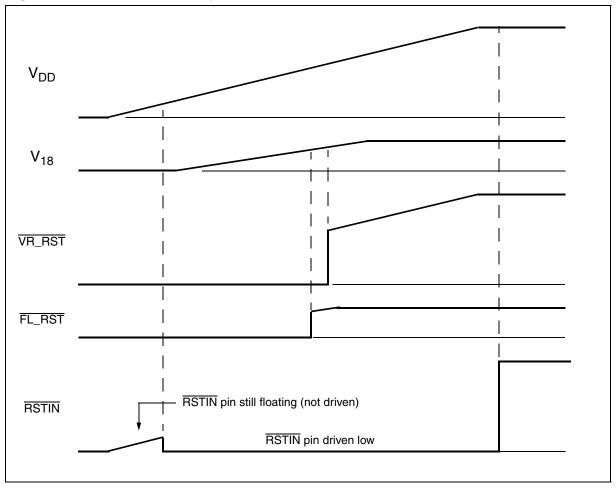

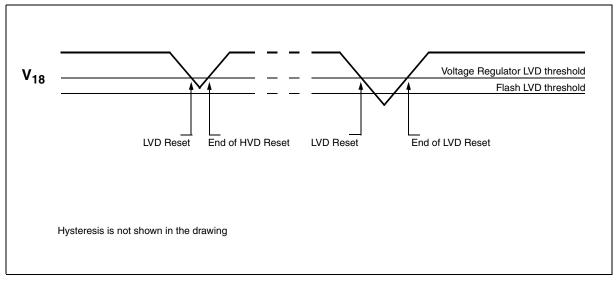

|                | 3.2.2          | LVD Reset                                |

| 3.3            | Clock          | (s                                       |

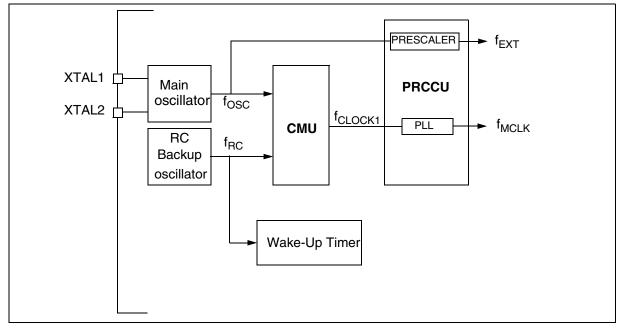

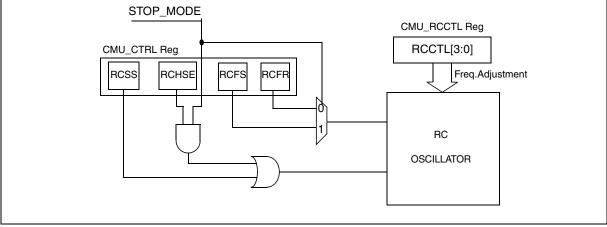

|                | 3.3.1          | RC Oscillator                            |

| 3.4            | Low I          | Power Modes                              |

|                | 3.4.1          | Slow Mode                                |

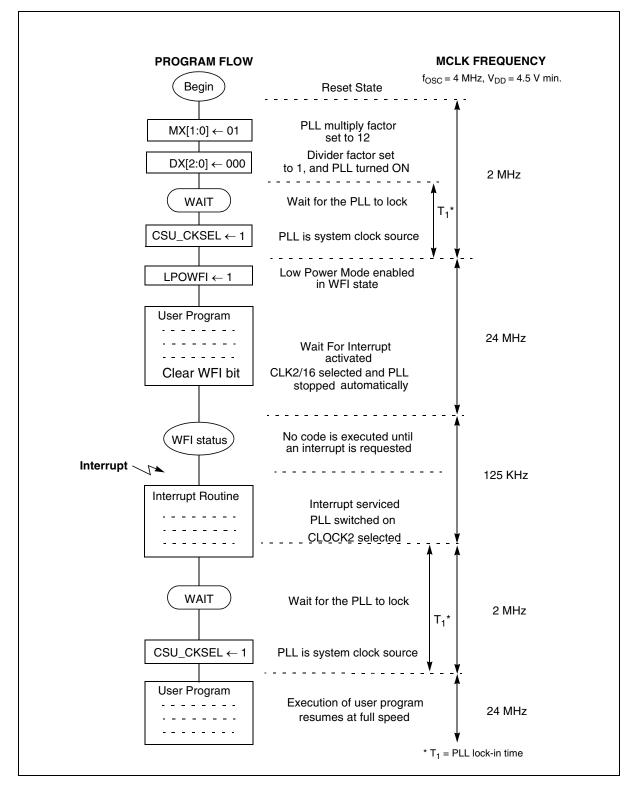

|                | 3.4.2          | WFI Mode                                 |

|                | 3.4.3          | LPWFI Mode                               |

|                | 3.4.4          | Halt Mode                                |

|                | 3.4.5          | Stop Mode                                |

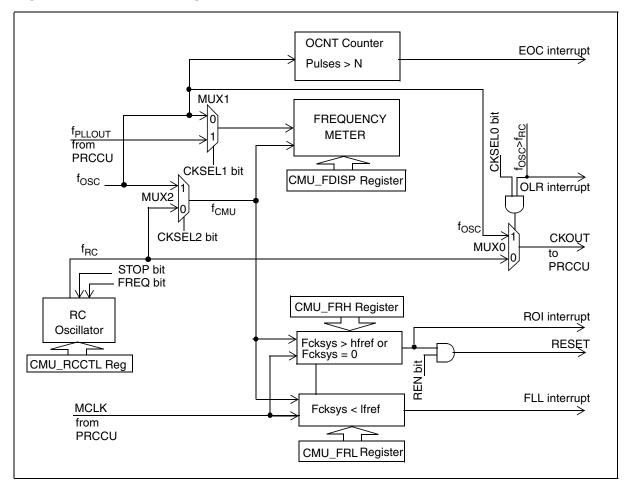

| 3.5            |                | Monitor Unit (CMU)                       |

|                | 3.5.1          | Register Write Protection                |

|                | 3.5.2          | Clock Source Selection                   |

|                | 3.5.3          | Oscillator Frequency Monitoring          |

|                | 3.5.4          | MCLK Frequency Monitoring                |

|                | 3.5.5          | Clock Frequency Measurement              |

|                | 3.5.6          | RC Oscillator Control                    |

|                | 3.5.7          | Limitations                              |

|                | 3.5.8          | Register Description                     |

|                | 3.5.9          | CMU Register Map                         |

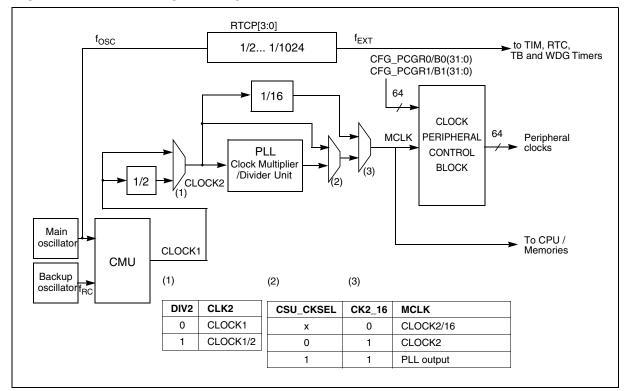

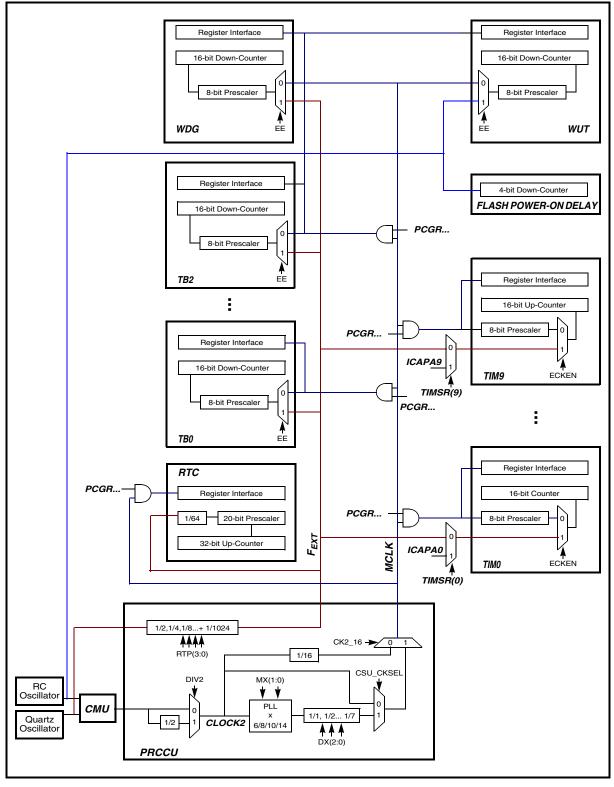

| 3.6            |                | er, Reset and Clock Control Unit (PRCCU) |

|                | 3.6.1          | Overview                                 |

|                | 3.6.2          | PLL Clock Multiplier Programming         |

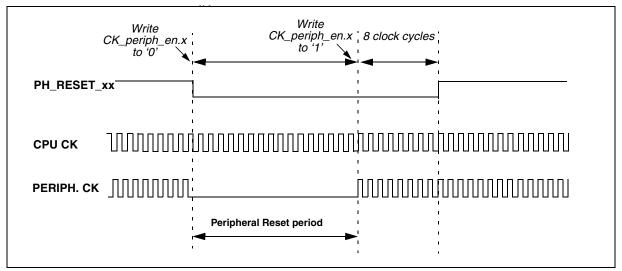

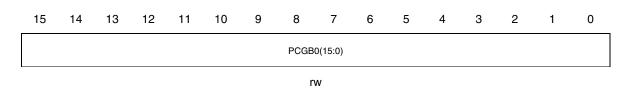

|                | 3.6.3<br>3.6.4 | Peripheral Clocks                        |

|                | 3.6.4<br>3.6.5 | RT Clock (fEXT)                          |

|                | 3.6.5<br>3.6.6 | Clock Configuration Reset State          |

|                | 3.6.7          | •                                        |

|                | 3.0.7          | Register Description                     |

\_

|         | 3.6.8    | PRCCU Register Map                                        |

|---------|----------|-----------------------------------------------------------|

| 4 CON   |          | ATION REGISTERS (CFG)61                                   |

| 4.1     |          | m Configuration Registers61                               |

|         | 4.1.1    | Configuration Register 0 (CFG_R0)61                       |

|         | 4.1.2    | Configuration Register 1 (CFG_R1)62                       |

|         | 4.1.3    | Device Identification Register (CFG_DIDR)                 |

| 4.2     | Exter    | nal Interrupt Request Configuration Registers             |

|         | 4.2.1    | External Interrupt Trigger Event Register 0 (CFG_EITE0)64 |

|         | 4.2.2    | External Interrupt Trigger Event Register 1 (CFG_EITE1)64 |

|         | 4.2.3    | External Interrupt Trigger Event Register (CFG_EITE2)65   |

| 4.3     | Peripl   | heral Clock Management Registers                          |

|         | 4.3.1    | Clock management in User Mode                             |

| 4.4     | BSPI     | and UART Management in Emulation Mode                     |

|         | 4.4.1    | Emulation Serial Protection Register (CFG_ESPR)73         |

| 4.5     | CFG F    | Register Map                                              |

| 5 Cloc  | k Tree M | Мар                                                       |

| 6 I/O F | PORTS .  |                                                           |

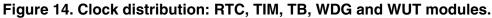

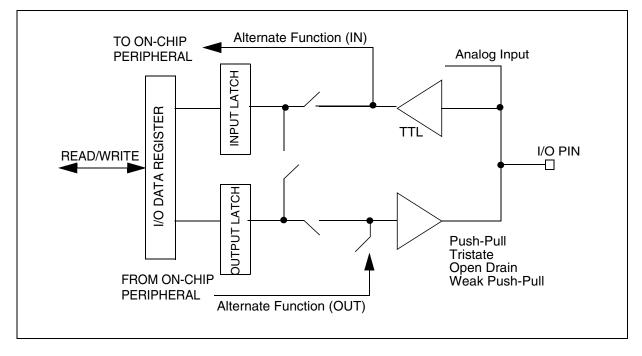

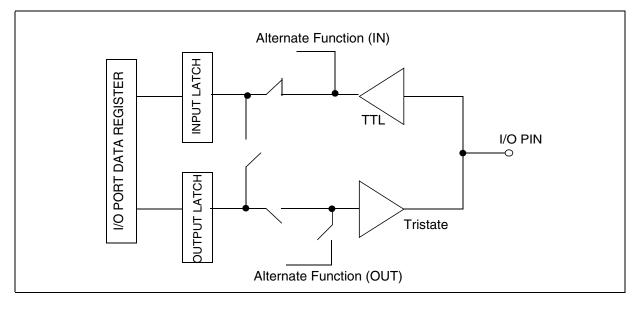

| 6.1     |          | tional Description                                        |

|         | 6.1.1    | Input Configuration                                       |

|         | 6.1.2    | Input Pull Up/Pull Down Configuration                     |

|         | 6.1.3    | Output Configuration                                      |

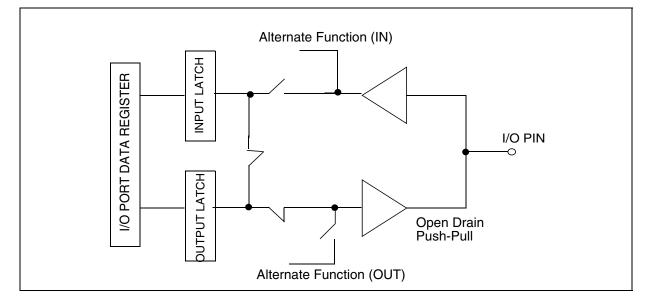

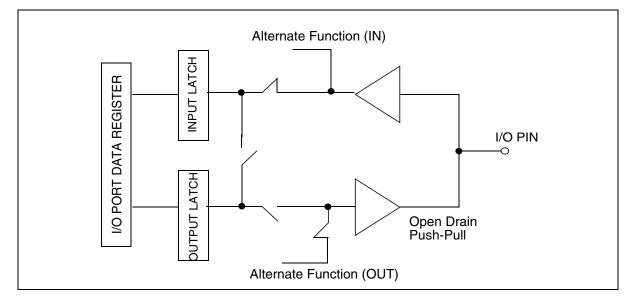

|         | 6.1.4    | Alternate Function Configuration                          |

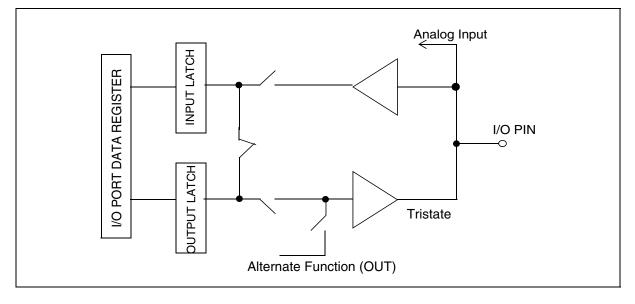

|         | 6.1.5    | High impedance-Analog Input Configuration                 |

| 6.2     | -        | ster Description                                          |

|         | 6.2.1    | I/O Port Register Map                                     |

|         |          | S                                                         |

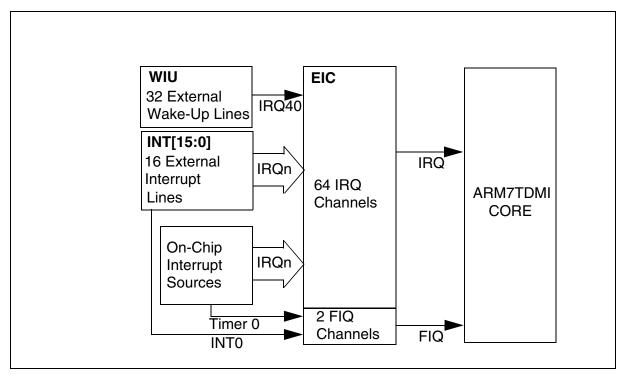

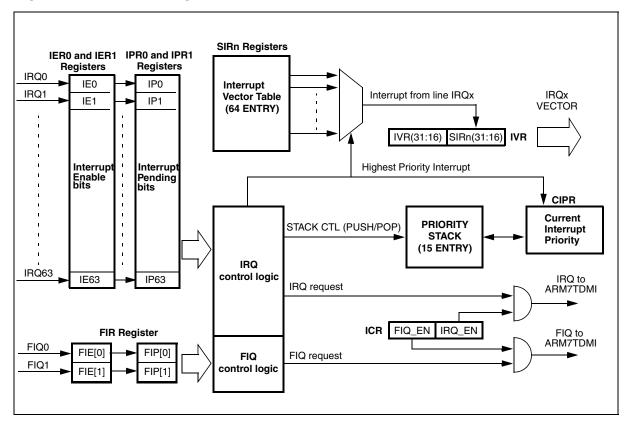

| 7.1     |          | nced Interrupt Controller (EIC)87                         |

|         | 7.1.1    | IRQ Interrupt Vector Table                                |

|         | 7.1.2    | FIQ Interrupt Vector Table                                |

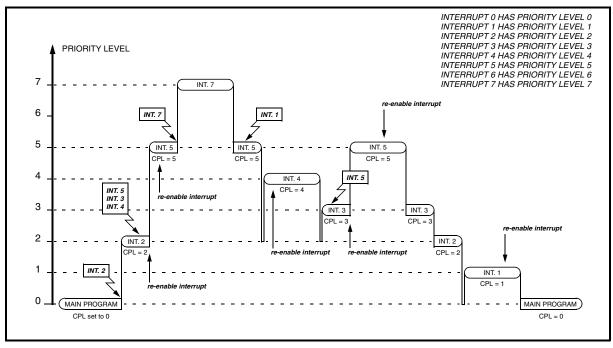

|         | 7.1.3    | IRQ Interrupt Structure                                   |

|         | 7.1.4    | Priority Decoder                                          |

|         | 7.1.5    | Finite State Machine                                      |

|         | 7.1.6    | Stack                                                     |

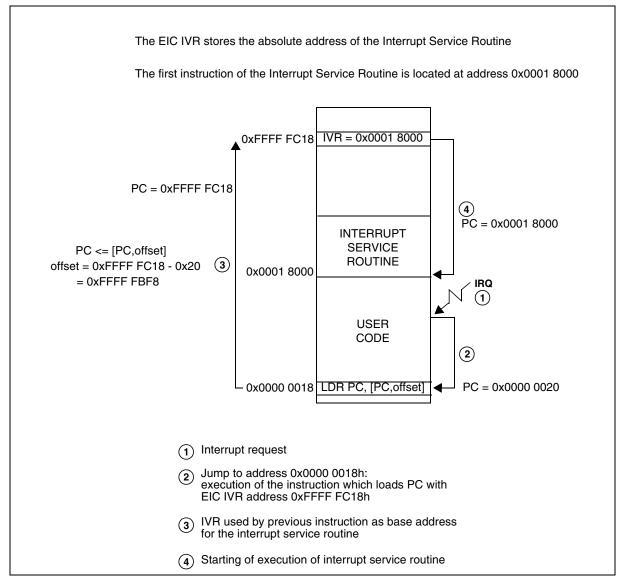

|         | 7.1.7    | EIC Interrupt Vectoring                                   |

|         | 7.1.8    | EIC IRQ notes                                             |

| 7.2     |          | nechanism                                                 |

| 7.3     | •        | ster Programming                                          |

| 7.4     |          | cation note                                               |

|         |          | Avoiding LR_sys and r5 registers content loss             |

|         | 7.4.2    | Hints about subroutines used inside ISRs101               |

\_

| 7.5          | Interr | rupt latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 102 |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.6          |        | ster Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|              | 7.6.1  | Interrupt Control Register (EIC_ICR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 103 |

|              | 7.6.2  | Current Interrupt Channel Register (EIC_CICR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104 |

|              | 7.6.3  | Current Interrupt Priority Register (EIC_CIPR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 105 |

|              | 7.6.4  | Fast Interrupt Enable Register (EIC_FIER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 106 |

|              | 7.6.5  | Fast Interrupt Pending Register (EIC_FIPR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108 |

|              | 7.6.6  | Interrupt Vector Register (EIC_IVR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 108 |

|              | 7.6.7  | Fast Interrupt Register (EIC_FIR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|              | 7.6.8  | Interrupt Enable Register 0 (EIC_IER0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 111 |

|              | 7.6.9  | Interrupt Enable Register 1 (EIC_IER1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|              | 7.6.10 | Interrupt Pending Register 0 (EIC_IPR0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 113 |

|              | 7.6.11 | Interrupt Pending Register 1 (EIC_IPR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|              |        | Source Interrupt Registers - Channel n (EIC_SIRn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 7.7          |        | Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 7.8          |        | nal Interrupt Pins INT[15:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|              | 7.8.1  | Edge-Triggered External Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|              | 7.8.2  | Level-Triggered External Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

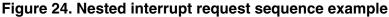

| 7.9          |        | e-Up Interrupt Unit (WIU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|              | 7.9.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|              | 7.9.2  | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|              | 7.9.3  | Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|              | 7.9.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

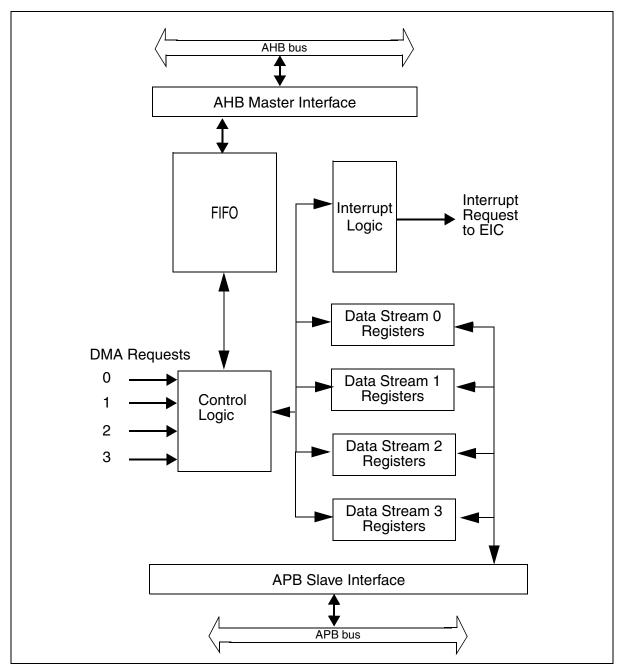

|              |        | ROLLER (DMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 8.1          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 8.2          |        | Controller Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.3          |        | Request Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 8.4          |        | tional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

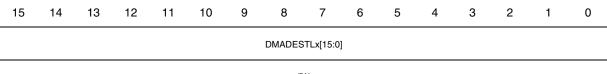

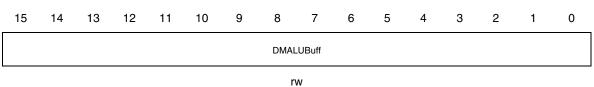

| 8.5          | •      | ster Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 8.6<br>9 NAT |        | Register Map    Sandard S<br>Sandard Sandard S |     |

| 9.1          |        | ster description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 5.1          | 9.1.1  | Time-Out Register (ARB_TOR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|              | 9.1.2  | Priority Register (ARB_PRIOR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|              | 9.1.3  | Control Register (ARB_CTLR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

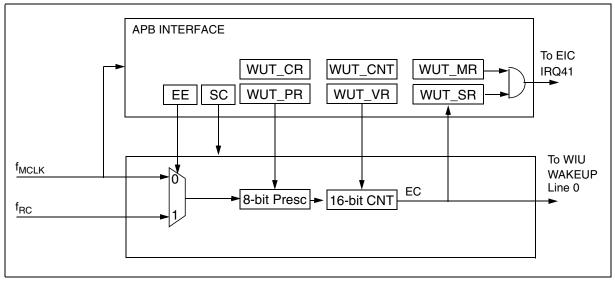

| 10 WA        |        | TIMER (WUT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|              |        | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|              |        | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |