### **Errata**

Title & Document Type: 16510A Front Panel Reference

Manual Part Number: 16510-90902

Revision Date: January 1988

### **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

### **About this Manual**

We've added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.

### **Support for Your Product**

Agilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:

### www.tm.agilent.com

Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.

# Front-Panel Operation Reference

HP 16510A Logic Analyzer Module

for the HP 16500A Logic Analysis System

© Copyright Hewlett Packard Company 1988

Manual Set Part Number 16510-90902 Microfiche Part Number 16510-90802

Printed in U.S.A January 1988

**Printing History**

First Edition - January 1988

Printed in U.S.A.

### **Product Warranty**

This Hewlett-Packard product has a warranty against defects in material and workmanship for a period of one year from date of shipment. During warranty period, Hewlett-Packard Company will, at its option, either repair or replace products that prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by Hewlett-Packard. However, warranty service for products installed by Hewlett-Packard and certain other products designated by Hewlett-Packard will be performed at the Buyer's facility at no charge within the Hewlett-Packard service travel area. Outside Hewlett-Packard service travel areas, warranty service will be performed at the Buyer's facility only upon Hewlett-Packard's prior agreement and the Buyer shall pay Hewlett-Packard's round trip travel expenses.

For products returned to Hewlett-Packard for warranty service, the Buyer shall prepay shipping charges to Hewlett-Packard and Hewlett-Packard shall pay shipping charges to return the product to the Buyer. However, the Buyer shall pay all shipping charges, duties, and taxes for products returned to Hewlett-Packard from another country.

Hewlett-Packard warrants that its software and firmware designated by Hewlett- Packard for use with an instrument will execute its programming instructions when properly installed on that instrument. Hewlett-Packard does not warrant that the operation of the instrument, software, or firmware will be uninterrupted or error free.

#### Limitation of Warranty

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software, or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED.

HEWLETT-PACKARD SPECIFICALLY DISCLAIMS THE IMPLIED

WARRANTIES OR MERCHANTABILITY AND FITNESS FOR A

PARTICULAR PURPOSE.

### **Exclusive Remedies**

THE REMEDIES PROVIDED HEREIN ARE THE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HEWLETT-PACKARD SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### Assistance

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

### Certification

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

### Safety

This product has been designed and tested according to International Safety Requirements. To ensure safe operation and to keep the product safe, the information, cautions, and warnings in this manual must be heeded.

### **Table of Contents**

### Introduction

## Chapter 1:

### **General Information**

- 1-1 Logic Analyzer Description

- 1-1 User Interface

- 1-2 Configuration Capabilities

- 1-3 Key Features

- 1-3 Accessories Supplied

- 1-4 Available Accessories

## Chapter 2:

### **Probing**

- 2-1 Introduction

- 2-1 Probing Options

- 2-1 The HP 10320C User-Definable Interface

- 2-2 The HP 10269C General Purpose Probe Interface

- 2-3 General Purpose Probing

- 2-3 The Termination Adapter

- 2-4 The HP 16510A Probing System

- 2-4 Probes and Probe Pods

- 2-4 Probe Pod Assembly

- 2-5 Probe Cable

- 2-5 Probes

- 2-6 Grabbers

- 2-6 Pod Grounds

- 2-7 Probe Grounds

- 2-8 Signal Line Loading

- 2-8 Maximum Probe Input Voltage

- 2-8 Pod Thresholds

- 2-8 Connecting the Logic Analyzer to the Target System

- 2-9 Connecting the Probe Cables to the Logic Analyzer

- 2-9 Connecting the Pods to the Probe Cable

- 2-10 Disconnecting the Probes from the Pods

- 2-11 Connecting the Grabbers to the Probes

- 2-11 Connecting the Grabbers to the Test Points

- 2-12 Labeling Pods, Probes, and Cables

## Chapter 3:

### Using the Front-Panel Interface

- 3-1 Introduction

- 3-1 Using the Mouse

- 3-2 How to Select Menus

- 3-3 How to Switch Between Analyzers

- 3-3 Returning to the System Configuration Menu

- 3-3 Pop-up Menus

- 3-3 How to Close Pop-up Menus

- 3-4 Toggle Fields

- 3-4 How to Select Options

- 3-6 How to Enter Numeric Data

- 3-7 How to Enter Alpha Data

- 3-9 How to Roll Data

- 3-11 Assignment/Specification Menus

- 3-11 Assigning Pod Bits to Labels

- 3-13 Specifying Patterns

- 3-14 Specifying Edges

### Chapter 4:

### Using the Menus

- 4-1 Introduction

- 4-1 Menu Maps

- 4-2 State/Timing Configuration Menu Map

- 4-3 Timing Format Menu Map

- 4-4 Timing Trace Menu Map

- 4-5 Timing Waveform Menu Map

- 4-7 State Format Menu Map

- 4-8 State Trace Menu Map

- 4-10 State Listing Menu Map

- 4-11 Mixed Display Menu Map

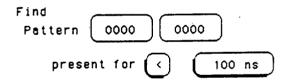

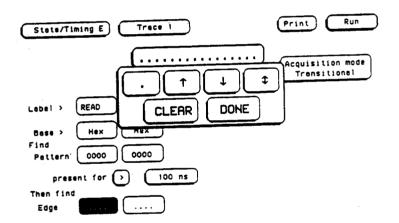

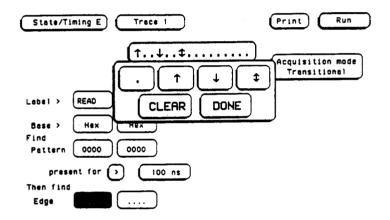

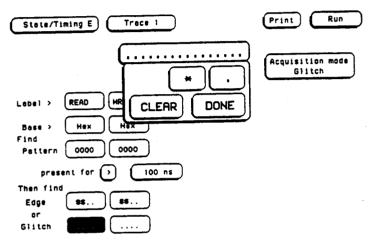

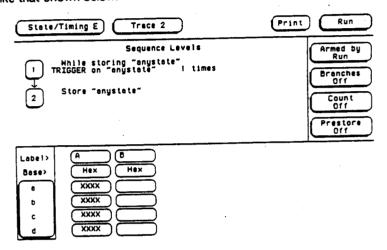

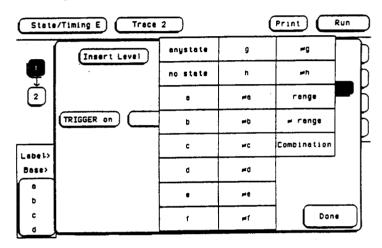

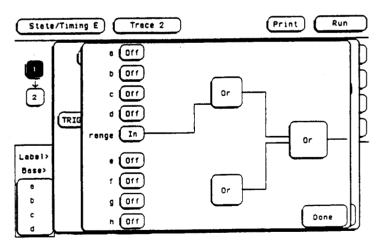

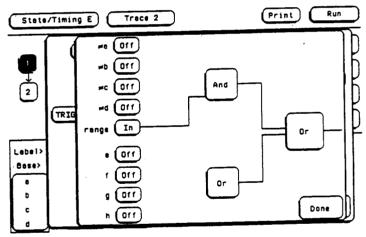

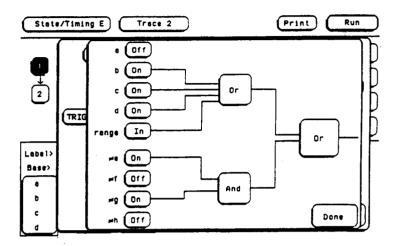

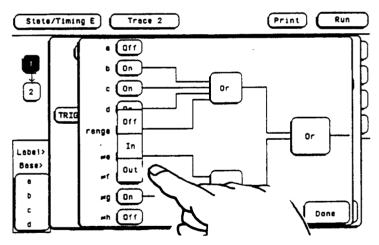

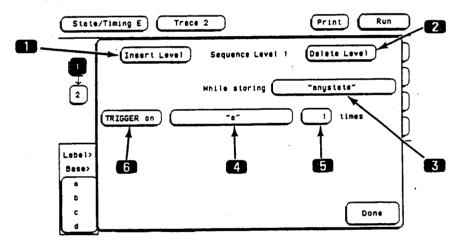

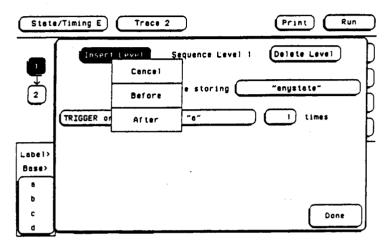

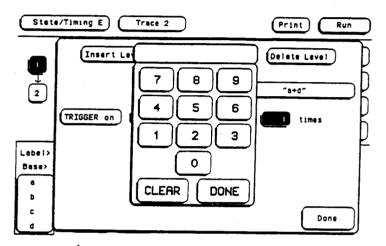

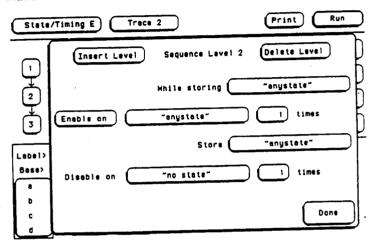

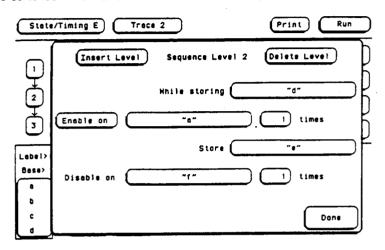

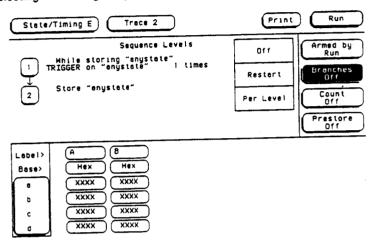

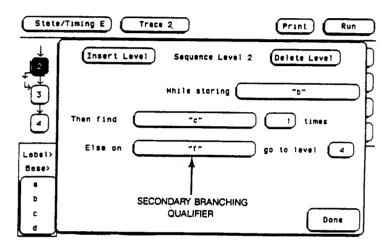

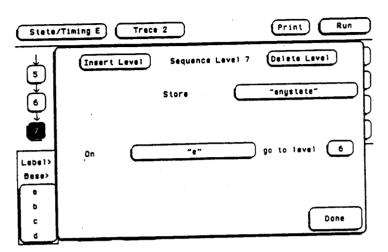

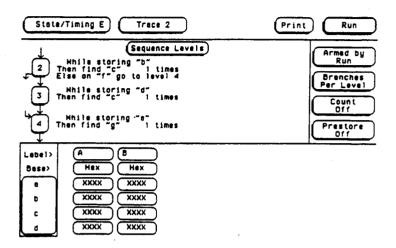

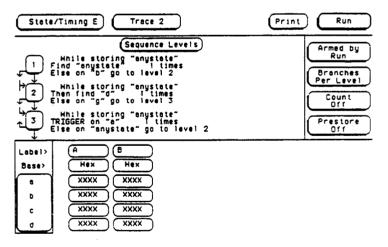

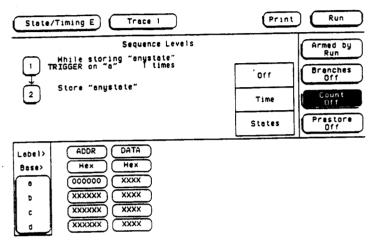

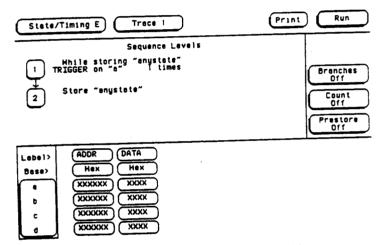

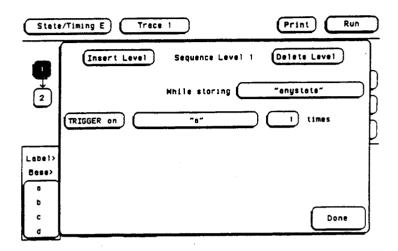

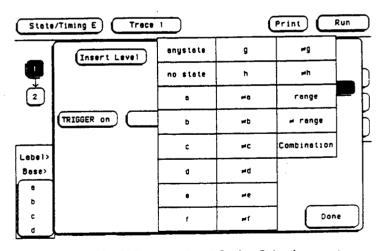

Menus 5-1 Introduction System Level Menu State/Timing Configuration Menu Name 5-2 5-3 Type 5-4 **Autoscale** 5-5 Pods 5-5 Print 5-6 Print Screen 5-6 Print All 5-7 Run 5-7 Sub-System Level Menus Timing and State Format Specification Menus 5-9 Timing and State Format Specification Menu Fields 5-9 Label 5-11 Polarity (Pol) 5-11 Bit Assignment 5-12 Pod Threshold 5-14 Specify Symbols 5-21 Clock 5-23 Pod Clock 5-27 Timing Trace Specification Menu 5-28 Timing Trace Specification Menu Fields 5-28 Run/Trace Mode 5-29 Armed By 5-30 **Acquisition Mode** 5-32 Label 5-33 Base 5-34 Find Pattern 5-37 Pattern Duration (present for \_\_\_\_\_) 5-39 Then Find Edge 5-43 State Trace Specification Menu 5-44 Sequence Levels 5-48 Insert Level 5-48 Delete Level 5-49 Storage Qualifier 5-49 **Branching Qualifier** 5-50 Occurrence Counter 5-50 Storage Macro

**Chapter 5:**

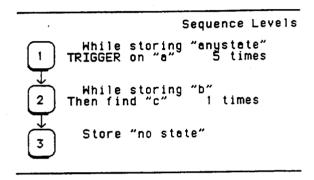

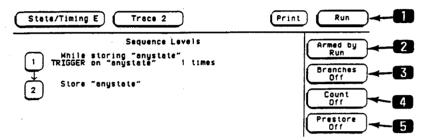

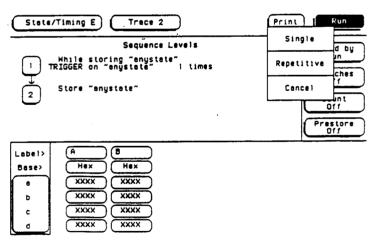

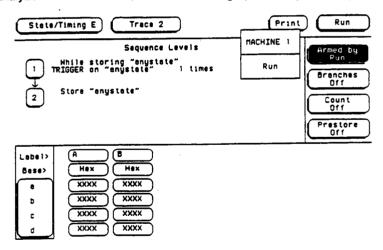

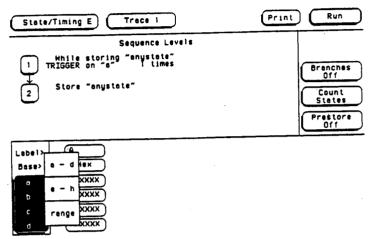

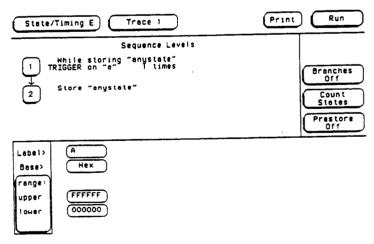

5-53 Reading the Sequence Level Display

5-55 Acquisition Fields

5-55 Run/Trace Mode

5-56 Armed By

5-57 Branches

5-61 Count

5-64 Prestore

5-65 Qualifier and Pattern Fields

5-65 Label

5-66 Base

5-67 Qualifier Field

5-68 Pattern Fields

## Chapter 6:

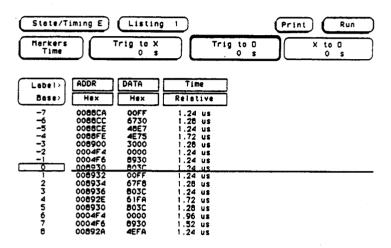

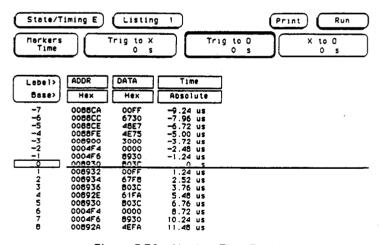

### Interpreting the Display

6-1 Introduction

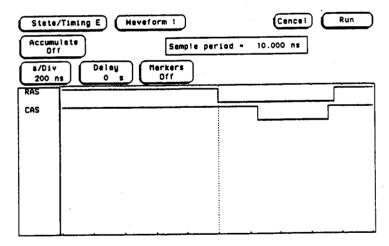

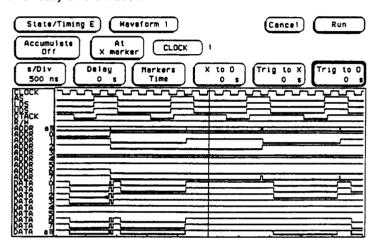

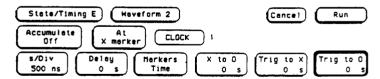

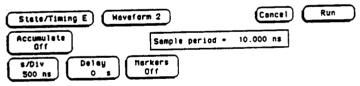

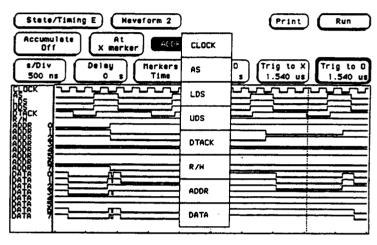

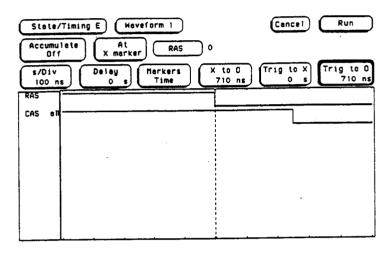

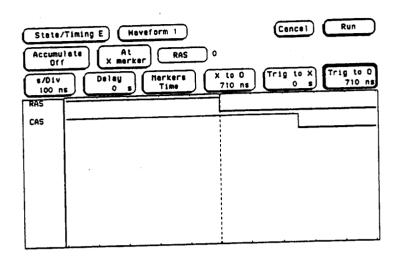

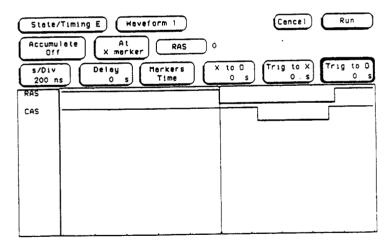

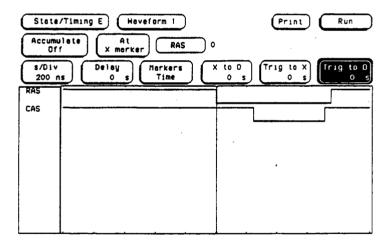

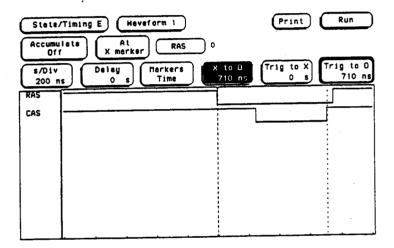

6-1 The Timing Waveforms Menu

6-2 Timing Waveforms Menu Fields

6-3 Markers (Timing)

6-3 Markers Off/Sample Period

6-3 Markers Time

6-5 Markers Pattern

6-6 Markers Statistics

6-6 Accumulate Mode

6-7 At\_\_\_ marker

6-8 s/Div (time per division) Field

6-9 Delay Field

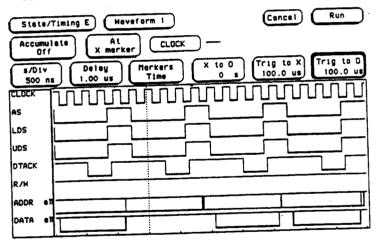

6-10 The State Listing Menu

6-12 State Listing Menu Fields

6-12 Markers (State)

6-13 Markers Off

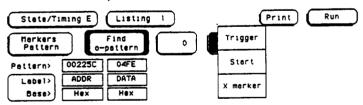

6-13 Markers Pattern

6-14 Markers Time

6-15 Markers Statistics

6-16 Timing/State Mixed Mode Display

6-17 State/State Mixed Mode Display

6-20 Time-Correlated Displays

### Chapter 7:

### Using the Timing Analyzer

- 7-1 Introduction

- 7-1 Problem Solving with the Timing Analyzer

- 7-2 What Am I Going to Measure?

- 7-2 How Do I Configure the Logic Analyzer?

- 7-4 Connecting the Probes

- 7-4 Activity Indicators

- 7-4 Configuring the Timing Analyzer

- 7-7 Specifying a Trigger Condition

- 7-8 Acquiring the Data

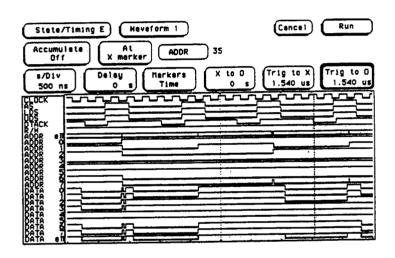

- 7-10 The Timing Waveform Menu

- 7-10 The Green and Yellow Dotted Lines

- 7-10 The Red Dotted Line

- 7-10 Configuring the Display

- 7-11 Display Resolution

- 7-12 Making The Measurement

- 7-13 Finding the Answer

- 7-14 Summary

## Chapter 8:

### Using the State Analyzer

- 8-1 Introduction

- 8-1 Problem Solving with the State Analyzer

- 8-2 What Am I Going to Measure?

- 8-3 How Do I Configure the Logic Analyzer?

- 8-5 Connecting the Probes

- 8-5 Activity Indicators

- 8-6 Configuring the State Analyzer

- 8-10 Specifying the J Clock

- 8-13 Specifying a Trigger Condition

- 8-16 Acquiring the Data

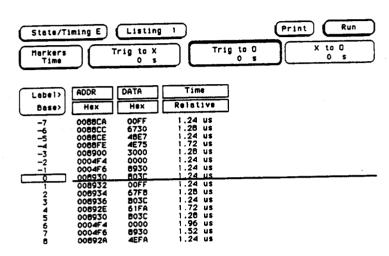

- 8-19 The State Listing

- 8-20 Finding the Answer

- 8-22 Summary

### **Chapter 9:**

### Using the Timing/State Analyzer

- 9-1 Introduction

- 9-2 Problem Solving with the Timing Analyzer

- 9-2 What Am I Going to Measure?

- 9-3 How Do I Configure the Logic Analyzer?

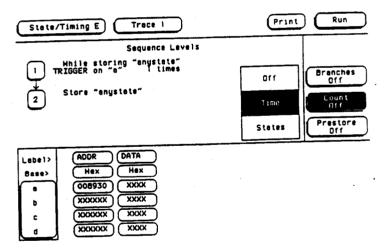

- 9-4 Configuring the State Analyzer

- 9-5 Connecting the Probes

- 9-5 Acquiring the Data

- 9-5 Finding the Problem

- 9-7 What Additional Measruements Must I Make?

- 9-8 How Do I Re-configure the Logic Analyzer?

- 9-8 Connecting the Timing Analyzer Probes

- 9-9 Configuring the Timing Analyzer

- 9-10 Setting the Timing Analyzer Trigger

- 9-11 Time Correlating the Data

- 9-12 The Timing Waveform Menu

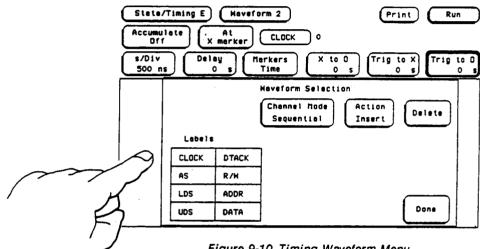

- 9-12 Displaying the Waveforms

- 9-15 Overlapping Timing Waveforms

- 9-17 Re-acquiring the Data

- 9-18 Finding the Answer

- 9-18 Summary

## Chapter 10:

### Using a Printer

- 10-1 Setting Printer Configuration

- 10-1 Printing Options

- 10-2 Printing On-Screen Data

- 10-2 Printing Entire State Listing

### Chapter 11:

### **Microprocessor Specific Measurements**

- 11-1 Introduction

- 11-1 Microprocessor Measurements

- 11-2 Microprocessors Supported by Preprocessors

- 11-3 Z80

- 11-4 NSC 800

- 11-5 8085

- 11-6 8086 or 8088

- 11-7 80186 or 80188

- 11-8 80286

- 11-9 80386

- 11-10 6800 or 6802

- 11-11 6809 or 6809E

- 11-12 68008

- 11-13 68000 or 68010 (64-pin DIP)

- 11-14 68000 or 68010 (68-pin PGA)

- 11-15 68020

- 11-16 Loading Inverse Assembler Files

- 11-16 Selecting the Correct File

- 11-16 Loading the Desired File

- 11-17 Connecting the Logic Analyzer Probes

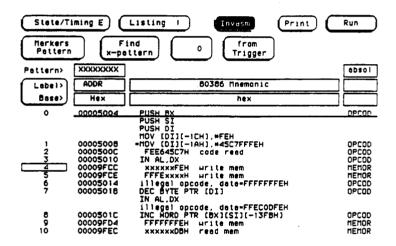

- 11-17 How to Display Inverse Assembled Data

## Appendix A:

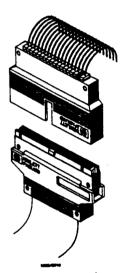

### Installing New Logic Analyzer Boards into the Mainframe

- A-1 Introduction

- A-1 Initial Inspection

- A-1 Power Requirements

- A-1 Probe Cable Installation

- A-2 Installation

- A-2 Module Installation

- A-2 Installation Considerations

- A-3 Procedure

- A-6 Operating Environment

- A-6 Storage

- A-7 Packaging

- A-7 Tagging for Service

Appendix B:

**Error Messages**

B-1 Error Messages

Appendix C:

**Specifications and Characteristics**

C-1 Specifications

C-3 Characteristics

C-6 General Characteristics

Index

### Introduction

## About this manual...

Welcome to the new generation of HP logic analyzers! The HP 16500A Logic Analysis System has been designed to be easier to use than any Hewlett-Packard logic analyzer before. In addition, because of its configurable architecture, it can easily be tailored to your specific logic design and debug needs.

The user interface of the HP 16500A was designed for the most intuitive operation possible. Pop-up windows and color graphics help lead you through setups and measurements so you won't have to memorize a lot of steps. As you read this manual and the other manuals about the mainframe and acquisition modules, you will see just how easy the HP 16500A is to use.

This logic analyzer reference manual is divided as follows:

- Chapters 1 through 4 contain introductory information about the logic analyzer and the accessories supplied with the HP 16510A.

They contain information that will familiarize you with the user-interface and menus.

- Chapters 5 and 6 describe all the menus of the logic analyzer.

- Chapters 7 through Appendix C discuss other logic analyzer functions such as making basic measurements, printing, specifications, etc.

If you aren't familiar with the HP 16510A Logic Analyzer, we suggest you read the HP 16510A Getting Started Guide. This guide contains tutorial examples on the basic functions of the logic analyzer.

If you're new to logic analyzers...or just need a refresher, we think you'll find *Feeling Comfortable with Logic Analyzers* valuable reading. It will eliminate any misconceptions or confusion you may have about their application, and will show you how to get the most out of your new logic analyzer.

. .

•

## **General Information**

## Logic Analyzer Description

The HP 16510A logic analyzer is part of a new generation of general purpose logic analyzers with improved features to accommodate next generation design tasks.

The 80-channel HP 16510A logic analyzer is capable of 100 MHz timing and 25 MHz state analysis on all channels.

This analyzer is designed as a stand alone instrument for use by digital and microprocessor hardware designers. The HP 16500A mainframe has HP-IB and RS-232C interfaces for hardcopy printouts and control by a host computer.

### **User Interface**

The user interface is easier to use than in previous generations for first- time and casual users as well as experienced logic analyzer users.

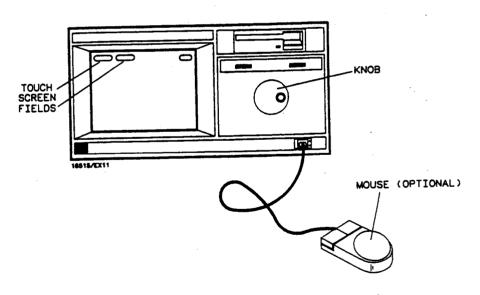

The HP 16500A has three user interface devices: the knob on the front panel, the touchscreen, and the optional mouse.

Figure 1-1. HP 16500A User Interfaces

The knob on the front panel is used to move the cursor on certain menus, increment or decrement numeric fields, and to roll the display.

The touchscreen fields can be selected by touch or with the optional mouse. To activate a touchscreen field by touch, touch or press the field (the dark blue box) on the display with your finger until the field changes color. Then remove your finger from the screen to activate your selection.

To activate a field with the optional mouse, position the cursor (+) of the mouse over the desired field and press the button on the upper-left corner of the mouse.

The user interfaces are discussed in more detail in the *HP 16500A Reference* manual.

## Configuration Capabilities

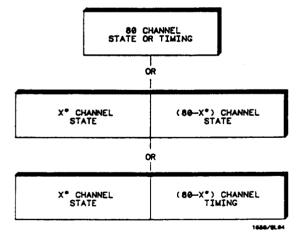

The HP 16510A can be configured as two independent machines (analyzers) maximum at one time or two machines interactively. The combinations are:

- Up to 80 channels state

- Up to 80 channels timing

- Two state machines with multiples of 16 channels per machine with a combined maximum of 80 channels

- One state and one timing machine with multiples of 16 channels per machine with a combined maximum of 80 channels

Figure 1-1. HP 16510A Configuration Capabilities

\* multiples of 16 channels

### **Key Features**

Two 3.5-Inch disc drives are integral to the instrument for storing logic analyzer configurations and acquired data. The disc drive also provides a way of loading inverse assembly configuration files into the logic analyzer for configuring ease.

Additional key features of both models include:

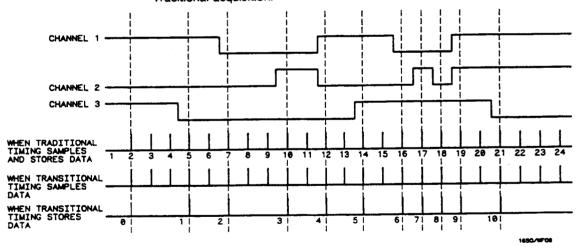

- Transitional timing for extended timing analyzer memory

- Lightweight passive probes for easy hook-up

- All channels can be used for state or timing at the maximum sample rate

- HP-IB and RS-232C interface for programming and printer dumps

- An external trigger BNC connector

- Efficient package size

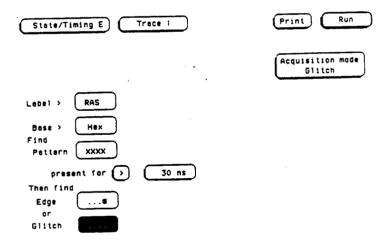

- Transitional or glitch timing modes

- 1k-deep memory on all channels

- Glitch detection

- Marker measurements

- Triggering and pattern qualification

- Overlapping of timing waveforms

- Eight sequence levels

- Eight pattern recognizers

- One range recognizer

- Time and number-of-states tagging

- Pre-store

- Auto-scale

- Programmability

- Cross-domain triggering

- Interactive measurements

- Mixed-mode display

- Oscilloscope type controls in the timing analyzer

## Accessories Supplied

Table 1 lists the accessories supplied with your HP16510A. If any of these accessories were missing when you received the logic analyzer from the factory, contact your nearest Hewlett-Packard office. If you need additional accessories, refer to the Accessories for the HP 1650A/HP 1651A and HP 16500A Logic Analyzers data sheet.

Table 1-1. Accessories

| Accessory                                  | HP Part No. | Quantity |

|--------------------------------------------|-------------|----------|

| Probe assemblies                           | 01650-61608 | 5        |

| Probe Cables (25MHz State)                 | 16510-61601 | 3        |

| Probe cables                               | 16510-61602 | 2        |

| Grabbers (Note 1)                          | 5959-0288   | 100      |

| Ground leads (long)                        | 01650-82102 | 5        |

| Ground leads (short)                       | 01650-82103 | 10       |

| RS-232C Loop back adapter                  | 01650-63202 | 1        |

| Probe and probe cable numbering label card | 01650-94303 | 1        |

| Operating system disc                      | 16510-13501 | 2        |

| Operating and<br>Programming manual set    | 16510-90902 | 1        |

| Service manual                             | 16510-90901 | 1        |

#### Notes:

1. Package of 20 per part number.

### Available Accessories

In addition to the accessories supplied, there are a number of accessories available that will make your measurement tasks easier and more accurate. You will find these listed in the Accessories for the HP 1650A/HP 1651A and HP 16510A Logic Analyzers.

### **Probing**

### Introduction

This chapter contains a description of the probing system of the HP 16510A logic analyzer. It also contains the information you need to connect the probe system components to each other, to the logic analyzer, and to the system under test.

### **Probing Options**

You can connect the HP 16510A logic analyzers to your system under test in one of four ways:

- HP 10320C User-definable Interface (optional)

- HP 10269C with microprocessor specific modules (optional)

- the standard HP 16510A probes (general purpose probing)

- direct connection to a 20-pin 3M<sup>®</sup> Series type header connector using the optional termination adapter (HP Part No. 01650-63201).

### The HP 10320C User-Definable Interface

The optional HP 10320C User-definable Interface module combined with the HP 10269C General Purpose Probe Interface (optional) allows you to connect the HP 16510A logic analyzer to your target system. The HP 10320C includes a breadboard (HP 64651B) which you custom wire for your system.

Also available as an option that you can use with the HP 10320C is the HP 10321A Microprocessor Interface Kit. This kit includes sockets, bypass capacitors, a fuse for power distribution, and wire-wrap headers to simplify wiring of your interface when you need active devices to support the connection requirements of your system.

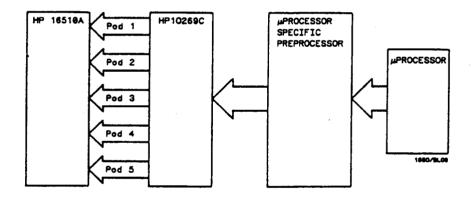

The HP 10269C General Purpose Probe Interface Instead of connecting the probe tips directly to the signal lines, you may use the HP 10269C General Purpose Probe interface (optional). This allows you to connect the probe cables (without the probes) to connectors on the interface. When the appropriate preprocessor is installed in the interface, you will have a direct connection between the logic analyzer and the microprocessor under test.

There are a number of microprocessor specific preprocessors available as optional accessories which are listed in the *Accessories for the HP 1650/HP1651A* and *HP 16500A Logic Analyzers* data sheet. Chapter 11 of this manual also introduces you to preprocessors and inverse assemblers.

Figure 2-1. HP 10269C with Preprocessor

### General Purpose Probing

General purpose probing involves connecting the probes directly to your target system without using the interface. General purpose probing does not limit you to specific hook-up schemes as the probe interface does.

## The Termination Adapter

The optional termination adapter (HP Part No. 01650-63201) allows you to connect the probe cables directly to test ports on your target system without the probes. However, since the probes contain the proper termination for the logic analyzer inputs, a termination must be provided when you aren't using the probes. The termination adapter provides this termination.

The termination adapter is designed to connect to a 20 (2x10) position, 4-wall, low profile header connector, 3M<sup>®</sup> Series 3592 or equivalent.

You connect the termination adapter to the probe cable in place of the pod connector and connect the other end of the adapter directly to your test port.

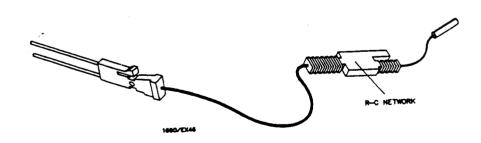

Figure 2-2. Termination Adapter

## The HP 16510A Probing System

The standard HP 16510A probing system consists of probes, pods, probe cable and grabbers. This system is passive (has no active circuits at the outer end of the cable). This means that the pods and probes are smaller and lighter, making them easier to use.

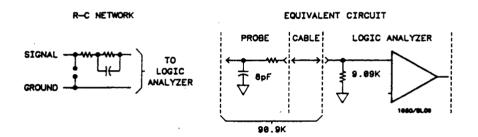

The passive probe system is similar to the probe system used with high frequency oscilloscopes. It consists of a series R-C network (90.9 k $\Omega$  in parallel with 8 pF) at the probe tip, and a shielded resistive transmission line.

The advantages of this system are:

- 2 ns risetime with ± 5% perturbations

- 8 pF input capacitance at the probe tip

- signal ground at the probe tip for higher speed timing signals

- inexpensive removable probe tip assemblies

## Probes and Probe Pods

Probes and probe pods allow you to connect the logic analyzer to your system under test without the HP 10269C Probe Interface. This general purpose probing is useful for discrete digital circuits. Each probe and pod assembly contains 16 data channels, one clock channel, and pod ground.

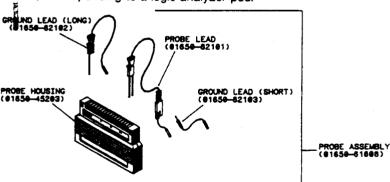

### **Probe Pod Assembly**

The pods, as they will be referred to for consistency, are the probe housings (as shown below) that group 16 data, one clock line, and grounds, corresponding to a logic analyzer pod.

Figure 2-3. Probe Assembly 1850/EX44

**Probe Cable**

The probe pod cable contains 17 signal lines, 34 chassis ground lines and two power lines that is woven together. It is 4.5 feet long.

CAUTION

The probe grounds are chassis (earth) grounds, not "floating" grounds.

Each cable is capable of carrying 0.60 amps for preprocessor power. DO NOT exceed this 0.60 amps per cable or the cable will be damaged. Also, the maximum power available from the logic analyzer (all cables) is 2 amps at 5 volts.

### Note

The preprocessor power source is fused. The fuse is located inside the HP 16500A on the logic analyzer card. If a preprocessor appears to be malfunctioning, refer to the HP 16510A service manual for instructions on checking this fuse.

The probe cable connects the logic analyzer to the pods, termination adapter, or the HP 10269C General Purpose Probe Interface.

Probes

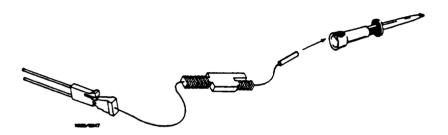

Each probe is a 12-inch twisted pair cable and is connected to the probe cable at the pod. One end of each probe has a probe tip assembly where the input R-C network is housed and a lead that connects to the target system. The other end of the probe has a two-pin connector that connects to the probe cable.

Figure 2-4. Probe Cable

You can connect the probe directly to the test pins on your target system. To do so, the pins must be 0.63 mm (0.025 in.) square pins or round pins with a diameter of between 0.66 mm (0.026 in.) and 0.84 mm (0.33 in.).

Each probe has an input impedance of 100  $k\Omega$  in parallel with approximately 8 pF.

Figure 2-5. Probe Input Circuit

Probes can be grounded in one of two ways: a common pod ground and a probe ground for each probe.

### Grabbers

The grabbers have a hook that fits around IC pins and component leads and connects to the probes and the ground leads. The grabbers have been designed to fit on adjacent IC pins.

#### **Pod Grounds**

Each pod is grounded by a pod ground lead that should always be used. You can connect the ground lead directly to a ground pin on your target system or use a grabber. The grabber connects to the ground lead the same way it connects to the probe lead.

To connect the ground lead to grounded pins on your target system, the pins must be 0.63 mm (0.025 in.) square pins or round pins with a diameter of 0.66 mm (0.026 in.) to 0.84 (0.033 in.).

### **Probe Grounds**

You can ground the probes in one of two ways. You can ground the probes with the pod ground only; however, the ground path won't be the same length as the signal path through the probe. If your probe ground path must be the same as your signal path, use the short ground lead (probe ground). The probe ground lead connects to the molded probe body via a pin and socket. You can then use a grabber or grounded pins on your target system the same way as the pod ground.

Figure 2-6. Probe Grounds

### Note

For improved signal fidelity, use a probe ground for every four probes in addition to the pod ground.

If you need additional probe ground leads, order HP part number 01650-82103 from your nearest Hewlett Packard sales office.

Signal Line Loading Any signal line you intend to probe must be able to supply a minimum of 600 mV to the probe tip, which has an input impedance of 100  $k\Omega$ shunted by 8 pF. If the signal line is incapable of this, you will not only have an incorrect measurement but the system under test may also malfunction.

### Maximum Probe Input Voltage

The maximum input voltage of each probe is ± 40 volts peak.

### Pod Thresholds

There are two preset thresholds and a user-definable pod threshold for each pod. The two preset thresholds are ECL (-1.3 V) and TTL (+1.6 V). The user-definable threshold can be set anywhere between - 9.9 volts and +9.9 volts in 0.1 volt increments.

The pod thresholds of pods 1, 2, and 3 can be set independently. The pod thresholds of pods 4 and 5 are slaved together; therefore, when you set the threshold on either pod 4 or 5, both thresholds will be the same.

### Connecting the Logic Analyzer to the Target System

There are four ways you can connect the logic analyzer to your target system as previously mentioned at the beginning of this chapter: the probes (general purpose probing); the HP 10320C User-definable Interface; the HP 10269C with microprocessor specific preprocessor modules; and direct connection to a 20 pin 3M<sup>®</sup> Series type header connector using the optional termination adapter (HP Part No. 01650-63201).

Since the probe interface hook-ups are microprocessor specific, they will be explained in their respective operating notes. The rest of this chapter is dedicated to general purpose probing with the HP 16510A probes.

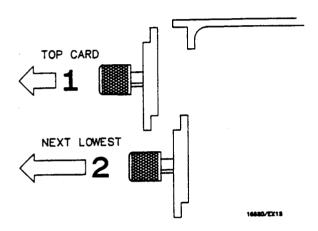

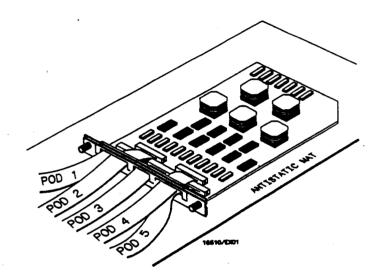

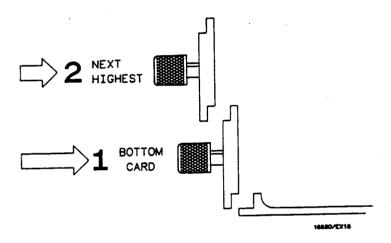

# Connecting the Probe Cables to the Logic Analyzer

The probe cables are installed in the Logic Analyzer module at the factory. The cable for pod 1 is the far left cable (rear view). Cables 2 through 5 follow cable 1 consecutively from left to right. If there is a need to install or replace the cables refer the *HP 16510A Service Manual*, Section VI.

# Connecting the Pods to the Probe Cable

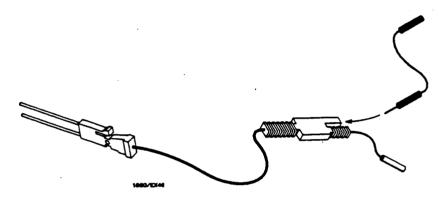

The pods of the HP 16510A differ from other logic analyzers in that they are passive (have no active circuits at the outer end of the cable). The pods, as they will be referred to for consistency, are the connector bodies (as shown below) that the probes are installed in when you receive your logic analyzer.

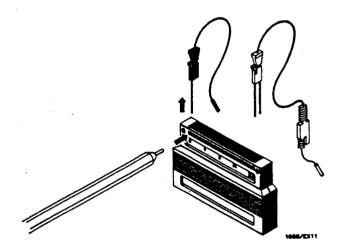

Figure 2-7. Connecting Pods to Probe Cables

To connect a pod to a cable, you align the key on the cable connector with the slot on the pod connector and push them together.

# Disconnecting the Probes from the Pods

The probes are shipped already installed in the pods. However, you can disconnect any un-used probes from any of the pods. This keeps the un-used probes from getting in your way.

To disconnect a probe, insert the tip of a ball-point pen in the latch opening and push while gently pulling the probe out of the pod connector as shown below.

Figure 2-8. Disconnecting Probes from Pods

You connect the probes to the pods by inserting the double pin end of the probe into the pod. The probes and pod connector body are both keyed (beveled) so that they will fit together only one way. Connecting the Grabbers to the Probes

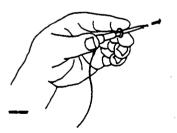

You connect the grabbers to the probes by slipping the connector at the end of the probe onto the recessed pin in the side of the grabber. If you need to use grabbers for either the pod or the probe grounds, connect them to the ground leads the same way you connect them to the probes.

Figure 2-9. Connecting Grabbers to Probes

Connecting the Grabbers to the Test Points

The grabbers have a hook that fits around IC pins and component leads. You connect the grabber by pushing the rear of the grabber to expose the hook, hooking the lead and releasing your thumb as shown below.

Figure 2-10. Connecting Grabbers to Test Points

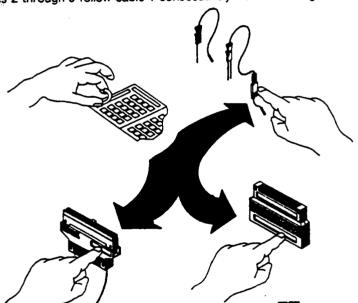

### Labeling Pods, Probes, and Cables

So you can find the pods and probes you want to connect to your target system, you need to be able to quickly identify them. Included with your logic analyzer are self-adhesive labels for each pod, cable and probe.

They come in sets. Each set has labels for the end of the cable-- a label for the pod connector body, a label for the clock probe and 16 labels for each of the channels.

One end of each cable is already connected to the HP 16510A logic analyzer module. The cable for pod 1 is the far left cable (rear view). Cables 2 through 5 follow cable 1 consecutively from left to right.

Figure 2-11. Labeling Pods, Probes, and Cables

## Using the Front-Panel Interface

### Introduction

This chapter gives you an overview of how to use the front-panel interface.

The front-panel user interface is merely accessing the many menus and using the convenient touch-screen to move around the menu tree. The front panel itself consists of a disc drive, the knob, power switch, display, and receptacle for connecting the optional mouse.

The user interface allows you to configure the logic analyzer and each analyzer (machine) within the logic analyzer. It also displays acquired data and measurement results.

Using the front-panel interface is a basic process of:

- · Selecting the desired menu

- · Selecting a desired field within a menu

- Displaying the options or current variable data associated with the desired field

- Selecting the desired option or entering new data (editing current data) in the field

- Starting and Stopping data acquisition when the logic analyzer is connected and configured

### Using the Mouse

Everything that can be done with the touch screen and knob on the HP 16500A can also be done with the optional mouse. The mouse plugs into the connector in the lower right of the front panel. As soon as the mouse is plugged in, it is active.

When the mouse is plugged in, a white cursor (cross) appears on the screen. Moving the mouse causes the cursor to move. To "touch" a field with the mouse, move the cursor to the field and press the left button on the mouse.

To use the mouse to perform the functions of the front-panel knob, hold down the right button and move the mouse. When you release this button, the function returns to the cursor.

### How to Select Menus

Before you try to select one of the main menus, make sure the field in the upper left-hand corner is set to State/Timing E. If the HP 16500A is in System or Intermodule, touch that field and select State/Timing E when the pop-up appears.

#### Note

The field containing State/Timing (x) may have a different letter following State/Timing. Don't be alarmed. This letter merely tells you what card slot the State/Timing module is in.

To select the main menus touch the second field from the left at the top of the screen. A pop-up appears showing you the active menus. The menus are:

- Configuration

- Format 1, 2, or both

- Trace 1, 2, or both

- Waveform (Timing analyzer only)

- Listing (State analyzer only)

When the menu is displayed you can access the fields within the menus. The second field from the left in the upper left-hand corner always displays the current menu. To move around in the menu tree, you must always touch the field displaying the current menu and select a new menu when the pop-up appears.

The Configuration, Format, Trace, Waveform, and Listing menu fields provide access to their respective menus. All menus, subsystems, and fields in the entire logic analyzer are pop-ups that appear on top of the currently displayed menu.

If more than one analyzer (machine) is on, you see the selected menu of either analyzer 1 or analyzer 2 depending on what analyzer menu was last displayed or what you did in the State/Timing E Configuration menu.

To switch from one of these menus to another menu within the same analyzer (machine) touch the current field (i.e. Waveform), which is displayed in the field second from the left in the upper left corner and make a new selection.

### How to Switch Between Analyzers

You can switch between analyzers in any main menu by touching the field (second from the left in the upper left-hand corner). When the pop-up appears you can select the desired menu in the desired analyzer when both analyzers are on. One example of the options available when both analyzers (one state and one timing) are on are:

- Format 1

- Format 2

- Trace 1

- Trace 2

- Waveform (for Timing analyzer)

- Listing (for State analyzer)

Touch the field in the pop-up to enter the desired menu. You will immediately go to that menu.

# Returning to the System Configuration Menu

You can return to the System Configuration menu from any main logic analyzer menu. To return to the System Configuration menu. touch State/Timing E. When the pop-up appears, touch System. When the pop-up closes, System will be displayed in the upper left corner. If Configuration is not displayed in the field second from the left in the upper left corner, touch this field. When the pop-up appears, touch Configuration. You will now be in the System Configuration menu.

### Pop-up Menus

The pop-up menu is used exclusively in this logic analyzer. This gives you more flexibility to move through the menu tree and faster access to the individual subsystems.

To use the pop-ups when they appear, simply touch the field in the pop-up you want. The pop-up will immediately close and the menu you select will appear.

## How to Close Pop-up Menus

Some pop-up menus automatically close when you touch a desired field. After closing, the logic analyzer places your choice in the main menu field from which you opened the pop-up.

Other pop-up menus don't automatically close when you make your selection (i.e. alphanumeric keyboard). These menus have a **Done** option. To close the pop-up all you have to do is touch the **Done** field.

### **Toggle Fields**

Some fields will toggle between two options (i.e., off and on). When you touch one of these fields, the displayed option toggles to the other choice and no additional pop-up appears.

## How to Select Options

How to select options depends on what type of pop-up menu appears when you touch the field. When the pop-up appears, you will see a list of options. You select the option by touching the option field. In most cases the pop-up menu closes when you touch an option and the selected option will be displayed. However, in some pop-ups, selecting the option does not automatically close the pop-up. In this case the option **Done** is present.

There are also pop-up menus where each option within the pop-up menu has more than one option available. In these cases, when you touch that field, another pop-up, with options, will be superimposed on the original pop-up.

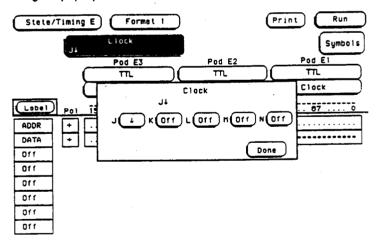

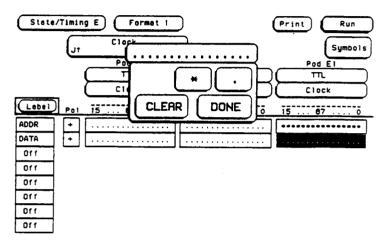

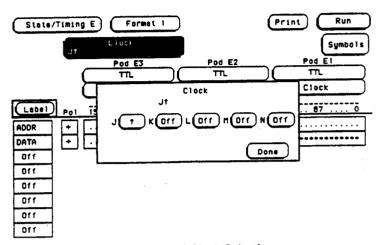

Figure 3-1. State Clock Pop-up Menu

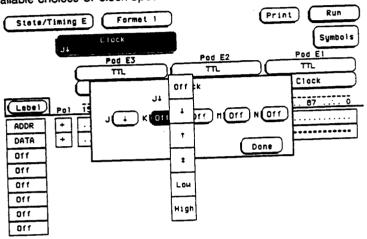

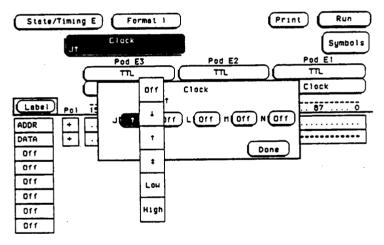

An example of one of these is the clock field in the State Format Specification menu. When you select the clock field in this menu it will pop-up and show you all five clocks (J, K, L, M, and N). When you select one of the five clocks, another pop-up appears showing you the available choices of clock specifications.

Figure 3-2. State Clock Pop-up with K Pop-up Open

When you touch one of these the pop-up will close, however, the original clock pop-up still remains open. When you are finished specifying the choices for the clocks, you close the original pop-up menu by touching **Done**.

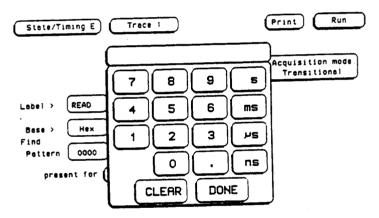

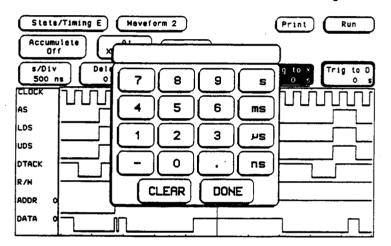

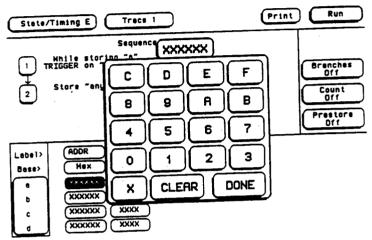

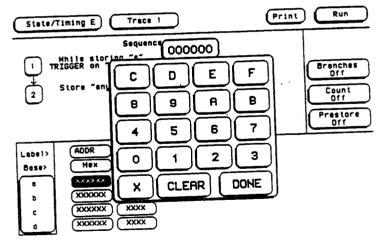

#### How to Enter Numeric Data

There are a number of pop-up menus in which you enter numeric data. The two major types are:

- Numeric entry with fixed units

- Numeric entry with variable units (i.e. μs, ms, etc.)

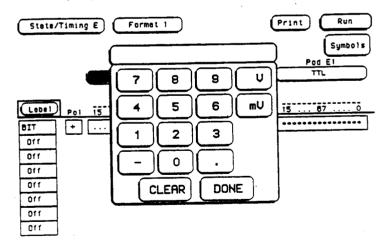

There are several numeric entry menus where you enter only the value, the units being pre-determined. There are other numeric entry menus for which you will be required to specify the units. One such type of numeric entry pop-up that you enter the units is the pod threshold pop-up.

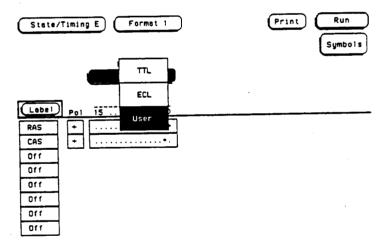

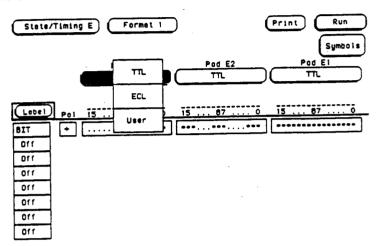

Besides being able to set the pod thresholds to either of the preset thresholds (TTL or ECL), you can set the thresholds to a specific voltage from -9.9 V to +9.9 V.

To set pod thresholds to a specific voltage, you enter either Format menu and touch a pod field. When the pop-up appears you can choose TTL, ECL, or User.

Figure 3-3. Pod Threshold

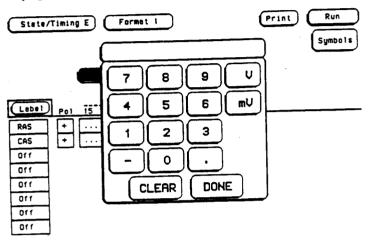

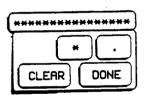

If you select the **User** option, a numeric keypad pop-up appears where you enter the desired threshold voltage. After selecting the value, you select the units (i.e., mV or V). Touch **Done** when you have finished specifying the pod threshold.

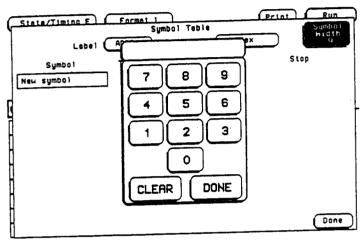

Figure 3-4. Numeric Entry Keypad

If you want a negative voltage for the threshold, press the - (minus sign) in the pop-up. Entering the - (minus sign) can be done either before or after the voltage level has been entered.

#### How to Enter Alpha Data

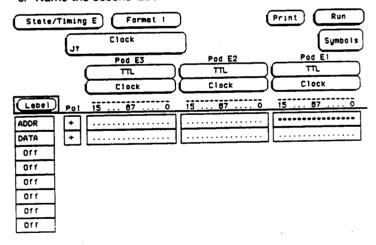

You can give specific names to several items. These names can represent your measurement specifically. For example, you might choose the name 68000STATE for the state analyzer configuration you are using on a 68000 microprocessor measurement.

The two major examples of items that can be named are:

- The name of each analyzer

- Labels

- Symbols

- Filenames

- File descriptions

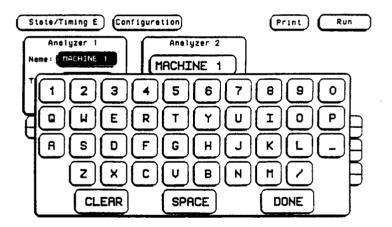

For example, you can name each analyzer with a name that is representative of your measurement. The default names for the analyzers within the logic analyzer are MACHINE 1 and MACHINE 2. To rename an analyzer, touch the field to the right of Name: in the State/Timing E Configuration menu. When the alphanumeric pop-up menu appears, enter the name you desire.

The line above the alphanumeric keyboard contains the current name. When you first enter the pop-up, the cursor in the name field is at the left. You can enter the name you wish by overwriting the existing name. If only a few changes need to be made, you can move the cursor using the knob to a character needing changed and select a new character. You can also clear the entire field by touching Clear. When you have entered the desired name, touch Done and the pop-up will close. The new name will appear in the field to the right of Name:

Figure 3-5. Alphanumeric Keypad

#### How to Roll Data

The roll feature is available in all menus that contain off-screen data. This allows you to roll data for viewing. Data can be off-screen both above and below or left and right of what you see on screen.

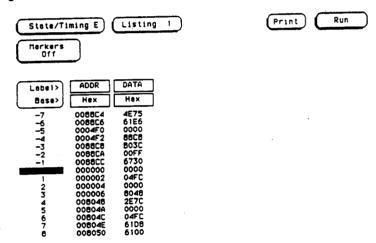

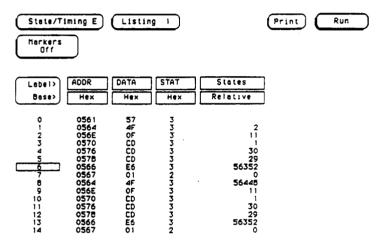

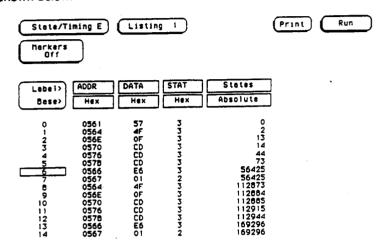

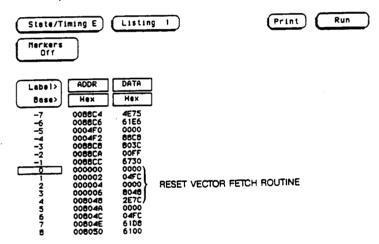

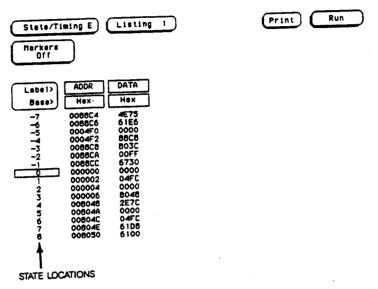

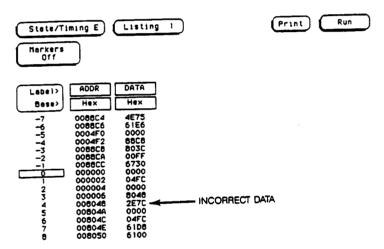

One example of a menu having off-screen data above and below the screen is the State Listing. The state listing is normally a list 1024 lines long, however, the display is only capable of showing you 16 lines at a time. To roll data in the state Listing (when the box in the left center of the listing area is light blue) simply turn the knob. If this box is not light blue, touch this box and then turn the knob. If you touch this box when it is light blue, a keypad will appear with which you can enter a state location. This allows you to effectively roll the displayed listing in large increments.

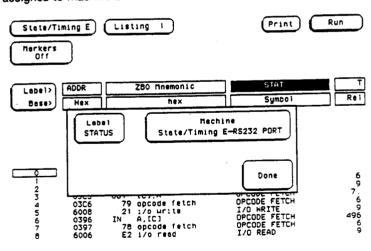

Figure 3-6. State Listing Menu with Off-screen Data

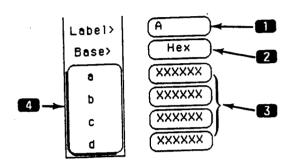

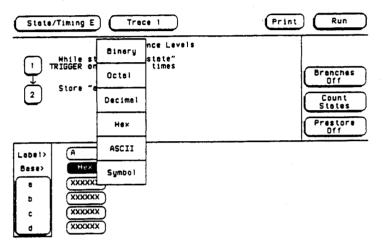

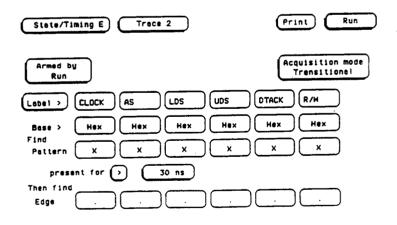

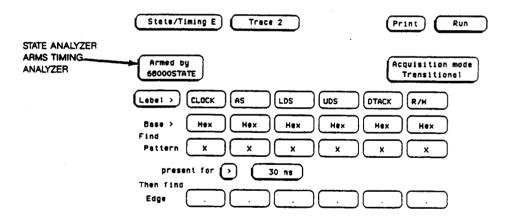

An example of off-screen data left and right can also be shown in figures 3-7 and 3-8. Figure 3-7 illustrates a timing Trace menu with labels off screen. In this case only six of the eight labels can be displayed at a time. Whenever there is data off screen to the left or right, an additional field exists in the menu as shown in figure 3-7. This is called a field because it is enclosed in a box and will turn light blue when touched.

Figure 3-7. Additional Field indicating Off-screen Data

If data does not exist off screen, the term Label > will not be enclosed in a box (see figure 3-8).

Figure 3-8. No Off-screen Data Left or Right

#### Assignment/ Specification Menus

There are a number of pop-up menus in which you can assign or specify what you want the logic analyzer to do. The basic menus of this type consist of:

- Assigning bits to pods

- Specifying patterns

- Specifying edges

#### Assigning Pod Bits to Labels

The bit assignment fields in both state and timing analyzers work identically. The convention for bit assignment is:

- \* (asterisk) indicates assigned bits.

- . (period) indicates un-assigned bits.

An example of assigning bits is in either the Timing or State Format menu.

#### Note

If you don't see any bit assignment fields, it merely means you don't have any pods assigned to this analyzer. Either switch analyzers or assign a pod to the analyzer you are working with.

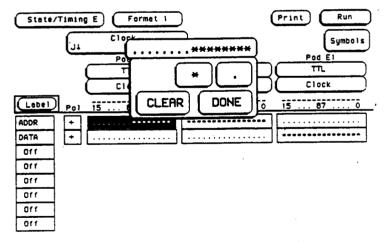

Figure 3-9. Bit Assignment Pod

To assign bits to either Analyzer 1 or Analyzer 2 there must be at least one pod assigned to the desired analyzer. If ther are no pods assigned to the analyzer you wish to use follow steps 1 and 2. If there is a pod assigned to the desired analyzer go to step 3 where you access the Format menu.

- 1. Enter the State/Timing E Configuration menu.

- 2. Touch a Pod field. When the pop-up appears, assign the pod to the analyzer of your choice.

- 3. Touch the field second from left in the top left corner. When the pop-up appears, touch Format 1 (or 2).

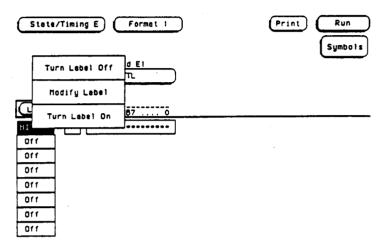

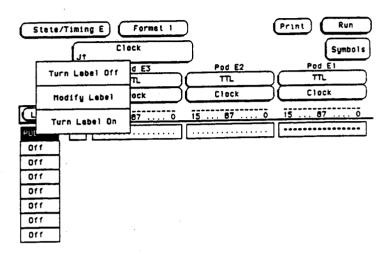

- 4. Before you can select a bit pattern at least one label must be on. To turn a label on, touch the label field and when the pop-up appears, touch **Turn Label On**.

- 5. Touch the bit assignemnt field to access the bit assignment pop-up.

- When the pop-up appears, using the KNOB, place the cursor on the desired bit and touch the asterisk to assign a bit or the period to unassign a bit. Touch **Done** when bit assignment is complete.

When the pop-up closes the bit assignment field is again displayed, however, now it is displayed with the assigned pattern.

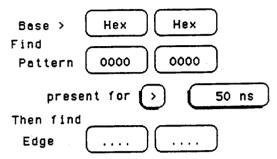

#### Specifying Patterns

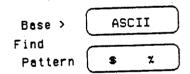

The Pattern field appears in several menus. Patterns can be specified in one of the available number bases. Patterns can be viewed in ASCII, but cannot be selected in ASCII.

The convention for "don't care" in these menus is an X except in the decimal base. If the base is set to decimal after a "don't care" is specified, a \$ will be displayed.

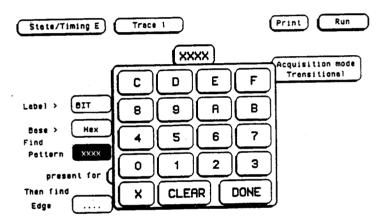

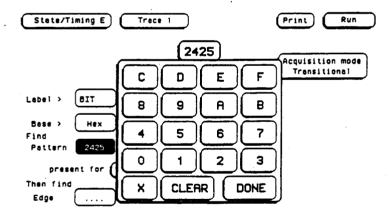

To select a pattern, enter the Trace menu and follow these steps:

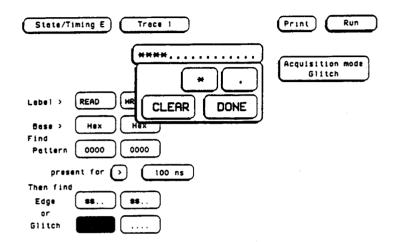

1. Touch the field to the right of Pattern. You will see a keypad pop-up (see figure 3-10).

Figure 3-10. Specifying Patterns Keypad Pop-up Menu

2. Using the alphanumeric keyboard, enter the desired pattern.

#### Note

Notice that the Base > field and the Find Pattern field are interactive. Only a keypad pop-up will appear that is compatible with the base selected. Since ASCII patterns cannot be entered directly, a keypad will not appear for data entry if the base is set to ASCII.

When the pop-up is open, you enter your desired pattern from the keypad (including don't cares). When you finish entering your pattern, close the pop-up by touching Done.

#### Specifying Edges

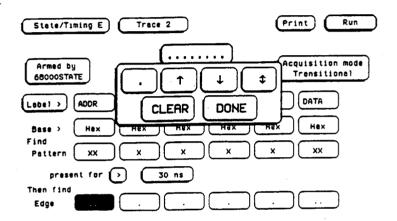

You can select a positive-going ( $\frac{1}{1}$ ), negative-going ( $\frac{1}{1}$ ), and either edge ( $\frac{1}{1}$ ) for your trigger.

To specify edges, enter the Trace menu and follow these steps:

1. Touch the field in the bottom left corner of the display. This field is labeled Edge. You will see the following pop-up.

Figure 3-11. Specifying Edges Pop-up Menu

When the pop-up appears you can make your edge selection for any bit by placing the cursor, using the KNOB, on the desired bit and touching the period, either edge, or both edges field.

After you have made your edge selection, touch Done.

#### Note

When you close the pop-up after specifying edges, you will see dollar signs (\$\$\_-) in the Then find Edge field if the logic analyzer can't display the edge correctly. This indicates the logic analyzer can't display the data correctly in the number base you have selected.

4

### **Using the Menus**

#### Introduction

This chapter contains menu maps of the HP 16510A logic analyzer. Since the front-panel user interface consists mainly of menus that you access to configure the logic analyzer, the menu maps provide quick reference to the menus, menu options, and ultimately the functions of the logic analyzer.

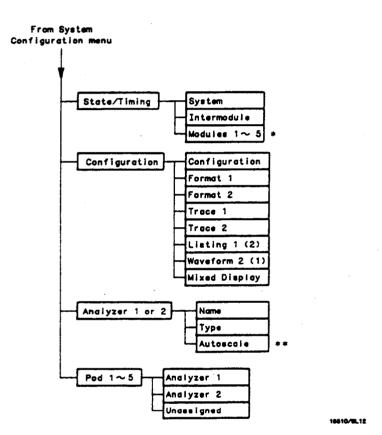

#### Menu Maps

The following pages show the menu maps of all functions of the logic analyzer. The State/Timing Configuration menu is the logic analyzer's system level menu. The rest of the menus are the subsystem level menus of the logic analyzer.

### State/Timing Configuration Menu Map

- Modules 1 through 5 depend on what modules are installed in the HP 16500A

- \*\* Timing analyzer only

Figure 4-1. State/Timing Configuration Menu Map

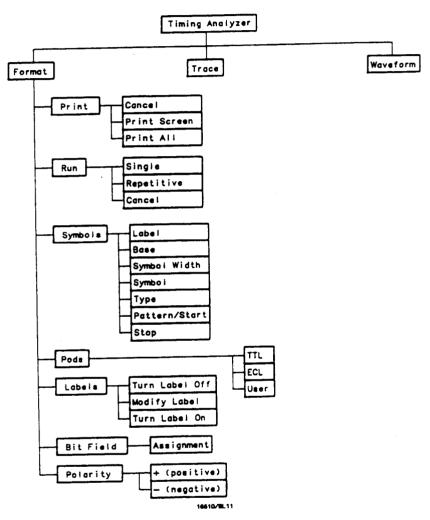

#### Timing Format Menu Map

Figure 4-2. Timing Format Menu Map

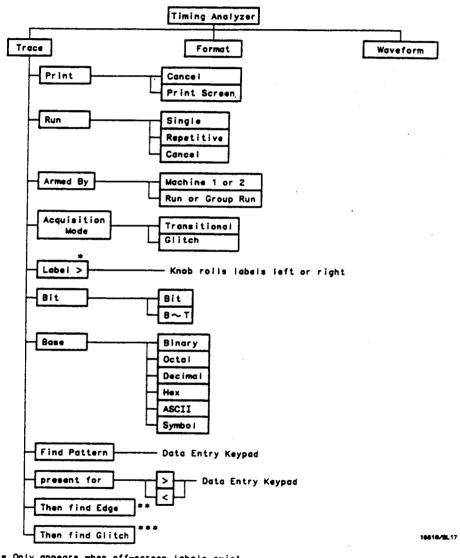

## Timing Trace Menu Map

- \* Only appears when off-screen labels exist

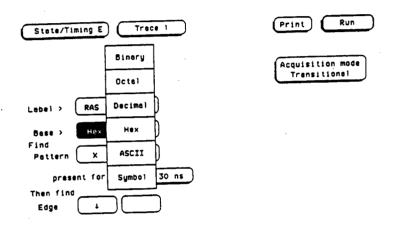

\*\* Only available when "greater than" is specified in "present for" field

\*\*\* Only available when "then find edge" is present and in Glitch mode

Figure 4-3. Timing Trace Menu Map

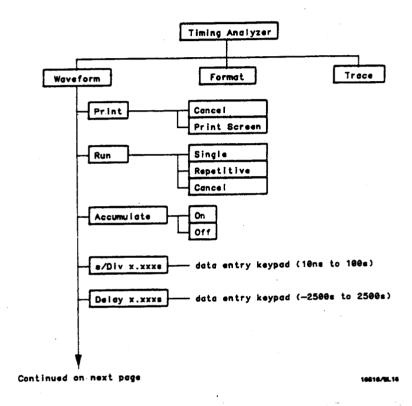

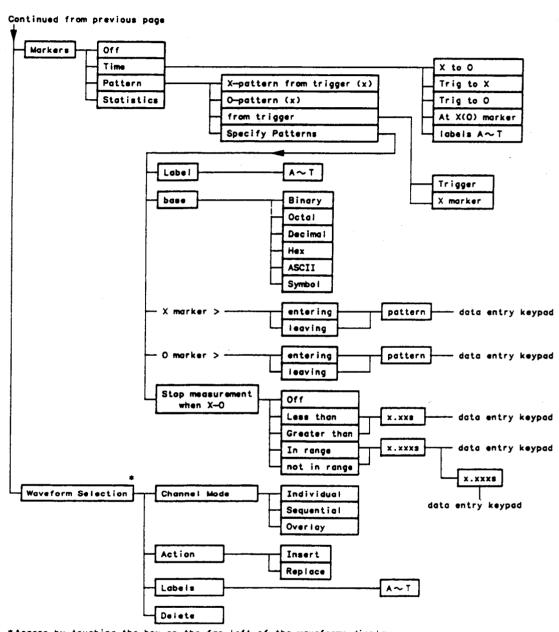

### Timing Waveform Menu Map

Figure 4-4a. P/O Timing Waveform Menu Map

\*Access by touching the box on the far left of the waveforms display where the labels are displayed

16516/BL19

Figure 4-4b. P/O Timing Waveform Menu Map

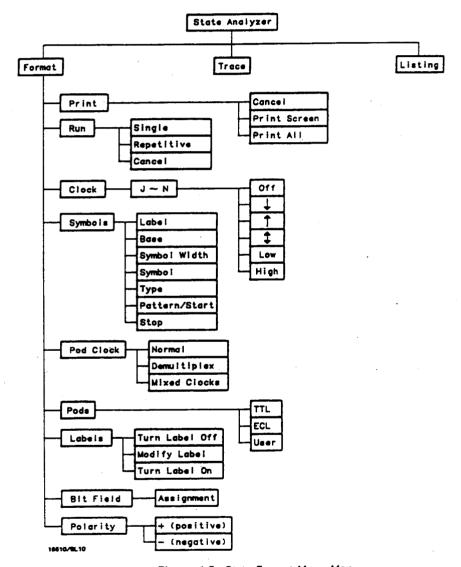

#### State Format Menu Map

Figure 4-5. State Format Menu Map

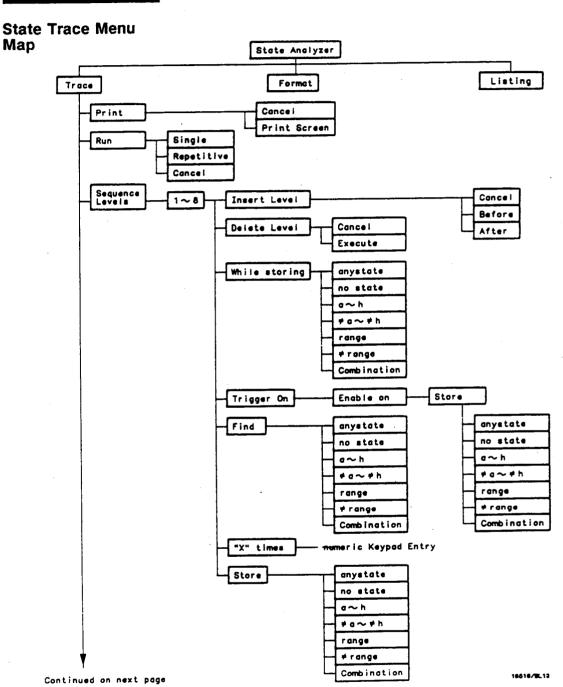

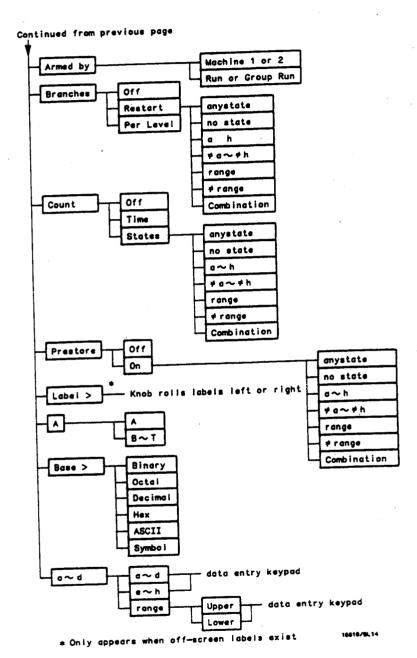

Figure 4-6a. P/O State Trace Menu Map

Figure 4-6b. P/O State Trace Menu Map

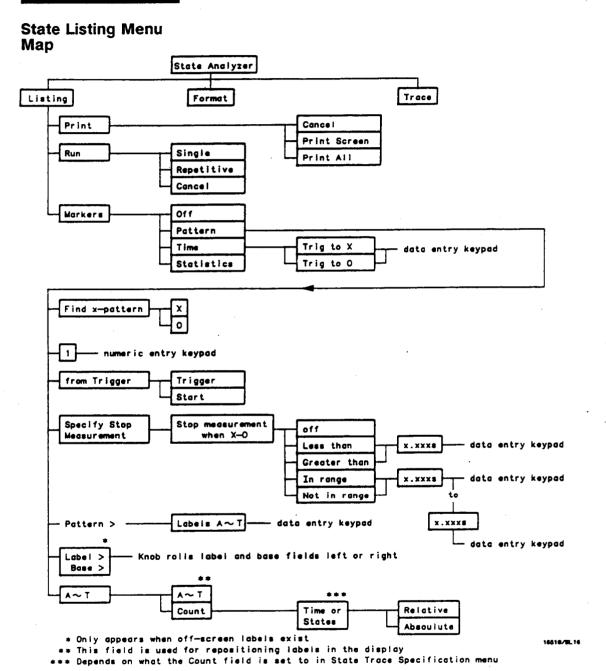

Figure 4-7. State Listing Menu Map

Using the Menus 4-10

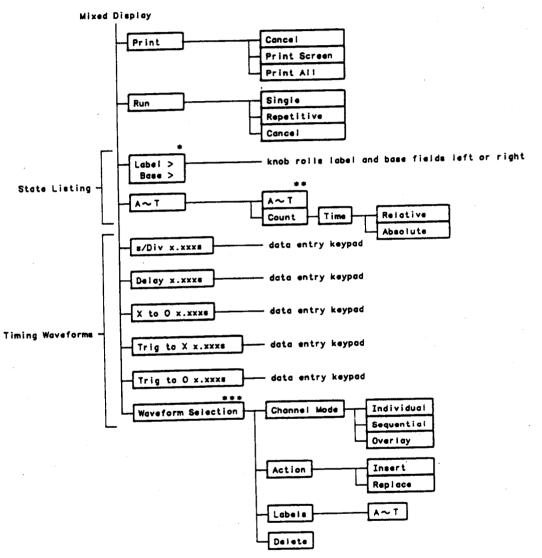

#### **Mixed Display** Menu Map

# Only appears when off-screen labels exist

\*\* This field is used for repositioning labels in the display

\*\*\* Access by touching the box on the far left of the waveforms display where the labels are displayed

Figure 4-8. Mixed Display Menu Map

#### Menus

#### Introduction

This chapter describes the menus and pop-up menus that you will use on your logic analyzer. The purpose and functions of each menu are explained in detail, and we have included many illustrations and examples to make the explanations clearer.

The main menus of the logic analyzer are grouped into two categories: System Level Menus and Subsystem Level Menus. The System Level Menu is:

State/Timing Configuration Menu

The Subsystem Level Menus are:

- Format (timing and state)

- Trace (timing and state)

- Timing Waveforms

- State Listing

An illustration of each main menu is given at the beginning of the section that describes the menu. In the illustration, the fields are numbered according to the order in which they are discussed to make them easy to reference.

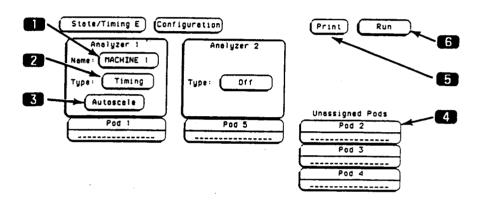

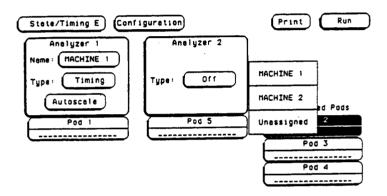

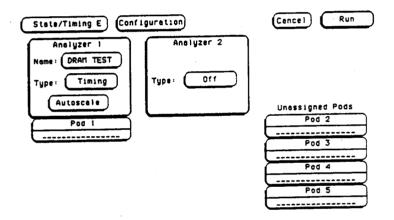

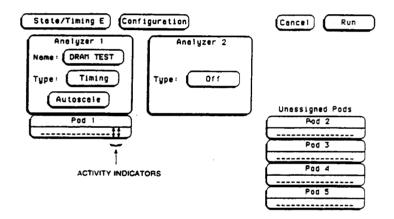

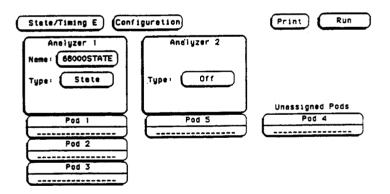

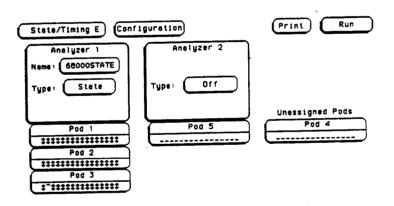

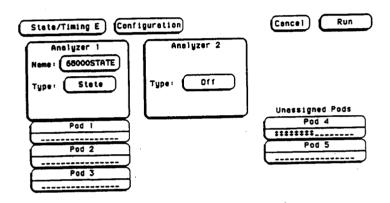

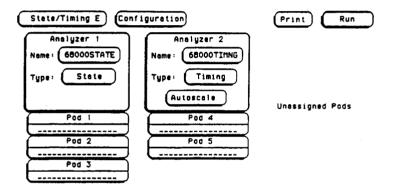

System Level Menu When the logic analyzer is selected from the System Configuration menu, the State/Timing Configuration menu is displayed. It is in this menu that you configure your logic analyzer in one of four ways: timing analyzer only, state analyzer only, two state analyzers, or one timing analyzer and one state analyzer. You can also name each internal analyzer and assign pods to them.

State/Timing The State/Timing Configuration menu for the HP 16510A Logic Configuration Menu Analyzer is shown below. The fields in the menu that are numbered in the figure are described in this section.

Figure 5-1. State/Timing Configuration Menu

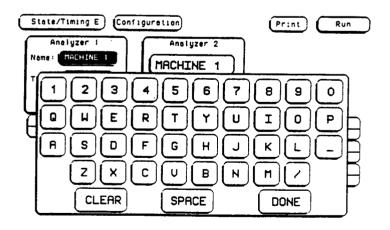

Name

You name an analyzer by selecting the Name field under it. An alphanumeric pop-up menu will appear. The keypad is similar to a computer keyboard.

Figure 5-2. Alphanumeric Keypad Pop-up

At the top of the keypad pop-up, is a box where the current name appears when the pop-up opens, and where the new name will appear when you touch keys on the keypad. In the name box is a cursor which indicates in what space your next selection will be placed.

You can name the analyzer in one of two ways. The first way is to position the cursor over the character to be replaced in the pop-up using the KNOB, then touching the new character. The new character appears in the name box.

The second way is to touch CLEAR. This clears the entire name from the box and places the cursor at the beginning of the name box in the pop-up.

When you have entered the correct name, touch DONE.

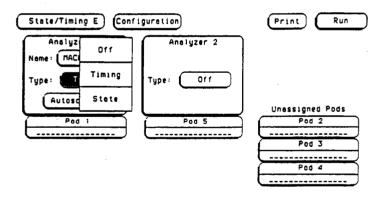

#### 2 Type

Ð

The Type field defines the machine as either a state analyzer or a timing analyzer or indicates that a system performance analysis (SPA) can be done on that analyzer (optional). When this field is touched, a pop-up menu appears. You touch the machine type to make your selection.

Figure 5-3. Type Pop-up Menu

#### **S** Autoscale

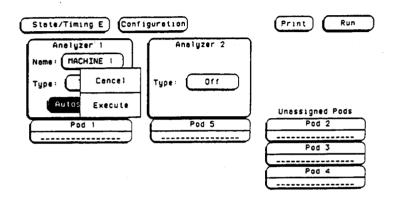

The purpose of Autoscale is to provide a starting point for setting up a measurement. The Autoscale field only appears on a timing analyzer. When you touch Autoscale, you will see a pop-up with two options: Cancel and Execute. If you select Cancel, the autoscale is cancelled and control is returned to the State/Timing Configuration menu.

Figure 5-4. Autoscale Pop-up Menu

If you choose Execute, autoscale configures the timing Format and Trace Specification menus and the timing Waveforms menu. Any configurations that you have done will be lost. Autoscale searches for channels with activity on the pods assigned to the timing analyzer and displays them in the Waveforms menu.

#### Note

Executing autoscale erases all previous configurations for your timing analyzer and turns the other analyzer off. If you don't want this to happen, touch Cancel in the pop-up.

4 Pods

Each pod can be assigned to one of the analyzers. When the HP 16510A Logic Analyzer is powered up, Pod 1 is assigned to Analyzer 1 and Pod 5 is assigned to Analyzer 2.

To assign a pod, touch the pod field. With the pop-up that appears, you can assign the pod to Analyzer 1, Analyzer 2, or Unassign it. Making a selection closes the pop-up and moves the pod field to the analyzer to which the pod is assigned.

Figure 5-5. Pod Assignment Pop-up Menu

Fint Print

The Print field allows you to print what is displayed on the screen at the time you initiate the printout. When you touch the Print field, a pop-up appears showing you the print options Cancel, Print Screen, and in some menus, Print All.

You start a print by touching the **Print** field. When the pop-up appears, you touch either **Print Screen** or **Print All**. The information on the screen is frozen, and the **Print** field changes to **Cancel** and turns red. While the data is being transferred to the printer, the logic analyzer's user-interface is not usable with the exception of the **Cancel** field. When the logic analyzer has completed the data transfer to the printer, the advisory "Print Completed" is displayed and the user-interface is usable again.

If you wish to stop a printout before it is completed, touch **Cancel**. This stops the print, and the message "Print Cancelled" appears in red.

Print Screen. In the Print Screen mode, the printer uses its graphics capabilities so that the printout will look just like the logic analyzer screen.

Print All. The Print All option prints not only what is displayed on screen but what is below, and, in the Format Specification, what is to the right of the screen at the time you initiate the printout.

#### Note

Make sure the first line you wish to print is in the light blue box at the center of the listing area when you touch Print All. Lines above this box will not print.

Use this option when you want to print all the data in menus like:

- Timing Format Specifications

- State Format Specifications

- State Trace Specifications

- State Listing

- Symbols

If there is information below the screen, as in the State Listing, the information will be printed on multiple pages. In Timing and State Format Specifications, the print will be compressed when necessary to print data that is off-screen to the right.

When you select the **Print All** option, the information on the screen is frozen, and the message "Printing All" appears at the top of the display. Don't worry, this message will not appear in your printout. While the data is being transferred to the printer, the logic analyzer's user-interface is not usable. When the logic analyzer has completed the data transfer to the printer, the advisory "Print Completed" appears and the user-interface is again usable.

If you wish to stop a printout before it is completed, touch Cancel.

This stops the print and the message "Print Cancelled" appears at the top of the display.

#### Run

The Run field allows you to start data acquisition. The pop-up that appears when you touch this field contains the trace mode options Single, Repetitive, and Cancel. This field is explained in detail in "Run/Trace Mode" in both the Timing and State Trace specification menus sections of this chapter.

## Sub-System Level Menus

The HP 16510A logic analyzer is configured for measurements in the Timing and State Format and Trace Specification menus. The Format menus can be accessed by touching Format 1 or 2, and the Trace menus by touching Trace 1 or 2.

The Format Specification menus let you specify how the logic analyzer groups the input channels from your microprocessor. You can set the threshold levels of the pods assigned to the analyzer, assign labels and channels, specify symbols, and, in the case of the state analyzer, set clocks for triggering.

The Trace Specification menus allow you to configure the logic analyzer to capture only the data of interest in your measurement. The logic analyzer acquires data until it triggers at a location that you specify by setting certain parameters for the data. In the timing analyzer you can configure the analyzer to trigger on specific patterns, edges, or glitches. In the state analyzer you can configure the analyzer to trigger on a sequence of states.

At power up, the logic analyzer is configured with a default setting. You can use this default setting to make a test measurement on your system. It can give you an idea of where to start your measurement.

Each of the format and trace specification menus will be covered in this chapter. For examples on setting up configurations for measurements with the timing and state analyzers, refer to your *HP 16510A Getting Started Guide* or chapters 7 through 9 in this manual.

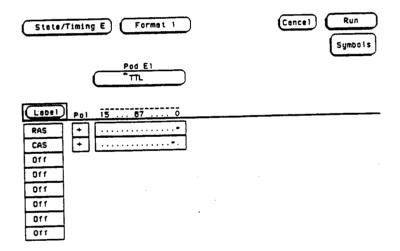

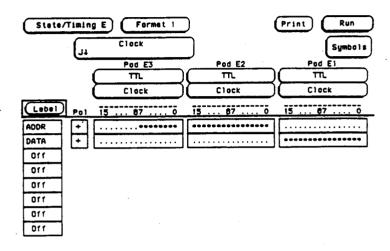

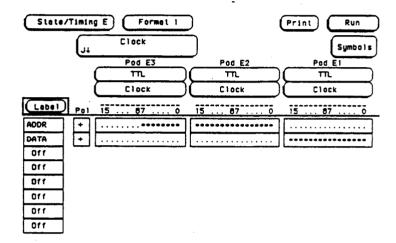

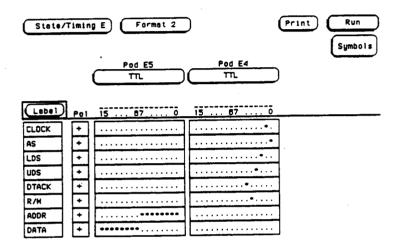

Timing and State Format Specification Menus

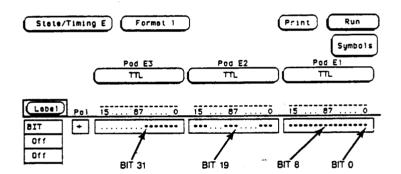

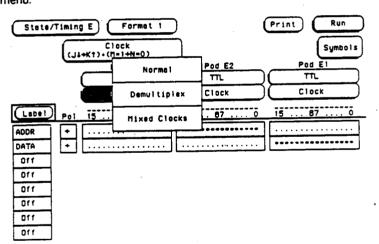

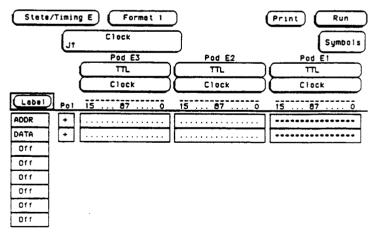

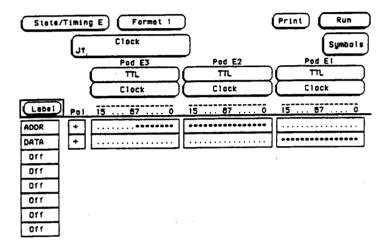

At power up the Timing and State Format Specification menus look basically the same, with a few exceptions in the state analyzer. The Timing Format Specification menu looks like that shown below:

Figure 5-6. Timing Format Specification Menu

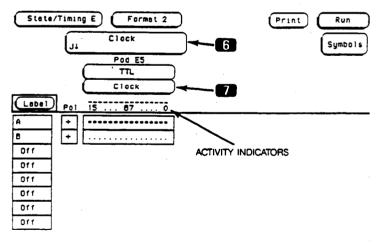

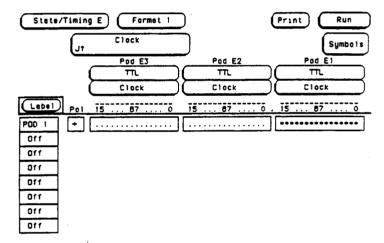

The State Format Specification menu for the HP 16510A looks like the following:

Figure 5-7. State Format Specification Menu

These menus show only one pod assigned to each analyzer at power up. Any number of pods can be assigned to one analyzer, from none to all five. In the Format menus, only three pods appear at a time in the display. If there are any pods off screen, an additional field will be present. This field is labeled Pods . To view off-screen pods, touch the Pods field and rotate the KNOB. The pods are always positioned so that the lowest numbered pod is on the right and the highest numbered pod is on the left.

# Timing and State Format Specification Menu Fields

Seven types of fields are present in the menus. They are:

- 1) Label

- 2) Polarity (Pol)

- 3) Bit assignments

- 4) Pod threshold

- 5) Specify Symbols

- 6) Clock (state analyzer only)

- 7) Pod Clock (state analyzer only)

A portion of the menu that is not a field is the Activity Indicators display. The indicators appear above the bit numbers of each pod. When the logic analyzer is connected to your target system and the system is running, you will see \$\frac{1}{2}\$ in the Activity Indicators display for each channel that has activity. These tell you that the signals on the channels are transitioning.

The fields in the Format menus are described in the following sections. The descriptions apply to both the timing and state analyzers unless noted otherwise.

Label

The label column contains 20 Label fields that you can define. Of the 20 labels, the logic analyzer displays only 8 at one time. To view the labels that are off screen, rotate the KNOB. The labels roll up and down.

To access one of the Label fields, touch the desired field. You will see a pop-up menu like that shown below.

Figure 5-8. Label Pop-up Menu

Turn Label On. Selecting this option turns the label on and gives it a default letter name. If you turned all the labels on they would be named POD 1 through T from top to bottom in the timing analyzer and A throughT in the state analyzer. When a label is turned on, bit assignment fields for the label appear to the right of the label under the pods.

Modify Label. If you want to change the name of a label, or want to turn a label on and give it a specific name, you would select the Modify Label option. When you do, an alphanumeric keypad pop-up menu appears. You use the pop-up keypad to name the label. A label name can be a maximum of six characters.

Turn Label Off. Selecting this option turns the label off. When a label is turned off, the bit assignments are saved by the logic analyzer. This gives you the option of turning the label back on and still having the bit assignments if you need them. The timing waveforms and state listings are also saved.

You can give the same name to a label in the state analyzer as in the timing analyzer without causing an error. The logic analyzer distinguishes between them. An example of this appears in chapter 7 of the *HP 16510A Getting Started Guide* and chapter 9 of this manual.

2 Polarity (Pol)

Each label has a polarity assigned to it. The default for all the labels is positive (+) polarity. You can change the polarity of a label by touching the the polarity field. This toggles the polarity between positive (+) and negative (-).

In the state analyzer, negative polarity inverts all the data. In the timing analyzer, negative polarity inverts all the data, but doesn't change the actual waveforms in the Timing Waveforms Menu.

Bit Assignment

The bit assignment fields allow you to assign bits (channels) to labels. Above each column of the bit assignment fields is a line that tells you the bit numbers from 0 to 15, with the left bit numbered 15 and the right bit numbered 0. This line helps you know exactly which bits you are assigning.

The convention for bit assignment is:

- \* (asterisk) indicates assigned bit

- . (period) indicates unassigned bit

At power up the 16 bits of Pod 1 are assigned to the timing analyzer, and the 16 bits of Pod 5 are assigned to the state analyzer.

To change a bit assignment configuration, touch a bit assignment field. You will see the following pop-up menu.

Figure 5-9. Bit Assignment Pop-up Menu

Use the KNOB to move the cursor to an asterisk or a period you wish to change. Touch the desired state (asterisk or period) in the pop-up. When the bits (channels) are assigned as desired, touch **DONE**. This closes the pop-up and displays the new bit assignment in the Format Specification menu.

Assigning one channel per label may be handy in some applications. This is illustrated in chapter 7 of the *HP 16510A Getting Started Guide*. Also, you can assign a channel to more than one label, but this usually isn't desired.

Labels may have from 1 to 32 channels assigned to them. If you try to assign more than 32 channels to a label, the logic analyzer will beep, indicating an error, and a message will appear at the top of the screen telling you that 32 channels per label is maximum.

Channels assigned to a label are numbered from right to left by the logic analyzer. The least significant assigned bit (LSB) on the far right is numbered 0, the next assigned bit is numbered 1, and so on. Since the maximum of 32 channels can be assigned to one label, the highest number that can be given to a channel is 31. Although labels can contain split fields, assigned channels are always numbered consecutively within a label. The numbering of channels is illustrated with the figure below.

Figure 5-10. Numbering of Assigned Bits

#### Pod Threshold

Each pod has a threshold level assigned to it. Threshold levels may be defined for Pods 1, 2 and 3 individually, and one threshold for Pods 4 and 5. It doesn't matter if Pods 4 and 5 are assigned to different analyzers. Changing the threshold of either pod 4 or 5 changes the threshold of the other.

If you touch the pod threshold fields you will see the following pop-up menu.

Figure 5-11. Pod Threshold Pop-up Menu

TTL sets the threshold at +1.6 volts, and ECL sets the threshold at -1.3 volts.

The **User** option lets you set the threshold to a specific voltage between -9.9 V and +9.9 V. If you select this option you will see a numeric entry keypad pop-up menu as shown.

Figure 5-12. Numeric Entry Keypad Pop-up Menu

You enter a threshold in the pop-up with the keypad by touching the desired value, units and polarity. When the correct threshold voltage is displayed, touch **DONE**. The pop-up will close and the new threshold will be placed in the pod threshold field.

In the state analyzer, the same threshold level applies to a pod's clock as to its 16 data bits.

#### 5 Specify Symbols

The logic analyzer supplies Timing and State Symbol Tables in which you can define a mnemonic for a specific bit pattern of a label. When measurements are made by the logic analyzer, the mnemonic is displayed where the bit pattern occurs if the Symbol base is selected.

It is possible for you to specify up to 200 symbols in the logic analyzer. If you have only one of the internal analyzers on, all 200 symbols can be defined in it. If both analyzers are on, the 200 symbols are split between the two. For example, analyzer 1 may have 150, leaving 50 available for analyzer 2.

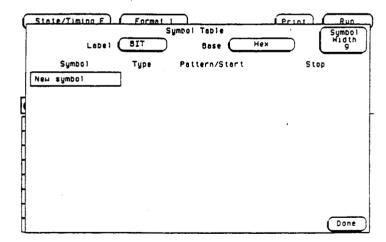

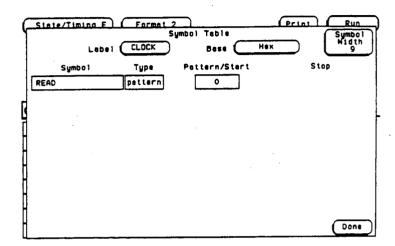

To access the **Symbol Table** in either the State or Timing **Format** Specification menus, touch the **Symbols** field. You will see a new menu as shown. This is the default setting for the **Symbol Table** in both the timing and state analyzers.

Figure 5-13. Symbol Table Menu

There are four fields in the Symbol Table menu. They are:

- Label

- Base

- Symbol Width

- Symbol name

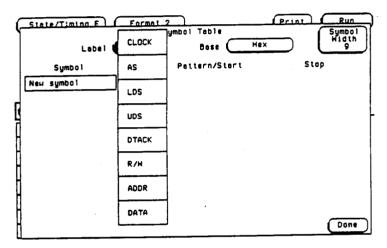

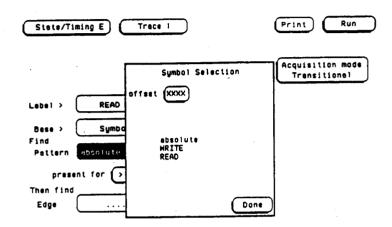

Label. The Label field identifies the label for which you are specifying the symbols. If you select this field you will get a pop-up that lists all the labels that are turned on in that analyzer.

Figure 5-14. Label Pop-up Menu

Each label has a separate symbol table. This allows you to give the same name to symbols defined under different labels. In the Label pop-up touch the label for which you wish to specify symbols.

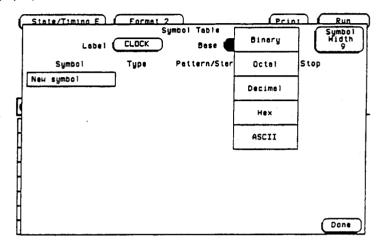

Base. The Base field tells you the number base in which the pattern will be specified. The base you choose here will appear in the Find Pattern field of the Timing Trace Specification menu in the timing analyzer, or the pattern field of the State Trace Specification menu in the state analyzer. These are covered later in this chapter.

To change the base, touch the current base. You will see the following pop-up menu.

Figure 5-15. Base Pop-up Menu

If more than 20 channels are assigned to a label, the **Binary** option is not offered in the pop-up. The reason for this is that when a symbol is specified as a range, there is only enough room for 20 bits to be displayed on the screen.

When you decide which base you want to work in, choose that option from the number Base pop-up menu.

If you choose the **ASCII** option, you can see what ASCII characters the pattern and ranges defined by your symbols represent. ASCII characters represented by the decimal numbers 0 to 127 (hex 00 to 7F) are offered on your logic analyzer. Specifying patterns and ranges for symbols is discussed in the next section.

#### Note

You cannot specify a pattern or range when the base is ASCII. First define the pattern or range in one of the other bases, then switch to ASCII to see the ASCII characters.

Symbol Width. The Symbol Width field lets you specify how many characters of the symbol name will be displayed when the symbol is referenced in the Timing and State Trace Specification menus, the Timing Waveforms menu, or the State Listing menu. Selecting this field gives you the following pop-up.

Figure 5-16. Symbol Width Pop-up Menu

You can have the logic analyzer display from 1 to all 16 of the characters in the symbol name. This is covered more in the sections on the Trace menus, the Waveforms menu, and the State Listing menu later in this chapter.

Symbol Name. When you first access the Symbol Table, there are no symbols specified. The symbol name field reads New Symbol. If you select this field an alphanumeric keypad pop-up menu appears. Use the keypad to enter the name of your symbol. A maximum of 16 characters can be used in the name of a symbol.

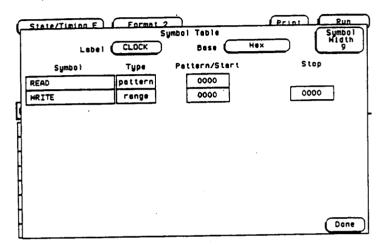

When you touch **DONE** field in the keypad pop-up menu, the name of the symbol appears in the symbol name field, and two more fields appear in the display to the right of the symbol name.

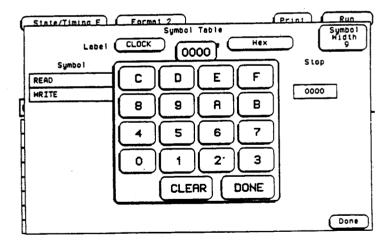

Figure 5-17. Symbol Defined as a Pattern

The first of these fields defines the symbol as either a pattern or a range. If you touch this field, it will toggle between pattern and range.

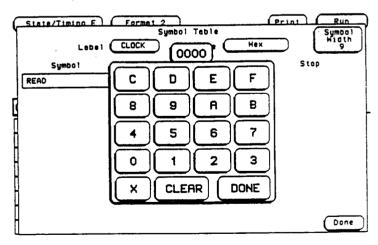

When the symbol is defined as a pattern, one field (Pattern/start) appears to specify what the pattern is. Touching this field displays a pop-up with which you can specify the pattern. Use the keypad and the X (Don't Care) key to enter the pattern.

Figure 5-18. Specify Pattern Pop-up

If the symbol is defined as a range, two fields appear in which you specify the upper and lower boundaries of the range. The fields are Pattern/Start and Stop.

Figure 5-19. Symbol Defined as a Range

Touching either of these fields gives you a pop-up with which you can specify the boundary of the range.

Figure 5-20. Specify Range Pop-up

You can specify ranges that overlap or are nested within each other. They must be specific. Don't cares are not allowed.

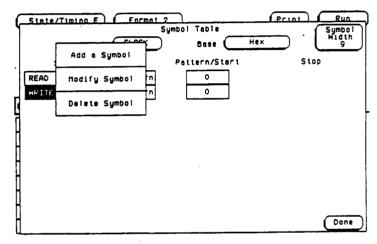

The logic analyzer gives patterns priority over ranges when displaying measurements. This will be covered in more detail in the sections "Timing Waveforms Menus" and "State Listing Menus" later in this chapter. To add more symbols to your symbol table, touch the field of the last symbol defined. A pop-up menu appears as shown.

Figure 5-21. Symbol Pop-up Menu

The first option in the pop-up is Add a Symbol. It allows you to add another symbol. When you select it, you will see an alphanumeric pop-up menu. Use the keypad to enter the name of your new symbol. When you select Done, your new symbol will appear in the Symbol Table.

The second option in the pop-up is **Modify symbol**. If you select this option, you will see an alphanumeric pop-up menu with which you can change the name of the symbol.

The third option in the pop-up is **Delete Symbol**. If you select this option, the symbol will be deleted from the Symbol Table.

**Leaving the Symbol Table Menu**. When you have specified all your symbols, you can leave the Symbol Table menu by touching **Done**. This puts you back in the Format Specification menu that you were in before entering the Symbol Table.

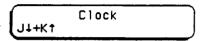

6 Clock

The Clock field is present in the Format Specification menu only in the state analyzer. This field displays the clocks that are to be used to clock the logic analyzer. The display will be referred to as the "clocking arrangement."

The HP 16510A Logic Analyzer has five clock channels, each of which is on a pod. The clocks are connected through the pods simply for convenience. The clock channels are labeled J, K, L, M, and N and are on pods 1 through 5, respectively. The clocking of the state analyzer is synchronous with your system because the analyzer uses the clocks present in your system that assure valid data.

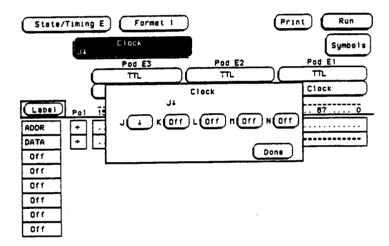

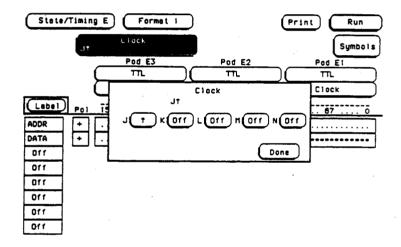

When you select the Clock field, you will see the following pop-up menu with which you specify the clock.

Figure 5-22. Clock Pop-up Menu

You can use one of the clocks alone or combine them to build one clocking arrangement.

If you select a field to the right of one of the clocks in the pop-up, you will see another pop-up menu:

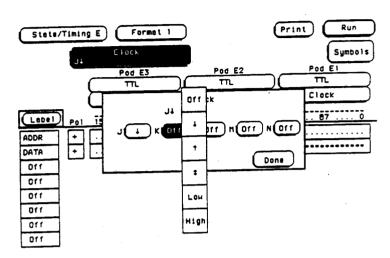

Figure 5-23. Single Clock Pop-up Menu

With this menu you set the condition needed by each clock. You can specify that the logic analyzer looks for the negative edge of the clock, the positive edge, either edge, a high level, or a low level, or you can turn the clock off.

The clocks are combined by ORing and ANDing them. Clock edges are ORed to clock edges, clock levels are ORed to clock levels, and clock edges are ANDed to clock levels.

For example, if you select \$\frac{1}{2}\$ for the J clock, \$\frac{1}{2}\$ for the K clock, **High** for the M clock, and **Low** for the N clock, the resulting clocking arrangement will appear in the display as:

Figure 5-24. Example of a Clocking Arrangement

With this arrangement, the logic analyzer will clock the data when there is a negative edge of the J clock OR a positive edge of the K clock, AND when there is a high level on the M clock OR a low level on the N clock.

You must always specify at least one clock edge. If you try to use only clock levels, the logic analyzer will display a message telling you that at least one edge is required.

### Pod Clock

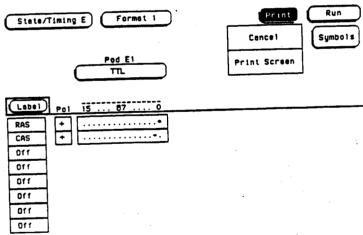

Your logic analyzer has the capability of clocking data in three different ways. The pod Clock fields in the **State Format Specification** menu allow you to specify which of the three ways you want to clock the data.

Each pod assigned to the state analyzer has a pod Clock field associated with it. As with the Clock field discussed in the previous section, the pod Clock fields are present only in the state analyzer. Selecting one of the pod Clock fields gives you the following pop-up menu:

Figure 5-25. Pod Clock Field Pop-up Menu

**Normal.** This option specifies that clocking will be done in single phase. That is, the clocking arrangement located in the Clock field above the pods in the State Format Specification menu will be used to clock all data (pods) assigned to this machine.

For example, suppose that the Clock field looks like the following:

Figure 5-26. Example of a Clocking Arrangement

In Normal mode the state analyzer will sample data present on all pods assigned to this machine on a negative edge of the J clock OR on a positive edge of the K clock.

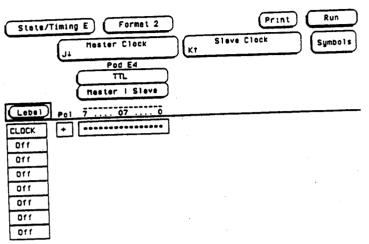

**Demultiplex.** With the HP 16510A Logic Analyzer, you can clock two different types of data that occur on the same lines. For instance, lines that transfer both address and data information need to be clocked at different times in order to get the right information at the right time. The Demultiplex option provides the means to do this.

When you select the Demultiplex option, the pod Clock field changes to Master | Slave, and two clock fields appear above the pods where just one Clock field used to be. These fields are the Master Clock and Slave Clock, as shown:

Figure 5-27. Master Clock and Slave Clock

Demultiplexing is done on the data lines of the specified pod to read only the lower eight bits. This is two phase clocking, with the Master Clock following the Slave Clock. The analyzer first looks for the clocking arrangement that you specify in the Slave Clock. When it sees that, the analyzer clocks the data present on bits 0-7 of the pod, then waits for the clocking arrangement that you specify in the Master Clock. When it sees that clocking arrangement, it again clocks the data present on bits 0-7 of the pod. The upper eight bits of the pod are ignored and don't need to be connected to your system.

Notice that the bit numbers that appear above the bit assignment field have changed. The bits are now numbered 7....07....0 instead of 15....87....0. This helps you set up the analyzer to clock the right information at the right time.

The address/data lines AD0-AD7 on the 8085 microprocessor are an example for **Demultiplex**. During part of the operating time the lines have an address on them, and during other times they have data on them. Hook the lower eight bits of one of the pods to these eight lines and set the Slave and Master Clocks for the pod such that they clock the data and the address at the proper time.

In this example, you may choose to assign the bits in the State Format Specification menu similar to that shown in the following figure. In this case you would want to clock the address with the Slave Clock and the data with the Master Clock.

Figure 5-28. Bit Assignments for Master and Slave Clocks

The Master and Slave Clocks can have the same clocking arrangements. The clocking is still done the same way, with the lower eight bits being clocked first on the Slave Clock, then on the Master Clock.

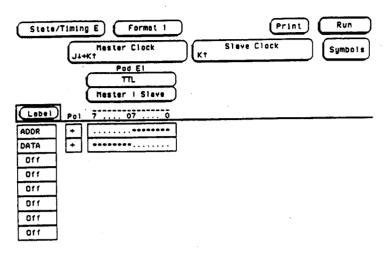

Mixed Clocks. The Mixed Clocks option allows you to clock the lower eight bits of a pod separately from the upper eight bits. The state analyzer uses Master and Slave Clocks to do this. If you select this option in the pod Clock pop-up, the pod Clock field changes to Master | Slave, and two Clock fields, Master and Slave, appear above the pods.

As in Demultiplex, the Master Clock follows the Slave Clock. The state analyzer looks for the clocking arrangement given by Slave Clock and clocks the lower eight bits. Then it looks for the clock arrangement given by the Master Clock and clocks the upper eight bits. Unlike Demultiplex, all 16 bits of a pod are sampled.

The Master and Slave Clocks can have the same clocking arrangements. The clocking is still done the same way, with the lower eight bits clocked on the Slave Clock and the upper eight bits clocked on the Master Clock.

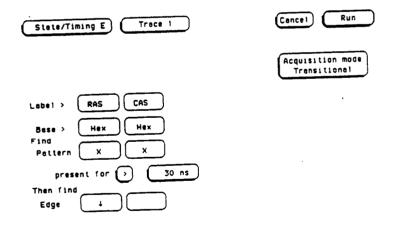

# Timing Trace Specification Menu

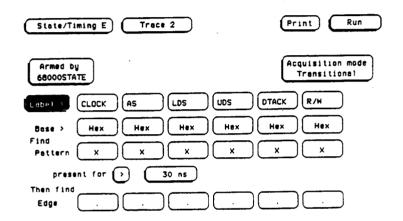

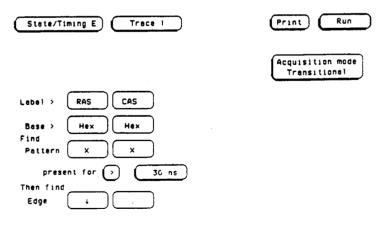

The Timing Trace Specification menu lets you specify the trigger point for the logic analyzer to start capturing data and the manner in which the analyzer will capture data. You configure the timing analyzer to find a pattern first and then a transition in the signal or signals:

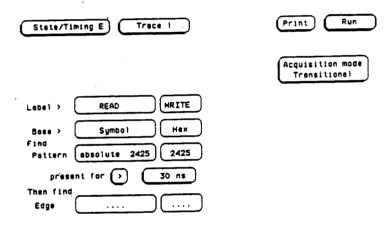

The menu looks like that shown below. This is the default setting for the menu. Print Trece 1 State/Timing E Acquisition mode Armed by Transitional Run BIT Hex Find XXXX **→**Pettern present for 🕟 30 ns

Then find

Figure 5-29. Timing Trace Specification Menu

## Timing Trace Specification Menu Fields

The fields in the Timing Trace Specification menu are:

- 1) Run/Trace Mode

- 2) Armed by

- 3) Acquisition mode

- 4) Label

- 5) Base

- 6) Find Pattern

- 7) Pattern Duration (present for \_\_\_\_\_

- 8) Then find Edge

These are described in the following sections.

## Run/Trace Mode

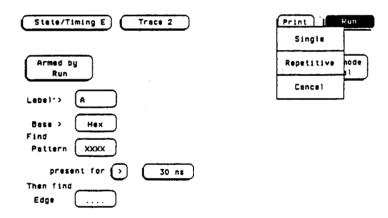

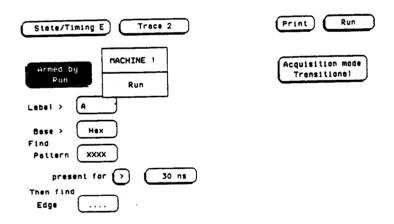

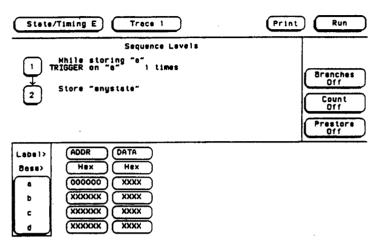

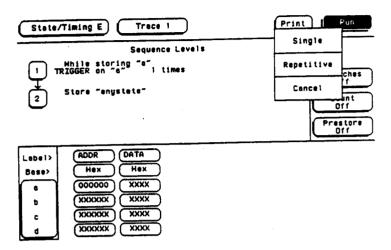

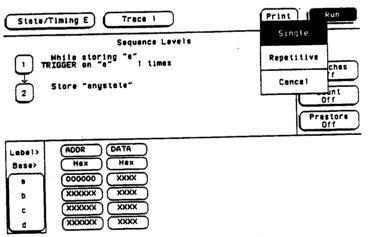

You specify the mode in which the timing analyzer will trace data when you touch **Run**. You have two choices for trace mode: Single and Repetitive. When you touch **Run** and hold your finger on the field, you will see the following pop-up menu:

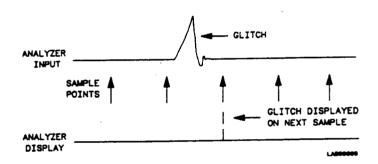

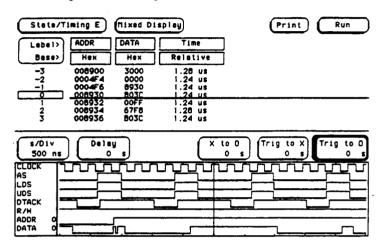

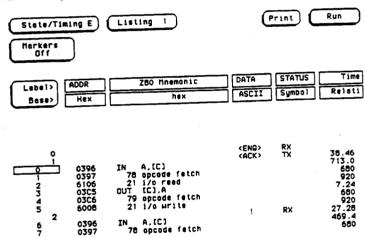

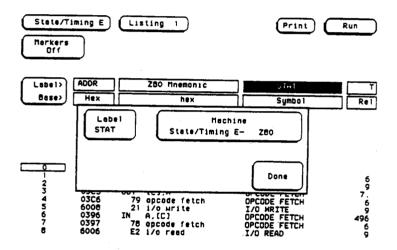

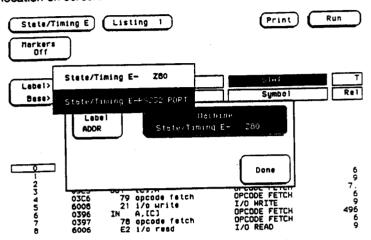

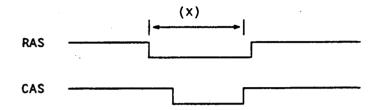

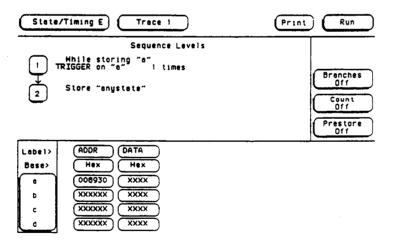

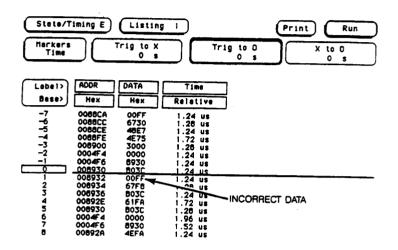

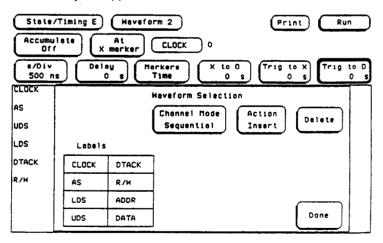

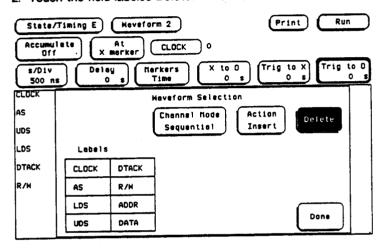

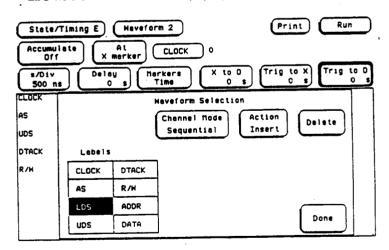

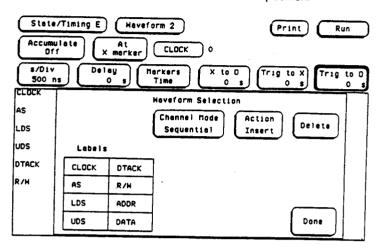

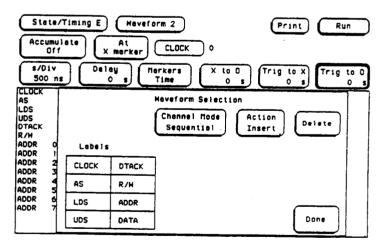

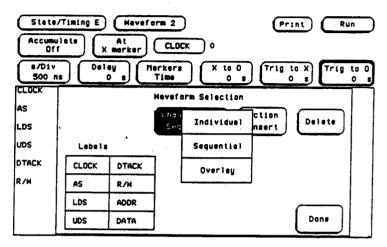

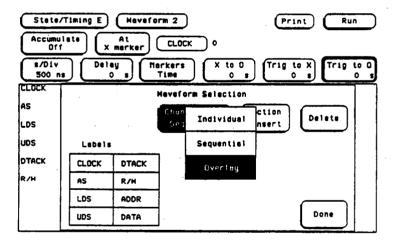

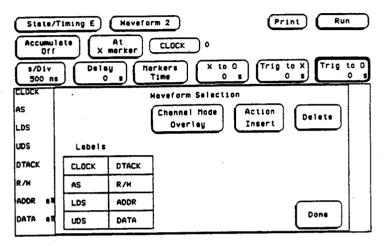

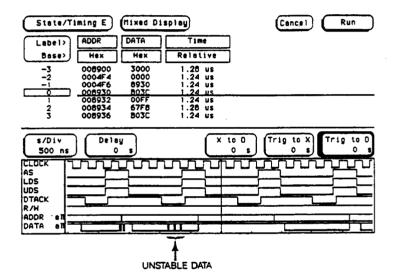

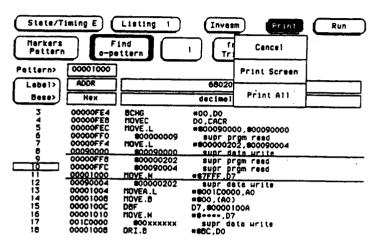

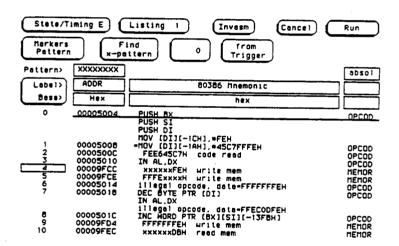

Figure 5-30. Run field pop-up Menu