# Keysight EEsof EDA GoldenGate RFIC Solutions

The Best-in-Class Circuit Simulation Solution for RFIC Design and Verification

#

# Introduction

GoldenGate is the most trusted simulation, analysis and verification solution available for integrated RF circuit design within Cadence Virtuoso. It is an integral part of Keysight Technologies, Inc. Silicon RFIC solution that also includes:

- ADS for small-scale RFIC front-to-back implementation

- Momentum and EMPro for on- and off-chip electromagnetic analysis

- SystemVue and Ptolemy wireless test benches for system-level verification

This suite of products links the RF system, subsystem, and component-level design and analysis as part of a unique and comprehensive RFIC design offering.

# GoldenGate Comprehensive RFIC Design and Verification Solution

GoldenGate offers unique simulation algorithms that enable full characterization of transceivers prior to tape-out. The industry's most advanced set of steady-state and envelope solvers allow design teams to confidently tackle even the most challenging radio designs. GoldenGate is seamlessly integrated into versions 5.x and 6.x of the Cadence Virtuoso design environment.

### GoldenGate RFIC Solutions– Powerful Simulation and More

**Best-in-class RF circuit simulator** provides the most advanced steady-state and envelope solvers for design and verification of RFICs within the Cadence Virtuoso environment.

Advanced analysis support offers a wide variety of capabilities to fully explore, analyze and optimize designs, before tape-out, minimizing the time and expense of re-spins.

Automation and usability features accelerate design and verification by providing a number of tools on top of ADE-L and ADE-XL

**RF to mm-Wave design support** provides the best performance, capacity and accuracy for RF to millimeter-wave (mm-Wave) applications.

Wireless standard-compliant design capability couples the power of systemand circuit-level simulators with a comprehensive library of standard-based wireless verification intellectual property (IP) to accelerate validation of complex RFICs.

### Figure 1.

While GoldenGate offers traditional analog simulators, it also goes beyond innovative RF simulation technology to provide a variety of solutions for designing, analyzing and verifying integrated RF circuits.

GoldenGate is the industry's best-in-class simulator, providing the most advanced steady-state and envelope solvers for design and verification of radios within the Cadence Virtuoso environment.

# Leading the Way in RF Circuit Simulation

Widely known for its advanced steadystate and envelope solvers, GoldenGate also provides a full set of analog and application-specific analyses. Additionally, GoldenGate supports X-parameter\* simulation and generation, which allows designers to capture the nonlinear behavior of active components in a standard format. X-parameters hide IP while enabling fast, accurate simulation within GoldenGate, ADS or SystemVue. GoldenGate also enables mixed-signal co-simulation between its transient and envelope transient analyses with thirdparty digital simulators — an especially critical capability given the increasingly mixed-signal and digital content of today's RFICs. Keysight EEsof EDA works closely with RFIC Foundries to ensure GoldenGate covers all relevant models and is continually qualified against new and updated process nodes to ensure silicon-accurate results.

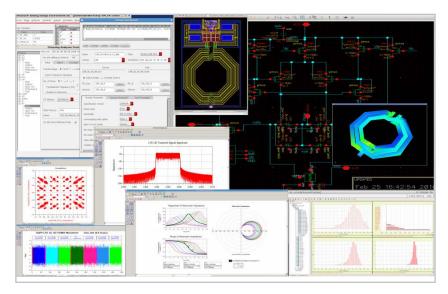

#### Figure 3.

GoldenGate is directly integrated within the Cadence Virtuoso environment to provide standard application development environment (ADE) functionality plus many unique RF capabilities.

Advanced analysis support Best-in-class RF circuit simulators GoldenGate Uterate and GoldenGate Uterate and Uteration and usability Wireless standardcompliant design

### **RFIC Circuit Simulation Overview**

- Unmatched Harmonic-Balance and Envelope-Transient analyses

- Steady-state solvers include: harmonic balance, time balance, time shooting, and hybrid solvers

- Envelope hybrid time-/frequency-domain nonlinear simulator

- Comprehensive set of analyses

- DC, AC, noise, S-parameters, transient

- Large-scale S-parameters, transient noise, sensitivity, as well as Bode, Nyquist and eigenvalue stability analyses

- Transistor-level integer-N PLL verification

- Intermodulation distortion and gain compression

- Keysight X-parameter support

- Mixed-signal co-simulation support

- Extensive foundry-verified model library

- HICUM, MEXTRAM, VBIC, BSIM, BSIMSOI, HISIM, GAASFETs, JFETs, and more

GoldenGate provides a full complement of analyses including X-parameter simulation and generation.

\* X-parameters is a trademark of Keysight Technologies. The X-parameter format and underlying equations are open and documented. For more information, visit: www.keysight.com/find/eesof-x-parameters-info

# Making Designs More Robust

GoldenGate features a suite of automation tools that enable design teams to quickly analyze and diagnose problem areas early in the design cycle, and fully optimize circuit performance. It also tightly integrates easy-to-use tools such as multidimensional sweeps, optimization and load-pull analysis. GoldenGate's broad range of powerful, easyto-use statistical tools helps pinpoint problems during the design phase. Advanced Monte Carlo algorithms speed trials while reducing the number required. Yield sensitivity histograms help identify critical design components. This information allows designers to make the design adjustments necessary to improve manufacturing yield. A Sensitivity analysis quickly allows insights on what parameters most strongly affect critical performances.

| nalysis                                       | Run List (CR)                                                |           |

|-----------------------------------------------|--------------------------------------------------------------|-----------|

| ⊕ DC<br>⊕ AC<br>⊕ SP<br>⊕ TR<br>⊕ PLL<br>⊖ CR | You are setting up analysis CR                               | Enabled [ |

|                                               | Enable Task Monte Carlo 💌                                    |           |

|                                               | Options Nominal Sweep Parallelism                            |           |

| Main<br>Options<br>Spec Var                   | Type Optimization<br>Monte Carlo                             |           |

| - Performance                                 | Regular Sensitivity      Boundary      Rerun                 |           |

| ⊡ LSSP<br>⊞- LSSP<br>⊞- GC                    | No. of Trials 100 Start From Number 1                        |           |

| ]- SSNA<br>]- IP<br>1. ET                     |                                                              |           |

| ⊕-ET<br>⊕-XP<br>⊕-ACSTAB                      | Options                                                      |           |

|                                               | Statistical Variation Seed 🔾 random 💿 specified 30105        |           |

|                                               | Max Wall Time (hr)                                           |           |

|                                               | Statistical Variation Type                                   |           |

|                                               | Process Enabled for  All Devices  List                       |           |

|                                               | Mismatch Enabled for    All Devices    List                  |           |

|                                               | • Both                                                       |           |

|                                               | Compute Correlations                                         |           |

|                                               | Save Trial Data 🔾 none 🖲 failures 🔾 all To File mctrials.txt |           |

|                                               | FYC 🗔                                                        |           |

| ~~~~                                          |                                                              |           |

| irtual Source 0                               |                                                              |           |

| /irtual Source 0                              |                                                              |           |

#### Figure 5.

The Choosing Analyses Form simplifies the setup of advanced analyses. The Task field provides access to a variety of multiple-run simulations including Monte Carlo analysis. Fast Yield Contributor (FYC) analysis is a unique capability which enables very fast computation of device-level contributions within Monte Carlo analysis.

### Advanced Analysis Overview

- Multi-dimensional sweeps with unmatched speed and convergence

- Fast yield and mismatch analyses for DC, AC, SP, SSNA, and CR with full contribution summary table

- Sensitivity analysis for CR, SSNA and DC analyses including sensitivity summary table

- Extensive load-pull setup and plotting capabilities

- Advanced Monte Carlo sampling algorithms

- Latin Hypercube

- Hammersley Sequence Sampling

- Boundary Mode and Orthogonal Arrays

- Fast yield and mismatch analyses for DC, AC, SP, SSNA, and CR

- Full contribution table

- Powerful optimization engine

- Digital state sweeping for operational mode performance, calibration and control sequences

- Unique transistor-level integer-N PLL simulator

- Steady-state circuit characteristics including deterministic noise

- Random jitter and noise with contributors

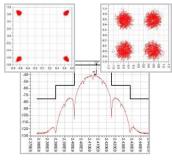

GoldenGate's distribution plots help identify components causing variation.

# Automation Tools for Accelerating the Design Cycle

**Best-in-class RF circuit simulators**

> Wireless standardcompliant design

Automation and usability

**RF to mm-Wave** design support

Advanced analysis support

GoldenGate

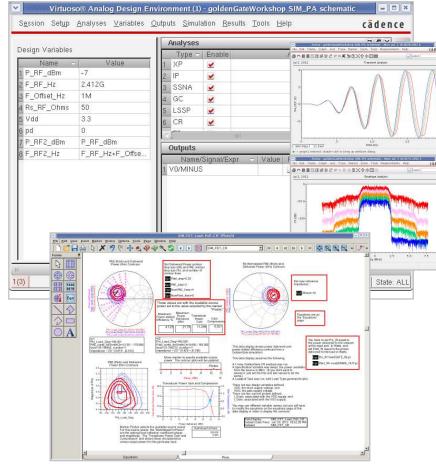

Design verification of today's RFICs can be tedious and time-consuming. GoldenGate accelerates this task with a number of powerful tools that allow designers to set up and run distributed simulations. These tools enable the quick analysis and display of massive amounts of data, and can be used within Virtuoso, operated separately or integrated with other third-party products.

GoldenGate offers a variety of post-processing solutions and functionality beyond support of the Cadence ADE plotting capabilities. The Performance Editor and ADS Data Display include large repositories of built-in expressions. Data Display's flexibility allows designers to create advanced plots (e.g., load-pull contours, gain circles or eye diagrams) or even write their own functions.

|                                                                                                     | ▼                                                                                                                                                                   | Choosing Analyses Form - GoldenGate0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                     | Analysis                                                                                                                                                            | Run List (ET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 7.<br>Job Manager allows designers to launch and<br>monitor multiple ADE states at one time. | B D DC<br>B AC<br>B AC<br>B SP<br>B PTR<br>B PLL<br>B CR<br>B SSNA<br>B GC<br>B SSNA<br>B P<br>E T<br>- Main<br>- Spec Var<br>- Spec Var<br>- Portrmance<br>- Taske | Vou are setting up analysis         EX         Enabled ≠           Name         ACPR, No.1xy, dB         Add. Change         Clear Det           Def         voldmu(TP_1, no.1xy, nby (0, 0, 0, 0, 1, 1920))         -voldmu(TP_1, no.1xy, nby (0, 0, 0, 0, 1, 1920))         -voldmu(TP_1, no.1xy, nby (0, 0, 0, 0, 1, 1920))           TP_T         T_1         T_2         No.1         -voldmu(TP_1, no.1xy, nby (0, 0, 0, 0, 1, 1920))         -voldmu(TP_1, no.1xy, nby (0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Job Manager                                                                                         | ⊕ XP<br>⊕ ACSTAB                                                                                                                                                    | V32. HINUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Window Simulation Results Help cādence                                                              |                                                                                                                                                                     | Analysis Spec. Probes Math Functions Transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| New Job Name     ET_WCDMA_MC     Add       Initialize New Job Directory from Current Job Directory  |                                                                                                                                                                     | Performance         Deales         Clobal         Performance         Deales           Prover, Bain, di-vo2dbar(PT, T. abc) (0.0         Disable         Disable |

| 3 SSNA_MC ready                                                                                     |                                                                                                                                                                     | OK Cancel Defaults Apply Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4 SSNA_Sweep_Blocker_Offset_and_P running                                                           | Figure 0                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5 ET_WCDMA_MC ready                                                                                 | Figure 8.                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Use the Performance Editor's built-in functions to calculate important figures-of-merit.

### Automation and Usability Overview

- Choosing Analyses Form Simplified setup plus direct access to multi-dimensional sweeps, optimization. Monte Carlo, or load-pull

- Job Manager Launch and monitor multiple ADE states simultaneously

- Sim Manager Environment beyond ADE to run multiple simulations

- Monte Carlo

- PVT corners

- Parallel sweeps on different machines

- Performance Editor Easily represent significant circuit metrics

- ADS Data Display Comprehensive plotting environment for wireless and wireline applications

- Automated Simulations Calculate EVM, ACPR, gain compression, IPN, and load-pull contours

- Virtuoso Integration Supports ADE-L and ADE-XL setup and post-processing capabilities

- Results Browser

- Calculator

- Wavescan

- ViVa

- Ocean

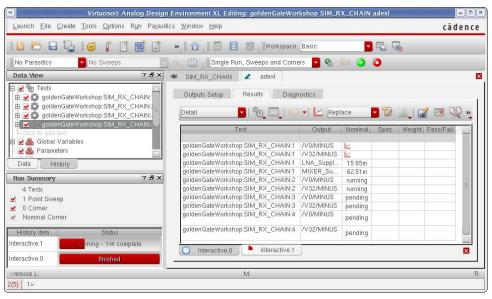

#### Figure 9.

GoldenGate supports the ADE-XL cockpit and also provides a variety of other tools to set up, launch and analyze parallel verification runs including corners

# Optimizing RFICs from RF to mm-Wave

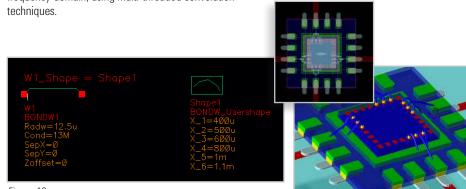

By leveraging the powerful ADS model library, GoldenGate accurately models the effects of integrating microwave components with silicon RFICs within the Cadence Virtuoso environment. Its transient and envelope-transient engines handle very large S-parameter blocks, beyond the frequency-domain, using multi-threaded convolution techniques. Tight links to the ADS common Open Access database allow designers to include IC content within the complete module design inside ADS or to perform more complete package characterization.

Figure 10. GoldenGate provides access from within Virtuoso to over 150 passive and distributed elements.

Figure 11. Perform end-to-end EM verification within the ADS platform and leverage unique capabilities like the ADS QFN Designer.

### RF to mm-Wave Design Overview

- Accurately model the effects of microwave components and parasitic elements on silicon or SiGe chips

- Momentum in Virtuoso enables siliconaccurate 3D planar EM simulation at nanometer scales

- Over 150 ADS models:

- Lines, bends, tees, and more

- Bond wires with coupling

- Other passive elements

- Tight links into ADS provide easy access to go beyond the IC

- ADS Data Display provides extensive plotting options

- Robust convolution engine ensures accurate results when using frequency-dependent components in a transient engine

## Integrated with the Momentum 3D Planar EM Simulator

### Popular 3D planar EM simulator:

- Advanced NlogN and multi-threading solver algorithms for optimal speed, accuracy and capacity

- Arbitrary polygonal meshing with reduction

- Thick metal analysis of sidewall currents and efficient via modeling account for skin and proximity effects

# Silicon-accurate nanometer RFIC process support:

- Automated layout pre-processing like via array merging

- Dummy metal fill and process scaling support

- Boolean layer operation for native MIM capacitor support

### Cadence Virtuoso integration:

- Seamlessly integrated into Cadence Virtuoso versions 5 and 6

- Broad PDK support for Momentum stack-up files and layout simplification routines

- 3D Viewer with embedded visualization of surface currents or radiated fields

- Broadband SPICE Model generation for efficient time-domain simulation

### Going beyond 3D planar:

- Fast, direct bond wire support

- Through Silicon Via modeling support

- Virtuoso export to EMPro for full 3D EM simulations

# Assuring System-Level to Circuit-Level Wireless-Standard Compliance

GoldenGate features links to system-level analysis-from architectural exploration up to full co-simulation with data flow engines-for verification of the complex measurements required by today's wireless standards. These scalable links support various levels of interaction ranging from simple input/output file exchange to powerful integration with Keysight test equipment, ADS Ptolemy and SystemVue.

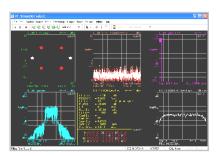

Figure 12 Links with SystemVue provide access to Keysight's powerful VSA instrument software

#### Figure 13.

GoldenGate lets designers investigate the impact of blockers on system-level metrics directly in Virtuoso.

### Wireless Standard Compliance Overview

- Full radio functionality verification using Keysight's extensive standard-compliant wireless libraries through scalable links to test equipment and ESL platforms

- Multiple links with SystemVue

- Fast Circuit-Envelope (FCE) model export to **SystemVue**

- Full GoldenGate SystemVue co-simulation

- Pre-configured standard-compliant Verification Test Benches (VTBs)

- Access to ADS-Ptolemy test benches for co-verification

- Links to Keysight test equipment

- Stimuli creation through Signal Studio

- Standard-compliant post-processing in Keysight's Vector Signal Analyzer (VSA) software

- Avoid overdesigning RFICs

- Impairments of "as designed" RFICs visible to system engineer

- Low barrier for RF verification engineer to access standard-compliant modulated signals

# SystemVue Links with RFIC Implementation

11010

1010

11010

### SystemVue overview:

- Complete ESL design environment

- Enables system architects and algorithm developers to innovate wireless and communication systems physical layers (PHYs)

### SystemVue wireless library support:

Adjust input signal magnitude NomGain -15

123

- Standard-based baseband PHY libraries covering all emerging standards (e.g., LTE, LTE-Advanced, 3G, WiMAX<sup>™</sup>, WLAN, WPAN, DVB-x2, and Radar)

- Includes full access to reference blocksets and application examples for OFDM and ZigBee

### Links to GoldenGate:

- Complete co-simulation

- Pre-configured standard-compliant Verification Test Benches (VTBs)

- FCE model export for accurate modeling of RF impairments in system-level verification

8

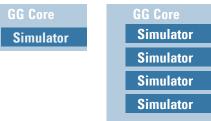

# GoldenGate Product Configuration

### **GoldenGate Core Bundles**

GoldenGate Solo is the baseline product providing one user one simulation per license. GoldenGate Quadpack, for Power Users, offers one user four simulations per license.

Most GoldenGate functionalities are covered by the core bundles with only X-parameter generation and co-simulations requiring additional licenses.

#### W2010 GoldenGate Solo

### W2001 GoldenGate Quad

### **GoldenGate Add-on Elements**

GoldenGate offers cost-effective parallel licenses for running massive parallel simulations. It requires either a Solo or Quad license. The X-parameter Generation license for GoldenGate is the same as for ADS.

| W2008 | GoldenGate Parallel Simulator |

|-------|-------------------------------|

| W2305 | X-Parameter Generator Element |

### **GoldenGate Co-Simulation Elements**

GoldenGate allows co-simulation with the Ptolemy and SystemVue data flow engines, as well as third-party digital simulators, via the following licenses:

| W2304 | Verilog-AMS Element           |

|-------|-------------------------------|

| W2361 | Ptolemy Element               |

| W1464 | SystemVue RF System Architect |

Note: Please refer to the ADS-Ptolemy and SystemVue product pages for details on numerous wireless libraries.

### **Momentum Elements and Bundles**

Access to Momentum in Virtuoso is enabled through one of the following licenses:

| W2341 | Momentum Element           |

|-------|----------------------------|

| W2203 | ADS Core, Layout, Momentum |

### **GoldenGate Co-Simulation Elements**

GoldenGate/ADS Combo Bundles provide flexible access to a variety of Keysight EEsof EDA GoldenGate/ADS Combo Bundlesare working in.

| W2218 | GoldenGate Solo, ADS Core & Circuit Sim          |

|-------|--------------------------------------------------|

| W1112 | GoldenGate Quad, ADS Core, Circuit Sim,          |

|       | Layout, Momentum, Ptolemy                        |

| W2013 | GoldenGate Quad, ADS Core, Circuit Sim,          |

|       | Layout, Momentum, Ptolemy, Matured Wireless Libs |

WiMAX, Mobile WiMAX, WiMAX Forum, the WiMAX Forum logo, WiMAX Forum Certified, and the WiMAX Forum Certified logo are US trademarks of the WiMAX Forum.

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

#### Americas

| Canada        | (877) 894 4414   |

|---------------|------------------|

| Brazil        | 55 11 3351 7010  |

| Mexico        | 001 800 254 2440 |

| United States | (800) 829 4444   |

| Asia Pacific  |                  |

#### Australia 1 800 629 485 China 800 810 0189 Hong Kong 800 938 693 India 1 800 112 929 Japan 0120 (421) 345 Korea 080 769 0800 1 800 888 848 Malaysia 1 800 375 8100 Singapore Taiwan 0800 047 866 Other AP Countries (65) 6375 8100

#### Europe & Middle East

United Kingdom

For other unlisted countries: www.keysight.com/find/contactus (BP-07-10-14)

Opt. 3 (IT)

0800 0260637

#### www.keysight.com/find/goldengate

This information is subject to change without notice. © Keysight Technologies, 2012–2014 Published in USA, September 3, 2014 5989-9484EN www.keysight.com