# Keysight J-BERT M8020A High-Performance BERT

Data Sheet Version 1.5

## Description

The high-performance Keysight Technologies, Inc. J-BERT M8020A enables fast and accurate receiver characterization of single- and multi-lane devices running up to 16 or 32 Gb/s.

With today's highest level of integration, the M8020A streamlines your test setup. In addition, automated in situ calibration of signal conditions ensures accurate and repeatable measurements. And, through interactive link training, it can behave like your DUT's link partner. All in all, the J-BERT M8020A will accelerate insight into your design.

## Key features:

- Data rates up to 8.5 and 16 Gb/s expandable to 32 Gb/s

- 1 to 4 BERT channels in a 5-slot AXIe chassis

- Integrated and calibrated jitter injection: RJ, PJ1, PJ2, SJ, BUJ, sinusoidal level interference (common-mode and differential-mode), SSC (triangular and arbitrary, residual) and Clock/2

- 8 tap de-emphasis, positive and negative

- Interactive link training for PCI Express

- Built-in clock recovery and equalization

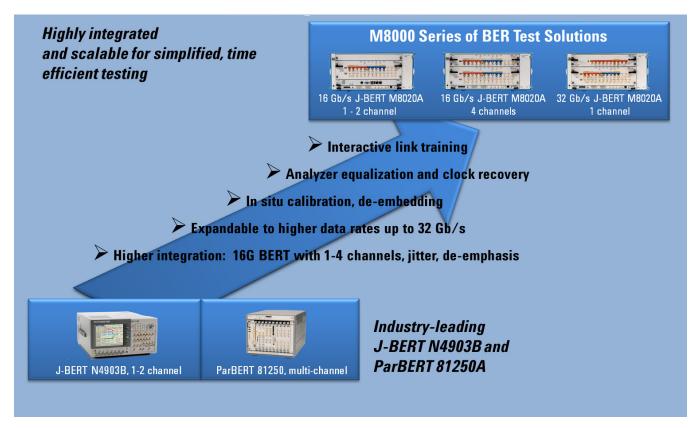

## M8000 Series of BFR Test Solutions

Simplified time-efficient testing is essential when you are developing next-generation computer, consumer, or communication devices.

The Keysight M8000 Series is a highly integrated BER test solution for physical layer characterization, validation, and compliance testing.

With support for a wide range of data rates and standards, the M8000 Series provides accurate, reliable results that accelerate your insight into the performance margins of high-speed digital devices.

Shift into high gear with the M8000 Series and take the design verification express lane.

Figure 1. The M8000 Series BER Test Solution is highly integrated and scalable to address the test challenges of the next generation of high-speed digital receiver test.

## J-BERT M8020A high-performance BERT

Enabling fast, accurate receiver characterization of single- and multi-lane devices running up to 16 or 32 Gb/s.

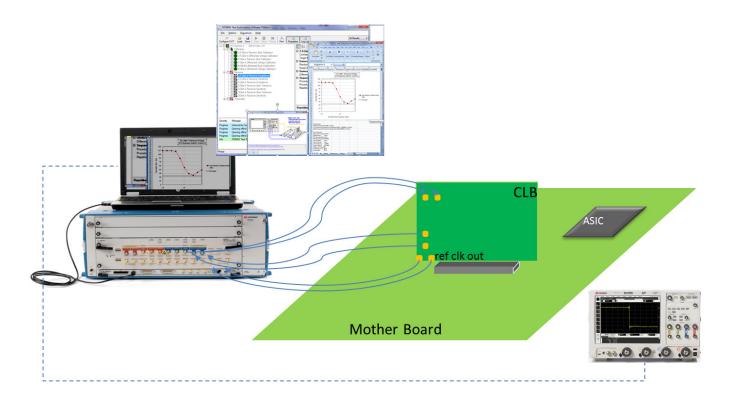

## Highest level of integration for streamlined test setups

With J-BERT M8020A all receiver (RX) test capabilities are built-in: jitter sources, "common- and differential-mode level interference, and de-emphasis to emulate the transmitter (TX) of the device under test (DUT). In addition M8020A provides a built-in reference clock multiplier for synchronization of the BERT pattern generator with the DUT's reference clock which can carry spread spectrum clocking (SSC). On the analyzer side an equalizer to open closed eyes and a clock recovery with adjustable loop bandwidth for the analyzer is built-in.

With this high level of integration a receiver test set-up with M8020A is now much easier to connect and more robust. Set up and debug time is shortened, calibration is simpler and the frequency of recalibration is lower, resulting in more efficient use of overall test time.

Figure 2: J-BERT M8020A streamlines complex receiver test setups. The example shows a PCIe 3 (8 GT/s) mother board RX test (CEM spec) with J-BERT M8020A connected via a compliance load board (CLB). J-BERT M8020A provides built-in de-emphasis, jitter sources, common-mode and differential mode interference (CMI, DMI), reference clock multiplier, clock recovery and continuous time linear equalizer (CTLE) – everything that is needed is built-in and calibrated.

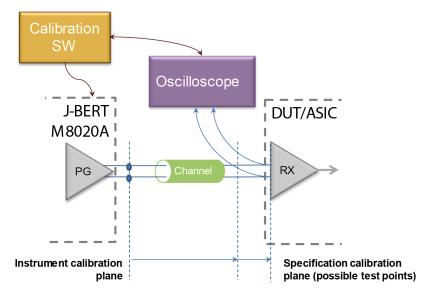

#### In situ calibration for the most accurate and repeatable results

At data rates above 5 Gb/s, the influence of the channel (PC-board, cable, connectors) between transmitter (TX) and receiver (RX) is no longer negligible. The reference point for the RX specification moves to the RX input, the test set-up typically has to contain a certain channel characteristic, often an ISI channel, as well. To accurately inject a defined stress condition to the RX in situ calibration is required: at that same exact point where the receiver under test has to be connected during test, a reference load is connected instead and the generated signal is measured. This allows calibration of the test signal at that point where the specification applies by adjusting the instrument generated stress such as jitter in a way that the target signal with all its ingredients is achieved.

Figure 3: With increasing bit rates the calibration plane for the receiver stress conditions moves closer to the receiver inputs. J-BERT M8020A supports in situ calibration to achieve higher accuracy of the signal and stress conditions at the relevant definable test point.

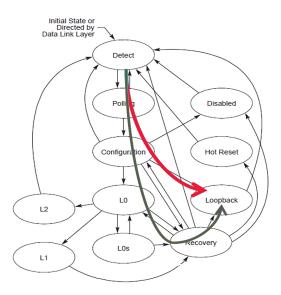

#### Interactive link training to fasten loopback

The ever increasing data rate of computer buses and datacom interfaces results in shrinking margins and the necessity to use equalization techniques in transmitters and receivers to compensate for the lossy channels caused by inexpensive PC board material or long cables. For the latest industry standards, such as PCI Express 3 or 4, SAS 12G, and backplanes such as 100GBASE-KR4, the link partners are required to optimize the TX de-emphasis and RX equalization combination. The RX takes the active part during this procedure. In order to do so, the BERT must be capable to understand the low level protocol and to react accordingly, i.e. change its TX de-emphasis as requested. J-BERT M8020A can behave like a real link partner with its interactive link training capability, initially PCIe is supported.

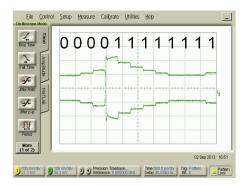

Figure 4: J-BERT M8020A can behave like a real link partner. Due to its interactive link training capability it is able to train the device into the loopback state via recovery state, as shown in this example for PCIe.

## Overview J-BERT M8020A High-performance BERT

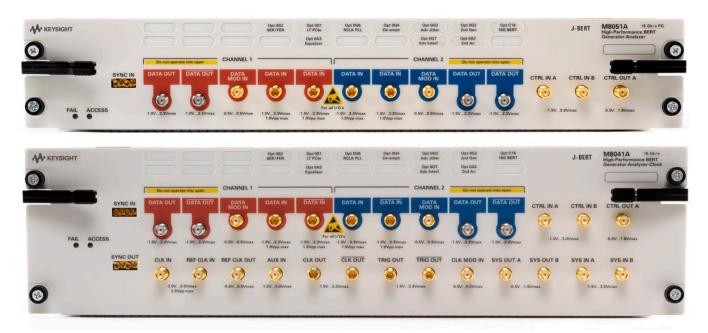

Figure 5: J-BERT M8020A high-performance BERT for accelerated receiver characterization. The configuration shows a 4 channel 16 Gb/s BERT in a 5-slot AXIe chasssis consisting of one M8041A module with two BERT channels and clock synthesizer and one M8051A extender module with two additional BERT channels

#### **Applications**

R&D and test engineers who characterize and verify compliance of chips, devices, boards and systems with serial I/O ports up to 16 Gb/s. The M8020A can be used to test popular serial bus standards, such as PCI Express®, SATA/SAS, DisplayPort, USB Super Speed, MIPI M-PHY, SD UHS-II, Fibre Channel, QPI, memory buses, backplanes, repeaters, active optical cables, Thunderbolt, 10 GbE/SFP+, 100GbE/CFP2.

#### Receiver characterization and compliance test

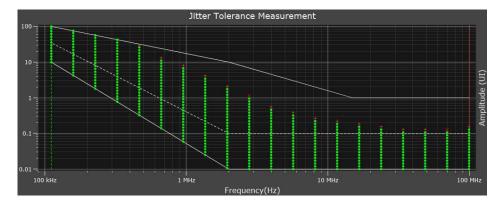

Most multi-gigabit digital interfaces define a receiver tolerance test where the receiver must detect the incoming data bits properly while a certain amount of stress is applied. J-BERT M8020A provides calibrated and built-in jitter sources and automated jitter tolerance measurements. Users can define the modulation frequency range, the number of frequency steps, the min. and max. applied jitter, BER and confidence level and relax time. Results can be exported.

Figure 6: J-BERT M8020A provides automated jitter tolerance characterization and compliance measurements. A library of Jitter tolerance templates is available. To opimze test time, customized jitter tolance templates can be created with a graphical jitter tolerance template editor. The red dots in the result screen show where the BER level was exceeded, the green dots show where the DUT tolerated the received jitter.

#### Emulate de-emphasis and compensate for channel loss

Most serial interfaces that operate above 5 Gb/s use transmitters with de-emphasis to compensate for electrical signal degradations caused by printed circuit boards or cables between the transmitter and the receiver ports. R&D and test engineers who need to characterize receiver ports under realistic and worst case conditions require a pattern generator that allows to accurately emulate transmitter de-emphasis and the channel with adjustable 8-tap de-emphasis levels.

Figure 7: J-BERT M8020A provides built-in de-emphasis with up to 8 taps to emulate a transmitter de-emphasis and to compensate for channel loss. The example shows a bit sequence of eight "0"s and eight "1"s with two pre-cursors and 5 post-cursors that can be adjusted individually.

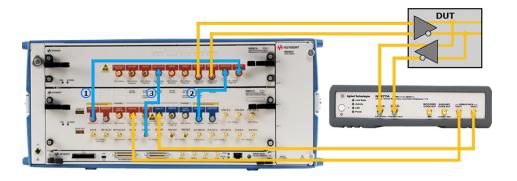

#### J-BERT M8020A configuration for 32 Gb/s

The J-BERT M8020A can be configured as a full 32 Gb/s BERT for accurate receiver characterization. It provides built-in jitter sources, up to 8-tap de-emphasis, and a clock recovery for full-sampling BER and jitter tolerance measurements up to 32 Gb/s. One common user interface allows controlling all parameters of the 32 Gb/s pattern generator and analyzer.

Key features of the 32 Gb/s BERT configuration:

- Excellent intrinsic jitter performance

- Calibrated jitter sources up to 1 UI eye closure for HF jitter, multi -UI LF jitter, BUJ and Clk/2 jitter

- No step increase when turning on jitter sources

- 8 tap de-emphasis with positive and negative cursors

- Superposition of level interference avoids external adders

- Clock recovery with adjustable loop bandwidth

- Add-on to 16 Gb/s BERT configuration

- Common user interface

(1) M8041A DATA OUT 1 -> M8061A DATA IN 1 (2) M8041A DATA OUT 2 -> M8061A DATA IN 2 (3) M8041A CLK OUT -> M8061A AUX CLK IN N4877A DUMUX DATA OUT1 -> M8041A DATA IN 1 N4877A DUMUX DATA OUT2 -> M8041A DATA IN 2

Figure 8: The J-BERT M8020A can be configured as a full 32 Gb/s BERT for accurate receiver characterization. A two channel M8041A BERT can be extended with the M8061A multiplexer and the N4877A CDR/de-multiplexer to data rates up to 32 Gb/s.

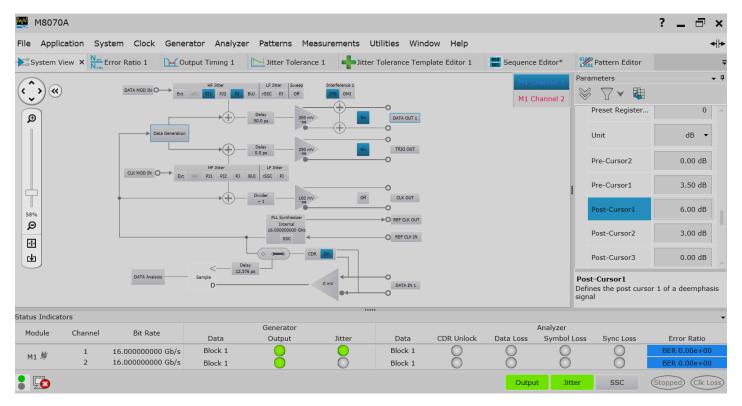

#### User interface and measurements

Figure 9: The graphical user interface for J-BERT M8020A offers multiple views that can be defined by the user. This example shows the system view on left side and the pattern generator data output parameters at the right.

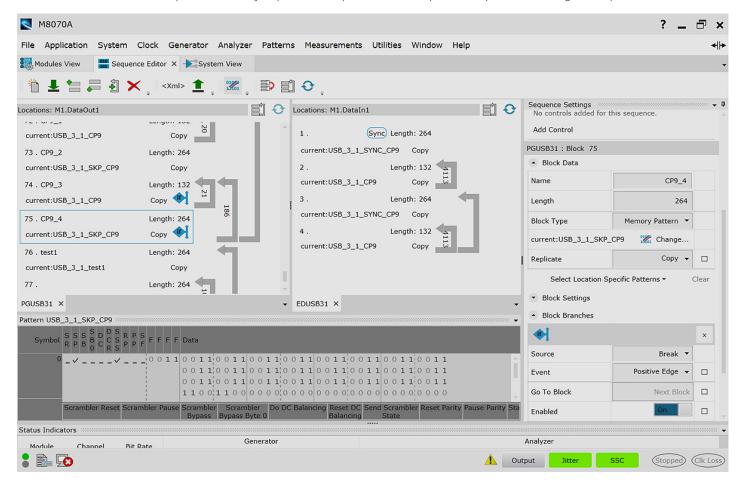

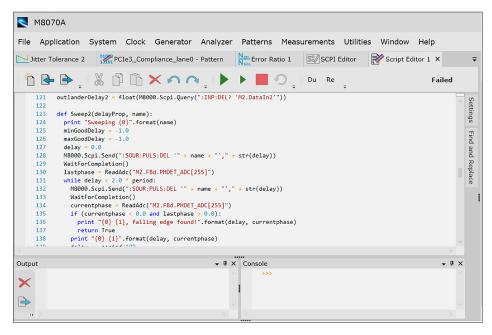

## Pattern sequencer, coding and interactive link training

To simplify test pattern creation, J-BERT M8020A provides unique tools such as an interactive link training state machine, pattern sequencer with break and branch conditions, a real-time scrambler for coded patterns, masking, symbol filtering for meaningful BER measurements for retimed loop back, a library of pre-defined patterns and loop-back sequences, and a grahical pattern editor.

Figure 10: The J-BERT M8020A provides powerful pattern sequencing capabilities. For each pattern generator and analyzer channel a pattern sequence with multiple loop levels, breaks and bock controls can be defined. A library of link training sequences for popular standards is available. The example shows a USB 3.1 link training sequence.

Figure 11: The interactive link training capability of J-BERT M8020A significantly reduces the effort to generate and tune a loopback sequence for your device under test. The example shows the properties you can choose for the PCIe3 link training state machine.

## Accuracy and performance

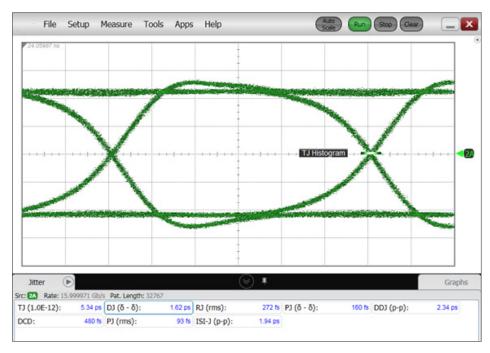

Figure 12: Clean 16.0 Gb/s output signal of J-BERT M8020A with M8041A BERT module using its internal clock source and PRBS 2  $1_5$ -1 pattern.

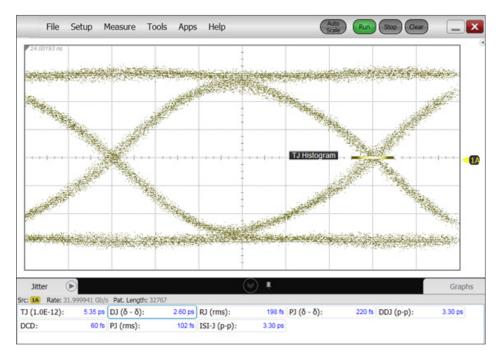

Figure 13: The 32 Gb/s output signal shows excellent intrinsic jitter. This shows the output signal of M8061A when used with M8041A BERT module and its internal clock source and PRBS 2  $^{15}$ –1 pattern, and the band pass filter M8061A–803 in the clock path.

## Specifications for M8041A and M8051A J-BERT high-performance BERT modules

Figure 14: Front panel view of M8041A module (bottom) and M8051A (top).

## Specification for M8061A

Please refer to M8061A data sheet (5991-2506EN) for specification details.

## Specifications pattern generator

## Data output (DATA OUT 1, DATA OUT 2)

Table 1. Data output characteristics for M8041A and M8051A.

| All timing parameters are measur     |                                                                                            | M8041A | M8051A |

|--------------------------------------|--------------------------------------------------------------------------------------------|--------|--------|

| Data rate                            | 256 Mb/s to 8.50 Gb/s (opt. G08 or C08),                                                   | Χ      | Χ      |

|                                      | 256 Mb/s to 16.20 Gb/s (opt. G16 or C16)                                                   | _      |        |

| Data format                          | NRZ                                                                                        | _      |        |

| Channels per module                  | 1 or 2 (second channel requires opt. OG2)                                                  | _      |        |

| Amplitude                            | 50 mV to 1.2 Vpp single ended,                                                             |        |        |

|                                      | 100 mV to 2.4 Vpp differential,                                                            |        |        |

|                                      | 1 mV resolution;                                                                           |        |        |

|                                      | addresses LVDS, CML, low-voltage CMOS, others.                                             |        |        |

|                                      | See table 2 for max. output amplitude in presence of CMI or DMI                            | _      |        |

| Amplitude accuracy                   | $5\% \pm 5$ mV typical (AC) <sup>3</sup>                                                   | _      |        |

| Output voltage window                | -1 V to +3.0 V                                                                             | _      |        |

| External termination voltage         | -1 V to +3.0 V. For offset > 1.3 V the termination voltage should be $\pm$ 0.5 V of offset | _      |        |

| Transition time                      | 15 to 20 ps typical (20%-80%)                                                              | _      |        |

| Crossing point                       | Adjustable from 30% to 70%                                                                 | _      |        |

| Intrinsic total jitter <sup>1</sup>  | 8 ps p-p typical                                                                           | _      |        |

| Intrinsic random jitter <sup>2</sup> | 300 fs rms typical                                                                         | _      |        |

| Data delay range                     | 0 to 10 ns, resolution 100 fs                                                              |        |        |

| Data delay accuracy                  | ± 1% ± 20 mUI typical <sup>5</sup>                                                         |        |        |

| Deskew accuracy                      | ± 10 ps typical between data out 1 and 2 of the same module                                |        |        |

| Electrical idle transition time      | Output transitions from full swing signal to 0 V amplitude and vice versa at constant      |        |        |

|                                      | offset within 4 ns typical. Electrical idle can be controlled from sequencer. Latency      |        |        |

|                                      | is TBD.                                                                                    | _      |        |

| Termination                          | $50~\Omega$ into GND or external termination voltage.                                      |        |        |

|                                      | Do not operate into open. Unused outputs must be terminated into termination               |        |        |

|                                      | voltage.                                                                                   | _      |        |

| Output protection                    | This is an emergency shut down feature. It disables an output in case an unexpect-         |        |        |

|                                      | ed voltage is detected.                                                                    |        |        |

|                                      | DC coupling mode:                                                                          |        |        |

|                                      | Termination range for devices connected to data out:                                       |        |        |

|                                      | – unbalanced $50 \Omega \pm 10 \Omega$ typical                                             |        |        |

|                                      | – balanced 100 $\Omega$ ± 20 $\Omega$ typical                                              |        |        |

|                                      | Operation into open is possible for these ranges when "DC coupled" and "balanced"          |        |        |

|                                      | termination modes are selected:                                                            |        |        |

|                                      | <ul> <li>output amplitude max. 300 mV <sup>4</sup></li> </ul>                              |        |        |

|                                      | <ul><li>offset 0 to 270 mV</li></ul>                                                       |        |        |

|                                      | AC coupling mode:                                                                          |        |        |

|                                      | An external DC blocking capacitor is expected. If a resistive load is discovered the       |        |        |

|                                      | output will not be enabled.                                                                | _      |        |

| Termination modes                    | Balanced/unbalanced                                                                        |        |        |

|                                      | DC/AC coupling                                                                             | _      |        |

| Connectors                           | 3.5 mm, female                                                                             |        |        |

<sup>1.</sup> At 16.2 Gb/s PRBS 2  $^{15}$ –1, BER 10  $^{-12}$ , with internal clock.

<sup>2.</sup> At 16 Gb/s and clock pattern.

At 256 Mb/s measured with DCA-X 86108B and clock pattern and in the middle of the eye.

Per output when differentially terminated into 100 Ω. Results in doubled swing when driving into open.

At constant temperature.

## Specifications pattern generator (continued)

## Data output (DATA OUT 1, DATA OUT 2) (continued)

Table 2. Data output amplitude maximum (single ended) in presence of DMI, CMI, offset voltage.

| Offset ≤ 1.9 V | Offset > 1.9 V | СМІ      | DMI                  |

|----------------|----------------|----------|----------------------|

| 1.2 Vpp        | 0.9 Vpp        | disabled | disabled             |

| 0.9 Vpp        | 0.675 Vpp      | disabled | enabled              |

| 0.9 Vpp        | 0.75 Vpp       | enabled  | disabled             |

| 0.675 Vpp      | 0.562 Vpp      | enabled  | enabled              |

| 0.8 Vpp        | 0.666 Vpp      | enabled  | enabled <sup>1</sup> |

<sup>1.</sup> For DMI < 12.5 % of amplitude.

## De-emphasis (DATA OUT)

M8020A provides built-in de-emphasis with positive and negative cursors based on a finite impulse response (FIR) filter.

Table 3. Specifications for multi-tap de-emphasis (requires option 0G4).

| '                          | The second secon | M8041A   | M8051A   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| De-emphasis taps           | 8 (requires opt. 0G4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | opt. 0G4 | opt. 0G4 |

|                            | can be adjusted for each channel independently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |          |

| Pre-cursor 2               | ± 6.0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |          |

| Pre-cursor 1               | ± 12.0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |          |

| Post-cursor 1              | ± 20.0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |          |

| Post-cursor 2              | ± 12.0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |          |

| Post-cursor 3              | ± 12.0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |          |

| Post-cursor 4              | ± 6.0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |          |

| Post-cursor 5              | ± 6.0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |          |

| De-emphasis tap resolution | ± 0.1 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |          |

| De-emphasis tap accuracy   | ± 1.0 dB <sup>1</sup> typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |

1. Sum of all cursors may not exceed Vpp max. The tap accuracy applies for PCIe 3 presets for pre-cursor 1 and post-cursor 1 at 8 Gb/s.

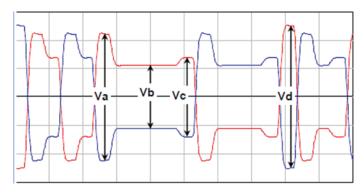

Post-cursor  $1 = 20\log_{10} Vb/Va$ Pe-cursor  $= 20\log_{10} Vc/Vb$ Vpp nominal  $= 20\log_{10} Vd$

Figure 15. Definition of nominal output amplitude and de-emphasis.

## Specifications pattern generator (continued)

## Clock output (CLK OUT)

Table 4. Clock output specifications

|                              |                                                                                                   | M8041A | M8051A |

|------------------------------|---------------------------------------------------------------------------------------------------|--------|--------|

| Frequency range              | 256 MHz to 8.50 GHz (opt. G08 or C08),                                                            | Х      | no clk |

|                              | 256 MHz to 16.20 GHz (opt. G16 or C16)                                                            | _      |        |

| Frequency resolution         | 1 Hz                                                                                              | _      |        |

| Frequency accuracy           | ± 15 ppm                                                                                          | _      |        |

| Amplitude                    | 0.1 to 1 V, 5 mV steps, single ended                                                              | _      |        |

| Output voltage window        | -1 V to +3 V <sup>1</sup>                                                                         | _      |        |

| External termination voltage | -1 V to +3.0 V                                                                                    | _      |        |

| Transition times             | 20 ps typical (20%-80%)                                                                           | _      |        |

| Duty cycle                   | 50%, accuracy ± 15%                                                                               | _      |        |

| Clock divider                | 1, 2, 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80.                                           |        |        |

|                              | For other dividers use TRG output                                                                 | _      |        |

| Clock modes                  | See table 5                                                                                       |        |        |

| Intrinsic random jitter      | 300 fs rms typical at 16.2 GHz and clock divider = 1                                              |        |        |

| SSB phase noise <sup>2</sup> | - 85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100MHz as exter-                  | _      |        |

|                              | nal reference clock.                                                                              |        |        |

|                              | <ul> <li>80 dBc/Hz with 10 kHz offset for reference clock multiplier bandwidth 0.1/2/5</li> </ul> |        |        |

|                              | MHz                                                                                               | _      |        |

| Termination                  | $50\Omega$ into GND or external termination voltage. Do not operate into open. Unused             |        |        |

|                              | outputs must be terminated into termination voltage.                                              | _      |        |

| Connectors                   | 3.5 mm, female                                                                                    |        |        |

If V<sub>term</sub> is other than 0 V the following applies:

High level voltage range= 2/3 \* V<sub>term</sub> - 0.95 V < HIL < V<sub>term</sub> + 2 V

Low level voltage range= 2/3 \* V<sub>term</sub> - 1 V < LOL < V<sub>term</sub> + 1.95 V

For 8.1 to 16.2 GHz clocks.

Table 5. Clock modes (M8041A only).

| Clock mode                                                | Clock generation                                        | Input frequency range |                     |        |

|-----------------------------------------------------------|---------------------------------------------------------|-----------------------|---------------------|--------|

|                                                           |                                                         | Option G08/ C08       | Option G16/ C16     | Option |

| Reference                                                 | PLL with bandwidth below 1 kHz                          | 10/100 MHz            | 10/100 MHz          |        |

| Direct                                                    | No PLL                                                  | 8.1 GHz to 8.5 GHz    | 8.1 GHz to 16.2 GHz |        |

| Reference clock multiplier bandwidth 100 kHz              | m/n PLL with loop bandwidth 100 kHz<br>m, n = 1 to 1620 | 10 MHz to 8.5 GHz     | 10 MHz to 16.2 GHz  |        |

| Reference clock multiplying PLL with loop bandwidth 2 MHz | Integer PLL with loop bandwidth 2 MHz <sup>1</sup>      | 10 to 105 MHz         | 10 to 105 MHz       | 0G6    |

| Reference clock multiplying PLL with loop bandwidth 5 MHz | Integer PLL with loop bandwidth 5 MHz <sup>1</sup>      | 50 to 105 MHz         | 50 to 105 MHz       | 0G6    |

<sup>1.</sup> Intended use with settings in Table 7 (other settings may be possible, contact factory)

## Specifications pattern generator (continued)

## Reference clock input (REF CLK IN)

This input on the M8041A module allows locking the system clock to an external reference clock of 10 or 100 MHz instead of the internal oscillator. It also allows to use an external clock, see clock modes.

Table 6. Reference clock input specifications (M8041A only).

|                 |                                                                     | M8041A      | M8051A |

|-----------------|---------------------------------------------------------------------|-------------|--------|

| Input amplitude | 0.2 to 1.4 Vpp                                                      | Χ           | no     |

| Input frequency | 10 MHz to 16.2 GHz, depends on clock mode and max. data rate option |             |        |

| Interface       | Single ended. $50 \Omega$ nominal                                   | <del></del> |        |

| Connector       | SMA, female                                                         |             |        |

Table 7. Predefined settings for reference clock multiplier (M8041A with option 0G6 only).

| Ref clock input   | Standard        | Target data rate              | Multiplier  | PLL loop BW | M8041A |

|-------------------|-----------------|-------------------------------|-------------|-------------|--------|

| 100 MHz           | PCIe 4          | 16 Gb/s                       | 160         | 2 MHz       | 0G6    |

| 100 MHz           | PCIe 3          | 8 Gb/s                        | 80          | 5 MHz       |        |

| 100 MHz           | PCIe 2          | 5 Gb/s                        | 50          | 5 MHz       |        |

| 100 MHz           | PCIe 1          | 2.5 Gb/s                      | 25          | 5 MHz       |        |

| 26 MHz to 52 MHz  | SD UHS-II       | 390 Mb/s to 780 Mb/s          | 15          | 2 MHz       |        |

| 26 MHz to 52 MHz  | SD UHS-II       | 780 MHz to 1.56 Gb/s          | 30          | 2 MHz       |        |

| 52 MHz to 104 MHz | SD UHS-II Gen 2 | 1.56 Gb/s to 3.12 Gb/s        | 30          | 2 MHz       |        |

| 52 MHz to 104 MHz | SD UHS-II Gen 2 | 3.12 Gb/s to 6.24 Gb/s        | 60          | 2 MHz       |        |

| 19.2 MHz          | MIPI M-PHY      | 1.248/ 1.4592/ 2.496/ 2.9184/ | 65/76/130/  | 2 MHz       |        |

|                   |                 | 4.992/5.8368 Gb/s             | 152/260/304 |             |        |

| 26 MHz            | MIPI M-PHY      | 1.248/ 1.456/ 2.496/ 2.912/   | 48/56/96/   | 2 MHz       |        |

|                   |                 | 4.992/5.824 Gb/s              | 112/192/224 |             |        |

| 38.4 MHz          | MIPI M-PHY      | 1.248/ 1.4592/ 2.496/ 2.9184/ | 65:2/38/65/ | 2 MHz       |        |

|                   |                 | 4.992/5.8368 Gb/s             | 76/130/152  |             |        |

| 52 MHz            | MIPI M-PHY      | 1.248/ 1.456/ 2.496/ 2.912/   | 24/ 28/ 48/ | 2 MHz       |        |

|                   |                 | 4.992/5.824 Gb/s              | 56/96/112   |             |        |

## Supplementary inputs and outputs of M8041A and M8051A

## Trigger output (TRG OUT)

The trigger output can be used in different modes:

- 1. Divided clock, dividers: 2 to 65535

- 2. Sequence block trigger with adjustable pulse width and offset

- 3. PRBS sequence trigger with adjustable pulse width

Table 8. Trigger output specifications (M8041A only).

|                              |                            | M8041A | M8051A |

|------------------------------|----------------------------|--------|--------|

| Amplitude                    | 0.1 to 1 Vpp single ended; | Х      | no trg |

|                              | 0.2 to 2 Vpp differential  |        |        |

| Output voltage window        | -1 to 3 V <sup>1</sup>     |        |        |

| External termination voltage | -1 to 3 V                  |        |        |

| Interface                    | Differential, $50 \Omega$  |        |        |

| Connector                    | 3.5 mm, female             |        |        |

1. If  $V_{\text{term}}$  is other than 0 V the following applies: High level voltage range=  $2/3 * V_{\text{term}} - 0.95 \text{ V} < \text{HIL} < V_{\text{term}} + 2 \text{ V}$ Low level voltage range=  $2/3 * V_{\text{term}} - 1 \text{ V} < \text{LOL} < V_{\text{term}} + 1.95 \text{ V}$

## Reference clock output (REF CLK OUT)

Outputs a 10 MHz clock, 1 Vpp single ended into 50  $\Omega$ . M8041A only.

Connector: SMA, female.

#### Clock input (CLK IN)

For future use. For M8041A only. See reference clock input for direct clock mode.

## Control input A and B (CTRL IN A, CTRL IN B)

Functionality of each input can be selected as: sequence trigger, error add input.

Table 9. Control input specifications (M8041A and M8051A).

|                     |              | M8041A | M8051A |

|---------------------|--------------|--------|--------|

| Input voltage       | -1 V to +3 V | X      | X      |

| Termination voltage | -1 V to +3 V |        |        |

| Threshold voltage   | -1 V to +3 V |        |        |

| Connector           | SMA, female  |        |        |

#### Control output A (CTRL OUT A)

Outputs a pulse in case of an error.

Table 10. Control output specifications (M8041A and M8051A).

|                             |                | M8041A | M8051A |

|-----------------------------|----------------|--------|--------|

| Amplitude <sup>1</sup>      | 0.1 to 2 V     | Х      | X      |

| Output voltage <sup>1</sup> | -0.5 to 1.75 V |        |        |

| Connector                   | SMA, female    |        |        |

1. When terminated with 50  $\Omega$  into GND. Doubles into open.

## Supplementary inputs and outputs of M8041A and M8051A (continued)

## Synchonization input and output (SYNC IN, SYNC OUT)

The Sync output on M8041A: clock output to synchronize multiple modules to a common clock. The Sync input is a clock input on M8051A module to synchronize additional modules to a common clock. A sync cable is delivered with each M8051A module by default.

#### System input A/B and auxillary input (AUX IN)

Control inputs to synchronize events for the pattern sequencer. Auxiliary input: for future use. For M8041A only.

Table 11. System input and auxiliary input specifications (M8041A only)

| ,                   | 3 1 1        |        |        |

|---------------------|--------------|--------|--------|

|                     |              | M8041A | M8051A |

| Input voltage       | -1 V to +3 V | Χ      | no     |

| Termination voltage | -1 V to +3 V |        |        |

| Threshold voltage   | -1 V to +3 V |        |        |

| Connector           | SMA, female  |        |        |

## System output A/B (SYS OUT A/B)

Control outputs to synchronize events for the pattern sequencer.

Table 12. System output specifications (M8041A only).

|                        |                | M8041A | M8051A |

|------------------------|----------------|--------|--------|

| Amplitude <sup>1</sup> | 0.1 to 2 V     | Χ      | no     |

| Output voltage 1       | -0.5 to 1.75 V |        |        |

| Connector              | SMA, female    |        |        |

<sup>1.</sup> When terminated with 50  $\Omega$  into GND. Doubles into open.

## Jitter tolerance test specifications

M8020A provides built-in calibrated jitter sources designed to cover receiver test needs for most of the popular multi-gigabit standards such as: PCIe, USB, MIPI, SATA, DisplayPort, CPU frontside buses, CEI, 10GbE, 100GbE, SFP+, QSFP, CFP2/4, etc. M8020A provides automated jitter tolerance measurements. A library of pre-defined compliance curves is provided.

For 32 Gb/s setups using M8061A, the jitter sources of M8041A/51A can be used. The M8061A multiplexer is transparent to jitter. The ranges specified in table 13 to 17 refer to the datarate at the output of M8061A when the mux configuration is selected.

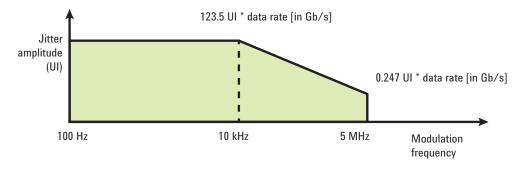

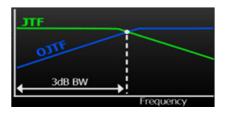

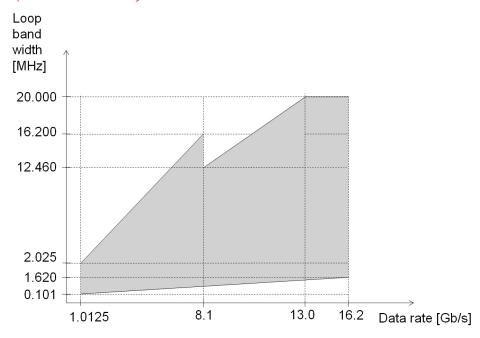

Table 13. Specifications for low frequency sinusoidal jitter (requires option 0G3 advanced jitter sources).

|                                 |                           |                                            | M8041A   | M8051A   |

|---------------------------------|---------------------------|--------------------------------------------|----------|----------|

| Low frequency sinusoidal jitter | Amplitude range           | 0 to 1000 UI. For frequencies              | opt. 0G3 | opt. OG3 |

| (LF SJ )                        |                           | between 10 kHz and 5 MHz see figure 16 for |          |          |

| (generated by IQ modulator)     |                           | maximum LF SJ.                             |          |          |

|                                 |                           | For frequencies between                    |          |          |

|                                 |                           | 10 kHz and 5 MHz the                       |          |          |

|                                 |                           | max. jitter amplitude =                    |          |          |

|                                 |                           | 1.235 ns * 10 <sup>-3</sup> * data rate    |          |          |

|                                 |                           | modulation frequency                       |          |          |

|                                 | Frequency                 | 100 Hz to 5 MHz                            |          |          |

|                                 | Jitter amplitude accuracy | ± 2 % ± 1 ps typical                       |          |          |

|                                 | Adjustable                | For each data channel independently,       |          |          |

|                                 |                           | same LF SJ for clock and trigger           |          |          |

## Low frequency sinusoidal jitter

| Data rate                  | Max UI at modulation       | Max UI at modulation |

|----------------------------|----------------------------|----------------------|

|                            | frequency 100 Hz to 10 kHz | frequency 5 MHz      |

| 256.0 Mb/s to 506.25 Mb/s  | 31.6 to 62.5 UI            | 0.0632 to 0.125 UI   |

| 506.25 Mb/s to 1.0125 Gb/s | 62.5 to 125 UI             | 0.125 to 0.25 UI     |

| 1.0125 Gb/s to 2.025 Gb/s  | 125 to 250 UI              | 0.25 to 0.5 UI       |

| 2.025 Gb/s to 4.05 Gb/s    | 250 to 500 UI              | 0.5 to 1 UI          |

| 4.05 Gb/s to 8.1 Gb/s      | 500 to 1000 UI             | 1 to 2 UI            |

| 8.1 Gb/s to 16.2 Gb/s      | 1000 to 2000 UI            | 2 to 4 UI            |

Figure 16. Low frequency sinusoidal jitter maximum depends on data rate and modulation frequency.

Table 14. Specifications for high frequency periodic jitter, random jitter, spectrally distributed random jitter, bounded uncorrelated jitter, Clock/2 jitter (requires option 0G3 advanced jitter sources).

|                                     |                           |                                                               | M8041A     | M8051A   |

|-------------------------------------|---------------------------|---------------------------------------------------------------|------------|----------|

| High frequency jitter               | Range                     | 1 UI p-p for data rates > 1 Gb/s                              | opt. 0G3   | opt. 0G3 |

| (generated by delay line)           |                           | note: this is max sum of RJ, HF-PJ1 and HF-PJ,                |            |          |

|                                     |                           | spectral RJ, external delay modulation and BUJ.               |            |          |

| High frequency periodic jitter      | Range                     | See HF jitter above <sup>1</sup>                              | _ opt. 0G3 | opt. 0G3 |

| (HF PJ1 and HF PJ2)                 | Frequency                 | 1 kHz to 500 MHz. For data rates                              |            |          |

|                                     |                           | < 4 Gb/s the max modulation frequency is data                 |            |          |

|                                     |                           | rate / 8. Two tone possible. Sweep.                           | _          |          |

|                                     | Jitter amplitude accuracy | ± 3 ps ± 10 % typical                                         | _          |          |

|                                     | Adjustable                | For each channel independently                                |            |          |

| Random jitter (RJ)                  | Range                     | 0 to 72 mUI rms (1 UI p-p max.) 1                             | opt. 0G3   | opt. 0G3 |

|                                     | Jitter amplitude accuracy | ± 300 fs ± 10 % typical                                       |            |          |

|                                     | Filters                   | High-pass: 10 MHz,                                            | _          |          |

|                                     |                           | Low-pass: 100 MHz,                                            |            |          |

|                                     |                           | Low pass: 500 MHz (for data rates ≥ 3.75 Gb/s)                |            |          |

|                                     |                           | Off (1 GHz bandwidth, for data rates ≥ 7.5 Gb/s)              | _          |          |

|                                     | Adjustable                | For each channel independently                                |            |          |

| Spectrally distributed RJ according | Range                     | 0 to 72 mUI rms (1 UI p-p), 1                                 | opt. 0G3   | opt. 0G3 |

| to PCIe 2 (sRJ) <sup>2</sup>        | Frequency                 | LF: 0.01 to 1.5 MHz, HF: 1.5 to 100 MHz                       | _          |          |

|                                     | Jitter amplitude accuracy | ± 300 fs ± 10 % typical                                       |            |          |

|                                     | Adjustable                | For each channel independently                                |            |          |

| Bounded uncorrelated jitter (BUJ)   | Range                     | See HF jitter above <sup>1</sup>                              | opt. 0G3   | opt. 0G3 |

|                                     | PRBS polynomials          | 2 <sup>n</sup> -1, n = 7,8,9,10,11,15,23,31                   | _          |          |

|                                     | Filters                   | 50/100/200 MHz low pass 3rd order                             | _          |          |

|                                     | Jitter amplitude accuracy | $\pm$ 5 ps $\pm$ 10% typical for settings shown in table 15   | _          |          |

|                                     | Adjustable                | For each channel independently                                | _          |          |

| Clock/2 jitter                      | Range                     | $\pm$ 20 ps or $\pm$ 0.1 UI typical (whatever is less). Note: | opt. 0G3   | opt. 0G3 |

| -                                   | -                         | this means that first eye can be up to 20 ps longer           | •          | •        |

|                                     |                           | or shorter than subsequent eye.                               |            |          |

|                                     | Jitter amplitude accuracy | ± 3 ps typical                                                | _          |          |

|                                     | Adjustable                | For each channel independently                                | _          |          |

<sup>1</sup> UI is the maximum sum of RJ, HF-PJ1 and HF-PJ2, spectral RJ, external delay modulation and BUJ.

Spectrally distributed random jitter is mutually exclusive with RJ and BUJ.

Table 15. BUJ accuracy applies for these BUJ settings.

| BUJ calibration settings <sup>1</sup> | Rate for PRBS generator | PRBS polynomial         | Low pass filter |  |

|---------------------------------------|-------------------------|-------------------------|-----------------|--|

| CEI 6G                                | 1.25 Gb/s               | PRBS 29-1               | 100 MHz         |  |

| CEI 11G                               | 2.5 Gb/s                | PRBS 2 <sup>11</sup> -1 | 200 MHz         |  |

| Gaussian                              | 2.5 Gb/s                | PRBS 2 <sup>31</sup> -1 | 100 MHz         |  |

<sup>1.</sup> Other settings are not calibrated and do not necessarily generate the desired jitter historgrams for all data rates of the PRBS generator.

Table 16. Specifications for Spread Spectrum Clocking (SSC) (requires opt. 0G3: advanced jitter sources).

|                             |                        |                                             | M8041A   | M8051A   |

|-----------------------------|------------------------|---------------------------------------------|----------|----------|

| SSC (Spread Spectrum Clock) | Range                  | 0 to 10,000 ppm (0 to 1%) peak-peak. Select | opt. 0G3 | na       |

|                             |                        | center-spread, up-spread, and down-spread.  |          |          |

|                             | Frequency              | 30 kHz to 100 kHz                           |          |          |

|                             | Modulation             | Triangular and arbitrary modulation         |          |          |

|                             | SSC amplitude accuracy | ± 0.025 % typical                           | _        |          |

|                             | Outputs                | Can be turned on/off together for CLK OUT,  | _        |          |

|                             |                        | DATA OUT 1, DATA OUT 2, TRG OUT             |          |          |

| Residual SSC (@ PCle2)      | Range                  | 0 to 100 ps                                 | opt. 0G3 | opt. 0G3 |

|                             | Frequency              | 10 to 100 kHz                               | _        |          |

|                             | Outputs                | Can be turned on/off independently for DATA | _        |          |

|                             |                        | OUT 1, DATA OUT 2                           |          |          |

Table 17. Specifications for external jitter modulation (DATA MOD IN 1 and 2, CLK MOD IN).

M8041A allows individual jitter injection for data 1, data 2 and clock. M8051A for data 1 and data 2. The option 0G3 is not needed.

|                                          |             |                                          | M8041A   | M8051A |

|------------------------------------------|-------------|------------------------------------------|----------|--------|

| External jitter - data modulation input  | Description | Input for delay modulation for each DATA | х        | Х      |

| 1 and 2                                  |             | OUT individually.                        |          |        |

|                                          | Range       | Up to 1 UI <sup>1</sup> , 0.8 Vpp max    | <u> </u> |        |

|                                          | Frequency   | Up to 1 GHz                              |          |        |

| External jitter - clock modulation input | Description | Input for delay modulation for the       | Х        | na     |

|                                          |             | TRG OUT and CLK OUT. Affects both.       |          |        |

|                                          | Range       | Up to 1 UI , 0.8 Vpp max                 | _        |        |

|                                          | Frequency   | Up to 1 GHz                              |          |        |

| Gain                                     |             | 1UI / 0.725 V ± 5%                       | Х        | Х      |

| Linearity                                |             | 50 mUI                                   | Х        | Х      |

| Connectors                               | •           | SMA, female                              |          | -      |

<sup>1. 1</sup> UI is the maximum sum of RJ, HF-PJ1 and HF-PJ2, spectral RJ, external delay modulation and BUJ.

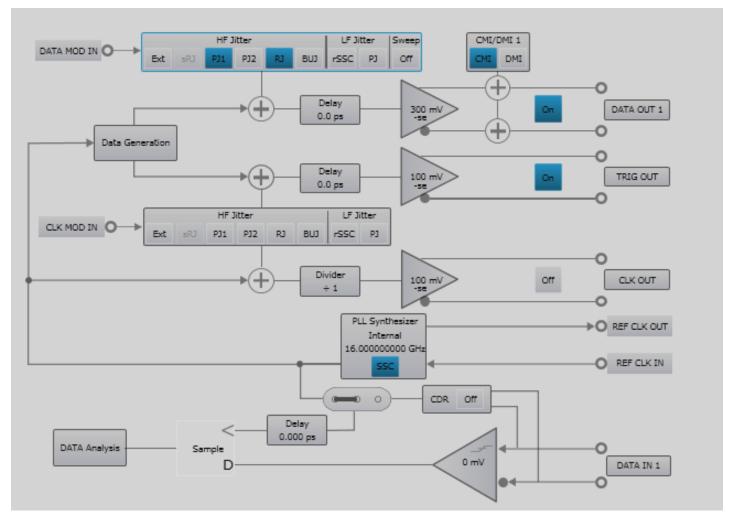

Figure 17. J-BERT M8020A system view for 1 channel.

#### ISI channels

External ISI channels are available to emulate channel loss. Keysight offers dedicated compliant ISI channels for DisplayPort, PCle3 (base spec) and SATA. M8048A is offererd in addition.

For detailed specifications see M8048A data sheet.

M8041A-001 ISI Channels provides four short traces: 7.7"(196 mm), 9.4" (240 mm), 11.12 "(282 mm), 12.8"(324 mm) M8041A.002 ISI Channels provides four long traces: 14.8" (366 mm), 16.1" (408 mm), 24.4" (620 mm), 34.4"(874 mm)

## Level interference injection

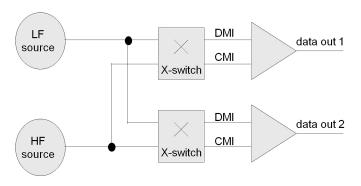

Common mode and differential mode level interference can be generated internally to test common mode rejection of a receiver and vertical eye closure tolerance. Simultaneous injection of CMI and DMI is possible. In 32 Gb/s configurations with M8061A, external sources for M8061A are required. See M8061A data sheet for details on built-in level interference superposition and gain adjust parameters.

Table 18. Specifications for sinusoidal level interference (CMI, DMI) (requires option 0G7).

| ·                                    |                           |                                                          | M8041A  | M8051A  |

|--------------------------------------|---------------------------|----------------------------------------------------------|---------|---------|

| Differential mode interference (DMI) | Amplitude <sup>2</sup>    | Max. 30% of output amplitude <sup>1</sup>                | opt 0G7 | opt 0G7 |

|                                      | Amplitude accuracy        | ±10 mV ±10% typ                                          | _       |         |

| Common mode interference (CMI)       | Amplitude <sup>2, 3</sup> | Up to 320 mV <sup>1</sup>                                |         |         |

|                                      | Amplitude accuracy        | ±10 mV ±10% typ                                          |         |         |

| Modulation frequency                 | Ranges                    | LF: 10 MHz to 1 GHz, sinusoidal only                     | _       |         |

|                                      |                           | HF: 1 GHz to 6 GHz, sinusoidal only                      |         |         |

| Simultaneous injection of            |                           | Yes. HF modulation cannot be used simultaneously for CMI | _       |         |

| CMI and DMI                          |                           | and DMI. LF modulation cannot be used simultaneously for |         |         |

|                                      |                           | CMI and DMI. See figure below.                           |         |         |

- 1. The maximum output amplitude decreases when CMI or DMI is enabled. See table 2.

- 2. For each channel independently.

- 3. Up to 5 GHz.

Figure 18: M8020A provides calibrated level interference sources for simultaneous injection of CMI (common mode interference) and DMI (differential mode interference).

## Pattern, sequencer and interactive link training

Table 19. Specifications for pattern, sequencer and link training.

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | M8041A   | M8051A | M8061A |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--------|

| PRBS <sup>1</sup>              | 2 <sup>n</sup> -1, n= 7, 10, 11, 15, 23, 23p <sup>3</sup> , 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Х        | Х      | Х      |

| PRBS                           | 2 <sup>n</sup> , n = 7, 10, 11, 13, 15, 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _        |        |        |