#### **Errata**

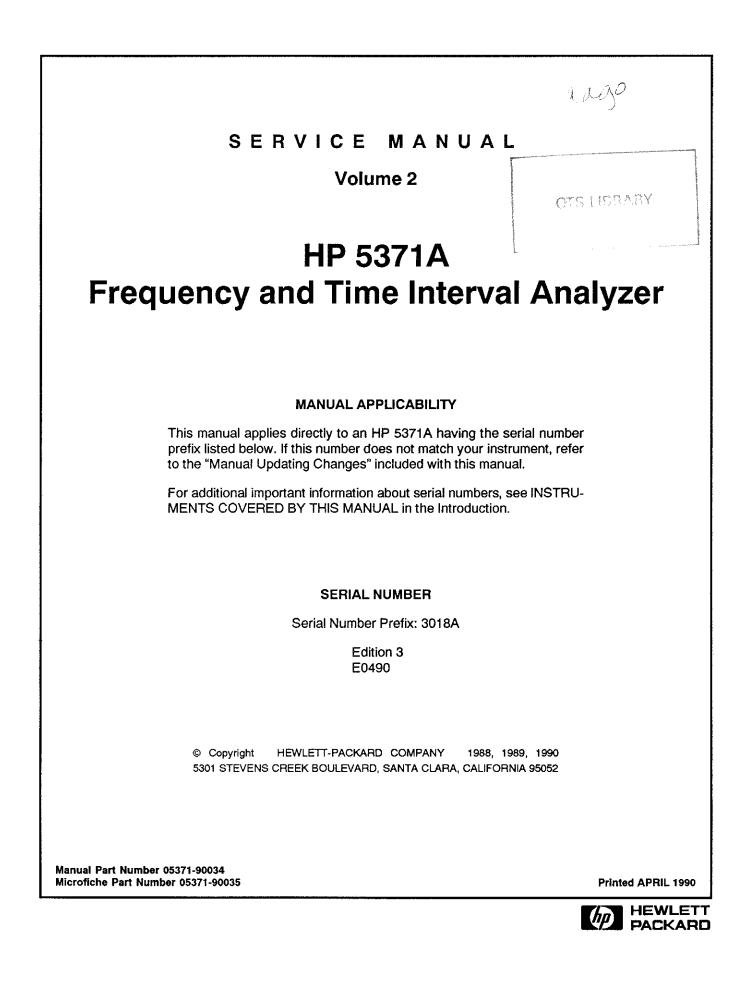

**Title & Document Type:** 5371A Frequency & Time Interval Analyzer Service Manual, Volume 2

Manual Part Number: 05371-90034

Revision Date: April 1, 1990

#### **HP** References in this Manual

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

#### About this Manual

We've added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.

#### **Support for Your Product**

Agilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:

www.tm.agilent.com

Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.

# HEWLETT-PACKARD

# Service Manual Volume 2

# HP 5371A Frequency and Time Interval Analyzer

# CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility, and to the calibration facilities of other International Standards Organization members.

# WARRANTY

This Hewlett-Packard instrument product is warranted against defects in material and workmanship for a period of one year from date of shipment. During the warranty period, Hewlett-Packard Company will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by HP. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

# LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

# ASSISTANCE

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

# SAFETY CONSIDERATIONS

### GENERAL

This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation.

This product is a Safety Class I instrument (provided with a protective earth terminal).

### **BEFORE APPLYING POWER**

Verify that the product is set to match the available line voltage and the correct fuse is installed. Refer to Operating Manual, Appendix B, INSTALLATION.

### SAFETY EARTH GROUND

An uninterruptible safety earth ground must be provided from the mains power source to the product input wiring terminals or supplied power cable.

# SAFETY SYMBOLS

Instruction manual symbol; the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual.

Indicates hazardous voltages.

Indicates terminal is connected to chassis when such connection is not apparent.

/77 OR 1

Alternating current.

Direct current.

The **WARNING** sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in personal injury. Do not proceed beyond a **WARNING** sign until the indicated conditions are fully understood and met.

The **CAUTION** sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a **CAUTION** sign until the indicated conditions are fully understood and met.

# SAFETY INFORMATION

# WARNING

Any interruption of the protective grounding conductor (inside or outside the instrument) or disconnecting the protective earth terminal will cause a potential shock hazard that could result in personal injury. (Grounding one conductor of a two conductor outlet is not sufficient protection.)

Whenever it is likely that the protection has been impaired, the instrument must be made inoperative and be secured against any unintended operation.

If this instrument is to be energized via an autotransformer (for voltage reduction) make sure the common terminal is connected to the earthed pole terminal (neutral) of the power source.

Instructions for adjustments while covers are removed and for servicing are for use by service-trained personnel only. To avoid dangerous electric shock, do not perform such adjustments or servicing unless qualified to do so.

For continued protection against fire, replace the line fuse(s) only with 250V fuse(s) of the same current rating and type (for example, normal blow, time delay). Do not use repaired fuses or short circuited fuseholders.

When measuring power line signals, be extremely careful and always use a step-down isolation transformer whose output voltage is compatible with the input measurement capabilities of this product. This product's front and rear panels are typically at earth ground, so **NEVER TRY TO MEASURE AC POWER LINE SIGNALS WITHOUT AN ISOLATION TRANSFORMER.**

# TABLE OF CONTENTS

### SECTION TITLE

| 7  | SERV  | ICE — GENERAL                                          | 7-1    |

|----|-------|--------------------------------------------------------|--------|

|    | 7-1.  | Introduction                                           | . 7-1  |

|    | 7-2.  | HP 5371A Service Kit                                   | . 7-2  |

|    | 7-3.  | Safety Considerations                                  | . 7-2  |

|    | 7-4.  | Safety Symbols                                         |        |

|    | 7-5.  | After Service Product Safety Checks                    | . 7-7  |

|    | 7-6.  | Troubleshooting                                        |        |

|    | 7-7.  | Introduction                                           | . 7-7  |

|    | 7-8.  | Dead-unit Troubleshooting                              |        |

|    | 7-9.  | Electrostatic Discharge                                |        |

|    | 7-10. | Cleaning Printed-Circuit Boards                        |        |

|    | 7-11. | Recommended Test Equipment                             |        |

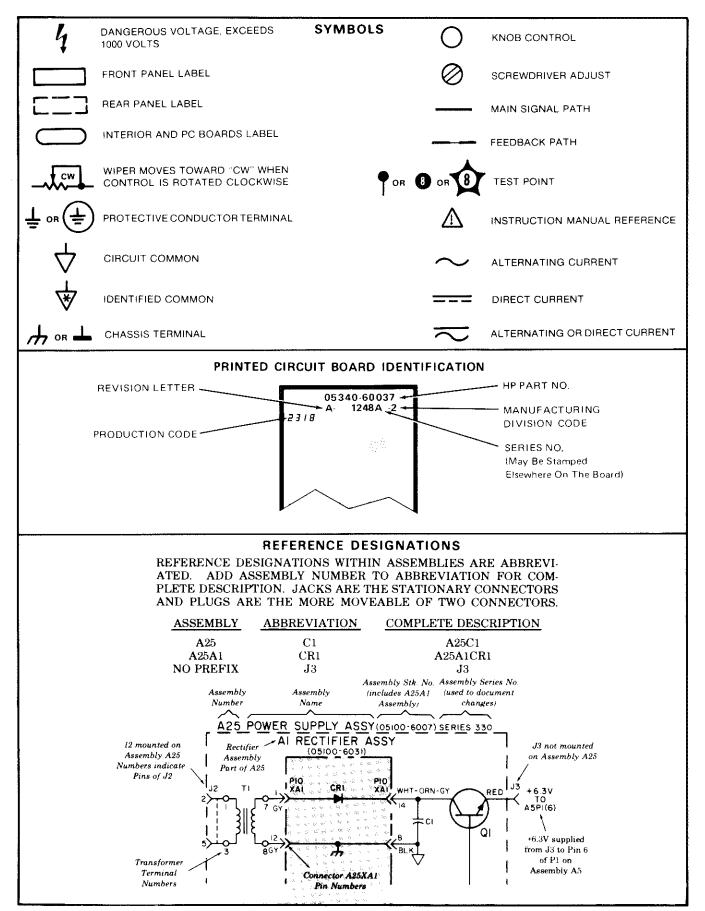

|    | 7-12. | Schematic Diagram Symbols And Reference Designations   |        |

|    | 7-13. | Reference Designators                                  |        |

|    | 7-14. | Identification Markings on Printed-circuit Boards      |        |

|    | 7-15. | Identification and Repair of Multilayer Circuit Boards |        |

|    | 7-16. | Logic Symbols                                          |        |

|    | 7-17. | Routine Maintenance                                    |        |

|    | 7-18. | Operating Environment                                  |        |

|    | 7-19. | Temperature                                            |        |

|    | 7-20. | Humidity                                               |        |

|    | 7-21. | Altitude                                               |        |

|    | 7-22. | Power Requirements                                     |        |

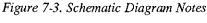

|    | 7-23. | Line Voltage and Fuse Selection                        |        |

|    | 7-24. | Front-Panel LED Annunciators                           |        |

|    | 7-25. | HP-IB Status LEDs                                      |        |

|    | 7-26. | Instrument Control LEDs                                |        |

|    | 7-27. | External Arm, Channel A, and Channel B LEDs            |        |

|    | 7-28. | STANDBY LED and Power (STBY-ON) Switch                 |        |

|    | 7-29. | Keyboard Memory                                        |        |

|    | 7-30. | Hewlett-Packard Interface Bus (HP-IB)                  |        |

|    | 7-31. | HP-IB Connections                                      |        |

|    | 7-32. | HP-IB Address Selection                                |        |

|    | 7-33. | HP-IB Descriptions                                     |        |

|    | 7-34. | Logic Family Voltage Levels                            |        |

|    |       |                                                        |        |

| 7A | DIAG  | NOSTICS                                                | 7A-1   |

|    | 7A-1. | Introduction                                           |        |

|    | 7A-2. | HP-IB Commands for Calling Diagnostic Tests            |        |

|    | 7A-3. | Help Menu Screens                                      |        |

|    | 7A-4. | Diagnostics                                            |        |

|    | 7A-5. | Power-up Self Tests                                    |        |

|    | 7A-6. | Back-Up RAM Test                                       |        |

|    | 7A-7. | Front Panel Keyboard Controller Initialization Test    |        |

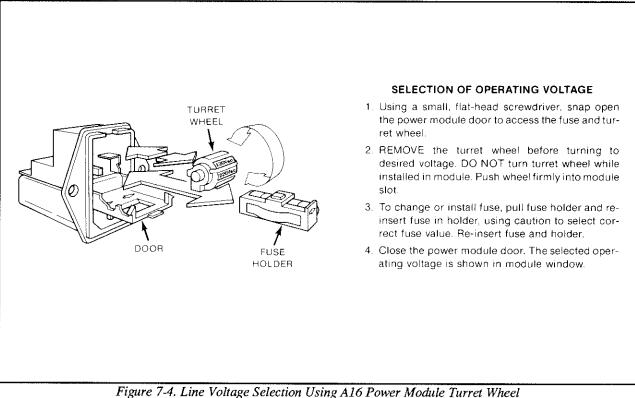

|    | 7A-8. | TEST Menu Screen                                       |        |

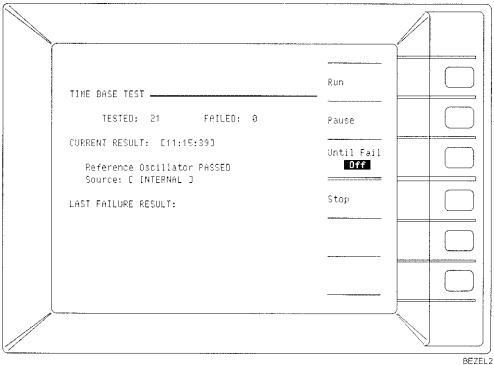

|    | 7A-9. | Standard Test Screen                                   | . 7A-5 |

#### SECTION TITLE

| 7A Cont'd. | DIAGN            | IOSTICS                                       |

|------------|------------------|-----------------------------------------------|

|            | 7A-10.           | Test Descriptions                             |

|            | 7A-11.           | Test 1. Self Test                             |

|            | 7A-12.           | Test 2. Time Base Test                        |

|            | 7A-13.           | Test 3. Input Pod Test                        |

|            | 7A-14.           | Test 4. Input Amplifier Test                  |

|            | 7A-15.           | Test 5. Count ICs Test                        |

|            | 7A-16.           | Test 6. Gate Timer Test                       |

|            | 7A-17.           | Test 7. Measurement RAM Test                  |

|            | 7A-18.           | Test 8. System ROM Test                       |

|            | 7A-19.           | Test 9. System RAM Test                       |

|            | 7A-20.           | Test 10. Timer Test                           |

|            | 7A-21.           | Test 11. Real-Time Clock Test 7A-16           |

|            | 7A-22.           | Test 12. CRT RAM Test                         |

|            | 7A-23.           | Test 13. LED Latch Test                       |

|            | 7A-24.           | Test 14. CRT Controller Test                  |

|            | 7A-25.           | Test 15. Front Panel Keyboard Controller Test |

|            | 7A-26.           | Test 16. DMA Controller Test                  |

|            | 7A-27.           | Test 17. Front Panel Test                     |

|            | 7A-28.           | Test 18. CRT Adjustment Pattern               |

|            | 7A-29.           | Test 19. CRT Video Pattern                    |

|            | 7A-30.           | Test 20. External Amplifier Test              |

|            | 7A-31.           | Test 21. Interpolator Calibration Routine     |

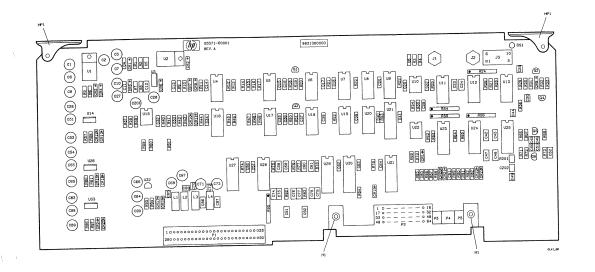

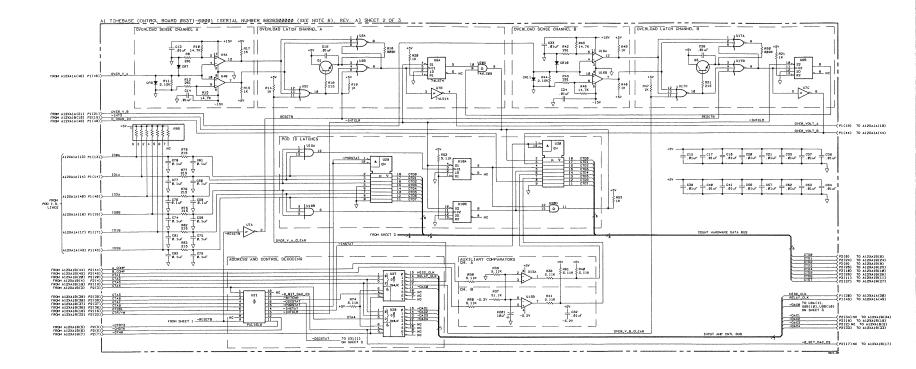

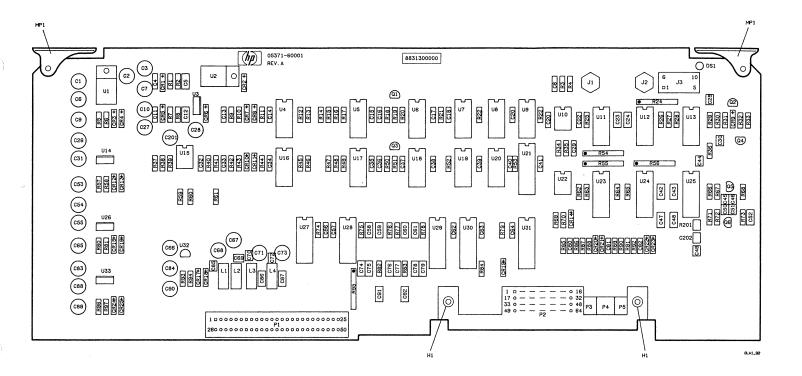

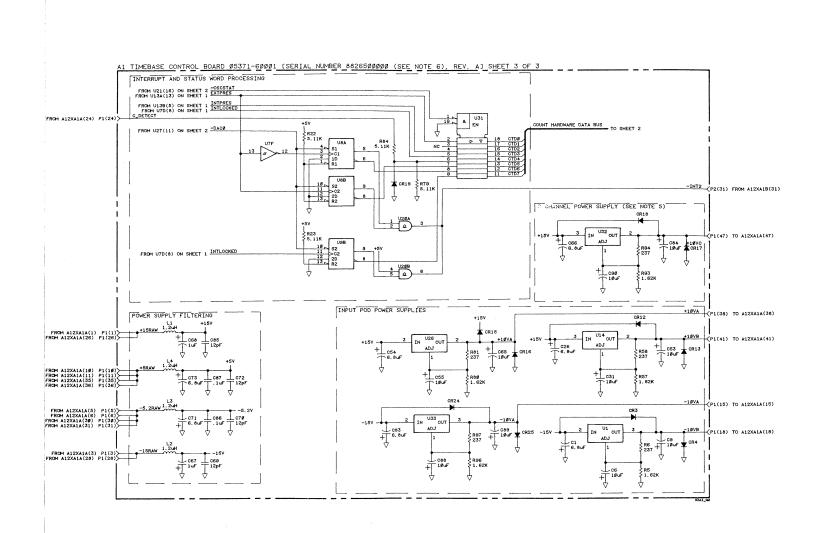

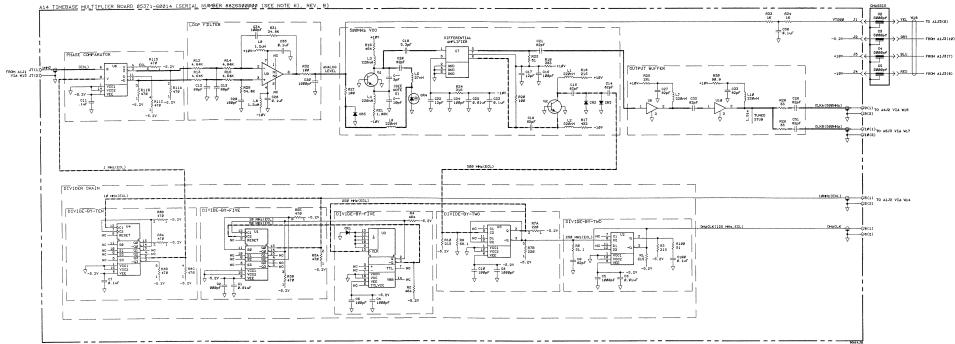

| 7B         | A1/A14           | TIMEBASE CONTROL/MULTIPLIER 7B-1              |

|            | 7 <b>B-</b> 1.   | A1 Timebase Control Board                     |

|            | 7B-2.            | Introduction                                  |

|            | 7B-3.            | Internal Timebase Buffer Stage                |

|            | 7B-4.            | External Timebase Buffer Stage                |

|            | 7B-5.            | External Timebase Detect Stage                |

|            | 7B-6.            | Internal Timebase Control Stage 7B-2          |

|            | 7 <b>B-</b> 7.   | Internal Timebase Detect Stage                |

|            | 7B-8.            | 10 MHz Multiplexer Stage 7B-2                 |

|            | 7B-9.            | Divide-By-N Stage                             |

|            | 7 <b>B-</b> 10.  | Reference Output Buffer Stage                 |

|            | 7 <b>B</b> -11.  | A2 Input Amplifier Board Support Circuitry    |

|            | 7B-12.           | Overload Sense Stage — Channels A and B       |

|            | 7B-13.           | Overload Latch Stage — Channels A and B       |

|            | 7 <b>B-</b> 14.  | Pod Identification Latches                    |

|            | 7B-15.           | Auxiliary Comparators Stage                   |

|            | 7B-16.           | Address and Control Decoding Stage            |

|            | 70.17            | Input Pod Power Supplies                      |

|            | 7B-17.           |                                               |

|            | 7В-17.<br>7В-18. | Interrupt and Status Word Processing Stage    |

|            |                  |                                               |

| SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TITLE           |                                                          | PAGE   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------|--------|

| 7B Cont'd.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>A1/A14</b> ] | FIMEBASE CONTROL/MULTIPLIER                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-21.          | Phase Comparator                                         | . 7B-5 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-22.          | Loop Filter                                              | . 7B-5 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-23.          | 500 MHz VCO                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-24.          | Divider Chain Stage                                      | . 7B-6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-25.          | Output Buffer Stage                                      | . 7B-6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-26.          | A1/A14 Timebase Control/Multiplier Board Troubleshooting |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-27.          | BACKGROUND                                               | . 7B-6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-28.          | A1 and A14 Troubleshooting Approach                      |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-29.          | A1 and A14 Failure Symptoms                              | . 7B-7 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-30.          | A1 and A14 Troubleshooting Preparation                   | . 7B-7 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7B-31.          | A1 and A14 Troubleshooting Procedures                    |        |

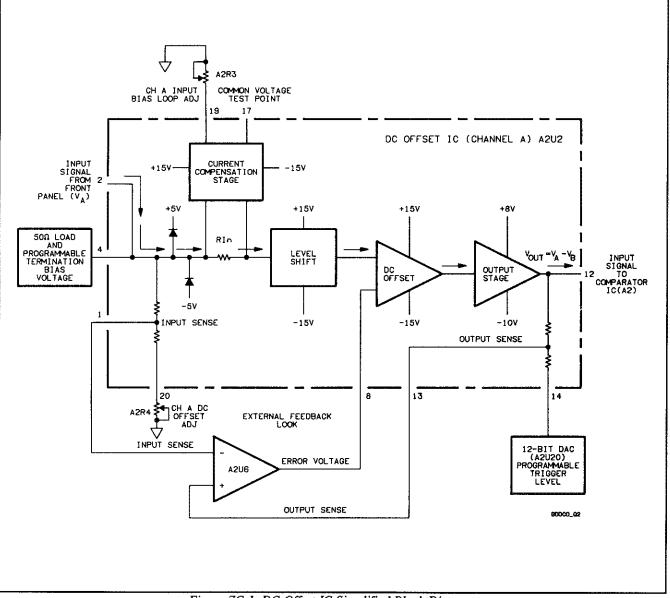

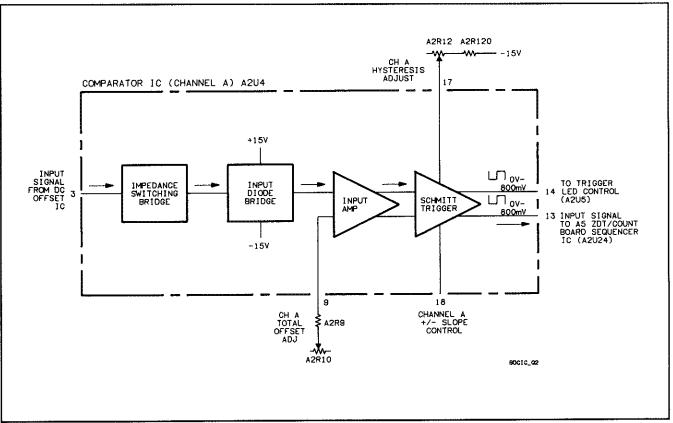

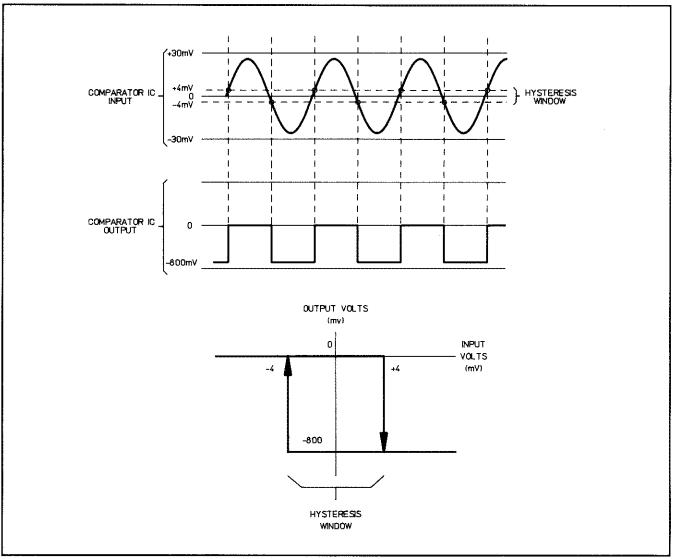

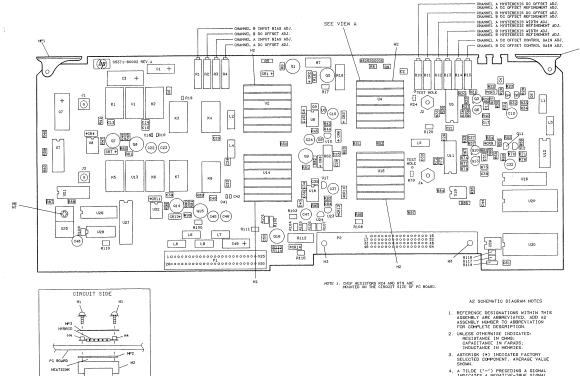

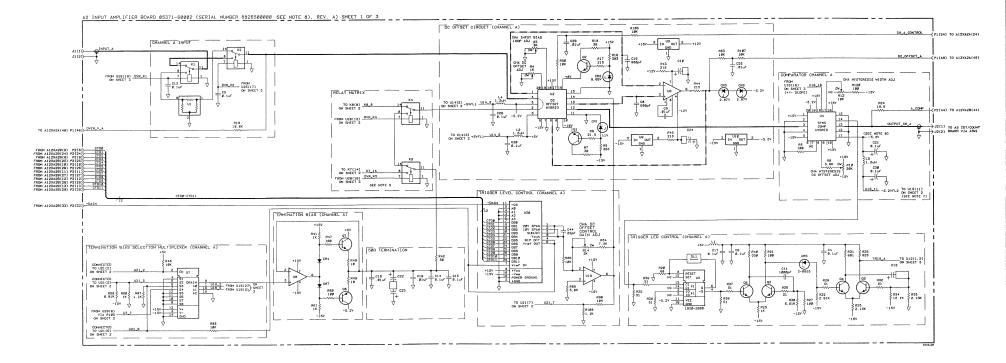

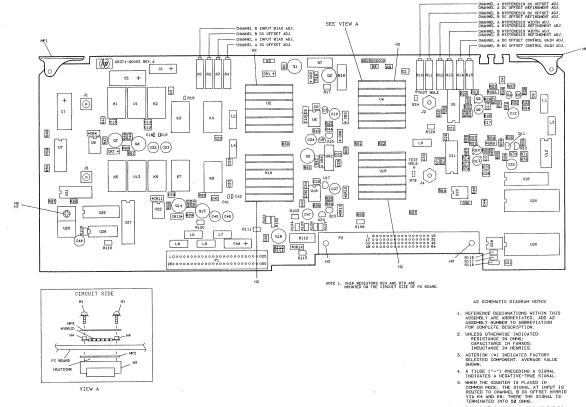

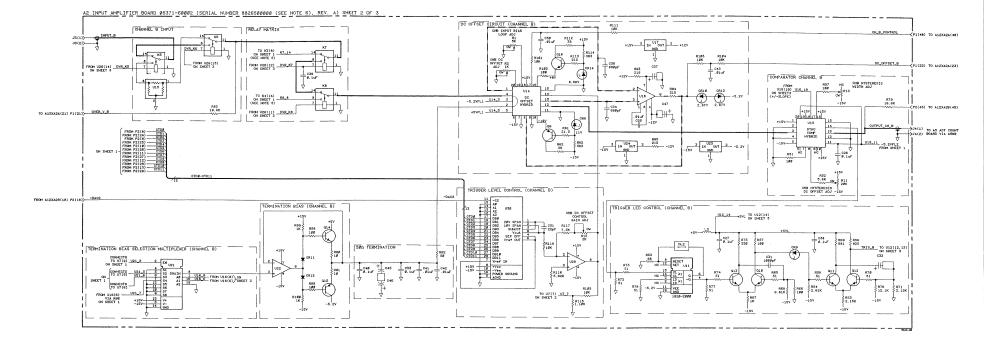

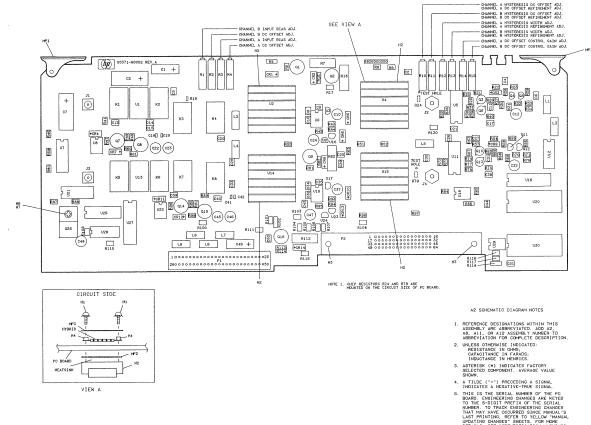

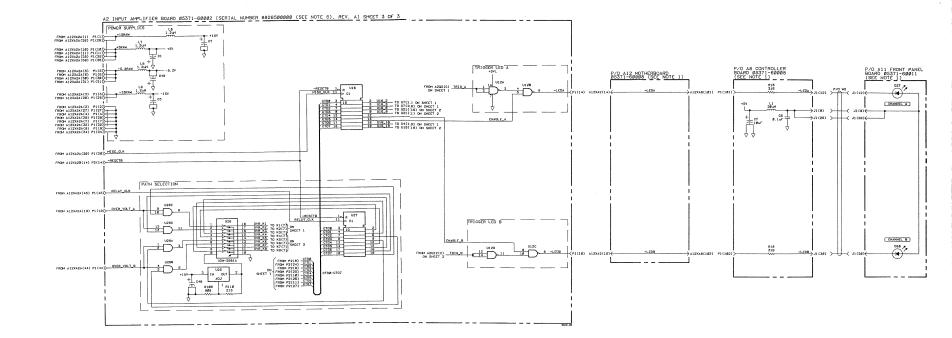

| 7C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A2 INPU         | JT AMPLIFIER BOARD                                       | 7C-1   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-1.           | Introduction                                             | . 7C-1 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-2.           | Channel Input Mode                                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-3.           | Termination Bias Voltage                                 |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-4.           | Channel A Input Description                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-5.           | Channel A Input                                          |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-6.           | DC Offset (Channel A)                                    |        |

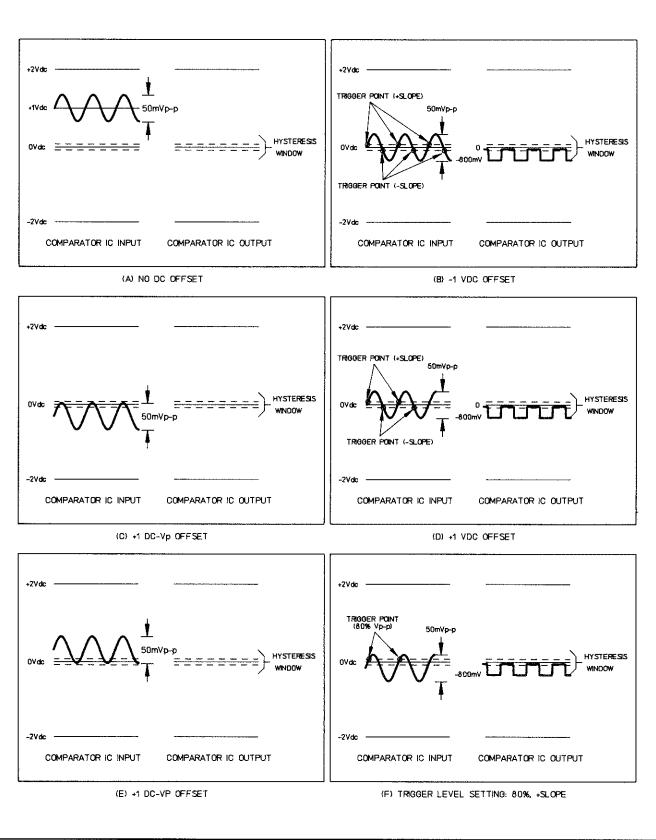

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-7.           | Comparator IC                                            |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-8.           | Trigger Level Control and Peak Amplitude Measurement     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-9.           | Trigger LED Control                                      |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-10.          | Path Selection (Relay Control)                           |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-11.          | Termination Bias, ± Slope, Trigger LED                   |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-12.          | Termination Bias Selection                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-13.          | A2 Input Amplifier Troubleshooting                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-14.          | Test Equipment Required                                  |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-15.          | Diagnostics                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-16.          | Background                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-17.          | A2 Input Amplifier Troubleshooting Approach              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-18.          | A2 Troubleshooting Procedure                             |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-19.          | DC Offset Hybrid Check                                   |        |

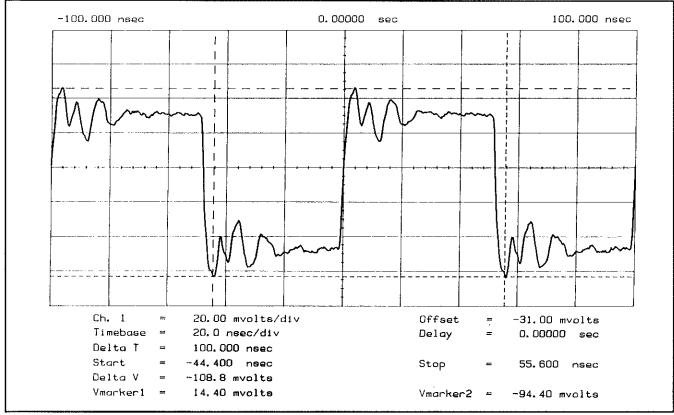

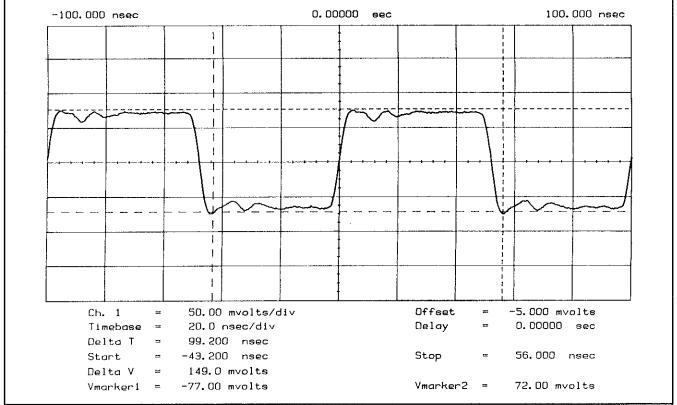

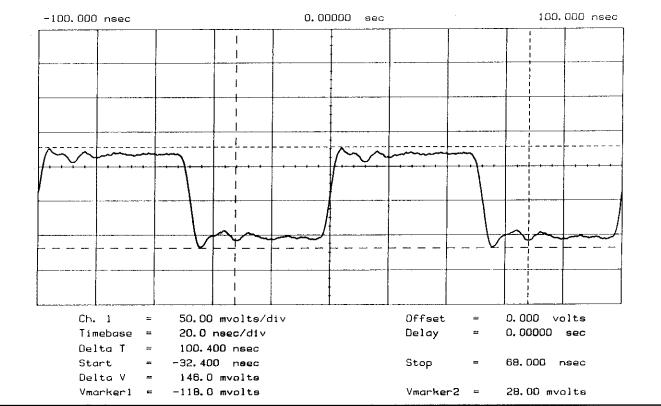

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-20.          | Comparator Hybrid Check                                  |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7C-21.          | Trigger Level Control Check                              |        |

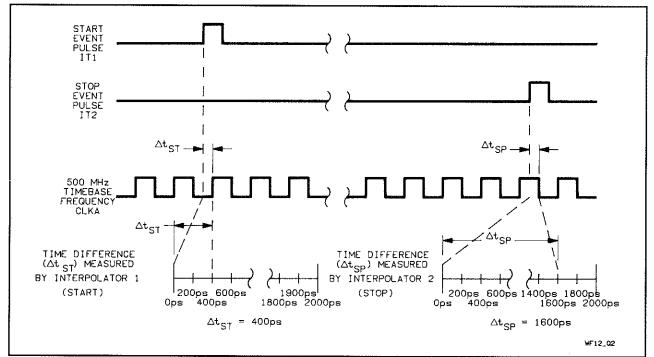

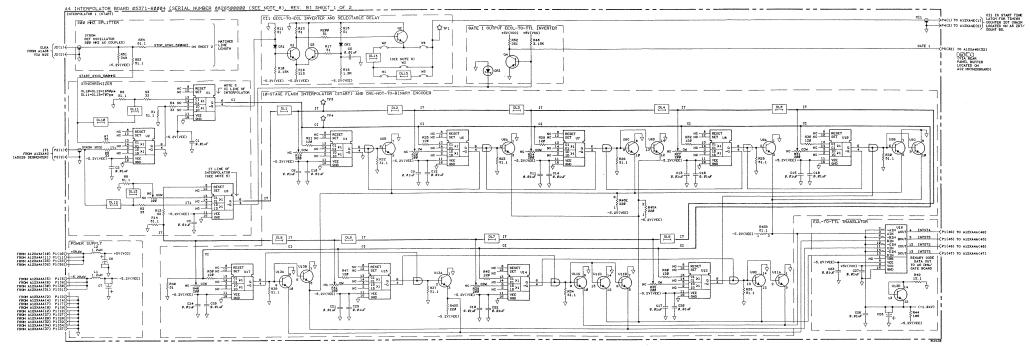

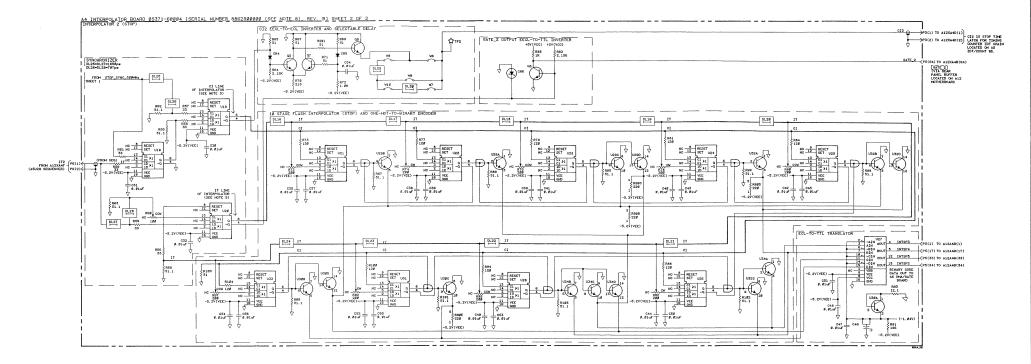

| 7D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A4 INTE         | CRPOLATOR BOARD                                          | 7D-1   |

| per la constante de |                 | A4 Interpolator Board                                    | . 7D-1 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-2.           | Introduction                                             |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-3            | A4 Interpolator Operation Overview                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-4.           | 500 MHz Splitter                                         |        |

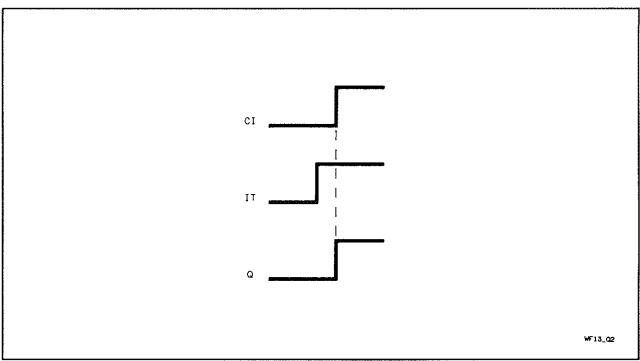

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-5.           | Synchronizer                                             |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-6.           | GATE 1 Output EECL-to-ECL Inverter                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-7.           | CI1 EECL-TO-ECL Inverter and Selectable Delay            |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-8.           | 10-Stage Flash Interpolator Chain                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7D-9.           | One-Hot-To-Binary Encoder                                |        |

PAGE

SECTION TITLE

| 7D Cont'd.    |                 | TERPOLATOR BOARD                                |

|---------------|-----------------|-------------------------------------------------|

|               | 7D-10.          | ECL-to-TTL Translator                           |

|               | 7D-11.          | A4 Interpolator Board Troubleshooting           |

|               | 7D-12.          | Test Equipment Required 7D-7                    |

|               | 7D-13.          | Diagnostics                                     |

|               | 7 <b>D-</b> 14. | Background                                      |

|               | 7D-15.          | A4 Troubleshooting Approach                     |

|               | 7D-16.          | A4 Failure Symptoms                             |

|               | 7D-17.          | A4 Troubleshooting Preparation                  |

|               | 7D-18.          | A4 Troubleshooting Procedure                    |

|               | 7D-19.          | Interpolator 1 (Start)                          |

|               | 7D-20.          | Interpolator 2 (Stop)                           |

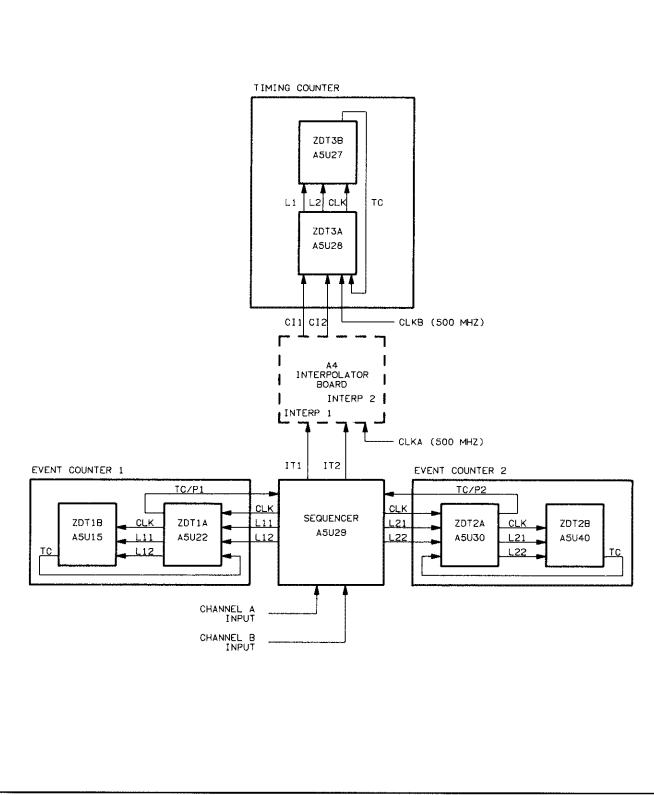

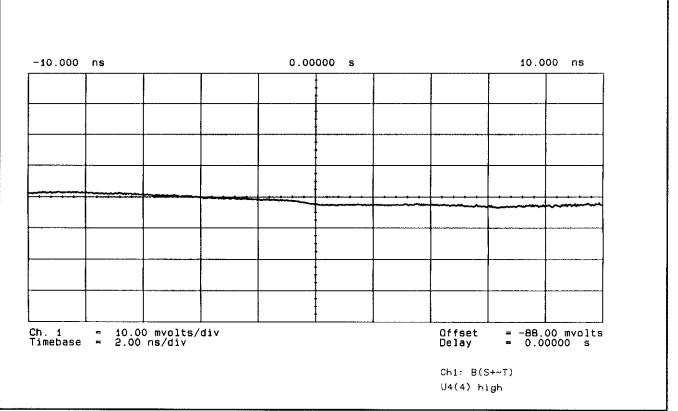

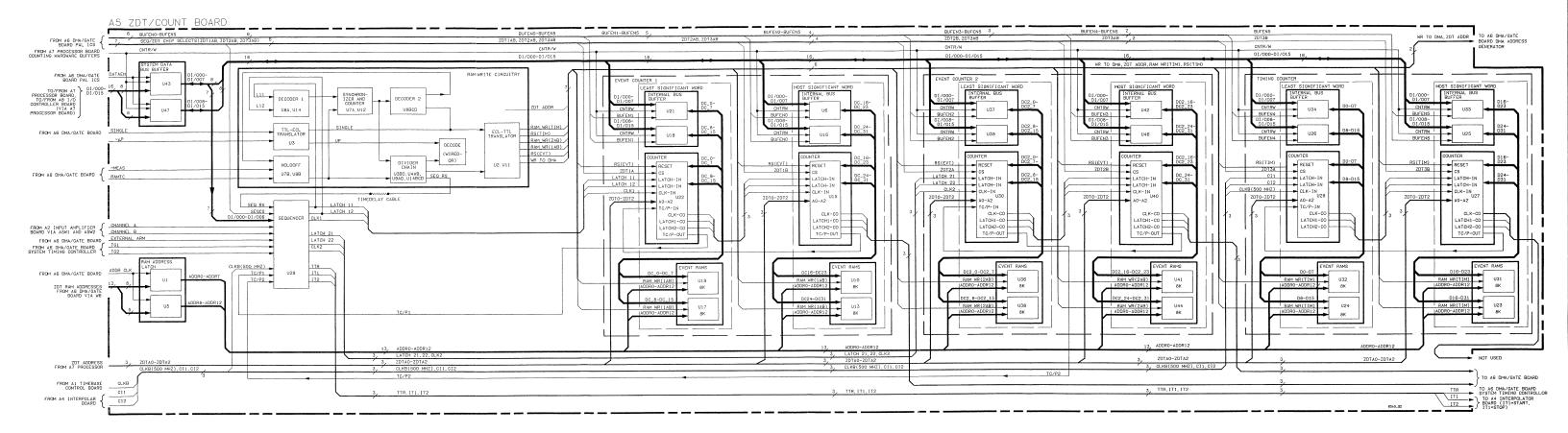

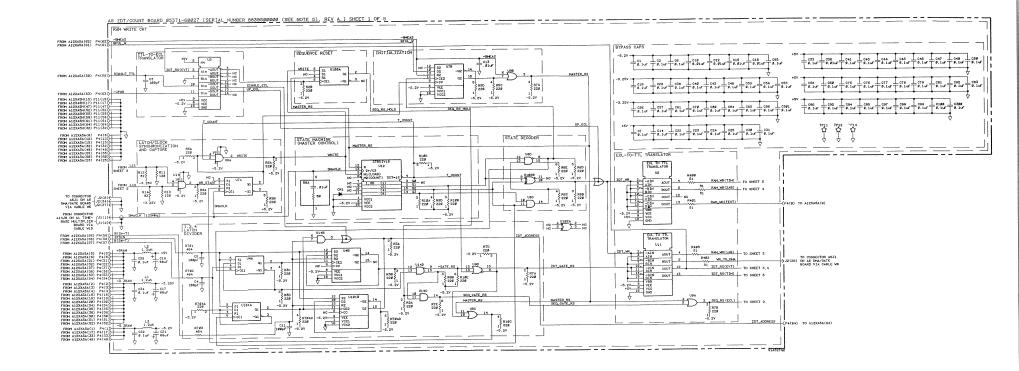

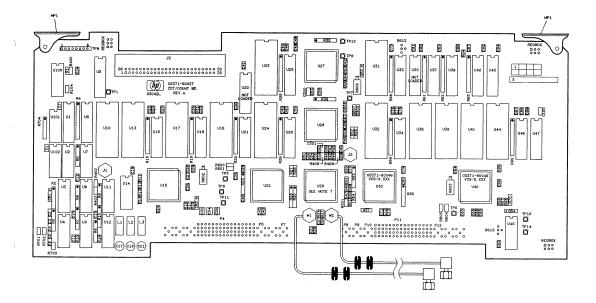

| 7E            | A5 ZD           | T/COUNT BOARD 7E-1                              |

|               | 7E-1.           | Introduction                                    |

|               | 7E-2.           | Typical Measurement Cycle                       |

|               | 7E-3.           | Counting Chain                                  |

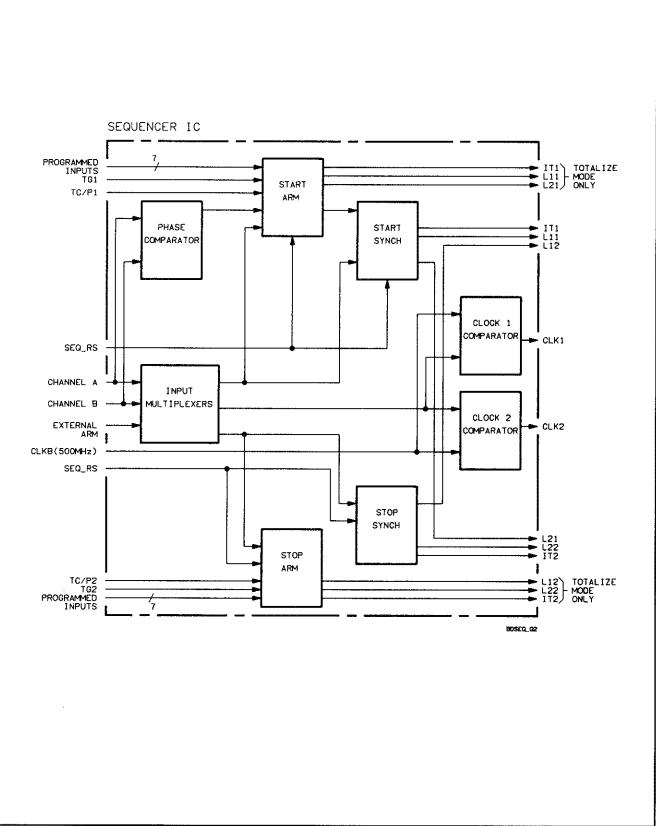

|               | 7E-4.           | Sequencer IC                                    |

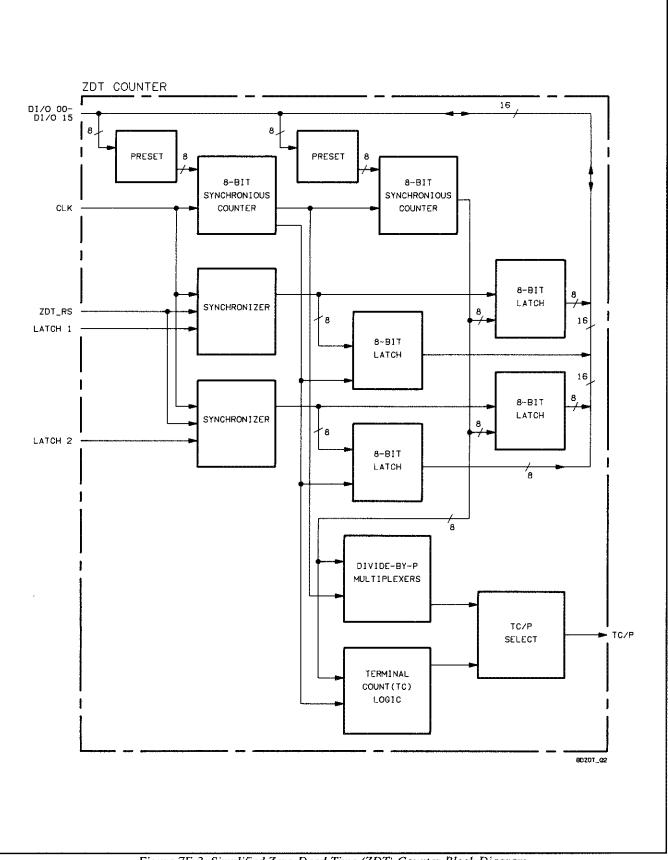

|               | 7E-5.           | ZDT Counter IC                                  |

|               | 7E-6.           | ZDT and Sequencer Interaction                   |

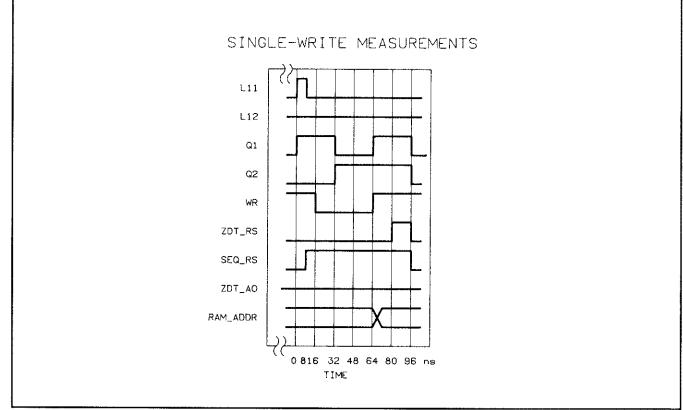

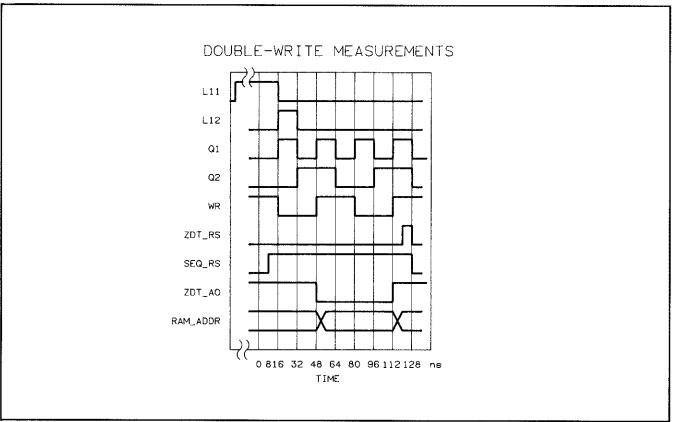

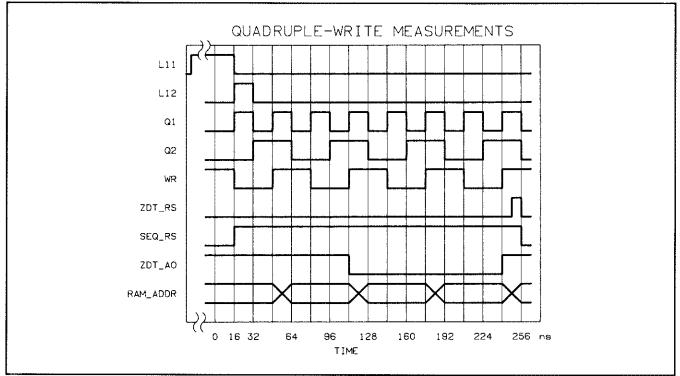

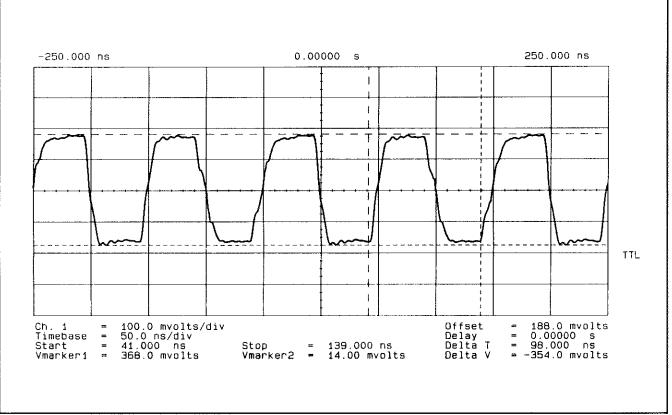

|               | 7E-7.           | RAM Write Circuit                               |

|               | 7E-8.           | Latch and DMA Clock Synchronization and Capture |

|               | 7E-9.           | State Machine (Master Control)                  |

|               | 7E-10.          | State Decoder                                   |

|               | 7E-11.          | 1, 2, 4 Latch Divider                           |

|               | 7E-12.          | Initialization Circuit                          |

|               | 7E-13.          | Sequencer Reset Holdoff                         |

|               | 7E-14.          | RAM Address Latches                             |

|               | 7E-15.          | System Buffers                                  |

|               | 7E-16.          | A5 ZDT/Count Board Troubleshooting              |

|               | 7E-17.          | Test Equipment Required                         |

|               | 7E-18.          | Diagnostics                                     |

|               | 7E-19.          | Background                                      |

|               | 7E-20.          | A5 Troubleshooting Preparation                  |

|               | 7E-21.          | A5 Troubleshooting Procedure                    |

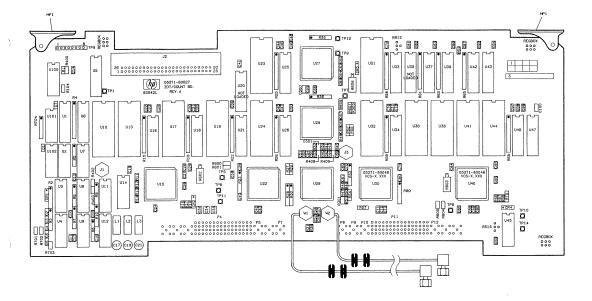

|               | 7E-22.          | RAM Write Circuit and Sequencer                 |

|               | 7E-23.          | Sequencer                                       |

| <b>** * *</b> |                 |                                                 |

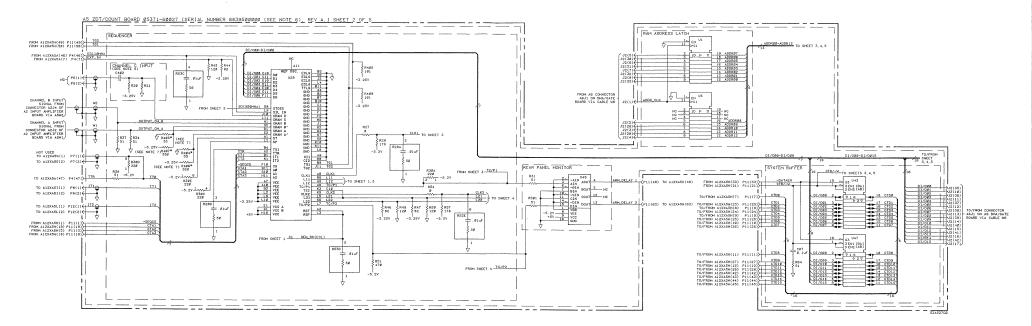

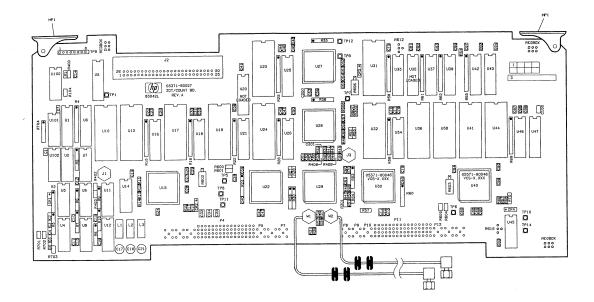

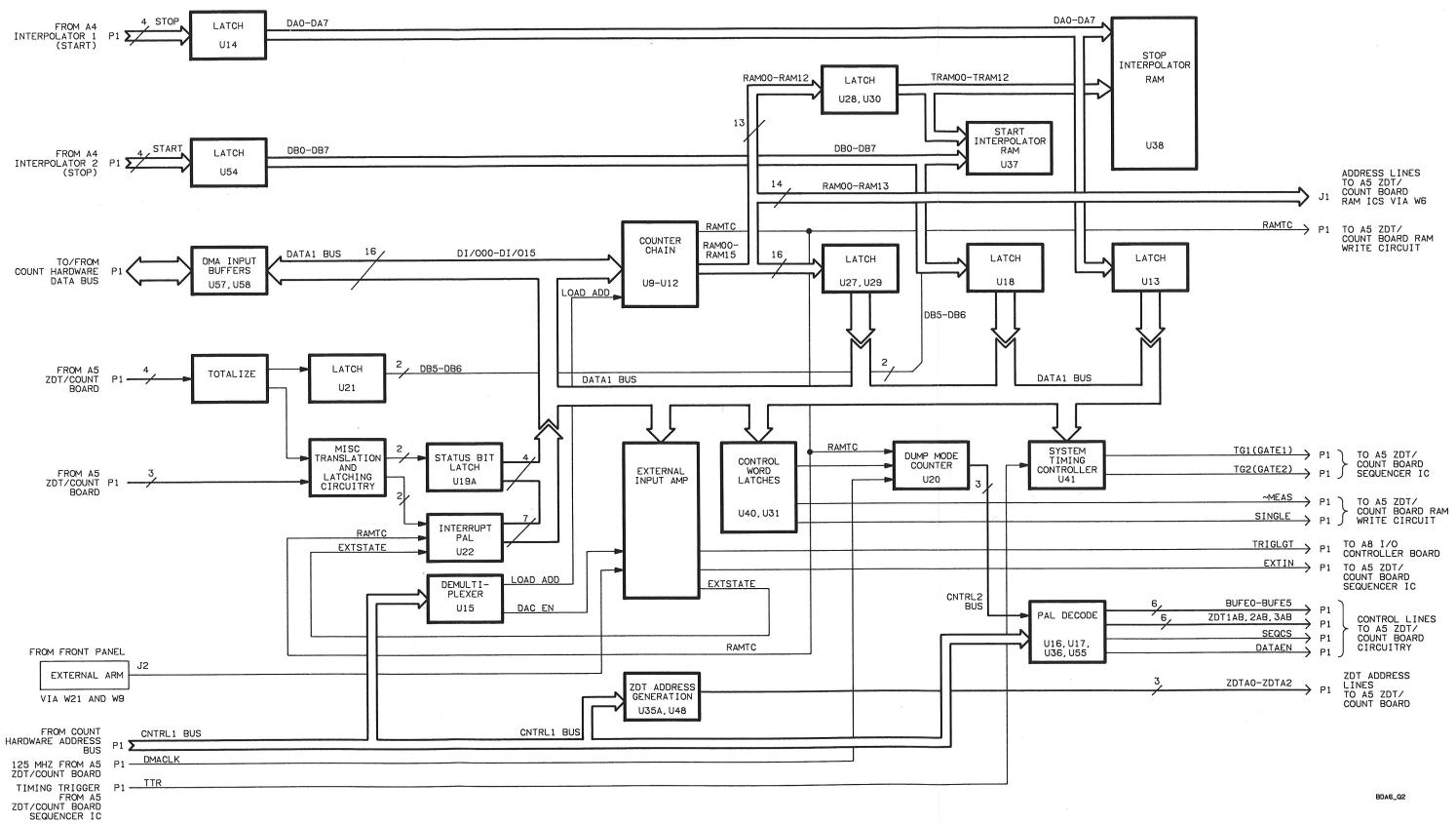

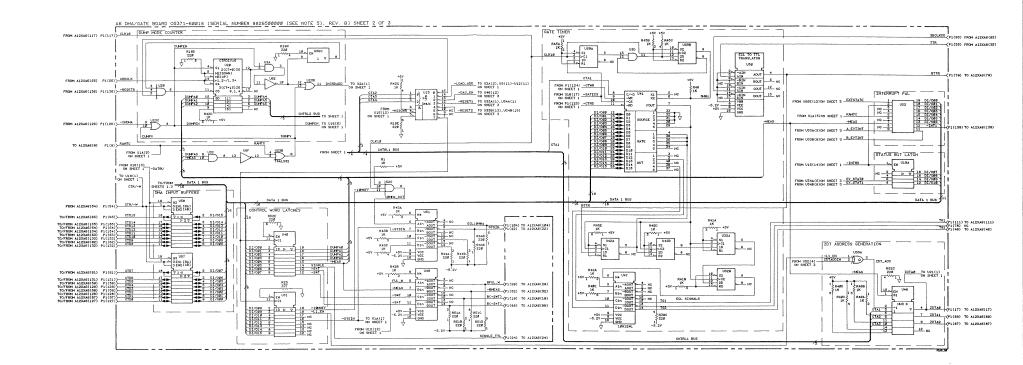

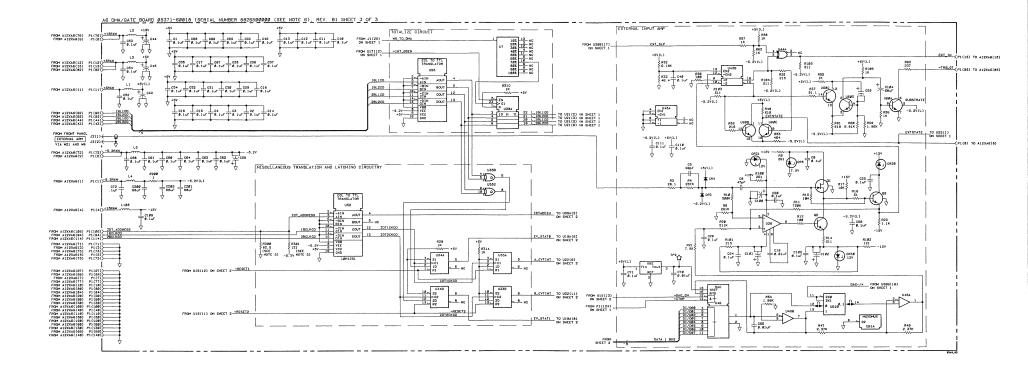

| <b>7</b> F    |                 | A/GATE BOARD 7F-1                               |

|               | 7F-1.           | A6 DMA/Gate Board                               |

|               | 7F-2.           | Introduction                                    |

|               | 7F-3.           | DMA Address Generation                          |

|               | 7F-4.           | DMA Input Buffers                               |

|               | 7F-5.           | Control Word Latches                            |

|               | 7F-6.           | Dump Mode Counter                               |

|               | 7F-7.           | Dump Mode Example                               |

#### SECTION TITLE

**7**G

#### 7F Cont'd. A6 DMA/GATE BOARD

| 7F-8.                                                                                                                                                                                       | System Timing Controller (STC)                                                                                                                                                                                                                                                                                                                                                                                      | 7F-6                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 7F-9.                                                                                                                                                                                       | Interrupt Generation PAL                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      |

| 7F-10.                                                                                                                                                                                      | ZDT Address Generation                                                                                                                                                                                                                                                                                                                                                                                              | 7F-6                                                                                                                                 |

| 7F-11.                                                                                                                                                                                      | Start and Stop Interpolator RAMs                                                                                                                                                                                                                                                                                                                                                                                    | 7F-7                                                                                                                                 |

| 7F-12.                                                                                                                                                                                      | PAL Section                                                                                                                                                                                                                                                                                                                                                                                                         | 7F-7                                                                                                                                 |

| 7F-13.                                                                                                                                                                                      | Totalize Circuitry                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                      |

| 7 <b>F-</b> 14.                                                                                                                                                                             | Overflow Detection Circuit                                                                                                                                                                                                                                                                                                                                                                                          | 7F-8                                                                                                                                 |

| 7F-15.                                                                                                                                                                                      | External Arm Input Amp                                                                                                                                                                                                                                                                                                                                                                                              | 7F-8                                                                                                                                 |

| 7F-16.                                                                                                                                                                                      | Signal Conditioning Stage                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                      |

| 7F-17.                                                                                                                                                                                      | High and Low Frequency Amplifier Stage                                                                                                                                                                                                                                                                                                                                                                              | 7F-8                                                                                                                                 |

| 7F-18.                                                                                                                                                                                      | Schmitt Stage                                                                                                                                                                                                                                                                                                                                                                                                       | 7F-9                                                                                                                                 |

| 7F-19.                                                                                                                                                                                      | External Arm Trigger Slope Stage                                                                                                                                                                                                                                                                                                                                                                                    | 7F-9                                                                                                                                 |

| 7F-20.                                                                                                                                                                                      | Buffer Stage                                                                                                                                                                                                                                                                                                                                                                                                        | 7F-9                                                                                                                                 |

| 7F <b>-</b> 21.                                                                                                                                                                             | Digital-to-analog (DAC) Stage                                                                                                                                                                                                                                                                                                                                                                                       | 7F-9                                                                                                                                 |

| 7F-22.                                                                                                                                                                                      | Troubleshooting Procedures                                                                                                                                                                                                                                                                                                                                                                                          | 7F-10                                                                                                                                |

| 7F-23.                                                                                                                                                                                      | Background                                                                                                                                                                                                                                                                                                                                                                                                          | 7F-11                                                                                                                                |

| 7F-24.                                                                                                                                                                                      | A6 Troubleshooting Approach                                                                                                                                                                                                                                                                                                                                                                                         | 7F-11                                                                                                                                |

| 7F-25.                                                                                                                                                                                      | A6 Failure Symptoms                                                                                                                                                                                                                                                                                                                                                                                                 | 7F-13                                                                                                                                |

| 7F-26.                                                                                                                                                                                      | A6 Troubleshooting Preparation                                                                                                                                                                                                                                                                                                                                                                                      | 7F-13                                                                                                                                |

| 7F-27.                                                                                                                                                                                      | A6 Troubleshooting Procedures                                                                                                                                                                                                                                                                                                                                                                                       | 7F-14                                                                                                                                |

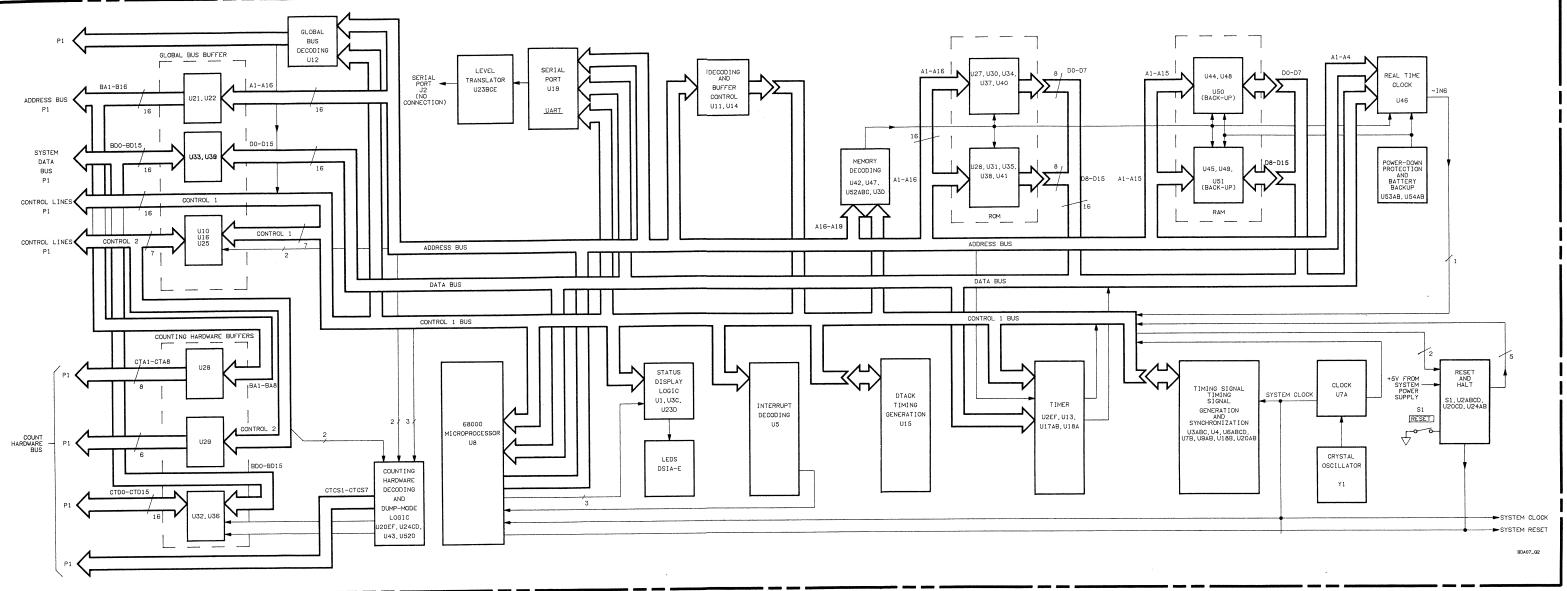

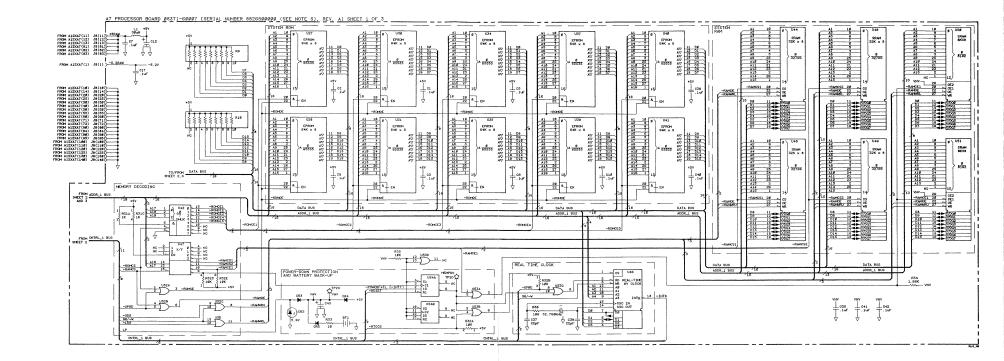

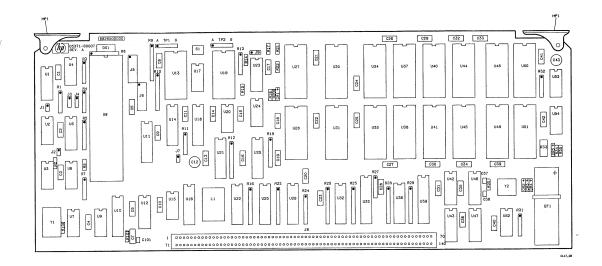

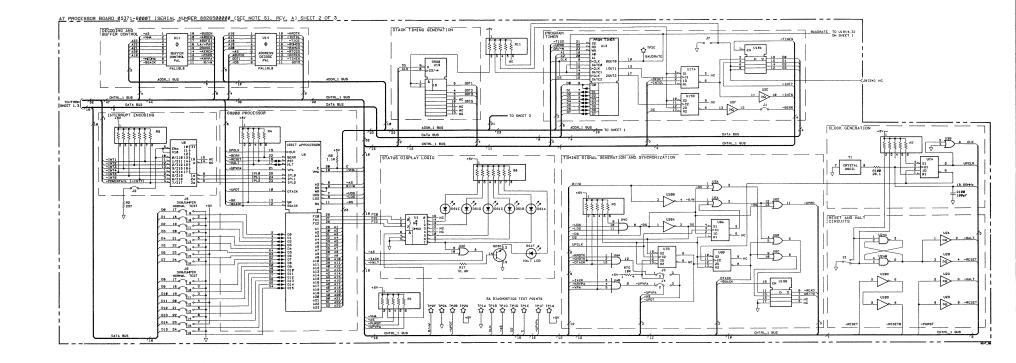

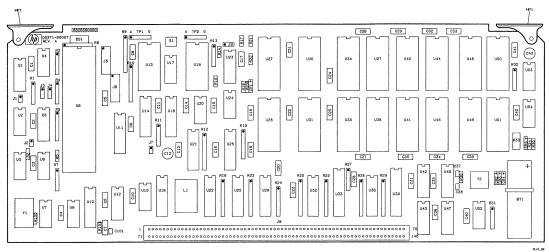

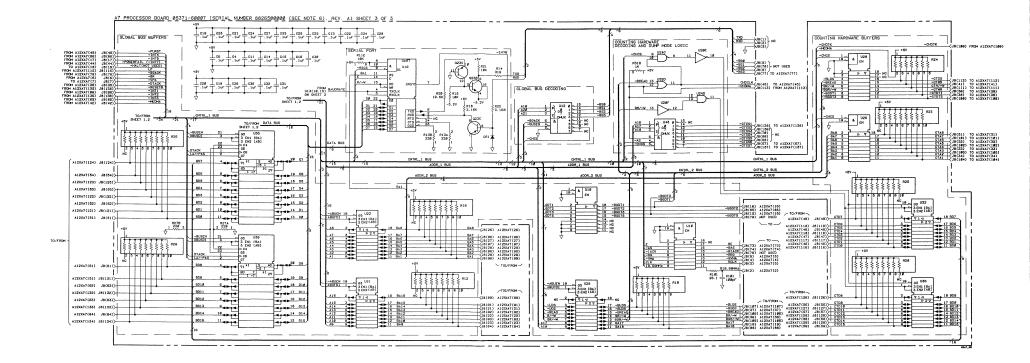

| A7 PR                                                                                                                                                                                       | OCESSOR BOARD                                                                                                                                                                                                                                                                                                                                                                                                       | 7G-1                                                                                                                                 |

| 7G-1.                                                                                                                                                                                       | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | . – –                                                                                                                                |

|                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                     | 7G-1                                                                                                                                 |

| 7G-1.                                                                                                                                                                                       | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1                                                                                                                         |

| 7G-1.<br>7G-2.                                                                                                                                                                              | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4                                                                                                                 |

| 7G-1.<br>7G-2.<br>7G-3.                                                                                                                                                                     | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4                                                                                                         |

| 7G-1.<br>7G-2.<br>7G-3.<br>7G-4.                                                                                                                                                            | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4<br>7G-4                                                                                                 |

| 7G-1.<br>7G-2.<br>7G-3.<br>7G-4.<br>7G-5.                                                                                                                                                   | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4<br>7G-4<br>7G-4                                                                                         |

| 7G-1.<br>7G-2.<br>7G-3.<br>7G-4.<br>7G-5.<br>7G-6.                                                                                                                                          | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4<br>7G-4<br>7G-4<br>7G-5                                                                                 |

| 7G-1.<br>7G-2.<br>7G-3.<br>7G-4.<br>7G-5.<br>7G-6.<br>7G-7.                                                                                                                                 | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4<br>7G-4<br>7G-4<br>7G-5<br>7G-5                                                                         |

| 7G-1.<br>7G-2.<br>7G-3.<br>7G-4.<br>7G-5.<br>7G-6.<br>7G-7.<br>7G-8.                                                                                                                        | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4<br>7G-4<br>7G-4<br>7G-5<br>7G-5<br>7G-5                                                                 |

| 7G-1.<br>7G-2.<br>7G-3.<br>7G-4.<br>7G-5.<br>7G-6.<br>7G-7.<br>7G-8.<br>7G-9.                                                                                                               | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4<br>7G-4<br>7G-4<br>7G-5<br>7G-5<br>7G-5<br>7G-6<br>7G-6                                                 |

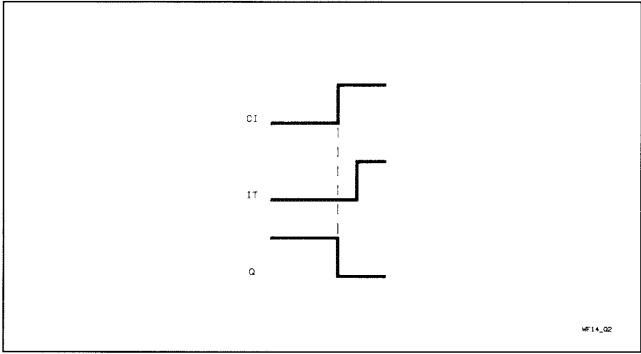

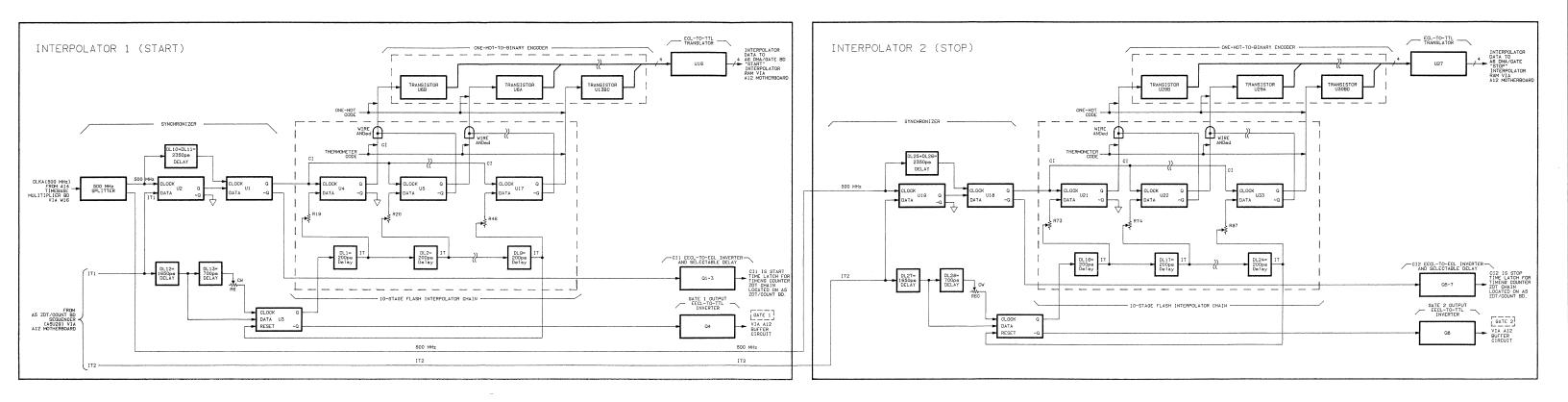

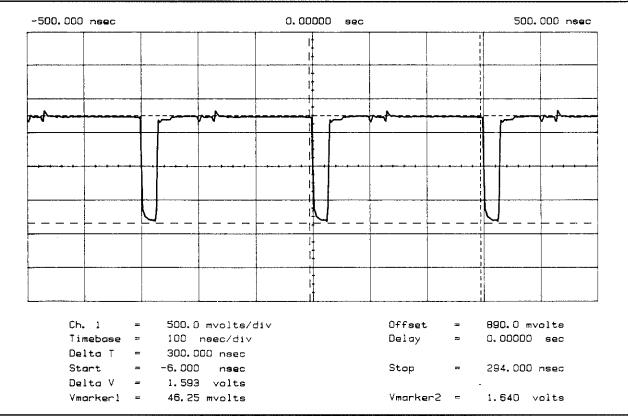

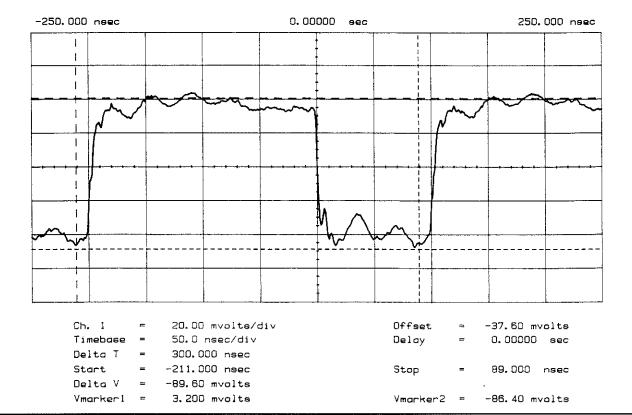

| 7G-1.<br>7G-2.<br>7G-3.<br>7G-4.<br>7G-5.<br>7G-6.<br>7G-7.<br>7G-8.<br>7G-9.<br>7G-10.                                                                                                     | A7 Processor Board                                                                                                                                                                                                                                                                                                                                                                                                  | 7G-1<br>7G-1<br>7G-4<br>7G-4<br>7G-4<br>7G-4<br>7G-5<br>7G-5<br>7G-5<br>7G-6<br>7G-6<br>7G-6                                         |