# 2430A DIGITAL OSCILLOSCOPE SECVICE

# LIST OF ILLUSTRATIONS

| rigure |                                                             | Page   |

|--------|-------------------------------------------------------------|--------|

|        | The 2430A Digital Oscilloscope                              | . vii  |

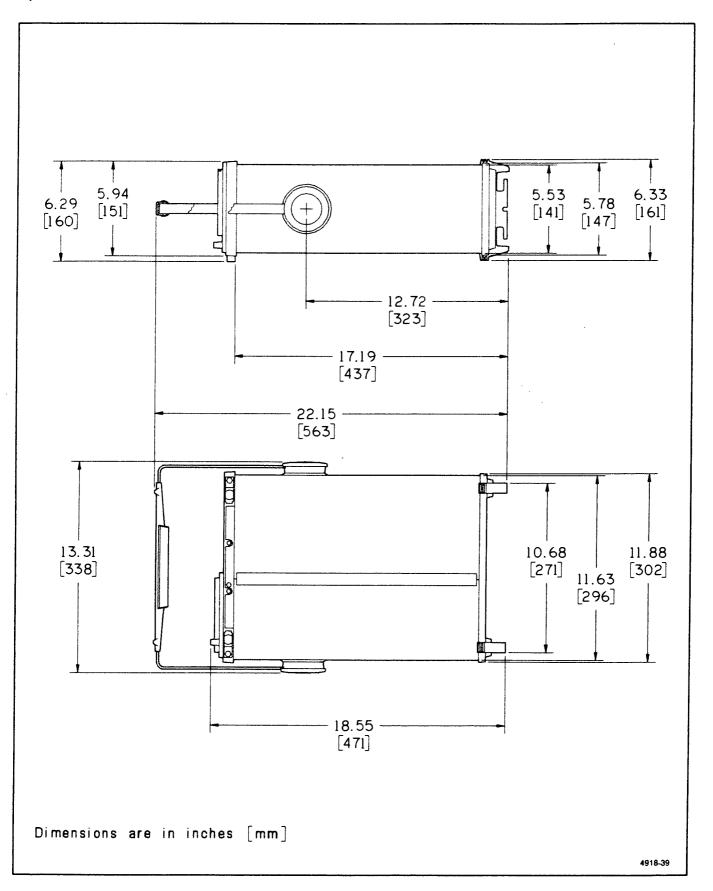

| 1-1    | Dimensional drawing                                         | . 1-22 |

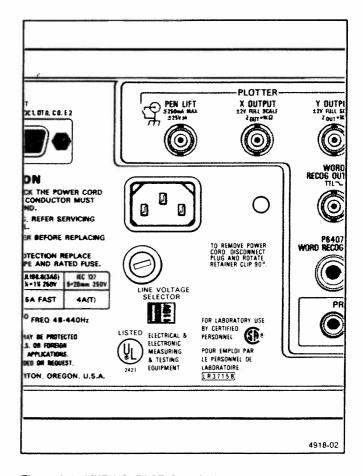

| 2-1    | LINE VOLTAGE SELECTOR, line fuse, and power cord receptacle | 2-1    |

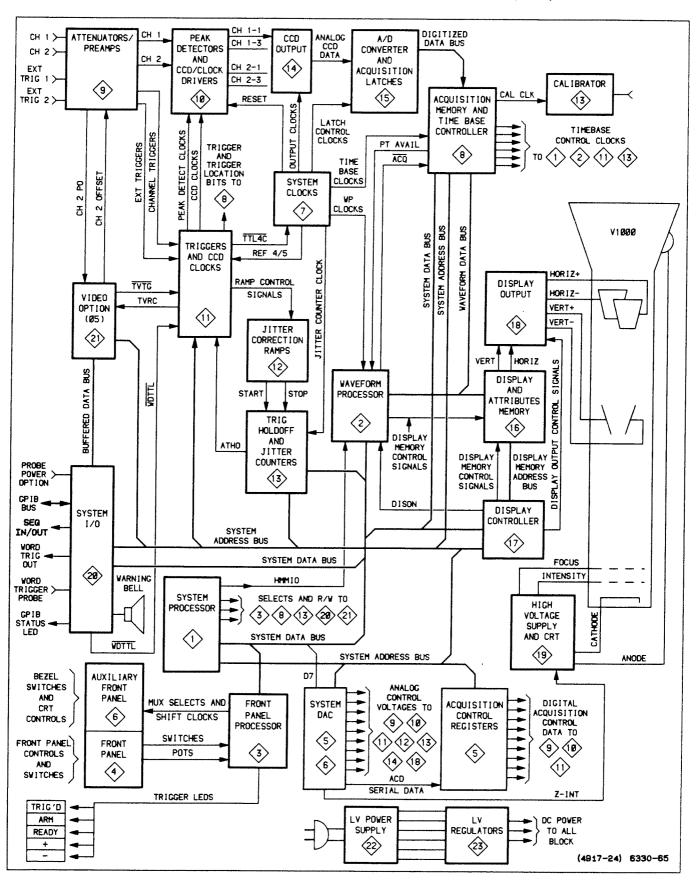

| 3-1    | 2430A simplified block diagram                              | 3-3    |

| 3-2    | Simplified Memory Map of the 2430A                          | 3-18   |

| 3-3    | System Clock waveforms                                      | 3-37   |

| 3-4    | Simplified Peak Detector block diagram                      | 3-47   |

| 3-5    | Simplified CCD architecture                                 | 3-49   |

| 3-6    | Trigger Logic Array Control Data Byte                       | 3-53   |

| 3-7    | Jitter correction waveforms                                 | 3-57   |

| 3-8    | Readout State Machine flow chart                            | 3-71   |

| 3-9    | Vertical Vector Generator                                   | 3-73   |

| 3-10   | DC Restorer                                                 | 3-78   |

| 3-11   | GPIB data flow diagram                                      | 3-81   |

| 3-12   | GPIB three-wire handshake state diagram                     | 3-82   |

| 3-13   | Video Option waveforms                                      | 3-87   |

| 3-14   | Video Option field-sync identification                      | 3-88   |

| 3-15   | PWM Regulator and Inverter                                  | 3-94   |

| 3-16   | PWM switching waveforms                                     | 3-96   |

| 5-1    | Adjustment locations for Displays 4 through 6               | 5-4    |

| 5-2    | Display 5—Vertical and Horizontal Gain, Offset, and Vector  |        |

|        | Compensation adjustment pattern                             | 5-5    |

| 5-3    | Display 6—Integrator Time adjustment pattern                | 5-7    |

| 6-1    | Multipin connector                                          | 6-8    |

| 6-2    | Circuit board Location                                      |        |

| 6-3    | Installation sequence for installing the crt frame screws   | 6-23   |

| 6-4    | Trigger LED binary coding for diagnostic tests              | 6-29   |

| 6-5    | Main EXT DIAG Menu                                          | 6-30   |

| 6-6    | Initial troubleshooting chart                               | 6-36   |

| 6-7    | Mux Test waveforms                                          | 6-41   |

| 6-8    | Typical Register test waveforms                             | 6-54   |

| 6-9    | Front Panel µP diagnostics test                             | 6-78   |

| 6-10   | System µP data bit D7 in the Bus Isolate mode               |        |

# LIST OF ILLUSTRATIONS (cont)

| rage |                                                                            |

|------|----------------------------------------------------------------------------|

| 9-1  | Color codes for resistors and capacitors.                                  |

| 9-2  | Semiconductor lead configurations.                                         |

| 9-3  | Locating components on schematic diagrams and circuit board illustrations. |

| 9-4a | Detailed 2430A Block Diagram.                                              |

| 9-4b | Detailed 2430A Block Diagram (cont).                                       |

| 9-5  | A12—Processor Board.                                                       |

| 9-6  | A13—Side Board.                                                            |

| 9-7  | A14—Front Panel Board.                                                     |

| 9-8  | A10—Main Board.                                                            |

| 9-9  | A11—Timebase/Display Board.                                                |

| 9-10 | A17—High Voltage Board.                                                    |

| 9-11 | A16—I OW Voltage Power Supply Board                                        |

# **LIST OF TABLES**

| Table |                                                              | Page   |

|-------|--------------------------------------------------------------|--------|

| 1-1   | Electrical Characteristics                                   | -      |

| 1-2   | Environmental Characteristics                                | . 1-1  |

| 1-3   | Mechanical Characteristics                                   | . 1-19 |

| 1-4   | Option 05 (TV Trigger) Electrical Characteristics            | . 1-2  |

| 2-1   | Voltage, Fuse, and Power-Cord Data                           | . 2-2  |

| 3-1   | Host Memory-Mapped I/O                                       | . 3-20 |

| 3-2   | Processor Control Register Functions                         | 3-21   |

| 3-3   | Processor Miscellaneous Register (PMREG) Output Functions    | 3-22   |

| 3-4   | Waveform / P Address Decoding                                | 3-27   |

| 3-5   | Trigger Logic Array Addresses (6080h-6087h)                  | 3-52   |

| 3-6   | REF4/5 Frequency for Each SEC/DIV Setting                    | 3-54   |

| 3-7   | Phase Clock Array Control Lines (CC3 through CC0).           | 2 55   |

| 3-8   | Holdoff Delay Range for Current Source vs Charging Capacitor | 3-55   |

|       | Combinations                                                 | 3-59   |

| 3-9   | Side Board Address Decoding                                  | 3-61   |

| 4-1   | Test Equipment Required                                      | 4.0    |

| 4-2   | Accuracy Limits CH 1 and CH 2 CURSOR VOLTS Readout and A and | 4-2    |

|       | B TRIGGER LEVEL Readouts                                     | 4.40   |

| 4-3   | Minimum Display Level for CH 1 or CH 2 Triggering            | 4-10   |

| 4-4   | Minimum Signal Level for EXT1 or EXT2 Triggering             | 4-19   |

|       | This is a signal better for EXT2 Triggering                  | 4-21   |

| 6-1   | Relative Susceptibility to Static-Discharge Damage           | 6-3    |

| 6-2   | External Inspection Check List                               | 6-5    |

| 6-3   | Internal Inspection Check List                               | 6-6    |

| 6-4   | Power Supply Voltage and Ripple Limits                       | 6-10   |

| 6-5   | Maintenance Aids                                             | 6 10   |

| 6-6   | 2430A Troubleshooting Procedures                             | 6-13   |

| 6-7   | Video Option Troubleshooting                                 | 6-37   |

| 6-8   | INIT PANEL States                                            | 0-102  |

|       |                                                              | 0-1U0  |

### OPERATORS SAFETY SUMMARY

The general safety information in this part of the summary is for both operating and servicing personnel. Specific warnings and cautions will be found throughout the manual where they apply and do not appear in this summary.

### **Terms in This Manual**

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

### Terms as Marked on Equipment

CAUTION indicates a personal injury hazard not immediately accessible as one reads the markings, or a hazard to property, including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

### Symbols in This Manual

This symbol indicates where applicable cautionary or other information is to be found. For maximum input voltage see Table 1-1.

### Symbols as Marked on Equipment

DANGER — High voltage.

Protective gound (earth) terminal.

ATTENTION — Refer to manual.

#### **Power Source**

This product is intended to operate from a power source that will not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

### **Grounding the Product**

This product is grounded through the grounding conductor of the power cord. To avoid electrical shock, plug the power cord into a properly wired receptacle before making any connections to the product input or output terminals. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

### **Danger Arising from Loss of Ground**

Upon loss of the protective-ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulated) can render an electric shock.

#### Use the Proper Power Cord

Use only the power cord and connector specified for the instrument.

### Use the Proper Fuse

To avoid fire hazard, use only the fuse specified in the instrument parts list. A replacement fuse must meet the type, voltage rating, and current rating specifications for the fuse that it replaces.

### Do Not Operate in Explosive Atmospheres

To avoid explosion, do not operate this instrument in an atmosphere of explosive gasses.

### Do Not Remove Covers or Panels

To avoid personal injury, the instrument covers or panels should only be removed by qualified service personnel. Do not operate the instrument without covers and panels properly installed.

## **SERVICING SAFETY SUMMARY**

### FOR QUALIFIED SERVICE PERSONNEL ONLY

Refer also to the preceding Operators Safety Summary.

### **Do Not Service Alone**

Do not perform internal service or adjustment of this product unless another person capable of rendering first aid and resuscitation is present.

### Use Care When Servicing With Power On

Dangerous voltages exist at several points in this product. To avoid personal injury, do not touch exposed connections or components while power is on.

Disconnect power before removing protective panels, soldering, or replacing components.

### **Power Source**

This product is intended to operate from a power source that does not apply more than 250 volts rms bwetween the supply conductors or between either supply conductor and ground. A protective ground connection by way of the grounding connector in the power cord is essential for safe operation.

# **SPECIFICATION**

### INTRODUCTION

The TEKTRONIX 2430A Digital Oscilloscope is a portable, dual-channel instrument with a maximum digitizing rate of 100 Megasamples per second. The scope is capable of simultaneous acquisition of Channel 1 and Channel 2 input signals. It has a real-time useful storage bandwidth of 40 MHz for single-event acquisitions, with an equivalent-time bandwidth of 150 MHz when repetitive acquisitions are acquired. Since both channels are acquired simultaneously, the XY display is available to full bandwidth. Options include a Word Recognition Probe, Video signal triggering, Probe Power, and Rackmounting.

The instrument is microprocessor controlled and menu driven, displaying at the top of the screen alphanumeric CRT readouts of the vertical and horizontal scale factors, trigger levels, trigger source, and cursor measurements. Menus, displayed at the bottom of the CRT display, are used by the operator to select the operating mode.

A user makes decisions as to what operation and mode setup the instrument must have to make the measurement wanted and then selects the proper functions using a combination of front-panel buttons and the displayed menu.

Five menu buttons mounted on the CRT bezel are used to make selections from the entry choices displayed. The top line of the menu display usually contains the menu title, and the bottom line labels the buttons with the control functions they select. The selection is made (indicated by an underscoring of the menu label in the display) when the bezel button below the selected function is pressed. The menus, system operating modes, and auxiliary functions are described in Section 5, "Controls, Connectors, and Indicators" of the Operators manual included with this instrument, and the "Getting Acquainted" procedure in Section 1 of that manual familiarizes the user with menu operation.

### **VERTICAL SYSTEM**

The two vertical channels have calibrated deflection factors from 2 mV to 5 V per division in a 1-2-5 sequence of 14 steps. Use of coded probes having attenuation factors of 1X, 10X, 100X, and 1000X extends the minimum sensitivity to 5,000 V per division (with the 1000X probe) and the maximum sensitivity to 200  $\mu$ V per division (using a 1X probe in SAVE or AVERAGE expanded mode).

VOLTS/DIV readouts are automatically switched to display a correct scale factor when properly coded probes are attached. Each channel can be separately inverted. ADD and MULT are display functions provided by the processor system.

In SAVE mode, the waveforms may be both horizontally and vertically repositioned, expanded horizontally and vertically, added to each other, or multiplied together for either XY or YT displays.

### HORIZONTAL SYSTEM

Horizontal display modes of A, A INTEN, and B Delayed are available. The time base has 28 calibrated SEC/DIV settings in a 1-2-5 sequence from 5 ns per division to 5 s per division. An External Clock mode is provided that accepts clocking signals from 1 MHz to 100 MHz.

The B Trace and the intensified zone on the A INTEN Trace may be delayed by time with respect to the A trigger, and a DELAY by EVENTS function permits the A display to be delayed by a selected number of B Trigger events. In the case of DELAY by EVENTS, the B Trigger SOURCE, COUPLING, SLOPE, and LEVEL controls define the nature of the signal needed to produce events triggering. The number of events required to satisfy the

delay may be set from 1 to 65,536, with a resolution of one event. The DELTA DELAY feature produces two independently settable delayed B Traces in DELAY by TIME.

### TRIGGER SYSTEM

The trigger system of the scope provides many features for selecting and processing a signal used in triggering the acquisition system. The conventional features of SOURCE selection, Trigger LEVEL control, Trigger SLOPE, Trigger MODE, and CPLG (coupling) include enhancements not normally found in a conventional oscilloscope.

The choices of VERT, CH1 or CH2, EXT1 or EXT2, LINE, and A\*B or WORD (16-bit data word recognition) are available as SOURCE selections for triggering A Horizontal Mode acquisitions. These sources for trigger signals provide a wide range of applications involving specialized triggering requirements. Except for A\*B (A AND B) and LINE (power-source frequency), the same Trigger SOURCE selections are available for triggering B acquisitions. The selected trigger signal is conditioned by the choice of input CPLG (coupling). These coupling selections are AC, DC, HF REF, LF REJ, and NOISE REJ. LEVEL control provides a settable amplitude (with CRT readout) at which triggering will occur, and SLOPE control determines on which slope of the triggering signal (plus or minus) the acquisition is triggered.

Trigger MODE choices are AUTO LEVEL, AUTO, NORM, and SINGLE SEQ (single sequence), for the A and A INTENSIFIED Modes, and Triggerable After Delay and Runs After Delay, for the B Mode. AUTO LEVEL provides for automatic leveling on the applied trigger signal. AUTO MODE produces an auto trigger in the event a trigger signal is either not received or not within the limits needed to produce a triggering event. When triggering conditions are met, a normal triggered display results. At SEC/DIV settings of 100 ms per division and longer, the AUTO MODE switches to ROLL. In ROLL MODE, the display is continually updated and trigger signals are disregarded.

NORM (normal) trigger MODE requires that all triggering requirements are met before an acquisition will take place. SINGLE SEQ (single sequence) MODE is a variation of the conventional single-shot displays found on many previous oscilloscopes. In SINGLE SEQ, a single complete acquisition is done on all called-up VERTICAL MODES. Since an acquisition depends on the acquisition mode in effect, many of the scope operating features are altered in SINGLE SEQ. A complete description of this

mode is discussed in "Controls, Connectors, and Indicators" in Section 5 of the Operators manual.

The user has a choice of trigger points within the acquired waveform record by selecting the amount of pre-trigger data displayed. The trigger location in the record is selectable from a choice of five pretrigger lengths beginning at one-eighth of the record length and increasing to seven-eighths of the record length. A record trigger position is independently selectable for both A and B acquisitions. Additional trigger positions in the record are selectable via the GPIB interface commands.

### **CURSOR MEASUREMENTS**

Time and Voltage cursors are provided for making parametric measurements on the displayed waveforms. Time may be measured either between the cursor positions (DELTA TIME) or between a selected cursor and the trigger point of an acquired waveform (ABSOLUTE). Time cursor readouts are scaled in seconds, degrees, or percentage values. The 1/TIME cursors may be scaled in hertz (Hz), degrees, or percentage.

Voltage cursor measurements on a waveform display can be selected to read either the voltage difference between the cursor positions or the absolute voltage position of a selected cursor with respect to ground. The volts measurement readouts may be scaled in units of volts, decibels (dB), or percent. The Voltage cursors and Time cursors may also be coupled to track together (V@T and SLOPE) and assigned to a particular waveform for ease in making peak-to-peak and slope waveform measurements. The units for V@T may be volts, percent, or dB; SLOPE may have units of slope (VOLTS/SEC), percent (VOLTS/VOLT), or dB.

### **WAVEFORM ACQUISITION**

Waveforms may be acquired in different modes, depending on the measurement requirements. The acquisition modes of NORMAL, ENVELOPE, and AVG (averaging) provide the user with a wide range of measurement adaptability. NORMAL mode provides a continuous acquisition producing a "live" waveform display similar to that seen with an analog oscilloscope. AVG (averaging) mode is especially useful for improving the signal-to-noise ratio of the displayed waveform. Small amplitude signals masked by noise become easily visible for making measurements and analysis by averaging from 2 to 256 acquisitions for removing uncorrelated noise.

Equivalent-time sampling, used for NORMAL and AVG acquisition of recurring periodic signals, extends the useful storage bandwidth to 150 MHz when the REPETITIVE mode is on. Randomly acquired data points taken from a periodic signal are used to fill the complete record of the signal waveform display. Depending on the SEC/DIV setting, as few as 10 samples (at 5 ns/DIV) or as many as 409 (at 200 ns/DIV) samples may be obtained on each trigger event. The user sees the waveform display build up as dots until the entire 1024 data point record is filled.

ENVELOPE mode saves the maximum and minimum data-point values over a selected number of acquisitions from 1 to 256 plus CONT (continuous). The display presents a visual image of the amount of change (envelope) that occurs to a waveshape during the accumulated acquisitions. Frequency, phase, amplitude, and position changes are easily identified when acquiring in ENVELOPE mode. The glitch-catching capability of ENVELOPE mode can capture single-event pulses as narrow as 2 ns at the slowest SEC/DIV setting of 5 seconds per division.

Horizontally, the record length of acquired waveforms is 1024 data points (512 max/min pairs in ENVELOPE mode), of which 500 make up a one-screen display (50 data points per division for 10 divisions). The entire record may be viewed by using the Horizontal POSITION control to position any portion of the record within the viewing area.

### STORAGE AND I/O

Acquired waveforms may be saved in any of four REF waveform nonvolatile memories. Any or all of the saved reference waveforms may be displayed for comparison with the waveforms being currently acquired. The source and destination of waveforms to be saved may be user designated. Assignment can be made to save either channel 1 or channel 2 (or the results of an addition or multiplication of the two channels) to any REF memory or to move a stored reference from one REF memory to another. Reference waveforms may also be written into a REF memory location via the GPfB interface.

The scope is fully controllable and capable of sending and receiving waveforms via the standard equipped GPIB interface. This feature makes the instrument ideal for making automated measurements in a production or research and development environment that calls for repetitive data taking. Self- calibration and self-diagnostic features built into the scope to aid in fault detection and servicing are also accessible via commands sent from the GPIB controller.

Another standard feature is the "DEVICES" setting for GPIB Interface control. This feature allows the user to output waveforms (and other on-screen information) to either a HP® Graphics Printer or Plotter from the scope frontpanel, providing a way to obtain hard copies of acquired waveforms without putting the scope into a system controller environment.

### **EXTENDED FEATURES**

There are several other features incorporated into this instrument designed to make it more usable, namely, the HELP, AUTOsetup, MEASURE, and AutoStep Sequencer features.

**HELP:** The HELP function can be used to display operational information about any front-panel control. When HELP mode is in effect, manipulating almost any front-panel control causes the scope to display information about that control. When HELP is first invoked, an introduction to HELP is displayed on screen.

**AUTOsetup:** The AUTOsetup function is used to automatically setup the scope for a viewable display based on the input signal. The user can specify the waveform characteristic the display is optimized for (front-edge, period, etc.) from a menu displayed upon executing AUTOsetup.

**MEASURE:** MEASURE automatically extracts parameters from signal input to the scope. In the "SNAPSHOT" mode, 20 different waveform parameters are extracted and displayed for a single acquisition. In the continuous extraction mode, up to four parameters are extracted continuously as the instrument continues to acquire.

AutoStep Sequencer (PRGM): With AutoStep, the user can save single front-panel setups or sequences of setups and associated flow control and Input/Output actions for later recall. If MEASURE and/or OUTPUT are saved as part of these setups they can be used for automatic parameter extraction and data printout. 100 to 800 front-panel setups (depending on complexity) can be stored in one or more sequences.

The complete descriptions of these four features are found in Section 5 of the Operators manual included with this instrument.

The following items are standard accessories shipped with the scope instrument:

- 2 Probe packages

- 1 Snap-lock accessories pouch

- 1 Zip-lock accessories pouch

- Operators manual

- 1 Programmer's Reference Guide

- 1 Users Reference Guide

- 1 Fuse

- 1 Power cord (installed)

- 1 Blue plastic CRT filter (installed)

- 1 Clear plastic CRT filter

- 1 Front-panel cover

For part numbers and further information about standard accessories and a list of the optional accessories, refer to "Options and Accessories" (Section 7) in this manual. For additional information on accessories and ordering assistance, contact your Tektronix representative or local Tektronix Field Office.

### PERFORMANCE CONDITIONS

The following electrical characteristics (Table 6-1) apply when the scope has been calibrated at an ambient temperature between  $+20^{\circ}$ C and  $+30^{\circ}$ C, has had a warmup period of at least 20 minutes and is operating at an ambient temperature between  $-15^{\circ}$ C and  $+55^{\circ}$ C (unless otherwise noted).

Items listed in the "Performance Requirements" column are verifiable qualitative or quantitative limits that define the measurement capabilities of the instrument.

Environmental characteristics are given in Table 6-2. The scope meets the environmental requirements of MILT-28800C for Type III, Class 3, Style D equipment, with the humidity and temperature requirements defined in paragraphs 3.9.2.2, 3.9.2.3, and 3.9.2.4. The rackmounted scope meets the vibration and shock requirements of MILT-28800C for Type III, Class 5, Style D equipment when mounted using the rackmount rear-support kit supplied with both the 1R Option and the Rackmount Conversion kit.

Mechanical characteristics of the scope are listed in Table 6-3.

Video Option characteristics are given in Table 6-4.

### RECOMMENDED ADJUSTMENTS SCHEDULE

For optimum performance to specification, the internal SELF CAL should be done:

- If the operating temperature is changed by more that 5°C since the last SELF CAL was performed.

- Immediately before before making measurements requiring the highest degree of accuracy.

Table 1-1 **Electrical Characteristics**

| Characteristics                                                                                                   | Performance Requirements                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACQUISITION S                                                                                                     | YSTEM—CHANNEL 1 AND CHANNEL 2                                                                                                                                                                                                                                                                            |

| Resolution                                                                                                        | 8 bits.ª                                                                                                                                                                                                                                                                                                 |

|                                                                                                                   | Displayed vertically with 25 digitization levels (DL) <sup>b</sup> per division, 10.24 divisions dynamic range. <sup>a</sup>                                                                                                                                                                             |

| Record Length                                                                                                     | 1024 samples.a                                                                                                                                                                                                                                                                                           |

|                                                                                                                   | Displayed horizontally with 50 samples per division, 20.48-division trace length. <sup>a</sup>                                                                                                                                                                                                           |

| Sample Rate                                                                                                       | 10 samples per second to 100 megasamples per second (5 s per division to 500 ns per division).                                                                                                                                                                                                           |

| Sensitivity                                                                                                       |                                                                                                                                                                                                                                                                                                          |

| Range                                                                                                             | 80 $\mu$ V per DL to 0.2 V per DL in a 1-2-5 sequence of 11 steps (2 mV per division to 5 V per division).                                                                                                                                                                                               |

| Accuracy                                                                                                          |                                                                                                                                                                                                                                                                                                          |

| Normal and Average Modes                                                                                          | Within ± (2% + 1 DL) at any VOLTS/DIV setting for a signal 1 kHz or less contained within ±75 DL (±3 divisions) of center when an Autocal has been performed within ±15°C of the operating temperature. Measured on a four- or five-division signal with VOLTS or V@T cursors; UNITS set to delta volts. |

| Envelope Mode                                                                                                     | Add 1% to Normal Mode specifications.                                                                                                                                                                                                                                                                    |

| Variable Range                                                                                                    | Continuously variable between VOLTS/DIV settings. Extends sensitivity to 0.5 V per DL or greater, 12.5 V per division or greater.                                                                                                                                                                        |

| Bandwidth                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| Normal and Average Mode; Repet off;                                                                               | DC to 40 MHz (calculated useful storage bandwidth—USB).a                                                                                                                                                                                                                                                 |

| SEC/DIV at 0.5 μs or Faster                                                                                       | $USB = \frac{F_{\text{(sample freq max)}}^{c}}{2.5}$                                                                                                                                                                                                                                                     |

| Normal and Average Modes with Repet On or Continuous Envelope Mode; SEC/DIV at 0.2 µs or Faster (-3 dB bandwidth) | DC to 150 MHz.                                                                                                                                                                                                                                                                                           |

|                                                                                                                   | Bandwidth with a P6133 probe is checked using the obtainable reference signal (six divisions or less) from a terminated 50 $\Omega$ system via probe-tip-to-BNC adapter. <sup>a</sup>                                                                                                                    |

|                                                                                                                   | Bandwidth with external termination is checked using a six-division reference signal from terminated 50 $\Omega$ system. <sup>a</sup>                                                                                                                                                                    |

|                                                                                                                   | Bandwidth with internal termination is checked using a six-division reference signal from a terminated 50 $\Omega$ system.                                                                                                                                                                               |

<sup>\*</sup>Performance Requirement not checked in the manual.

b"DL" is the abbreviation for "digitization level". A DL is the smallest voltage level change that can be resolved by the Internal 8-bit A-D converter, with the input scaled to the VOLTS/DIV setting of the channel used. Expressed as a voltage, a DL is equal to 1/25 of a division times the VOLTS/DiV setting.

<sup>&</sup>lt;sup>c</sup>Sample frequency max. is 100 MHz.

Table 1-1 (cont)

| Characteristics                                                                              | Performance Requirements                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AC Coupled Lower —3 dB Point                                                                 |                                                                                                                                                                                                                        |  |  |

| 1X Probe                                                                                     | 10 Hz or less. <sup>8</sup>                                                                                                                                                                                            |  |  |

| 10X Probe                                                                                    | 1 Hz or less. <sup>8</sup>                                                                                                                                                                                             |  |  |

| Step Response, Repet and Average On;<br>Average Set to 16                                    | ·                                                                                                                                                                                                                      |  |  |

| Rise Time                                                                                    | 2.3 ns or less (calculated). <sup>a</sup>                                                                                                                                                                              |  |  |

|                                                                                              | $T_{r} (in ns) = \frac{350}{BW (in MHz)}$                                                                                                                                                                              |  |  |

| Envelope Mode Pulse Response                                                                 |                                                                                                                                                                                                                        |  |  |

| Minimum Single Pulse Width for 50% or Greater Amplitude Capture at 85% or Greater Confidence | 2 ns. <sup>a</sup>                                                                                                                                                                                                     |  |  |

| Minimum Single Pulse Width for Guaranteed 50% or Greater Amplitude Capture                   | 4 ns.ª                                                                                                                                                                                                                 |  |  |

| Minimum Single Pulse Width for Guaranteed 80% or Greater Amplitude Capture                   | 8 ns.ª                                                                                                                                                                                                                 |  |  |

| Channel Isolation                                                                            | 100:1 or greater attenuation of the deselected channel at 100 MHz; 50:1 or greater attenuation at 150 MHz, for a 10-division input signal from 2 mV/div to 500 mV/div; with equal VOLTS/DIV settings on both channels. |  |  |

| Acquired Channel 2 Signal Delay with Respect to Channel 1 Signal at Full Bandwidth           | ± 250 ps.ª                                                                                                                                                                                                             |  |  |

| Input R and C (1 MΩ)                                                                         |                                                                                                                                                                                                                        |  |  |

| Resistance                                                                                   | 1 M $\Omega$ ±0.5%.8                                                                                                                                                                                                   |  |  |

|                                                                                              | In each attenuator, the input resistance of all VOLTS/DIV positions is matched to within 0.5%. <sup>a</sup>                                                                                                            |  |  |

| Capacitance                                                                                  | 15 pF ±2 pF.a                                                                                                                                                                                                          |  |  |

|                                                                                              | In each attenuator, the input capacitance of all VOLTS/DIV positions is matched to within 0.5 pF.a                                                                                                                     |  |  |

<sup>\*</sup>Performance Requirement not checked in the manual.

Table 1-1 (cont)

| Characteristics                                                              | Performance Requirements                                                                                                                                 |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input R (50 Ω)                                                               |                                                                                                                                                          |

| Resistance                                                                   | $50 \Omega \pm 1\%$ .a                                                                                                                                   |

| VSWR (DC to 150 MHz)                                                         | 1.3:1 or better. <sup>a</sup>                                                                                                                            |

| Maximum Input Voltage                                                        | 5 V rms; 0.5 W-sec for any one-second interval for instantaneous voltages from 5 V to 50 V.                                                              |

| Maximum Input Voltages                                                       |                                                                                                                                                          |

| Input Coupling Set to DC, AC, or GND                                         | 400 V (dc + peak ac); 800 V p-p ac at 10 kHz or less.a                                                                                                   |

| Common-Mode Rejection Ratio (CMRR);<br>ADD Mode with Either Channel Inverted | At least 10:1 at 50 MHz for common-mode signals of 10 divisions or less with VARIABLE VOLTS/DIV adjusted for best CMRR at 50 kHz.                        |

| POSITION                                                                     |                                                                                                                                                          |

| Range                                                                        | $\pm$ (9.3 to 10.4) div., at 50 mV per division with INVERT off, when Self Cal has been done within $\pm5^{\circ}\text{C}$ of the operating temperature. |

| Gain Match Between NORMAL and SAVE                                           | ±3 DLs for positions within ±5 divisions from center.                                                                                                    |

| Low-Frequency Linearity                                                      |                                                                                                                                                          |

| Normal or Average Mode                                                       | 3 DLs or less compression or expansion of a two-division,<br>center-screen signal when positioned anywhere within the acquisi-<br>tion window.           |

| 20 MHz Bandwidth Limiter                                                     |                                                                                                                                                          |

| -3 dB Bandwidth                                                              | 13 MHz to 24 MHz.                                                                                                                                        |

| 50 MHz Bandwidth Limiter                                                     |                                                                                                                                                          |

| -3 dB Bandwidth                                                              | 40 MHz to 55 MHz.                                                                                                                                        |

| Rise Time                                                                    | 6.3 ns to 8.7 ns. <sup>a</sup>                                                                                                                           |

|                                                                              | With a five-division, fast-rise step (rise time of 300 ps or less) using 50 $\Omega$ dc input coupling and VOLTS/DIV setting of 10 mV. <sup>a</sup>      |

<sup>\*</sup>Performance Requirement not checked in the manual.

Table 1-1 (cont)

| Characteristics                                                                         | Performance Requirements                                                                                                                          |  |  |  |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TRIGGERING—A and B                                                                      |                                                                                                                                                   |  |  |  |

| Minimum P-P Signal Amplitude for Stable Triggering from Channel 1, Channel 2, or ADD    |                                                                                                                                                   |  |  |  |

| A Trigger                                                                               |                                                                                                                                                   |  |  |  |

| DC Coupled                                                                              | 0.35 division from DC to 50 MHz, increasing to 1.0 division at 150 MHz; 1.5 divisions at 150 MHz in ADD mode.                                     |  |  |  |

| NOISE REJ Coupled                                                                       | 1.2 divisions or less from DC to 50 MHz, increasing to 3 divisions<br>at 150 MHz; 4.5 divisions at 150 MHz in ADD mode.                           |  |  |  |

| AC Coupled                                                                              | 0.35 division from 60 Hz to 50 MHz; increasing to 1.0 division at 150 MHz, 1.5 divisions at 150 MHz in ADD mode. Attenuates signals below 60 Hz.  |  |  |  |

| HF REJ Coupled                                                                          | 0.50 division from DC to 30 kHz. Attenuates signals above 30 kHz.                                                                                 |  |  |  |

| LF REJ Coupled                                                                          | 0.50 division from 80 kHz to 50 MHz; increasing to 1.0 division at 150 MHz; 1.5 divisions at 150 MHz in ADD mode. Attenuates signal below 80 kHz. |  |  |  |

| B Trigger                                                                               | Multiply all A Trigger specifications by two.                                                                                                     |  |  |  |

| A∗B Selected                                                                            | Multiply all A Trigger specifications by two.                                                                                                     |  |  |  |

| from EXT TRIG 1 or EXT TRIG 2 Source  A Trigger  EXT Gain = 1                           |                                                                                                                                                   |  |  |  |

| DC Coupled                                                                              | 17.5 mV from DC to 50 MHz, increasing to 50 mV at 150 MHz.                                                                                        |  |  |  |

| NOISE REJ Coupled                                                                       | 60 mV or less from DC to 50 MHz; increasing to 150 mV at 150 MHz.                                                                                 |  |  |  |

| AC Coupled                                                                              | 17.5 mV from 60 Hz to 50 MHz; increasing to 50 mV at 150 MHz. Attenuates signals below 60 Hz.                                                     |  |  |  |

| HF REJ Coupled                                                                          | 25 mV from DC to 30 kHz.                                                                                                                          |  |  |  |

| LF REJ Coupled                                                                          | 25 mV from 80 kHz to 50 MHz; increasing to 50 mV at 150 MHz.                                                                                      |  |  |  |

| EXT Gain = ÷5                                                                           | Amplitudes are five times those specified for Ext Gain = 1.                                                                                       |  |  |  |

| B Trigger                                                                               | Multiply all A Trigger amplitude specifications by two.                                                                                           |  |  |  |

| A+B Selected                                                                            | Multiply all A Trigger amplitude specifications by two.                                                                                           |  |  |  |

| Maximum P-P Signal Rejected by NOISE REJ Coupling Signals within the Vertical Bandwidth |                                                                                                                                                   |  |  |  |

| Channel 1 or Channel 2 Source                                                           | 0.4 division or greater for VOLTS/DIV settings of 10 mV and higher.                                                                               |  |  |  |

|                                                                                         | Maximum noise rejected is reduced at 2 mV per division and 5 mV per division.                                                                     |  |  |  |

| EXT TRIG 1 or EXT TRIG 2 Source                                                         | 20 mV or greater when Ext Trig Gain = 1. 100 mV or greater when Ext Trig Gain = $\div$ 5.                                                         |  |  |  |

Table 1-1 (cont)

| Characteristics                                                                          | Performance Requirements                                                                                                                                   |  |  |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EXT TRIG 1 and EXT TRIG 2 Inputs                                                         |                                                                                                                                                            |  |  |

| Resistance                                                                               | 1 MΩ ±1%.ª                                                                                                                                                 |  |  |

| Capacitance                                                                              | 15 pF ±3 pF. <sup>a</sup>                                                                                                                                  |  |  |

| Maximum Input Voltage                                                                    | 400 V (dc + peak ac); 800 V p-p ac at 10 kHz or less. <sup>a</sup>                                                                                         |  |  |

| LEVEL Control Range                                                                      |                                                                                                                                                            |  |  |

| Channel 1 or Channel 2 Source                                                            | ±18 divisions × VOLTS/DIV setting.a                                                                                                                        |  |  |

| EXT TRIG 1 or EXT TRIG 2 Source                                                          |                                                                                                                                                            |  |  |

| EXT GAIN = 1                                                                             | ± 0.9 volt.ª                                                                                                                                               |  |  |

| EXT GAIN = ÷5                                                                            | ±4.5 volts.ª                                                                                                                                               |  |  |

| LEVEL Readout Accuracy (for triggering signals with transition times greater than 20 ns) |                                                                                                                                                            |  |  |

| Channel 1 or Channel 2 Source                                                            |                                                                                                                                                            |  |  |

| DC Coupled                                                                               |                                                                                                                                                            |  |  |

| +15°C to +35°C                                                                           | Within $\pm$ [3% of setting $+$ 3% of p-p signal $+$ (0.2 division $\times$ VOLTS/DIV setting) $+$ 0.5 mV $+$ (0.5 mV $\times$ probe attenuation factor)]. |  |  |

| -15°C to $+55$ °C (excluding $+15$ °C to $+35$ °C)                                       | Add (1.5 mV x probe attenuation) to +15°C to +35°C specification. <sup>a</sup>                                                                             |  |  |

| NOISE REJ Coupled                                                                        | Add $\pm$ (0.6 division $\times$ VOLTS/DIV setting) to DC Coupled specifications.                                                                          |  |  |

|                                                                                          | Checked at 50 mV per division.                                                                                                                             |  |  |

| EXT TRIG 1 or EXT TRIG 2 Source                                                          | ,                                                                                                                                                          |  |  |

| EXT GAIN = 1                                                                             |                                                                                                                                                            |  |  |

| DC Coupled                                                                               | Within $\pm$ [3% of setting + 4% of p-p signal + 10 mV + (0.5 mV $\times$ probe attenuation factor)].                                                      |  |  |

| NOISE REJ Coupled                                                                        | Add ±30 mV to DC Coupled specifications.                                                                                                                   |  |  |

| EXT GAIN = ÷5                                                                            |                                                                                                                                                            |  |  |

| DC Coupled                                                                               | Within $\pm$ [3% of setting + 4% of p-p signal + 50 mv + (0.5 mV $\times$ probe attenuation factor)].                                                      |  |  |

| NOISE REJ Coupled                                                                        | Add ±150 mV to DC Coupled specifications.                                                                                                                  |  |  |

|                                                                                          |                                                                                                                                                            |  |  |

<sup>\*</sup>Performance Requirement not checked in manual.

Table 1-1 (cont)

| Characteristics                             | Perfo                                               | Performance Requirements                                                                                                                                                |            |  |  |

|---------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Variable A Trigger Holdoff                  | A SEC/DIVª MIN HOª                                  |                                                                                                                                                                         | MAX HOª    |  |  |

|                                             | 5 ns<br>10 ns<br>20 ns<br>50 ns<br>100 ns<br>200 ns | 2-4 μs                                                                                                                                                                  | 9-15 μs    |  |  |

|                                             | 500 ns                                              | 5-10 μs                                                                                                                                                                 | 1          |  |  |

|                                             | 1 μs<br>2 μs<br>5 μs                                | 10-20 μs<br>20-40 μs<br>50-100 μs                                                                                                                                       | 100-150 μs |  |  |

|                                             | 10 μs<br>20 μs<br>50 μs                             | 0.1-0.2 ms<br>0.2-0.4 ms<br>0.5-1.0 ms                                                                                                                                  | 1-1.5 ms   |  |  |

|                                             | 100 μs<br>200 μs<br>500 μs                          | 1-2 ms<br>2-4 ms<br>5-10 ms                                                                                                                                             | 10-15 ms   |  |  |

|                                             | 1 ms<br>2 ms<br>5 ms                                | 10-20 ms<br>20-40 ms<br>50-100 ms                                                                                                                                       | 90-150 ms  |  |  |

|                                             | 10 ms<br>20 ms<br>50 ms                             | 0.1-0.2 s<br>0.2-0.4 s<br>0.5-1.0 s                                                                                                                                     | 0.9-1.5 s  |  |  |

|                                             | 100 ms<br>200 ms                                    | 1-2 s<br>2-4 s                                                                                                                                                          |            |  |  |

|                                             | 500 ms<br>1 s<br>2 s<br>5 s                         | 5-10 s                                                                                                                                                                  | 9-15 s     |  |  |

| SLOPE Selection                             | Conforms to trigger-s waveform.                     | Conforms to trigger-source waveform and ac-power-source                                                                                                                 |            |  |  |

| Trigger Position Jitter (p-p)               |                                                     |                                                                                                                                                                         |            |  |  |

| SEC/DIV 0.5 $\mu$ s per Division or Greater |                                                     |                                                                                                                                                                         |            |  |  |

| A and B Triggered Sweeps                    | 0.04 × SEC/DIV setting                              | 0.04 × SEC/DIV setting. <sup>a</sup>                                                                                                                                    |            |  |  |

| B RUNS AFTER Delay                          | 0.08 × SEC/DIV setting. <sup>a</sup>                |                                                                                                                                                                         |            |  |  |

| SEC/DIV 0.2 μs per Division or Less         | Checked at 5 ns/DIV in                              | (0.02 × SEC/DIV setting) + 500 ps <sup>a</sup> Checked at 5 ns/DIV in NORMAL ACQUIRE mode with REPET ON using a 5-division step having less or equal to 1 ns rise time. |            |  |  |

<sup>\*</sup>Performance Requirement not checked in the manual.

Table 1-1 (cont)

| Characteristics                                | Performance Requirements                                                                                                                                         |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | TIME BASE                                                                                                                                                        |

| Sample Rate Accuracy                           |                                                                                                                                                                  |

| Average Over 100 or More Samples               | ± 0.001%.a                                                                                                                                                       |

| External Clock                                 |                                                                                                                                                                  |

| Repetition Rate                                |                                                                                                                                                                  |

| Minimum                                        | 1 MHz.ª                                                                                                                                                          |

| Maximum                                        | 100 MHz. <sup>a</sup>                                                                                                                                            |

| Events Count                                   | 1 to 65,536 <sup>a</sup>                                                                                                                                         |

| Events Maximum Repetition Rate                 | 100 MHz.a                                                                                                                                                        |

| Signal Levels Required for EXT Clock or EVENTS |                                                                                                                                                                  |

| Channel 1 or Channel 2 SOURCE                  |                                                                                                                                                                  |

| DC Coupled                                     | 0.7 division from DC to 20 MHz; increasing to 2.0 divisions at 100 MHz; 3.0 divisions at 100 MHz in ADD mode. <sup>a</sup>                                       |

| NOISE REJ Coupled                              | 2.4 divisions or less from DC to 20 MHz; increasing to 6.0 divisions at 100 MHz; 9.0 divisions at 100 MHz in ADD mode. <sup>a</sup>                              |

| AC Coupled                                     | 0.7 division from 60 Hz to 20 MHz; increasing to 2.0 divisions at 100 MHz; 3.0 divisions at 100 MHz in ADD mode. Attenuates signals below 60 Hz. <sup>a</sup>    |

| HF REJ Coupled                                 | 2.0 divisions from DC to 30 kHz. Attenuates signals above 30 kHz. <sup>a</sup>                                                                                   |

| LF REJ Coupled                                 | 2.0 divisions from 80 kHz to 20 MHz; increasing to 4.0 divisions at 100 MHz; 3.0 divisions at 100 MHz in ADD mode. Attenuates signals below 80 kHz. <sup>a</sup> |

| EXT TRIG 1 or EXT TRIG 2 Source                |                                                                                                                                                                  |

| Ext Gain = 1                                   |                                                                                                                                                                  |

| DC Coupled                                     | 35 mV from DC to 20 MHz; increasing to 100 mV at 100 MHz.a                                                                                                       |

| NOISE REJ Coupled                              | 120 mV or less from DC to 20 MHz; increasing to 300 mV at 100 MHz.a                                                                                              |

| AC Coupled                                     | 35 mV from 60 Hz to 20 MHz; increasing to 100 mV at 100 MHz. Attenuates signals below 60 Hz. <sup>a</sup>                                                        |

| HF REJ Coupled                                 | 50 mV from DC to 30 kHz.ª                                                                                                                                        |

| LF REJ Coupled                                 | 50 mV from 80 kHz to 20 MHz; increasing to 100 mV at 100 MHz.a                                                                                                   |

| Ext Gain = ÷ 5                                 | Amplitudes are five times those specified for Ext Gain = 1.a                                                                                                     |

| Delay Time Range                               | (0.04 $	imes$ B SEC/DIV) to (65,536 $	imes$ 0.04 $	imes$ B SEC/DIV). <sup>a</sup>                                                                                |

| Delay Time Accuracy                            | Same as the sample rate accuracy.a                                                                                                                               |

| Delay Time Resolution                          | The greater of (0.04 $\times$ B SEC/DIV) or 20 ns.                                                                                                               |

| **************************************         | 1                                                                                                                                                                |

<sup>\*</sup>Performance Requirement not checked in the manual.

Table 1-1 (cont)

| Characteristics                                                                          | Performance Requirements                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NONVOLATILE MEMORY                                                                       |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Front-Panel Setting, Waveform Data,<br>Sequencer, and Calibration Data Retention<br>Time | Greater than 3 years.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Battery                                                                                  | 3.6-volt, 1.6-Amp Hour, Lithium Thionyl Chloride; Manufacturer EAGLE PICHER, Type LTC16P/P, TEK Part Number 146-0062-00; UL Listed. (See Warning below.)                                                                                                                                                                                                                          |  |  |  |

|                                                                                          | WARNING                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                                                          | To avoid personal injury, observe proper procedures for handling and disposal of lithium batteries. Improper handling may cause fire, explosion, or severe burns. Don't recharge, crush, disassemble, heat the battery above 212°F (100°C), incinerate, or expose contents of the battery to water. Dispose of battery in accordance with local, state, and national regulations. |  |  |  |

|                                                                                          | Typically, small quantities (less than 20) can be safely disposed of with ordinary garbage in a sanitary landfill.                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                          | Larger quantities must be sent by surface transport to a hazard-<br>ous waste disposal facility. The batteries should be individually<br>packaged to prevent shorting and packed in a sturdy container<br>that is clearly labeled "Lithium Batteries—DO NOT OPEN."                                                                                                                |  |  |  |

<sup>\*</sup>Performance Requirement not checked in the manual.

Table 1-1 (cont)

| Characteristics Performance Requirements                       |                                                                                                                  |                                                                                                          |                                   |                                                                   |  |  |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------|--|--|

|                                                                | SIGNAL OUTPUTS                                                                                                   |                                                                                                          |                                   |                                                                   |  |  |

| CALIBRATOR  Voltage (with A SEC/DIV switch set to 1 ms)        | CALIBRATOR output amplitudes at 5 MHz are at least 50% o output amplitudes at 1 ms SEC/DIV setting. <sup>a</sup> |                                                                                                          |                                   |                                                                   |  |  |

| 1 MΩ Load                                                      | 0.4 V ±1%.a                                                                                                      | 0.4 V ± 1%.ª                                                                                             |                                   |                                                                   |  |  |

| 50 Ω Load                                                      | 0.2 V ±1.5%. <sup>a</sup>                                                                                        |                                                                                                          |                                   |                                                                   |  |  |

| Current (short circuit load with A SEC/DIV switch set to 1 ms) | 8 mA ±1.5%.a                                                                                                     |                                                                                                          |                                   |                                                                   |  |  |

| Repetition Period                                              | A SEC/DIV<br>Setting <sup>a</sup>                                                                                | Calibrator<br>Frequency <sup>a</sup>                                                                     | Calibrator<br>Period <sup>a</sup> | Div/<br>Cycle <sup>a</sup>                                        |  |  |