**User Manual**

# Tektronix

73A-270 Arbitrary Pulse/Pattern Generator Module 070-9148-03

This document supports firmware version 1.00 and above.

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to the Safety Summary prior to performing service.

CE

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of three (3) years from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

We Tektronix Holland N.V. Marktweg 73A 8444 AB Heerenveen The Netherlands declare under sole responsibility that the 73A-270 meets the intent of Directive 89/336/EEC for Electromagnetic Compatibility. Compliance was demonstrated to the following specifications as listed in the Official Journal of the European Communities: EN 55011 **Class A Radiated and Conducted Emissions** EN 50081-1 Emissions: EN 60555-2 **AC** Power Line Harmonic Emissions EN 50082-1 Immunity: IEC 801-2 Electrostatic Discharge Immunity

| ILC 001 L | Electrostatic Discharge minimunity       |

|-----------|------------------------------------------|

| IEC 801-3 | RF Electromagnetic Field Immunity        |

| IEC 801-4 | Electrical Fast Transient/Burst Immunity |

| IEC 801-5 | Power Line Surge Immunity                |

To ensure compliance with EMC requirements this module must be installed in a mainframe which has backplane shields installed which comply with Rule B.7.45 of the VXIbus Specification. Only high quality shielded cables having a reliable, continuous outer shield (braid & foil) which has low impedance connections to shielded connector housings at both ends should be connected to this product.

# **Table of Contents**

#### Description

| Introduction                   |     |

|--------------------------------|-----|

| Controls And Indicators        |     |

| Switches                       |     |

| Fuses                          | 5   |

| LEDs                           | 6   |

| BITE (Built-In Test Equipment) |     |

| Glossary                       | 7   |

| ecifications                   | . 8 |

| stallation                     |     |

# Installation Requirements and Cautions 14 Installation Procedure 15 Installation Checklist 16

#### Operation

| Overview                                  |

|-------------------------------------------|

| Programming Sequence 17                   |

| Programmable Features                     |

| Front Panel BNC Connectors 19             |

| Power-up                                  |

| System Commands                           |

| Module Commands 20                        |

| Summary                                   |

| Command Descriptions 22                   |

| SYSFAIL, Self Test, and Initialization 41 |

| Programming Examples 41                   |

| Definition of BASIC Commands 41           |

| Programming Examples in BASIC 42          |

#### Appendices

| Appendix A – VXIbus Operation                     | 46 |

|---------------------------------------------------|----|

| Appendix B – Front Panel Input/Output Connections | 51 |

| Appendix C – VXIbus Glossary                      | 53 |

| Appendix D – Performance Verification             | 55 |

| Appendix E – User Service                         | 77 |

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

## **Injury Precautions**

| Avoid Electric Overload                      | To avoid electric shock or fire hazard, do not apply a voltage to a terminal that is outside the range specified for that terminal. |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Do Not Operate Without<br>Covers             | To avoid electric shock or fire hazard, do not operate this product with covers or panels removed.                                  |

| Use Proper Fuse                              | To avoid fire hazard, use only the fuse type and rating specified for this product.                                                 |

| Do Not Operate in<br>Wet/Damp Conditions     | To avoid electric shock, do not operate this product in wet or damp conditions.                                                     |

| Do Not Operate in an<br>Explosive Atmosphere | To avoid injury or fire hazard, do not operate this product in an explosive atmosphere.                                             |

# **Product Damage Precautions**

| Provide Proper Ventilation                | To prevent product overheating, provide proper ventilation.                                       |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|

| Do Not Operate With<br>Suspected Failures | If you suspect there is damage to this product, have it inspected by qualified service personnel. |

# Safety Terms and Symbols

| Terms in This Manual   | These terms m                            | ay appear in this manu                | ual:                         |                            |

|------------------------|------------------------------------------|---------------------------------------|------------------------------|----------------------------|

| $\triangle$            | <b>WARNING</b> . Wai<br>in injury or los | -                                     | ify conditions or pra        | ctices that could result   |

| $\wedge$               |                                          | •                                     | • •                          | tices that could result in |

|                        | damage to this                           | product or other prop                 | perty.                       |                            |

| Terms on the Product   | These terms m                            | ay appear on the prod                 | uct:                         |                            |

|                        | DANGER indi marking.                     | cates an injury hazard                | l immediately access         | ible as you read the       |

|                        | WARNING ind marking.                     | dicates an injury hazar               | rd not immediately a         | ccessible as you read the  |

|                        | CAUTION ind                              | licates a hazard to pro-              | perty including the p        | product.                   |

| Symbols on the Product | The following                            | symbols may appear o                  | on the product:              |                            |

|                        | A                                        |                                       | $\triangle$                  |                            |

|                        | DANGER<br>High Voltage                   | Protective Ground<br>(Earth) Terminal | ATTENTION<br>Refer to Manual | Double<br>Insulated        |

# **Certifications and Compliances**

| Overvoltage Category | Overvoltage categories are defined as follows:                                                    |  |

|----------------------|---------------------------------------------------------------------------------------------------|--|

|                      | CAT III: Distribution level mains, fixed installation                                             |  |

|                      | CAT II: Local level mains, appliances, portable equipment                                         |  |

|                      | CAT I: Signal level, special equipment or parts of equipment, telecommunica-<br>tion, electronics |  |

### 73A-270 ARBITRARY PULSE/PATTERN GENERATOR

### DESCRIPTION

# INTRODUCTION

The 73A-270 Arbitrary Pulse/Pattern Generator (APPG) Module is a printed circuit board assembly for use in a card cage conforming to the VXIbus Specification, such as the 73A-021 used in the CDS 73A IAC System. The module provides two completely independent output channels with a common VXIbus backplane interface. Each channel can be individually programmed to generate an arbitrary string of active and inactive TTL or bipolar analog ( $\pm 17.4V$ ) pulse or pattern outputs.

Each channel contains a 1600-word by six-decimal digit high-speed memory. This memory is used to store up to 1600 6-digit output duration time values. Since the APPG allows programming of 1600 duration values (not just 1600 1's and 0's), very complex pulse trains may be programmed. After initial programming, these duration values may be updated "in-progress" (while the APPG is transmitting).

The APPG's ability to output short pulses repeatedly, or short pulses delayed by long intervals, make it ideal for triggering other VXIbus instruments, using either front panel connectors or the VXIbus backplane TTLTRG bus for signal routing. And in applications requiring synchronous operation between multiple VXIbus mainframes, multiple APPG modules may be driven by a single APPG, or all modules can be driven by a single external clock source.

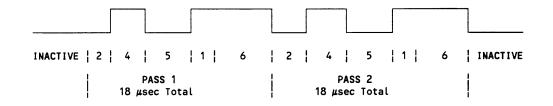

The six-digit data loaded into each memory location represents the duration time of the output (the length of time the output will remain active or inactive) for that point in the data list. A separate two-digit decimal counter is provided for each channel to allow transmission of the data list from 1 to 63 times.

Each location in memory can be identified as an active or inactive output. Any location in the memory can be identified as the last address to provide a variable length data list. Any number of locations in the memory can be identified as breakpoints for pausing and then continuing transmission.

Like other CDS products, the APPG Module combines ease of use and flexibility of function in its programmable features. These features include:

- four output modes per channel - Retriggerable and Non-Retriggerable Modes, each with internal or external triggering.

- breakpoint capability provided in all four modes at any location in the list.

- interrupts can be programmed to generate an interrupt to the VXIbus backplane when transmission is complete or at breakpoints.

- four time resolutions (ranges) -100 nsec, 1 μsec, 10 μsec, or 100 μsec.

- initial polarity of transmission - may be programmed so that a transition from the inactive state will occur either immediately on triggering or

►

after one or more durations of output.

- repeat count can be programmed to repeat from 1 to 63 times or indefinitely.

- capability to drive any of the eight VXIbus TTLTRG backplane lines.

- external triggering external trigger source may be selected under program control to be any of the eight VXIbus TTLTRG lines.

- bipolar analog output programmable over the full ±17.4V output range for both the active and inactive states.

The card is programmed with simple ASCII character strings consisting of numerical data combined with single letter commands. The 73A-270 supports the VXI fast handshake mode and handles all characters on a Direct Memory Access (DMA) basis. VXIbus handshake time is less than 500 nanoseconds per character.

Front panel BNC connectors are provided for TTL Pulse/Pattern Outputs, Analog Bipolar Pulse/Pattern Outputs, and External Trigger Inputs. A 25 pin DB25S connector on the front panel provides duplicates of the above BNC signals plus additional Input/Output signals for an external clock input, a buffered internal clock, and a transmission in progress signal. See Appendix B for a complete description of these signals.

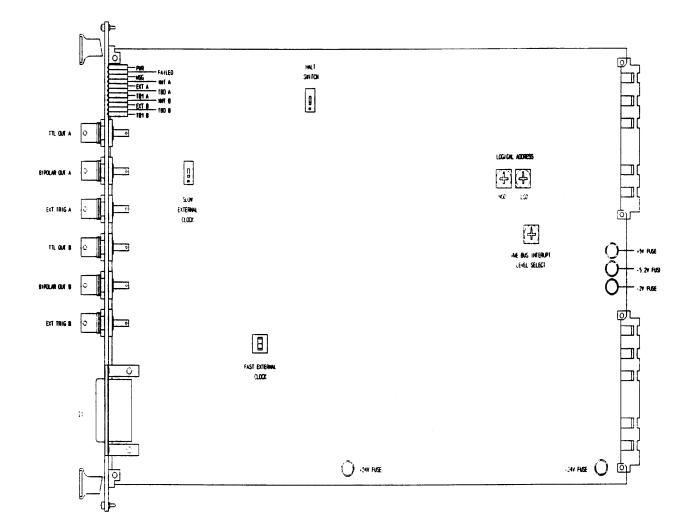

Figure 270-1: 73A-270 Controls and Indicators

# CONTROLS AND INDICATORS

The following controls and indicators are provided to select and display the functions of the 73A-270 Module's operating environment. See Figure 270-1 for their physical locations.

#### • Switches

#### Logical Address Switches

Each function module in a VXIbus System must be assigned a unique logical address, from 1 to 255

decimal. The base VMEbus address of the 73A-270 is set to a value between 1 and FFh (255d) by two <u>hexadecimal</u> rotary switches. Align the desired switch position with the arrow on the module shield.

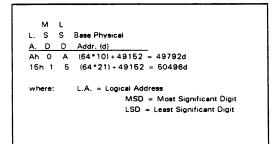

The actual physical address of the 73A-270 Module is on a 64 byte boundary. If the switch representing the most significant digit (MSD) of the logical address is set to position X and the switch representing the least significant digit (LSD) of the logical address is set to position Y, then the base physical address of the 73A-270 will be [(64d \* XYh) + 49152d]. For example:

#### IEEE-488 Address

Using the 73A-270 Module in an IEEE-488 environment requires knowing the module's IEEE-488 address in order to program it. Different manufacturers of IEEE-488 interface devices may have different algorithms for equating a logical address with an IEEE-488 address.

If the 73A-270 is being used in a CDS IEEE-488 IAC system, consult the operating manual of the CDS 73A-151 RM/488 Interface Module.

If the 73A-270 is not being used in a CDS IAC System, consult the operating manual of the IEEE-488 interface device being used for recommendations on setting the logical address.

#### VMEbus Interrupt Level Select Switch

∷NT ⊊EVEL Each function module in a VXIbus System can generate an interrupt on the VMEbus to request service from the interrupt handler located on

its commander (for example, the 73A-151 RM/IEEE-488 Interface Module in a CDS 73A-IBX System). The VMEbus interrupt level on which the 73A-270 Module generates interrupts is set by a BCD rotary switch. Align the desired switch position with the arrow on the module shield.

Valid Interrupt Level Select switch settings are 1 through 7, with setting 1 equivalent to level 1, etc. The level chosen should be the same as the level set on the 73A-270's interrupt handler, typically the module's commander. Setting the switch to an invalid interrupt level (0, 8, or 9) will disable the module's interrupts. When using the 73A-270 in a CDS 73A-IBX System, set the interrupt level to the same level chosen on the 73A-151.

Interrupts are used by the module to return VXIbus Protocol Events to the module's commander. Refer to the <u>Operation</u> section for information on interrupts. The VXIbus Protocol Events supported by the module are listed in the <u>Specifications</u> section.

#### <u>Halt Switch</u>

- This two-position slide switch

- selects the response of the

73A-270 Module when the Reset bit in the module's VXIbus

Control register is set.

If the Halt Switch is in the ON position, the 73A-270 Module is reset to its power-up state and all programmed module parameters are reset to their default values.

If the Halt Switch is in the OFF position, the module will ignore the Reset bit and no action will take place.

*NOTE*: The module is not in strict compliance with the VXIbus Specification when the Halt switch is OFF.

Control of the Reset bit depends on the capabilities of the 73A-270's commander. In a CDS 73A-IBX System, for example, the Reset bit is set if the 73A-151 RM/IEEE-488 Interface Module receives a STOP command via the IEEE-488 bus.

#### External Clock Switches

The 73A-270 has two External Clock switches. Depending on the clock source and/or frequency of the external clock, either the Fast External Clock or the Slow External Clock switch must be activated.

The Fast External Clock switch is a two-position rocker switch. Switch to position C2 if an external clock with a frequency of greater than 250 KHz (up to 10 MHz) is being supplied.

Switch to position C1 if the internal clock is to be used, or if an external clock with a frequency of less than 250 KHz is to be used. NOTE: If a frequency of less than 10 MHz is supplied, VXIbus backplane handshake times for the 73A-270 will be lengthened to greater than 500 nanoseconds.

The Slow External Clock Switch is a twoposition slide switch. The switch should be placed in the ON position if an external clock with a frequency of less than 250 KHz is to be used.

NOTE: For slow external clock operation, the external clock is internally synchronized to the internal 10 MHz clock. Phase jitter of up to  $\pm 50$  nsec will be introduced. Slow external clock operation does not delay the 500 nanosecond VXIbus backplane handshake times.

The Fast External Clock switch instead of the Slow External Clock switch may be used for slow external clocks if throughput is not critical and elimination of phase jitter is required.

#### • Fuses

The 73A-270 Module has +5V, -5.2V, -2V, and  $\pm 24V$  removable fuses. The fuses protect the module in case of an accidental shorting of the power bus or any other situation where excessive current might be drawn.

If any fuse opens, the VXIbus Resource Manager will be unable to assert SYSFAIL INHIBIT on this module to disable SYSFAIL\*.

If any fuse opens, remove the fault <u>before</u> replacing the fuse. Replacement fuse information is given in the <u>Specifications</u> section of this manual.

#### • LEDs

The following LEDs are visible at the top of the 73A-270 Module's front panel to indicate the status of the module's operation:

#### Power LED

This green LED is normally lit and is extinguished if the +5V, -5.2V, -2V, or  $\pm 24V$ buses or the internally regulated  $\pm 20.9V$ buses fail, or if the -2V, +5V, -5.2V, or  $\pm 24V$  fuses open.

#### Failed LED

This normally off red LED is lit whenever SYSFAIL\* is asserted, indicating a module failure. Module failure consists of loss of a power voltage.

NOTE: If the module loses any of its power voltages, the Failed LED will be lit and SYSFAIL\* asserted. A module power failure is indicated when the module's Power LED is extinguished.

#### <u>MSG LED</u>

This green LED is normally off. When lit, it indicates that the module is processing a VMEbus cycle. The LED is controlled by circuitry that appears to stretch the length of the VMEbus cycle. For example, a five microsecond cycle will light the LED for approximately 0.2 seconds. The LED will remain lit if the module is being constantly addressed.

#### Mode/Resolution LEDs

Four LEDs are provided for each of the two channels (Channel A and Channel B). The eight LEDs are arranged in the following order at the top front of the module. When lit, the LEDs indicate the following:

| XMTA<br>transmitting                                    | Channel A is                                     |  |

|---------------------------------------------------------|--------------------------------------------------|--|

| EXTA                                                    | Channel A external<br>trigger is enabled.        |  |

| TBOA                                                    | Channel A resolution - least<br>significant bit. |  |

| TBIA                                                    | Channel A resolution - most significant bit.     |  |

| XMTB<br>transmitting                                    | Channel B is                                     |  |

| ЕХТВ                                                    | Channel B external trigger is enabled.           |  |

| ТВОВ                                                    | Channel B resolution - least<br>significant bit. |  |

| TBIB                                                    | Channel B resolution - most significant bit.     |  |

| The TBO and TBI resolution LEDs are encoded as follows: |                                                  |  |

| <u>TBI LED</u> | <u>TBO LED</u> | <u>Resolution</u> |

|----------------|----------------|-------------------|

| OFF            | OFF            | 100 nanosecond    |

| OFF            | ON             | l microsecond     |

| ON             | OFF            | 10 microsecond    |

| ON             | ON             | 100 microsecond   |

|                |                |                   |

BITE (Built-In Test Equipment)

Four LEDs for each channel provide visual indication of the transmit status, resolution status, and external trigger mode. A readback mode provides the transmit status and data list command accept status of either channel. Finally, the serial pattern output connections to the VXIbus TTLTRG lines allow checking the programming and output intervals by any counter resource in the same VXIbus card cage.

A glossary of VXIbus terms is provided in Appendix C. In addition, the following terms specific to the 73A-270 Module are defined:

#### Bipolar Outputs

An output for each channel that provides the same pulse/pattern output as the basic pulse/pattern TTL output but at a programmable high and low level up to  $\pm 17.4V$  for both the active and inactive states.

#### Breakpoint

A programmed breakpoint temporarily holds the output at the last programmed level until a trigger instructs the module to continue.

#### Non-Retriggerable Mode

A programmed mode on the 73A-270 that ignores additional triggers while a channel is actually transmitting until transmission is completed or a breakpoint is executed.

#### Repeat Count

A programmable count on the 73A-270 Module that allows the pulse/ pattern output (up to 1600 locations) to be repeated a specified number of times up to 63 times, or continuously.

#### Retriggerable Mode

A programmed mode on the 73A-270 that allows the pulse/pattern output to restart at the beginning of its transmission list if a trigger is received while the module is actively transmitting.

#### Pulse/Pattern Outputs

A series of active and inactive levels of varying programmable time durations provided on a single wire output. Two independent outputs are provided on the 73A-270 Module.

#### Time Duration Value

One of 1600 values programmable on each channel with a value of 1 to 999,999. This value is multiplied by the resolution programmed for the channel to determine the time a particular output level (active or inactive) programmed in any one of the 1600 locations is present on the pulse/ pattern output.

### SPECIFICATIONS

| Number of Channels:                                 | Two.                                                                                                                                                                                                                               |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type Outputs:                                       | TTL active high and active low; VXIbus TTLTRG; bipolar analog (each channel).                                                                                                                                                      |

| Bipolar Outputs:                                    | Programmable level - $\pm 17.4$ volts ( $\pm 8.7$ into 50 ohms).<br>Transition time - <70 nsec, 10% to 90% points, typical                                                                                                         |

| TTL Outputs:                                        | Drive capability, 3.2 mA source, 24 mA sink current.                                                                                                                                                                               |

| Number of Sequentiai<br>Output Durations:           | 1 to 1600 per channel.                                                                                                                                                                                                             |

| Number of Repeat Times:                             | 1 to 63, or continuous.                                                                                                                                                                                                            |

| Time Period of Each Output<br>Duration:             | Programmable, 1 to 999,999 times the resolution range selected for each channel:                                                                                                                                                   |

|                                                     | Resolution<br>RangeTime Period Duration100 ns100 nanoseconds to 99.9999 milliseconds.1 μs1 microsecond to 0.999999 seconds.10 μs10 microseconds to 9.99999 seconds.                                                                |

| Programmable Resolution<br>of Each Output Duration: | <ul> <li>100 μs</li> <li>100 microseconds to 99.9999 seconds.</li> <li>Internal 10 MHz Clock:</li> <li>Four programmable resolution ranges:</li> <li>100-nanosecond, 1 μsec, 10 μsec, and 100 μsec</li> <li>resolution.</li> </ul> |

| Significant Digits<br>(Time Period Programming):    | External Clock:<br>1/f, 10/f, 100/f, 1000/f<br>f = external clock input frequency.<br>6 decimal digits (20 bit resolution).                                                                                                        |

| Trigger Modes:<br>Non-retriggerable Mode:           | Single trigger for total number of output cycles without interruption.                                                                                                                                                             |

| Retriggerable Mode:                                 | Each trigger restarts output from first output duration.                                                                                                                                                                           |

| Trigger Capability:<br>Programmable:                                                     | Trigger under program control or trigger with external                                                                              |  |  |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                          | trigger input from multiple sources.                                                                                                |  |  |

| Sources (programmable):                                                                  | Internal:<br>Software initiated.<br>External:<br>Front panel connector.<br>Any of 8 VXIbus TTLTRG lines.<br>VXIbus TRIGGER command. |  |  |

| External Trigger Input:                                                                  | Input (Front Panel or VXIbus TTLTRG):<br>Trigger occurs on TTL transition from high to low.                                         |  |  |

|                                                                                          | Front Panel Loading:<br>1 TTL load equivalent with 10K pullup.                                                                      |  |  |

| VXIbus TTLTRG<br>Selection:                                                              | Programmable, TTLTRG 0 through 7, synchronous trigger protocol.                                                                     |  |  |

| Trigger Delay:                                                                           | From receipt of trigger to start of output: 315 ns - 0 ns + 100 ns for all resolution ranges.                                       |  |  |

| Breakpoint Capability:                                                                   | l to 1600 programmable breakpoints for each channel.<br>Available in either Retriggerable or Non-Retriggerable<br>modes.            |  |  |

| Programmed By:                                                                           | ASCII characters.                                                                                                                   |  |  |

| On-Card Memory:                                                                          | 3200 24 bit words (1600 words/channel).                                                                                             |  |  |

| Clock Source:                                                                            | Internal: VXIbus slot 0 10 MHz ECL clock.<br>External: front panel connector.                                                       |  |  |

| External Clock Input:<br>Type Input:                                                     | TTL.                                                                                                                                |  |  |

| Range:                                                                                   | 1 kHz to 10 MHz.                                                                                                                    |  |  |

| Loading:                                                                                 | 1.25 TTL load equivalents.                                                                                                          |  |  |

| External Clock Outputs:<br>Type:                                                         | TTL, 15 mA source, 64 mA sink current.                                                                                              |  |  |

| Frequency:                                                                               | 10 MHz.                                                                                                                             |  |  |

| TTL Outputs:<br>Channel A and B Pulse/<br>Pattern Outputs:                               | TTL active high and TTL active low.                                                                                                 |  |  |

| Channel A and B Transmission<br>In Progress Outputs: TTL active high and TTL active low. |                                                                                                                                     |  |  |

| Drive Capability:                         | TTL, 5 mA source, 32 mA sink current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pulse/Pattern Output Sense:               | BNC output, TTL high when active;<br>VXIBus TTLTRG output, TTL low when active;<br>DB25S TTL active high output, TTL high when active;<br>DB25S TTL active low output, TTL low when active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Transmission In Progress<br>Output Sense: | TTL active high output, TTL high for transmission in<br>progress;<br>TTL active low output, TTL low for transmission in<br>progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bipolar Analog Outputs:                   | <ul> <li>Levels (50 ohm load):</li> <li>Inactive level - ±8.7V dc.</li> <li>Active level - ±8.7V dc.</li> <li>Levels (high impedance load):</li> <li>Inactive level - ±17.4V dc.</li> <li>Active level - ±17.4V dc.</li> <li>Minimum load: 50 ohms.</li> <li>Resolution: 100 mV with 50 ohm load; 200 mV with high impedance.</li> <li>DC accuracy: 3% of full scale range.</li> <li>10-90% rise/fall time: less than 60 nanoseconds.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |

| Power-Up Conditions:                      | <ul> <li>When power is applied, the module will go to the following known states:</li> <li>Channel A: Selected.</li> <li>Resolution: 100 nanosecond, both channels.</li> <li>Mode: Retriggerable, both channels.</li> <li>External Trigger: Disabled, both channels.</li> <li>External Trigger Source: Front panel, both channels.</li> <li>VXIbus TTLTRG Pulse/Pattern output: not programmed.</li> <li>Interrupt Capability: Disabled, both channels.</li> <li>Pulse/Pattern Memory Contents: Undefined.</li> <li>Channel A &amp; B Repeat Count: Undefined.</li> <li>LEDs: Extinguished, except for Power LED.</li> <li>Pulse/Pattern Outputs: Inactive.</li> <li>Transmission In Progress Outputs: Transmission not in progress.</li> <li>Bipolar Outputs: OV dc for both Active and Inactive levels.</li> </ul> |

| VXIbus Data Rate:                         | Data/Commands, 1.8 Mbytes per second, fast handshake<br>mode. Throughput will be affected by system controller<br>and system controller/VXIbus interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Handshake Types:                          | Normal Mode Word Serial transfer or Fast Handshake                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Logical Address:                          | Word Serial mode.<br>Switch selectable, 1 through 254.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VXIbus Compatibility:                     | Fully compatible with the VXIbus Specification for<br>message-based instruments with the Halt Switch in the<br>ON position.                                                                                                 |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VXI Device Type:                          | VXI message based instrument, VXIbus Revision 1.2.                                                                                                                                                                          |

| VXI Protocol:                             | Word serial.                                                                                                                                                                                                                |

| VXI Card Size:                            | C size, one slot wide.                                                                                                                                                                                                      |

| Module-Specific<br>Commands:              | All module-specific commands and data are sent via the<br>VXIbus Byte Available command. All module-specific<br>commands are made up of ASCII characters. Module-<br>specific data may be in either ASCII or binary format. |

| VMEbus Interface:                         | Data transfer bus (DTB) slave - A16, D16 only.                                                                                                                                                                              |

| Interrupt Level:                          | Switch selectable, levels 1 (highest priority) through 7 (lowest).                                                                                                                                                          |

| Interrupt Acknowledge:                    | D16, lower 8 bits returned arc the logical address of the module. Upper 8 bits contain the VXIbus protocol event code.                                                                                                      |

| VXIbus Fast Handshake:<br>VXIbus Commands | Active for internal clock and for recommended external clock switch settings for external clock.                                                                                                                            |

| Supported:                                | All VXIbus commands are accepted (e.g. DTACK*<br>will be returned). The following commands have<br>effect on this module; all other commands will cause<br>an Unrecognized Command Event:                                   |

|                                           | BYTE AVAILABLE (with or without END bit set)<br>BYTE REQUEST<br>BEGIN NORMAL OPERATION<br>CLEAR<br>IDENTIFY COMMANDER<br>READ PROTOCOL                                                                                      |

| VXIbus Protocol                           | TRIGGER                                                                                                                                                                                                                     |

| Events Supported:                         | VXIbus events are returned via VME interrupts. The following events are supported and returned to the 73A-270 Module's commander:                                                                                           |

| VXIbus Registers:                         | UNRECOGNIZED VXIbus COMMAND<br>REQUEST TRUE (In IEEE-488 systems such as the 73A-<br>IBX, this interrupt will cause a Service Request<br>(SRQ) to be generated on the IEEE-488 bus.)<br>ID<br>Device Type                   |

|                                           |                                                                                                                                                                                                                             |

|                                                | Status<br>Control<br>Protocol<br>Response<br>Data Low<br>See Appendix A for definition of register contents.                                                                                                                                                                                     |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Requirements:                            | All required dc power is provided by the Power Supply in the VXIbus card cage.                                                                                                                                                                                                                   |

| Voltage:                                       | +5 Volt Supply: 4.75V dc to 5.25V dc.<br>+24 Volt Supply: +23.2V dc to +25.2V dc.<br>-24 Volt Supply: -23.2V dc to -25.2V dc.<br>-5.2 Volt Supply: -4.95V dc to -5.45V dc<br>-2.0 Volt Supply: -1.9V dc to -2.1V dc                                                                              |

| Current (Peak<br>Module, I <sub>PM</sub> ):    | +5 volt supply: 3.3 A<br>+24 volt supply: 120 mA *<br>-24 volt supply: 100 mA *<br>-5.2 volt supply: 35 mA<br>-2.0 volt supply: 26 mA                                                                                                                                                            |

| Current (Dynamic<br>Module, I <sub>DM</sub> ): | +5 volt supply: 150 mA ptp @ 23 MHz<br>+24 volt supply: 185 mA ptp @ 23 MHz *<br>-24 volt supply: 245 mA ptp @ 17 MHz *<br>-5.2 volt supply: 435 mA ptp @ 23 MHz<br>-2.0 volt supply: 435 mA ptp @ 22 MHz<br>* +24V dc tested with ±7V dc 1 MHz bipolar output into<br>50 Ohms on both channels. |

| Cooling:                                       | Provided by the fan in the VXIbus card cage. Less than $10^{\circ}$ C temperature rise with 1.76 liters/sec of air at a pressure drop of 0.099 mm of H <sub>2</sub> O.                                                                                                                           |

| Fuses:                                         | Replacement fuses: +5V: Littlefuse P/N 273004,<br>-5.2V, -2V: Littlefuse P/N 273002,<br>±24V: Littlefuse P/N 273001,                                                                                                                                                                             |

| Temperature:                                   | -10°C to +65°C, operating (assumes ambient temperature<br>of 55° and airflow to assure less than 10°C temperature<br>rise).<br>-40°C to +85°C, storage.                                                                                                                                          |

| Humidity:                                      | Less than 95% R.H., noncondensing.                                                                                                                                                                                                                                                               |

| VXIbus Radiated Emissions:                     | Complies with VXIbus Specification.                                                                                                                                                                                                                                                              |

| VXIbus Conducted Emissions:                    | Complies with VXIbus Specification.                                                                                                                                                                                                                                                              |

| Dimensions, Shipping:                                   | When ordered with a CDS card cage, this module will be installed and secured in one of the instrument module slots (slots 1 - 12).                                                                                                                            |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | When ordered alone, the module's shipping dimensions are:                                                                                                                                                                                                     |

|                                                         | 406 mm x 305 mm x 102 mm.<br>(16 in x 12 in x 4 in).                                                                                                                                                                                                          |

| Weight:                                                 | 1.4 kg. (3.1 lbs).                                                                                                                                                                                                                                            |

| Weight, Shipping:                                       | When ordered with a CDS card cage, this module will be installed and secured in one of the instrument module slots (slots 1-12).                                                                                                                              |

|                                                         | When ordered alone, the shipping weight is:                                                                                                                                                                                                                   |

|                                                         | 1.9 kg. (4.3 lbs).                                                                                                                                                                                                                                            |

| Mounting Position:                                      | Any orientation.                                                                                                                                                                                                                                              |

| Mounting Location:<br>Front Panel Signal<br>Connectors: | Installs in an instrument module slot (slots 1-12) of a C or<br>D size VXIbus card cage. (Refer to D size card cage<br>manual for information on required adapters.)                                                                                          |

|                                                         | Six BNC jacks:<br>Pulse/pattern outputs, TTL;<br>Pulse/pattern outputs, bipolar;<br>External trigger inputs.                                                                                                                                                  |

|                                                         | One DB-25S connector:<br>Pulse/pattern outputs, TTL active high and active<br>low;<br>Pulse/pattern outputs, bipolar;<br>External trigger inputs;<br>Transmission in progress outputs, TTL active high<br>and active low;<br>External clock input and output. |

| Recommended Cable:                                      | (for DB-25S connector) 73A-734 Data Cable or 73A-782P<br>Hooded Connector.                                                                                                                                                                                    |

| Equipment Supplied:                                     | l - 73A-270 Arbitrary Pulse/Pattern Generator Module.                                                                                                                                                                                                         |

### INSTALLATION

#### INSTALLATION REQUIREMENTS AND CAUTIONS

The 73A-270 Module is a C size VXIbus instrument module and therefore may be installed in any C or D size VXIbus card cage slot other than slot 0. If the module is being installed in a D size card cage, consult the operating manual for the card cage to determine how to install the module in that particular card cage. Setting the module's logical address switch defines the module's programming address. Refer to the <u>Controls and Indicators</u> subsection for information on selecting and setting the 73A-270 Module's logical address.

#### CAUTION:

To avoid confusion, it is recommended that the slot number and the logical address be the same.

#### **Tools Required**

The following tools are required for proper installation:

Slotted screwdriver set.

#### CAUTION:

Note that there are two ejector handles on the module. To avoid installing the module incorrectly, make sure the ejector labeled "73A-270" is at the <u>top</u>.

#### CAUTION:

In order to maintain proper card cage cooling, unused card cage slots must be covered with blank front panels supplied by the card cage manufacturer. Based on the number of IAC Modules ordered with a CDS card cage, blank front panels are supplied to cover all unused slots.

#### CAUTION:

Verify that the card cage is able to provide adequate cooling and power for the 73A-270 Module. Refer to the card cage Operating Manual for instructions on determining cooling and power compatibility.

#### CAUTION:

If the 73A-270 Module is inserted in a slot with any empty slots to the left of the module, the VME daisychain jumpers must be installed on the backplane in order for the 73A-270 Module to operate properly. Check the manual of the card cage being used for jumpering instructions.

If a CDS 73A-021 Card Cage is being used, the jumper points may be reached through the front of the card cage. There are five (5) jumpers that must be installed for each empty slot. The five jumpers are the pins to the <u>left</u> of the empty slot.

#### INSTALLATION PROCEDURE

#### CAUTION:

The 73A-270 Module is a piece of electronic equipment and therefore has some susceptibility to electrostatic damage (ESD). ESD precautions must be taken whenever the module is handled.

- Record the module's Revision Level, Serial Number (located on the CDS label on the top shield of the 73A-270), and switch settings on the Installation Checklist on the next page. Only qualified personnel should install the 73A-270 Module.

- 2) Verify that the Logical Address and Interrupt Level switches are switched to the correct value. The Halt switch should be in the ON position unless it is desired to not allow the resource manager to reset this module.

Note that with either Halt Switch position, a "hard" reset will occur at power-on and when SYSRST\* is set true on the VXIbus backplane. If the module's commander is a CDS 73A-151 RM/IEEE-488 Interface Module, SYSRST\* will be set true whenever the Reset Switch on the front panel of the 73A-151 is depressed. Also note that when the Halt Switch is in the OFF position, the module is not in strict compliance with the VXIbus Specification.

The module can now be inserted into any slot of the chassis other than slot 0. NOTE: This module does not connect to the VXIbus local bus, so no front panel keying is required.

#### 4) Cable Installation -

If the DB25S connections are to be used, use either a 73A-734 Data Cable or 73A-782P Hooded Connector to interface between the DB25S output connector and the UUT. If the module is being installed in a CDS 73A Series card cage, route the cable from the front panel of the module down through the cable tray at the bottom of the card cage and out the rear of the card cage.

No calibration is required for this module.

#### INSTALLATION CHECKLIST

Installation parameters may vary depending on the card cage being used. Be sure to consult the card cage Operating Manual before installing and operating the 73A-270 Module.

| Revision Level:                |  |

|--------------------------------|--|

| Serial No.:                    |  |

| Card Cage Slot Number:         |  |

| Switch Settings:               |  |

| VXIbus Logical Address Switch: |  |

| Interrupt Level Switch:        |  |

| Halt Switch:                   |  |

| Fast External Clock:           |  |

| Slow External Clock:           |  |

| Cable Installed:               |  |

Performed by: \_\_\_\_\_ Date: \_\_\_\_\_

### OPERATION

The 73A-270 Module is programmed by ASCII characters issued from the system controller to the 73A-270 Module via the module's VXIbus commander and the VXIbus card cage backplane. The module is a VXIbus Message Based Instrument and communicates using VXIbus Word Serial Protocol. Refer to the manual for the VXIbus device that will be the 73A-270 Module's commander for details on the operation of that device.

If the Module is being used in a CDS 73A-IBX System card cage, the module's commander will be the 73A-151 Resource Manager/IEEE-488 Interface Module. Refer to the 73A-151 Operating Manual and the programming examples at the end of this section for information on how the system controller communicates with the 73A-151.

The module consists of two completely separate arbitrary pulse pattern generators with a common VXIbus backplane interface. Each channel contains a 1600-word by six- decimal digit high-speed memory. This memory is used to store up to 1600 six-digit output duration time values.

The six-digit data loaded into each memory location represents the length of time the output will remain active or inactive for that point in the data list. A separate two-digit decimal counter is provided for each channel to allow transmission of the data list from 1 to 63 times. Separate circuitry is provided for each channel to allow channel-specific selection of resolution, start of transmission, retriggering modes, or interrupt enabling. Very complex wave trains may be programmed. For example, up to 800 100nsec pulses may be programmed with the intervals between each pulse varying from 100 nsec to 100 msec. Or, by programming 1500 consecutive 100-millisecond active levels followed by a 100-nsec inactive level, a 100-nsec pulse may be accurately delayed 150 seconds. In the higher resolution range a 100 µsec pulse may be delayed up to 150,000 seconds (41 hours).

Each location in memory can be identified as an active or inactive output. Any location in the memory can be identified as the last address in order to provide a variable length data list. Any number of locations in the memory can be identified as breakpoints for independent triggering of segments of memory.

Four eight-channel multiplexers allow connection of the channel A and B pulse/ pattern output and external trigger input to any of the eight VXIbus TTLTRG lines.

There are two bipolar analog output amplifiers for each channel, providing a programmable active and inactive level for each channel.

#### • Programming Sequence

The typical programming sequence is:

- One of two channels is selected with an S (Select) command. All channelspecific commands apply to that channel until another channel is selected.

- An R (Resolution) command is used to specify one of four clock resolutions for the selected channel.

- A decimal address in the 1600-word memory is selected with an A (Address) command.

- Memory data values consisting of a time duration value and polarity, a last location identifier, and breakpoint location identifiers are loaded into that address with an L (List) command.

The selected address automatically increments after each L (List) command, or it may be reprogrammed at any time with the A command.

- The selected channel is programmed for the number of times the entire data list in memory is to be transmitted with the C (Count) command.

- The selected channel may also be programmed with the M (Mode) command to select or deselect the retriggerable or non-retriggerable modes with or without external trigger enabled, or to enable or disable the VXIbus interrupt capability with the I (Interrupt) command.

- Transmission is then initiated with the B (Begin) command.

#### • Programmable Features

#### <u>Modes</u>

Four output modes are provided for each channel. The first two, the Non-Retriggerable Modes with internal or external triggering, each transmit the string of active and inactive level outputs the specified number of times, ignoring additional triggers during transmission. The second two, the Retriggerable Modes with internal or external triggering, reset the module to the beginning of the transmit string if an additional trigger is received during transmission.

#### Breakpoint Capability

A breakpoint capability is provided in all four modes at any location in the list. Transmission stops following any level programmed with a breakpoint, and resumes when an additional trigger is received. The external trigger modes may be triggered by a TTL signal on each channel, either through the VXIbus TTLTRG lines, through a front panel BNC or DB25S connector, or by the VXIbus TRIGGER command.

#### Interrupts

The APPG Module can be programmed to generate an interrupt to the VXIbus backplane when transmission is complete or at breakpoints, to indicate the need for a trigger to continue transmission.

#### Time Duration Ranges

The 6-digit output time duration values for each channel may be programmed using:

- 100-nanosecond increments up to 100 milliseconds,

- 1 µsec increments up to 1 second,

- 10 μsec increments up to 10 seconds, or

- 100 μsec increments up to 100 seconds.

Other resolutions may be obtained by using an external clock, available through the front panel DB25S connector. The module uses the VXIbus slot 0 10 MHz ECL clock for its internal time base. In applications requiring synchronous operation between multiple VXIbus mainframes, multiple APPG modules may be driven by a single APPG, or all modules can be driven by a single external clock source.

#### Initial Polarity

The initial polarity of transmission (active or inactive level) may be programmed so that a transition from the inactive state will occur either immediately on triggering or after one or more durations of output. Both polarities of the output are available at the module's DB25S front connector so that either polarity may be defined as the inactive state. BNC connectors are provided on the front panel for TTL output and the bipolar analog output levels for each of the two channels.

#### <u>Repeat Count</u>

The complete output pulse train for each channel can be programmed to repeat from 1 to 63 times or indefinitely. The individual output durations (active or inactive, including the level duration presently transmitting) may be updated 'inprogress' (while the module is transmitting).

#### TTLTRG Capability

Each channel's output may be programmed to drive any of the eight VXIbus TTLTRG backplane lines. The 73A-270's ability to output short pulses repeated or delayed by extremely long intervals makes it useful for triggering other VXIbus instruments.

#### External Triggering

The external triggers for each channel may also be driven under program control by any of the eight VXIbus TTLTRG lines. By selecting the same TTLTRG line, one channel's pulse/pattern output may be used to externally trigger the other channel or other APPG modules.

#### <u>Bipolar Analog Outputs</u>

The bipolar analog output for both the active and inactive states is programmable over the full  $\pm$  voltage output range. The outputs for each channel are 50 ohm sources capable of driving a 50 ohm load to  $\pm 8.7$ V dc with a 100 mV resolution or a high impedance load to  $\pm 17.4$ V dc with a 200 mV resolution.

#### • Front Panel BNC Connectors

#### TTL Pulse/Pattern Outputs

The TTL OUT A and TTL OUT B BNC connections provide the programmed active and inactive output pulse trains for each channel. The TTL-compatible outputs for each channel are at a TTL high when an active level is programmed.

#### Analog Bipolar Pulse/Pattern Outputs

The BPLR OUT A and BPLR OUT B BNC connections provide analog output signals. The signal level when the module is not transmitting, or transmitting at an inactive level, will be the voltage level programmed by the N command. The signal level when the module is transmitting and at an active level will be the voltage level programmed by the P command.

#### External Trigger Inputs

The EXT TRG A and EXT TRG B BNC connections are used to input front panel external triggers. When Channel A or B is programmed for an external trigger and the front panel external trigger has been selected by the X command, transmission will start three to four clock cycles (400 ns maximum using the internal clock) following a high-to-low transition of the channel's external trigger input. Internal 10K pull-up resistors pull each input high when not connected.

#### DB25S Signals

Additional signals provided at the 25 pin DB25S front panel connector are:

- external clock input allows several modules to be programmed for parallel operation.

- buffered internal clock allows any module to be the common clock source for a parallel module output configuration.

- transmission in progress indicates whether transmission is in progress for each channel.

See Appendix B for a complete description of these signals.

|  | UP |  |

|--|----|--|

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

The 73A-270 Module will be ready for programming as soon as the VXIbus Resource Manager has initialized the VXIbus system. The 73A-270 Power LED will be on, and all other LEDs off. The MSG LED will blink during the power-up sequence as the VXIbus Resource Manager addresses all modules in the card cage. The default condition of the module after power-up is described in the <u>SYSFAIL</u>, <u>Self</u> <u>Test and Initialization</u> subsection.

Although these non-data commands are initiated by the 73A-270's commander (for example, the 73A-151 Module in a CDS 73A-IBX System) rather than the system controller, they have an effect on the 73A-270 Module. The following VXIbus instrument protocol commands will affect the 73A-270:

#### Command Effect

CLEAR The module clears its VXIbus interface. The 73A-270 Module has no input or output command buffers, so input and output data transfers are unaffected. Current module functional operation is also unaffected.

#### TRIGGER

The module triggers operation if the external trigger mode is programmed and the VXIbus TRIGGER command has been programmed as the source for the external trigger.

#### BEGIN NORMAL OPERATION

7**3A-**270

The module will begin operations.

#### READ PROTOCOL

The module will return its protocol to its commander.

# MODULE COMMANDS

A summary of the 73A-270's Module's commands is listed below. This is followed by detailed descriptions of each of the commands. A sample BASIC program using these commands is shown at the end of this section.

Command protocol and syntax for the 73A-270 Module are as follows:

- 1) The format for each command is specified in the detailed command description section of this manual.

- 2) Commands may be strung together indefinitely.

- 3) Carriage-return <CR>, line feed <LF>, or other separation characters (such as slashes, periods, commas, colons or semi-colons) are permitted but not required between commands. Leaving out <CR><LF> will usually significantly reduce a system controller's execution time. However, adding a <CR><LF> following commands improves readability.

#### • Summary

An overview of the commands, in the order they typically would be programmed, is as follows:

- S Select selects the channel (A or B) for which all following commands (except the T and X commands) will apply.

- R Resolution specifies one of four time resolution ranges for the selected channel.

- A Address specifies any of the 1,600 addresses in the selected channel for loading data into memory.

- L List specifies the time duration and polarity (active or inactive) of the output at the selected address for the selected channel. It can also specify the selected address as a breakpoint or last address. The programmed address will increment automatically at the end of each LIST command.

- C Count specifies the number of times the entire data list will be transmitted before stopping for the selected channel.

- M Mode specifies either the Triggerable or the Non-retriggerable Mode for the selected channel. It also enables or disables the external triggering for both modes.

- T TTLTRG specifies VXIbus TTLTRG0 through TTLTRG7 for connection to Channel A and B's pulse/pattern output, or specifies no connection.

- X External Trigger specifies the source for an external trigger for Channel A and B as: a) VXIbus TTLTRG0 through TTLTRG7, b) the VXIbus TRIGGER command, or

c) the front panel BNC connector (or the equivalent DB25S connector pin).

- N Inactive Analog specifies the analog bipolar output voltage level for the selected channel corresponding to an inactive pulse/pattern signal output.

- P Active Analog specifies the analog bipolar output voltage level for the selected channel corresponding to an active pulse/pattern signal output.

#### Input Request

An Input Request to the 73A-270 returns status information for the selected channel. An input request is not a command output. It is generated by reading from the module.

- I Interrupt enables or disables interrupt capability for the selected channel.

- B Begin triggers data transmission for one or both channels. Transmission will begin immediately if external triggering is not active. If external triggering is active for a channel, the B command arms the external trigger input. Subsequently received external trigger inputs will then initiate transmission.

- Q Quit stops transmission in progress for one or both channels.

A detailed description of each command, in alphabetical order, is given on the following pages.

• Command Descriptions

Command: A (Address)

Syntax: zA

Purpose: The A command specifies a memory address in the selected channel's memory.

Description: z is a 1- to 4-digit decimal integer from 0 to 1599 that specifies the current memory address for the selected channel. If z is omitted, the address will be set to address 0.

The A command strobes the address specified by z into the memory address register of the selected channel.

An A command can be sent while a transmission is in progress. The command will not affect the transmission nor will the transmission affect the contents of the address register. Two independent address registers, one for programming, the other for transmission, permit re-programming without affecting transmission.

Since the A command doesn't require reloading of the complete data list, any time duration value in memory can be changed by programming the appropriate address with the A command and updating the time duration value with the L command.

Example: If Channel B has been selected as the active channel (using the S command), then the command string "44A" programs Channel B memory address register to decimal value 44.

| Command:     | B (Begin)                                                                                                                                                                                                                                                                      |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:      | zB                                                                                                                                                                                                                                                                             |  |  |

| Purpose:     | The B command either initiates or arms transmission for the selected channel or for both channels.                                                                                                                                                                             |  |  |

| Description: | z is a 1-digit decimal integer (0 or 1) that specifies the following:                                                                                                                                                                                                          |  |  |

|              | <u>z</u> <u>Action</u>                                                                                                                                                                                                                                                         |  |  |

|              | <ol> <li>Begin or arm transmission for the channel last selected with an S command.</li> <li>Begin or arm transmission for both channels simultaneously.</li> </ol>                                                                                                            |  |  |

|              | The type of triggering (selected by the M command) determines whether the B command starts or arms transmission. With internal triggering, the command starts transmission. With external triggering, the B command is ARM command for the external trigger.                   |  |  |

| Example:     | The command string "0S0M0B1S1M0B" initiates transmission in Channel A, then arms transmission in Channel B.                                                                                                                                                                    |  |  |

|              | <ul> <li>0S select Channel A</li> <li>0M enable internal trigger and retriggerable mode</li> <li>0B begin transmission</li> <li>1S select Channel B</li> <li>1M enable external trigger and retriggerable mode</li> <li>0B arm transmission for an external trigger</li> </ul> |  |  |

| Command:     | C (Count)                                                                                                                                                                                                                                                                                                                                      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:      | zC                                                                                                                                                                                                                                                                                                                                             |

| Purpose:     | The C command specifies the number of times to transmit the entire data list<br>in memory associated with the selected channel.                                                                                                                                                                                                                |

| Description: | z is a 1- or 2-digit decimal integer from 0 to 63 that specifies the number of times to transmit the data list. The value 0 specifies that the data list is to be transmitted continuously. The repeat count value can not be changed during operation.                                                                                        |