## **Instructions**

# **Tektronix**

TLA7PG2 Pattern Generator Module 071-1306-00

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service.

www.tektronix.com

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software - Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., 14200 SW Karl Braun Drive, Beaverton, OR 97077

TEKTRONIX, TEK, TLAVu, PatGenVu, and MagniVu are registered trademarks of Tektronix, Inc.

#### HARDWARE WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| General Safety Summary                                                                                                                                | iii                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Preface                                                                                                                                               | v<br>v<br>vi            |

| Pattern Generator Module Introduction                                                                                                                 | <b>1</b><br>1           |

| Setting Up the Pattern Generator Module  Module Setup Window Channel Setup Window Probe Setup Window Signal Setup Window                              | 3<br>3<br>4<br>5<br>5   |

| Setting Up the Pattern Generator Program  Block Definition Window  Sequence Definition Window  Subsequence Definition Window  Event Definition Window | 7<br>7<br>8<br>11<br>11 |

| Appendix A: TLA7PG2 Pattern Generator Module Characteristics  Appendix B: Pattern Generator Physical-Logical Conversion                               | 13<br>17                |

# **List of Figures**

**List of Tables**

| Figure 1: Block diagram of the pattern generator module                                   | 1              |

|-------------------------------------------------------------------------------------------|----------------|

| Figure 2: Module Setup window                                                             | 4              |

| Figure 3: Channel Setup window                                                            | 4              |

| Figure 4: Probe Setup window                                                              | 5              |

| Figure 5: Signals Setup window                                                            | 6              |

| Figure 6: Block Definition window                                                         | 7              |

| Figure 7: Listing window                                                                  | 8              |

| Figure 8: Sequence Definition window                                                      | 9              |

| Figure 9: Drag the vertical bar to the left to display the sequence flow graphic          | 10             |

| Figure 10: Sequence flow graphic                                                          | 10             |

| Figure 11: Subsequence Definition window                                                  | 11             |

| Figure 12: Event Definition window                                                        | 12             |

| Table i: Tektronix TLAPG2 Pattern Generator Module                                        |                |

| documentation                                                                             | v              |

| Table 1: PG module electrical specification, operational mode                             | 13             |

|                                                                                           | 4.4            |

| Table 2: PG module clocking                                                               | 14             |

| Table 2: PG module clocking                                                               | 14<br>14       |

|                                                                                           |                |

| Table 3: PG module event processing                                                       | 14             |

| Table 3: PG module event processing          Table 4: PG module inter-module interactions | 14<br>15       |

| Table 3: PG module event processing                                                       | 14<br>15<br>15 |

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.

To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

**Connect and Disconnect Properly.** Do not connect or disconnect probes or test leads while they are connected to a voltage source.

**Ground the Product.** This product is indirectly grounded through the grounding conductor of the mainframe power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Observe All Terminal Ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal, that exceeds the maximum rating of that terminal.

**Do Not Operate Without Covers.** Do not operate this product with covers or panels removed.

**Use Proper Fuse.** Use only the fuse type and rating specified for this product.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

**Keep Product Surfaces Clean and Dry.**

**Provide Proper Ventilation.** Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

**Symbols and Terms Terms in this Manual.** These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

**Terms on the Product.** These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

**Symbols on the Product.** The following symbols may appear on the product:

## **Preface**

This manual provides high-level information for use of the Tektronix TLAPG2 Pattern Generator Module. Use this manual together with the Pattern Generator online help to use your Tektronix pattern generator.

Refer to the *TLA700 Series Logic Analyzer Instruction Manual* to install and configure the Tektronix pattern generator module.

#### **Related Documentation**

In addition to this instruction manual, the documentation listed in Table i is available for your Tektronix logic analyzer product. For documentation not specified in the table, contact your local Tektronix representative.

**Table i: Tektronix TLAPG2 Pattern Generator Module documentation**

| Location                                                                          | TLA Documentation                                            |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| Documents available in printed form and downloadable from the Tektronix web site. |                                                              |  |

|                                                                                   | Tektronix Logic Analyzer Family User Manual                  |  |

|                                                                                   | TLA700 Series Installation Manual                            |  |

| 0000                                                                              | TLA7PG2 Probe Instruction Manual                             |  |

|                                                                                   | TLA7UP Field Upgrade Kit Instructions                        |  |

| tektronix.com                                                                     |                                                              |  |

| Documents available as PDF files on the documentation CD.                         |                                                              |  |

|                                                                                   | Tektronix Logic Analyzer Family User Manual                  |  |

|                                                                                   | TLA700 Series Installation Manual                            |  |

|                                                                                   | Tektronix Pattern Generator Programmatic Interface (PPI.com) |  |

|                                                                                   | TLA7PG2 Probe Instruction Manual                             |  |

|                                                                                   | PatGenVu Readme                                              |  |

## **Contacting Tektronix**

Phone 1-800-833-9200\*

Address Tektronix, Inc.

Department or name (if known) 14200 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

**USA**

Web site www.tektronix.com

**Sales support** 1-800-833-9200, select option 1\*

Service support 1-800-833-9200, select option 2\*

Technical support Email: techsupport@tektronix.com

1-800-833-9200, select option 3\* 6:00 a.m. - 5:00 p.m. Pacific time

Outside North America, contact a Tektronix sales office or distributor; see the Tektronix web site for a list of offices.

<sup>\*</sup> This phone number is toll free in North America. After office hours, please leave a voice mail message.

## **Pattern Generator Module Introduction**

The pattern generator module adds pattern generator capability to the logic analyzer. You can generate specific data patterns to a target system and then use the logic analyzer to evaluate the resultant data from the target system.

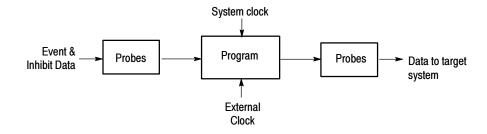

The pattern generator module functionality can be divided into blocks as shown in Figure 1. Refer to the figure as you read about the functional blocks.

Figure 1: Block diagram of the pattern generator module

#### **Probes**

The probe interface serves two purposes: to detect event and inhibit information and to output data to a target system. In addition to sending pattern generator data to the target system, the probe also sends clock and strobe information.

You can connect up to four probes to a single module. Each probe supports either 8 or 16 channels.

For information about connecting the Pattern Generator probes to both the TLA7PG2 module and the target system, refer to the *TLA700 Series Logic Analyzer Installation Manual*.

#### **Pattern Generator Program**

The pattern generator program is the heart of the pattern generator module. You can create blocks of data vectors to work together to create complex pattern generator programs. The program uses external and internal events to determine specific actions such as loops and branches to other data blocks. The program can be controlled by an internally selected clock or by an external clock through a front-panel BNC connector.

Use the Sequence Definition page of the Program window to set up and define a sequence events that make up the pattern generator program. Each sequence line determines how the pattern generator will use blocks of data that you define in the Pattern Generator Listing or Waveform window. You can set up the program to wait for specific events or signals and then jump to a different sequence when an event is either true or false.

You can also set up the pattern generator to single step through programs and output a single set of vectors with each clock cycle. This is useful for trouble-shooting or debugging setups.

For information about installing the Pattern Generator program, refer to the *TLA700 Series Logic Analyzer Installation Manual*.

# **Setting Up the Pattern Generator Module**

The pattern generator modules, like the LA modules, have a Setup window where you can specify the individual module setups, channel setups, probe setups, and signal setups. You should define these parameters before setting up the pattern generator program in the Program window.

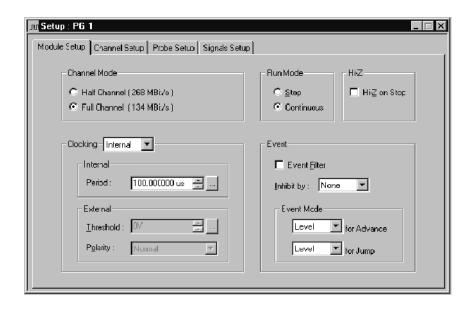

## **Module Setup Window**

Use the Module Setup window to define the channel mode, Run mode, clocking, and event setups. Figure 2 shows an example of the Module Setup window.

- Use the channel mode to select the speed and width of the logical module. Define the channel mode before defining other parameters. Otherwise, all module information will be lost when you change the channel mode.

- Set the Run mode to Step to output the patterns vectors one at a time. Use the Step button in the Status Monitor window to advance the steps. Set the Run mode to Continuous to output all vectors in a single step.

- Select the Hi-Z on Stop to cause the probes data and strobe outputs to go to a high-impedance state when the program stops.

- Use the Clocking to select an internal or external clock. When you select an external clock, you can also select the polarity and the threshold levels.

- Use the Event setups to filter out events, enable inhibit functions, and to define whether the pattern generator responds to events due to edges or levels.

Figure 2: Module Setup window

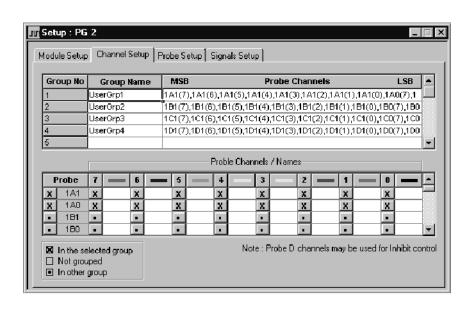

## **Channel Setup Window**

The Channel Setup window functions like the Channel Setup window in the LA modules. Use this window to define the channel group names, the logical grouping of channels, and the individual channel names. Figure 3 shows an example of the Channel Setup window.

Figure 3: Channel Setup window

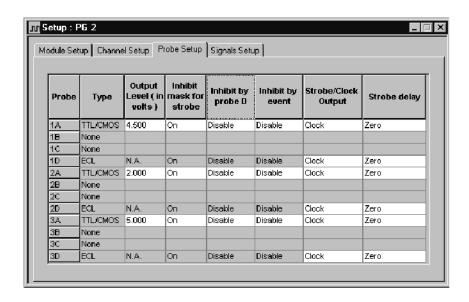

### **Probe Setup Window**

Use the Probe Setup window to specify the probe details such as the output threshold voltage and inhibit information. Figure 4 shows an example of the Probe Setup window.

Figure 4: Probe Setup window

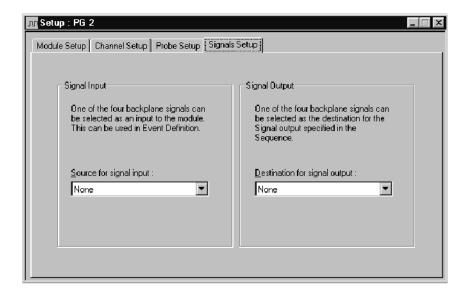

### **Signal Setup Window**

Use the Signal Setup window to define the input and output signals. After defining these signals, you can use them in the Program window to control the flow of the pattern generator program. You can use one of the backplane signals as an input to the pattern generator module and another backplane signal as an output signal. For more information on using signals, refer to the *Intermodule and External Signaling* section in the *Tektronix Logic Analyzer Family User Manual*.

Figure 5 shows an example of the Signal Setup window.

Figure 5: Signals Setup window

# **Setting Up the Pattern Generator Program**

After you have defined the module setups, you can use the Program window to define the pattern generator program. Use the Program windows in the following sequence:

- 1. Use the Block Definition window together with the Listing or Waveform window to define the data blocks and the vectors in each block.

- **2.** Use the Sequence Definition window to define a high-level sequence flow of the pattern generator program.

- **3.** Use the Subsequence Definition window to define subsequences or macros. You can call these subsequences in the Sequence Definition window.

- **4.** Use the Event Definition window to define how events are used with the pattern generator program.

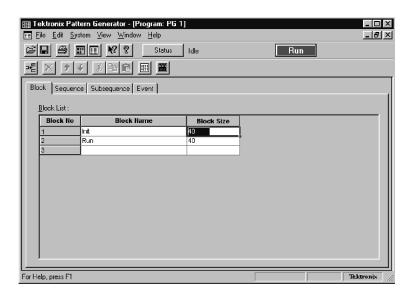

#### **Block Definition Window**

Use the Block definition window to define blocks of output data. You can define the size of each block and assign each block a meaningful name (such as Init, Read Cycle, Interrupt). Each block has its own associated Listing or Waveform window. Figure 6 shows an example of the Block Definition window.

Figure 6: Block Definition window

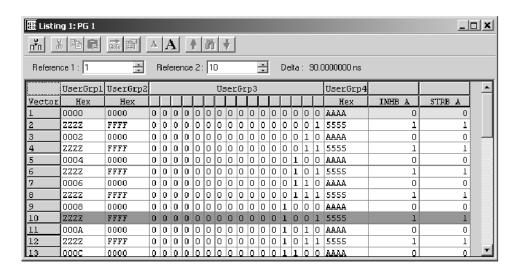

Use the Listing and Waveform windows to enter the data vectors. Click the Listing window icon to open the Listing window for the current block and enter the vector data. You can edit the vectors in either the Listing or Waveform windows.

Figure 7: Listing window

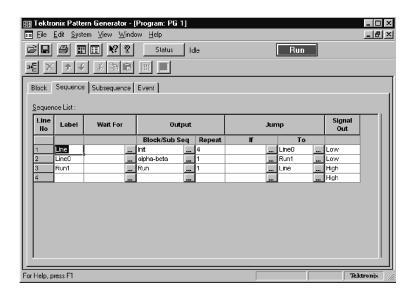

#### **Sequence Definition Window**

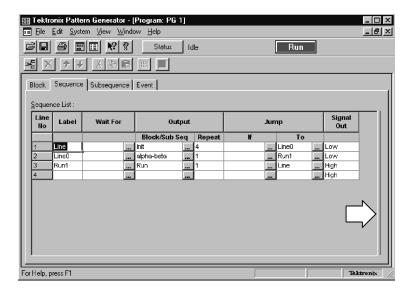

After defining the data blocks, use the Sequence Definition window to create a high-level overview of the pattern generator program. Figure 8 shows an example of the Sequence Definition window. You can do the following tasks with sequences:

- Output the data blocks. Use the data blocks that you defined in the Block Definition window. You can specify how many times you want to output the data blocks.

- Determine the program flow. You can wait for an external event to occur before outputting the data blocks. You can also pass the program control to another sequence by jumping to a specific sequence label.

- Use Subsequences to execute or control the program flow. Subsequences are macros that you define in the Subsequence Definition window. For example, you can use a subsequence to output a read cycle five times and then output a write cycle before returning control to the main program sequence.

- Output a high or low signal to a defined event line. The event line is the one you defined in the Signal Setup window.

Each sequence has its own line. Use labels for each line to help with the program flow. Unless you set up a data block to be repeated an infinite number of times, the program flow will pass to the next sequence (or jump to a defined label). When the last sequence has been executed, the program flow stops.

Figure 8: Sequence Definition window

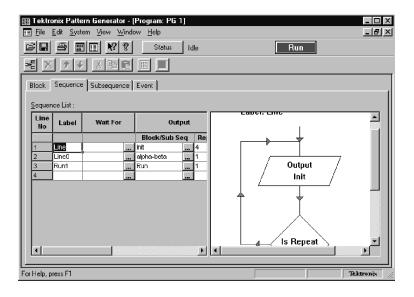

After defining a sequence, you can display a graphical image of the sequence flow by clicking and dragging the vertical bar on the right side of the Sequence Definition window (see Figure 9).

The appearance of the sequence flow depends on the sequence definition. Each sequence line has its graphic (see Figure 10).

Figure 9: Drag the vertical bar to the left to display the sequence flow graphic

Figure 10: Sequence flow graphic

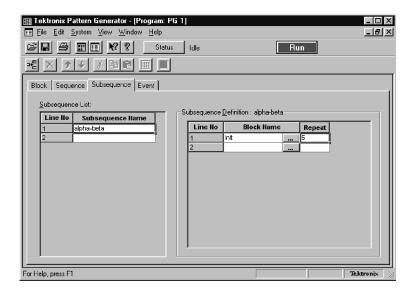

#### **Subsequence Definition Window**

Use the Subsequence Definition window to define macros to use in the Sequence Definition window. Subsequences are useful for defining tasks that you may not want to appear directly in the Sequence Definition window.

Assign a name for the subsequence in the left side of the window. This name will appear in the Sequence Definition window. Define the actual tasks (data blocks) in the right side of the window. The block names are the ones you defined in the Block Definition window. Figure 11 shows an example of the Subsequence Definition window.

Figure 11: Subsequence Definition window

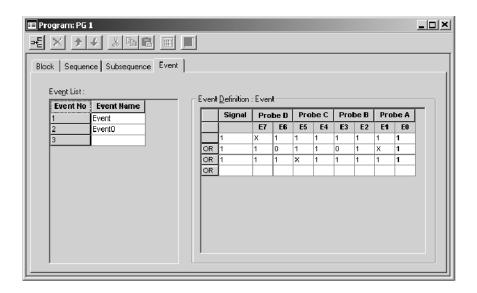

#### **Event Definition Window**

Use the Event Definition window to define events that you can use in the Sequence Definition window. Enter an event name in the left side of the window and then define events in the right side of the window.

Signal events refer to the input backplane input signal that you defined in the Signal Setups window. The Probe events refer to the input signals on each probe; each probe can have two event lines. Figure 12 shows an example of the Event Definition window.

The events in each row are logically ANDed together while the rows are logically ORed together.

Figure 12: Event Definition window

# **Appendix A: TLA7PG2 Pattern Generator Module Characteristics**

Tables 1 through 6 list the specifications for the pattern generator module. For information on the individual pattern generator probes, refer to *TLA7PG2 Pattern Generator Probe Instruction Manual*.

Table 1: PG module electrical specification, operational mode

| Characteristic                                                                                                      | Description                                                                                                                                                                                                                                                                                                                             |                                        |  |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Operational mode                                                                                                    | •                                                                                                                                                                                                                                                                                                                                       |                                        |  |

| Normal                                                                                                              | Pattern data output is synchronize                                                                                                                                                                                                                                                                                                      | d by the internal/external clock input |  |

| Step                                                                                                                | Pattern data output is synchronize                                                                                                                                                                                                                                                                                                      | d by the software command              |  |

| Output pattern                                                                                                      |                                                                                                                                                                                                                                                                                                                                         |                                        |  |

| Maximum Data Output Rate Output level: 5 V Load: 1 M $\Omega$ + 1 pF Series termination resistor: 75 $\Omega$       | 134 Mb/s in Full Channel Mode<br>268 Mb/s in Half Channel Mode                                                                                                                                                                                                                                                                          |                                        |  |

| Maximum Clock Output Frequency Output level: 5 V Load: 1 M $\Omega$ + 1 pF Series termination resistor: 75 $\Omega$ | 134 MHz in Full Channel Mode<br>134 MHz in Half Channel Mode                                                                                                                                                                                                                                                                            |                                        |  |

| Maximum Operating Frequency                                                                                         | The maximum operating frequency of the module is a function of the output level, output pattern and the load condition, including the series termination resistor in the probe. Operating conditions exceeding this frequency may result in damage to the probe.                                                                        |                                        |  |

| Pattern length                                                                                                      | 40 to 262,140 (2 <sup>18</sup> - 4) in Full Channel Mode (standard)<br>80 to 524,280 (2 <sup>19</sup> - 8) in Half Channel Mode (standard)<br>40 to 1,048,572 (2 <sup>20</sup> - 4) in Full Channel Mode (option 1M or PowerFlex upgrade)<br>80 to 2,097,144 (2 <sup>21</sup> - 8) in Half Channel Mode (option1M or PowerFlex upgrade) |                                        |  |

| Number of channels                                                                                                  | 64 channels in Full Channel Mode<br>32 channels in Half Channel Mode<br>The pattern memory for the followi<br>control/internal inhibit control                                                                                                                                                                                          |                                        |  |

|                                                                                                                     | Probe D data output channel                                                                                                                                                                                                                                                                                                             | Control                                |  |

|                                                                                                                     | D0:0                                                                                                                                                                                                                                                                                                                                    | STRB0                                  |  |

|                                                                                                                     | D0:1                                                                                                                                                                                                                                                                                                                                    | STRB1                                  |  |

|                                                                                                                     | D0:2                                                                                                                                                                                                                                                                                                                                    | STRB2                                  |  |

|                                                                                                                     | D0:3                                                                                                                                                                                                                                                                                                                                    | STRB3                                  |  |

|                                                                                                                     | D0:4                                                                                                                                                                                                                                                                                                                                    | Inhibit probe A                        |  |

Table 1: PG module electrical specification, operational mode (Cont.)

| Characteristic         | Description             | Description     |  |

|------------------------|-------------------------|-----------------|--|

|                        | D0:5                    | Inhibit probe B |  |

|                        | D0:6                    | Inhibit probe C |  |

|                        | D0:7                    | Inhibit probe D |  |

| Sequences              | Maximum 4,000           | •               |  |

| Number of blocks       | Maximum 4,000           |                 |  |

| Number of subsequences | Maximum 50              |                 |  |

| Subsequences           | Maximum 256 steps       |                 |  |

| Repeat count           | 1 to 65,536 or infinite |                 |  |

Table 2: PG module clocking

| Characteristic       | Description                                                                                         |  |

|----------------------|-----------------------------------------------------------------------------------------------------|--|

| Internal clock       | <u> </u>                                                                                            |  |

| Clock Period         | 2.0000000 s to 7.462865 ns in Full Channel Mode<br>1.0000000 s to 3.7313432 ns in Half Channel Mode |  |

| Period Resolution    | 8 digits                                                                                            |  |

| Frequency Accuracy   | ± 100 PPM                                                                                           |  |

| External clock input | ·                                                                                                   |  |

| Clock Rate           | DC to 134 MHz in Full Channel Mode<br>DC to 267 MHz in Half Channel Mode                            |  |

| Polarity             | Normal or Invert                                                                                    |  |

| Threshold            |                                                                                                     |  |

| Range                | -2.56 V to +2.54 V                                                                                  |  |

| Resolution           | 20 mV                                                                                               |  |

| Input Impedance      | 1 k $\Omega$ terminated to GND                                                                      |  |

| Sensitivity          | 500 mV <sub>p-p</sub>                                                                               |  |

Table 3: PG module event processing

| Characteristic              | Description                                                              |

|-----------------------------|--------------------------------------------------------------------------|

| Event Action                | Advance, Jump and Inhibit                                                |

| Number of Event Inputs      | 8 External Event Inputs (2 per each probe)                               |

| Number of Event Definitions | 8 (A maximum of 256 event input patterns can be OR'd to define an event) |

#### Table 3: PG module event processing (Cont.)

| Characteristic | Description   |

|----------------|---------------|

| Event Mode     |               |

| for Advance    | Edge or Level |

| for Jump       | Edge or Level |

| Event Filter   | None or 50 ns |

#### Table 4: PG module inter-module interactions

| Characteristic | Description                                                                                              |

|----------------|----------------------------------------------------------------------------------------------------------|

| Signal Input   | Input from backplane Selectable from Signal 1, 2, 3, and 4 Used to define the Event                      |

| Signal Output  | Output to backplane Selectable from Signal 1, 2, 3, and 4 Specified as High or Low in each Sequence line |

#### Table 5: PG module merged PG modules

| Characteristic                                | Description                                                                                                                                                |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of modules that can be merged together | Five                                                                                                                                                       |

| External Event Input for merged module        | For Jump and Advance, only the External Event Input of the leftmost module is used. For Inhibit, each module uses its own External Event Input as a source |

#### Table 6: PG module mechanical

| Characteristic                            | Description                   |

|-------------------------------------------|-------------------------------|

| Slot width                                | Requires two mainframe slots  |

| Weight<br>(Typical)                       | 2.5 kg (5 lbs. 4 oz.)         |

| Overall dimensions (excluding connectors) |                               |

| Height                                    | 10.32 in (262 mm)             |

| Width                                     | 2.39 in (61 mm)               |

| Depth                                     | 14.7 in (373 mm)              |

| Mainframe interlock                       | 1.4 ECI keying is implemented |

# **Appendix B: Pattern Generator Physical-Logical Conversion**

The logic analyzer and DSO modules handle signals 1, 2, 3, and 4 with a logical expression (True/False). However, the pattern generator module handles these signals with a physical expression (High/Low). Select whether to use the signals as AND or OR from the TLA application's Signals property page of the System Configuration window. Use Tables 7 and 8 to convert physical expressions to logical expressions or vice versa.

Table 7: For Signal 1, 2, and 3, 4, (logical function AND)

| LA/DSO expression                  | Logical true | Logical false |

|------------------------------------|--------------|---------------|

| Pattern generator signal output    | High         | Low           |

| Pattern generator event definition | 1            | 0             |

Table 8: For Signal 3, 4 (logical function OR)

| LA/DSO expression                  | Logical true | Logical false |

|------------------------------------|--------------|---------------|

| Pattern generator signal output    | Low          | High          |

| Pattern generator event definition | 0            | 1             |

Only one module in the system can drive Signal 1. Only one module in the system can drive signal 2. When used with an expansion mainframe, all modules that drive Signal 3 should be in the same mainframe, and all modules that drive Signal 4 should be in the same mainframe.