# **TOPSwitch**GX Forward Design Methodology Application Note AN-30

### Introduction

The single-ended forward converter topology is often the best solution for AC-DC applications that require higher powers and higher output currents than are practical from flyback converters. The forward converter extends the power capability of *TOPSwitch-GX* to greater than 200 W for high current outputs.

The feature set of *TOPSwitch-GX* offers the following advantages in single-ended forward designs:

- · Built-in soft-start

- Built-in under-voltage lockout

- Built-in adjustable current limit

- Programmable duty cycle reduction to limit duty cycle excursion at high line and transient load conditions

- Higher efficiency (typically >70%)

- Very good light-load efficiency

- Voltage mode control for simpler loop designs with magnetic amplifier post-regulators

- · Built-in remote on-off

- Low component count

- Improved EMI

### Scope

This application note is for engineers designing an AC-DC power supply using *TOPSwitch-GX* in a single-ended forward converter. It addresses single input voltage 230 VAC or doubled 115 VAC input, but does not address universal input (85 V to 265 V) designs. The document highlights design parameters that are fundamental to the use of *TOPSwitch-GX* in a single-ended forward converter. It offers a procedure to compute transformer turns, output inductance and other design parameters. This procedure enables designers to build an operational prototype in the shortest possible time. Refinement of the prototype hardware after bench evaluation will lead to a final design.

The design methodology presented here is sufficiently general to cover a variety of single-ended forward designs, including power supplies for personal computers. It provides for multiple outputs with coupled inductors, independent multiple outputs, and outputs with both linear or magnetic amplifier post regulators.

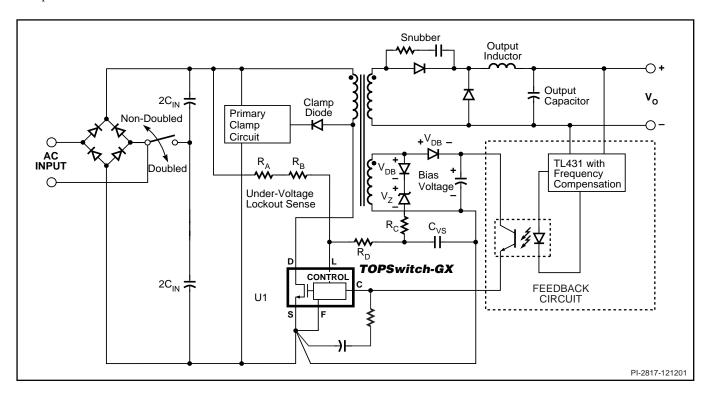

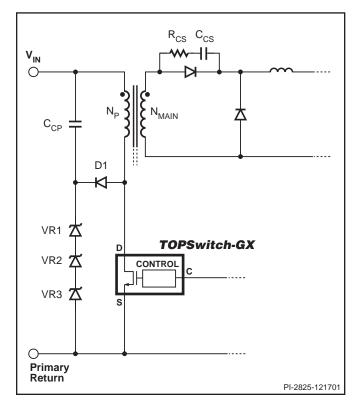

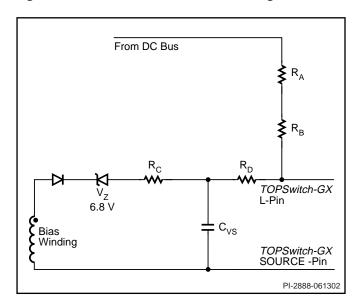

Figure 1. Typical Configuration of TOPSwitch-GX in a Single-Ended Forward Converter.

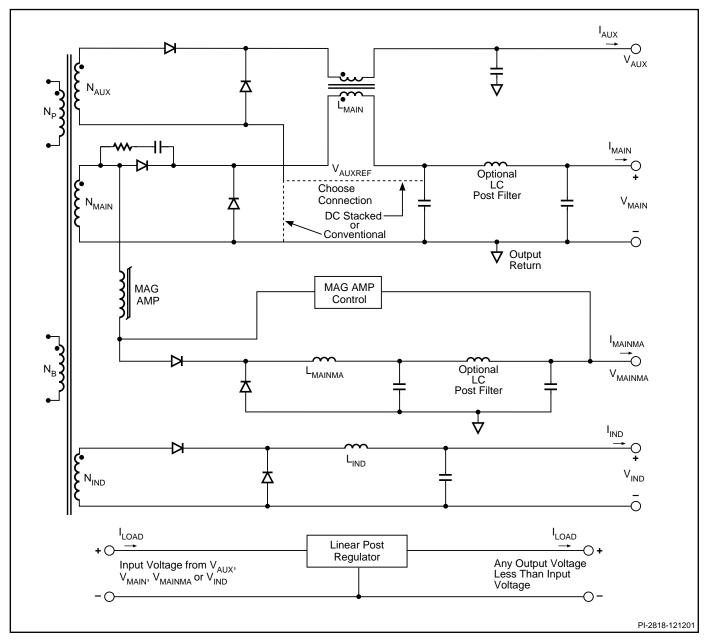

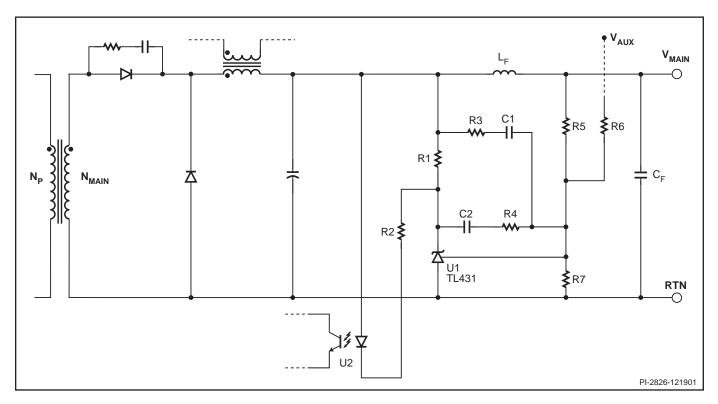

Figure 2. General Output Options for the Forward Converter Described in the Methodology.

This document does not address the design of magnetic amplifiers nor linear regulators. It determines design parameters for the transformer and the inductors, but does not give construction details for those magnetic components. Such details are deferred to other application notes and component suppliers. References [1] through [6] are good sources of information for the design of transformers and inductors. Software for design of magnetic amplifiers is available from [5]. Reference [1] is also an excellent resource for other important topics in power electronics.

### **Design Methodology Overview**

The methodology assumes the reader knows the theory of operation of the forward converter and the fundamentals of power supply design. It is a companion to the *PI Expert* software for forward converter design (available from the Power Integrations Web site). Designers are advised to check Power Integrations' Web site at *www.powerint.com* for the latest application information.

This presentation uses a typical combination of output options for illustration of the methodology (see Figure 2). This document

gives the basic expressions illustrating the methodology. The *PI Expert* software uses more complex versions of these expressions containing additional parameters to account for non-ideal effects. Thus, results from the software may not exactly match the computations from expressions in this document.

This document assumes a non-doubled input configuration. *PI Expert* includes modified expressions for both doubler and non-doubler input configurations. To simplify the expressions, all outputs are assumed to operate in continuous conduction mode, consistent with the worst case design at maximum load. At lower load conditions it is possible for individual outputs to operate in discontinuous conduction mode.

The methodology begins with an explanation of the general converter topology. It then presents the design flow, showing the major tasks in a high level flowchart. After a review of the nomenclature and definitions of variables, it discusses the details of the design procedure. Rationale, assumptions and expressions are given to help the designer enter parameters and interpret results. A complete list of variables used in the expressions follows in Appendix A. Appendix B offers a procedure for hardware verification. A worked example is presented in Appendix C.

### **General Converter Topology**

Figure 1 shows a typical single-ended forward converter using *TOPSwitch-GX*. Detail is focused on the primary side of the transformer because the circuits on the secondary are conventional and covered in other literature.

Resistors  $R_A$  and  $R_B$  set the under-voltage lockout threshold. Resistor network  $R_A$ ,  $R_B$ ,  $R_C$ , and  $R_D$  with capacitor  $C_{vs}$  adjusts the maximum duty ratio as a function of the input voltage. This methodology gives the procedure to determine proper values for the resistors and the capacitor.

Another key element in the use of TOPSwitch-GX is the primary clamp ( $C_{CP}$ , D1, VR1, VR2 and VR3 in Figure 10) which resets the transformer flux and limits the maximum drain voltage. This methodology assumes use of this Zener-capacitor clamp circuit. Guidance for selection of components for this particular clamp is included in this application note.

The topic of clamp circuits is deferred to a separate application note. Designers may choose to use their own clamp circuits with the restriction that *resonant clamps*, *(for example, LCD clamps-inductor/capacitor/diode) and reset windings are not recommended*. The internal current sense of *TOPSwitch-GX* does not allow the high reset current of a resonant clamp to be excluded from the sensed drain current.

This methodology uses an ordinary optically isolated feedback

circuit that is common in voltage mode systems with a two-pole response. The frequency compensation will in general require two zeros and two poles to obtain the phase margin desired for most applications. While the design of the feedback circuit is a separate topic beyond the scope of this application note, the general topology of the circuit is discussed.

### **Output Options**

Salient features of the output circuits are illustrated in Figure 2. Multiple secondary windings of the transformer may be configured in many different ways to give several options for regulated and unregulated output voltages.

All applications will have only one main output. This is the voltage that is regulated directly by *TOPSwitch-GX* through the optically isolated feedback circuit. In general, any number of auxiliary outputs may be derived from other secondary windings and regulated indirectly by means of a coupled inductor that they share with the main output.

The secondary windings for the auxiliary outputs may be configured in two different ways. The conventional configuration connects one side of the auxiliary winding to the main output return. This connection is used when the auxiliary output is the opposite polarity of the main output. An alternative configuration, sometimes known as the DC stacked connection, has one side of the auxiliary winding referenced to the main output instead of the output return. It has the advantage of better regulation of the auxiliary output voltage than the non-stacked arrangement, but is limited to outputs that are greater in magnitude and of the same polarity as the main output voltage.

Any number of unregulated output voltages may be derived from circuits that do not share an inductor with any other outputs. They are related to the main output only through separate secondary windings on the transformer. Their inductors are independent of the others. These outputs typically are referenced to the output return, but alternatively they may be referenced to any potential that the isolation of the transformer will tolerate.

Multiple tightly regulated voltages may be obtained with either linear or switching post regulators. These external regulators may be added to any output, including the main output. They are simply additional loads on those output voltages.

A particularly useful type of switching post regulator is the magnetic amplifier, which uses a saturating magnetic element as an independently controlled switching device. While a magnetic amplifier can in theory be operated from any output, this methodology restricts the connection to the main output only.

Since it is not possible to treat every combination of output

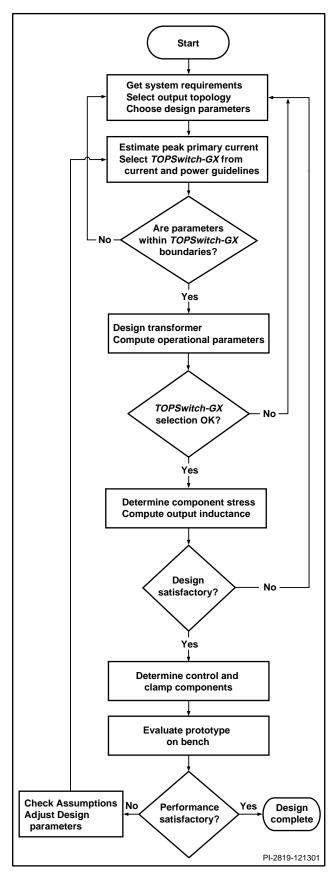

Figure 3. Flowchart Showing Major Tasks in the Design of Forward Converters with TOPSwitch-GX.

options in this presentation, the methodology will be restricted to those that are typical for power supplies in personal computers. Therefore, this methodology allows the following options:

- One main output

- A maximum of one auxiliary output that may be DC stacked to the main output or referenced to output return

- A maximum of one independent output

- A maximum of one magnetic amplifier post regulator that operates from the secondary winding for the main output

- Any number of linear post regulators that may operate from any output

### **Design Flow**

Figure 3 is an abbreviated flowchart of the major tasks in the design methodology. The important decision blocks involve the selection of the proper *TOPSwitch-GX* device for the application, and the designer's satisfaction with the overall design.

All designs begin with the definition of requirements. The next section discusses the parameters a designer needs to know before the design can start.

Parameters for the forward converter are dominated by the output specifications. The designer will have to choose a topology that is appropriate for the application. An application that calls for only one output is simplest, while a requirement for several outputs with complex loading needs careful consideration. It may be necessary to go through several designs to select the most satisfactory configuration.

Knowledge of system requirements and selection of the output topology allow the designer to compute the magnetic parameters. These are turns ratios for the transformer and the coupled inductor (if the design has an auxiliary output), plus values of inductance for independent outputs and the output inductor for the magnetic amplifier (also called mag amp). The output inductor for the mag amp is different from the inductive switching element (sometimes called a saturable reactor, saturable core, or saturable choke), that is not addressed in this note.

The peak primary current can be computed from the turns ratios established for the transformer along with the ripple current in the output inductors. This allows selection of the appropriate *TOPSwitch-GX*. It must have sufficient current limit to handle the maximum steady-state load and must have enough additional margin to accommodate peak loads and transients. Another consideration in the selection of the *TOPSwitch-GX* is power dissipation in the device. A device that can handle the steady-state and peak primary currents does not guarantee ability to meet thermal limitations – this is an independent consideration.

The efficiency of the power system is an important consideration in every design. The designer should have a goal for the efficiency of the system at the start of the design, based on reasonable allowances for power lost in the specific areas of the power supply.

The efficiency goal should take into account losses in the transformer, inductors, output rectifiers, and clamp circuits. Most high power designs have some form of power factor correction (PFC). The type of PFC will affect the efficiency. For example, the voltage drop on a passive PFC (a large inductor in series with the AC line input) will reduce the minimum input voltage at the converter, and will also reduce system efficiency.

Total system efficiency should consider losses in the AC input circuit, including the EMI filter, that are not part of this design methodology. Only a bench evaluation can determine the actual efficiency of the power supply. If the efficiency is not satisfactory, the designer must revise the values of component parameters or change the output topology for a repeat design.

If the requirements call for a holdup time, the designer must determine the amount of bulk input capacitance that is required to achieve the specified holdup time from the designated input voltage. It is often necessary to adjust parameters by iteration to meet the objectives of the design.

*PI Expert* performs the calculations to allow the designer to see the interactions of the variables immediately.

After the values of the major power components are determined, the designer needs to check voltage and current stress to select components with the proper ratings. Then the designer can choose values for small signal components that set voltage detection thresholds and other control parameters.

The final step is an evaluation of a prototype on the bench. This is the only way to confirm that the design is satisfactory, and to get necessary information to adjust the parameters if a redesign is necessary.

### **Definition of Variables**

Table 1 gives a set of system parameters that should be known at the start of the design. The list is general, so all the parameters will not necessarily be relevant to all applications. Some values will be given by the system specification, while others are the designer's choice.

The notation in this document uses descriptive subscripts to keep track of variables. Quantities that refer to the main output are designated with the subscript  $_{MAIN}$ . Variables associated with an auxiliary output are identified by the subscript  $_{AUX}$ , and those related to an independent output have the subscript  $_{IND}$ .

| Name                                                      | Description                               |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

| η                                                         | Total system efficiency                   |  |  |  |  |  |

| f <sub>L</sub>                                            | AC mains frequency                        |  |  |  |  |  |

| f <sub>s</sub>                                            | TOPSwitch-GX switching frequency          |  |  |  |  |  |

| I <sub>AUX</sub>                                          | Current from auxiliary output             |  |  |  |  |  |

| I <sub>IND</sub> Current from independent output          |                                           |  |  |  |  |  |

| I <sub>MAIN</sub>                                         | Current from main output                  |  |  |  |  |  |

| I <sub>MAINMA</sub>                                       | Current from magnetic amplifier           |  |  |  |  |  |

| t <sub>H</sub>                                            | Holdup time                               |  |  |  |  |  |

| V <sub>ACMAX</sub> Maximum AC input voltage               |                                           |  |  |  |  |  |

| V <sub>ACMIN</sub> Minimum AC input voltage               |                                           |  |  |  |  |  |

| V <sub>ACNOM</sub> Nominal AC input voltage               |                                           |  |  |  |  |  |

| V <sub>ACUV</sub> AC under-voltage threshold              |                                           |  |  |  |  |  |

| V <sub>AUX</sub> Auxiliary output voltage                 |                                           |  |  |  |  |  |

| V <sub>AUXREF</sub> Auxiliary output reference voltage    |                                           |  |  |  |  |  |

| V <sub>DROPOUT</sub> Lowest DC bus voltage for regulation |                                           |  |  |  |  |  |

| V <sub>DSOP</sub> Maximum drain-to-source voltage         |                                           |  |  |  |  |  |

| V <sub>HOLDUP</sub>                                       | DC bus voltage at start of $t_{_{\rm H}}$ |  |  |  |  |  |

| V <sub>IND</sub>                                          | Independent output voltage                |  |  |  |  |  |

| V <sub>MAIN</sub>                                         | Main output voltage                       |  |  |  |  |  |

| V <sub>MAINMA</sub>                                       | Magnetic amplifier output voltage         |  |  |  |  |  |

Table 1. System Parameters Needed to Start a Design.

These conventions are used to identify voltages, currents, and components.

When there is more than one output in a category, the individual members are distinguished by numbers appended to the subscript, as in  $_{\rm IND1}$ ,  $_{\rm IND2}$  and  $_{\rm IND3}$  for three independent outputs. Quantities related to the magnetic amplifier have  $_{\rm MA}$  appended to the subscript, as in  $_{\rm MAINMA}$  referring to the magnetic amplifier on the secondary winding for the main output. This notation has the generality necessary to expand the allowable output options.

Turns ratios on magnetic components are designated by lower case n with appropriate subscripts, while actual numbers of turns are distinguished by upper case N with identifying subscripts.

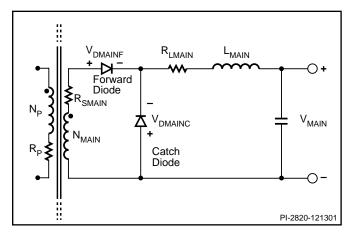

There are a few other variables and notations that need definition. Figure 4 shows a section of output circuitry that identifies some important electrical quantities. Each output of a forward converter has two diodes. One is designated the forward diode and the other is the catch diode. Associated quantities have  $_{\rm F}$  or  $_{\rm C}$  appended to their respective subscripts.

Figure 4. Output Circuit with Parameter Definitions.

Voltage drops on diodes have subscripts with the prefix  $_{\rm D}$  for the conduction drop and  $_{\rm PIV}$  for the reverse blocking voltage. The only exception to this convention is for drain-to-source voltages, which will be obvious from context.

Figure 4 also shows series resistances that the designer can include to get better predictions of performance.

### **Detailed Design Procedure**

This methodology guides the designer through a procedure that determines parameters for prototype hardware. After bench evaluation, the designer refines the parameters to meet all requirements.

The design can start with knowledge of only the most basic system requirements. For example, the forward voltage drops on diodes and the resistances of transformer windings are seldom known very accurately at the beginning of a new design. Results of the design with default values will guide the designer to select particular components with known parameters. Figure 5 gives an expanded flowchart that includes the detailed steps which follow.

### Step 1. Establish system requirements.

Determine the parameters in Table 1. These should be available from a system specification of the power supply's application.

The software will compute and display the maximum and minimum DC bus voltages to the converter from the AC inputs. The need to know maximum and minimum voltages is obvious. The optional nominal input voltage  $V_{\text{ACNOM}}$  helps determine the turns ratios of the transformer. The goal is to set the unregulated output voltages at their nominal values when the input is at its nominal value. The designer may choose any value between  $V_{\text{ACMAX}}$  and  $V_{\text{ACMIN}}$  to be the nominal value.

The peak DC bus voltage (non-doubled) is

$$V_{MAX} = V_{ACMAX} \sqrt{2} \tag{1}$$

while the DC bus voltage at the valley of the ripple at the minimum steady state AC input is

$$V_{MIN} = \sqrt{2V_{ACMIN}^2 - \frac{2P_o\left(\frac{1}{2f_L} - t_C\right)}{\eta_{DC}C_{IN}}}$$

(2)

where  $P_{\scriptscriptstyle O}$  is the total output power,  $t_{\scriptscriptstyle C}$  is the conduction time of the bridge rectifier,  $\eta_{\scriptscriptstyle DC}$  is the efficiency exclusive of losses in the AC input circuit, and  $C_{\scriptscriptstyle IN}$  is the capacitance at the input to the converter. Use 3 ms for  $t_{\scriptscriptstyle C}$  and use the total system efficiency  $\eta$  for  $\eta_{\scriptscriptstyle DC}$  if no better estimates are available. A good initial value for  $C_{\scriptscriptstyle IN}$  is 1  $\mu F$  per watt multiplied by  $P_{\scriptscriptstyle O}$ .

The designer should carefully choose the value of  $t_c$  when using passive PFC input (a large inductor in the AC line), since this approach significantly increases the diode conduction time. Also, the voltage waveform will deviate from a sinusoid, causing some error in the prediction of Equations (1) and (2).

Remember to use the input voltage to linear regulators, not the regulated output voltage, to compute the total output power. The dissipation in the linear regulator is part of the load on the converter.

The nominal DC bus voltage is defined to be

$$V_{NOM} = \frac{\sqrt{2}}{2} \left[ V_{ACNOM} + \sqrt{V_{ACNOM}^2 - \frac{P_O\left(\frac{1}{2f_L} - t_C\right)}{\eta_{DC} C_{IN}}} \right]$$

(3)

This is simply the midpoint between the peak and valley of the ripple voltage on the input capacitor (non-doubled).

### Step 2. Set ripple current in the output inductors.

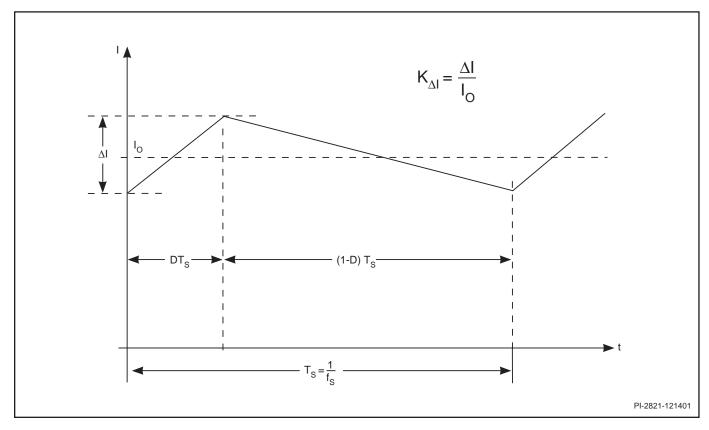

Choose the ripple current factor  $K_{AI}$ . Figure 6 shows how it is related to the average output current.  $K_{AI}$  is a useful parameter for design because it directly influences the size of the output inductor. It also affects the peak primary current and the RMS current in the output capacitors.

Figure 5. Expanded Flow Chart Showing Detailed Steps in Forward Design Methodology.

Figure 6. Inductor Current Showing Definition of  $K_{\Lambda r}$

The ripple current in the inductor depends on the converter's operating point. In general,  $K_{AI}$  will change with the duty ratio according to the relationship

$$K_{\Delta I} = K_{\Delta I0} (1 - D) \tag{4}$$

where  $K_{_{\! \! \Delta 10}}$  is the limit as the duty ratio approaches zero. The expression that relates  $K_{_{\! \! \Delta 10}}$  to the inductance L for a given generic output is

$$K_{\Delta I0} = \frac{V_{OUTPUT} + V_{D(OUTPUT)C}}{LI_{OUTPUT}f_{S}}$$

(5)

where  $V_{\mbox{\tiny D(OUTPUT)C}}$  is the voltage on the catch diode when it is conducting.

$\rm K_{AI}$  will be between 0.15 and 0.3 for most practical designs. The  $\rm K_{AI}$  corresponding to the highest input voltage is used for calculations. All dependent quantities should then be computed for the designer's inspection. Since the duty ratio at the highest input voltage will usually be very small,  $\rm K_{AIO}$  is usually a very good approximation to the worst case  $\rm K_{AI}$ .

If any outputs have nonzero minimum load, use the minimum load as a guide for the upper limit on  $K_{AI}$ . The best regulation

across multiple outputs at minimum load is obtained when

$$K_{\Delta I} \le 2 \left( \frac{I_{MINIMUM}}{I_{MAXIMUM}} \right) \tag{6}$$

where  $I_{\text{minimum}}$  and  $I_{\text{maximum}}$  are the respective minimum and maximum average output currents.

The common  $K_{AI}$  at full load allows calculation of the inductance. The designer has the option to change any value of any inductor to suit particular requirements. The change in inductance will change the  $K_{AI}$  for that particular inductor.

For coupled inductors,  $K_{AI}$  indicates the ripple component of the total ampere turns, not ripple current on any individual winding.

#### Step 3. Calculate turns ratios for the transformer.

Turns ratios on the transformer are computed with respect to the main output winding. The primary-to-main turns ratio is fixed by the input and output voltages and the maximum duty ratio, which is limited by the maximum drain-to-source voltage that is set by the designer. The maximum duty ratio to guarantee reset of the transformer is

$$D_{MAX\_RESET} \le 1 - \frac{V_{DROPOUT}}{V_{DSOP}} \le 0.74 \tag{7}$$

where  $V_{DROPOUT}$  is the DC bus voltage at the end of the holdup time and  $V_{DSOP}$  is the maximum drain-to-source voltage on the TOPSwitch-GX during operation. The minimum recommended value for  $V_{DROPOUT}$  is 130 V, while  $V_{DSOP}$  is usually less than the breakdown voltage of 700 V by a comfortable safety margin. A safety margin of 15% is typical, giving 600 V for  $V_{DSOP}$ .

The maximum duty ratio for the converter occurs at  $V_{DROPOUT}$ . This must be reduced as a function of line voltage from the  $DC_{MAX}$  of TOPSwitch-GX by external circuitry in Step 15. The recommended maximum duty ratio  $D_{MAX}$  for the forward converter application depends on the operating input voltage range. For a 3:1 operating range ( $V_{MAX}$ :  $V_{DROPOUT}$ ) 70% is typical. As the operating range reduces so does the value of  $D_{MAX}$ . For a 2:1 operating range a value of 50% would be selected.

First, compute the turns ratios for the primary and the auxiliary winding. The turns ratio on the primary of the transformer is

$$n_{P} = \frac{V_{DROPOUT} - V_{DS}}{\left(V_{MAIN} + V_{DMAINC}\right)\left(\frac{1 - D_{MAX}}{D_{MAX}}\right) + V_{MAIN} + V_{DMAINF}} \tag{8a}$$

Where  $V_{DS}$  is the average drain-to-source voltage during the on-time of *TOPSwitch-GX*:

When  $V_{\text{DMAINF}}$  and  $V_{\text{DMAINC}}$  are the same value  $V_{\text{DMAIN}}$ , this equation simplifies to:

$$n_P = \frac{\left(V_{DROPOUT} - V_{DS}\right)D_{MAX}}{V_{MAIN} + V_{DMAIN}} \tag{8b}$$

The turns ratio for the auxiliary winding is

$$n_{AUX} = \frac{V_{AUX} + V_{DAUXC} - V_{AUXREF}}{V_{MAIN} + V_{DMAINC}} \tag{9}$$

Equation (8) is valid for systems where the leakage inductance of the transformer is negligible. This is a reasonable assumption because the leakage inductance must be minimized for low power dissipation and proper operation of the clamp circuit. Leakage inductance reduces the effective duty ratio on the secondary circuits by delaying the turn-off of the catch diodes. The effect can be significant in designs with very high output currents. To compute the turns ratio for the primary winding when leakage inductance is a consideration, subtract the constant

$$\delta_D = \frac{L_{MAINLK} I_{MAINSEC}}{V_{MAIN}} D_{MAX} f_S \tag{10}$$

from  $D_{\text{MAX}}$  in Equation (8). In Equation (10),  $L_{\text{MAINLK}}$  is the leakage inductance of the secondary winding of the main output,  $I_{\text{MAINSEC}}$  is the winding current required to turn off the catch diode of the main output, and  $f_{\text{s}}$  is the switching frequency. Note that in the DC stacked connection for the auxiliary output, the winding for the main output carries the current of the main output plus the current of the stacked auxiliary outputs.

Next, compute the duty ratio  $D_{\text{NOM}}$  that corresponds to the nominal input voltage.

$$D_{NOM} = \frac{V_{MAIN} + V_{DMAINC}}{\frac{V_{NOM}}{n_P} - V_{DMAINF} + V_{DMAINC}}$$

(11)

This allows a better estimate of the turns ratio that will produce the desired independent output voltage.

$$n_{IND} = \frac{V_{IND} + V_{DINDF} D_{NOM} + V_{DINDC} (1 - D_{NOM})}{V_{MAIN} + V_{DMAINF} D_{NOM} + V_{DMAINC} (1 - D_{NOM})}$$

$$(12)$$

Finally, compute the turns ratio for the bias winding so that the bias voltage is greater than eight volts. This value is the CONTROL pin voltage, 5.8 V, plus the 2.2 V saturation voltage of the optocoupler's phototransistor at  $V_{\text{DROPOUT}}$ .

The turns ratio for the bias winding is then

$$n_B \ge n_P \left( \frac{8 \text{ volts} + V_{DB}}{V_{DROPOUT}} \right)$$

(13)

where  $V_{\text{DROPOUT}}$  is the minimum DC bus voltage for regulation and  $V_{\text{DB}}$  is the voltage drop on the rectifier for the bias voltage. Check that the breakdown voltage on the phototransistor of the optocoupler is higher than the bias voltage at the highest transient input voltage.

#### Step 4. Calculate the primary current.

Find the peak and RMS values for the primary current. This is a preliminary estimate from the system parameters. It allows the designer to assess the suitability of his application for *TOPSwitch-GX* as early as possible.

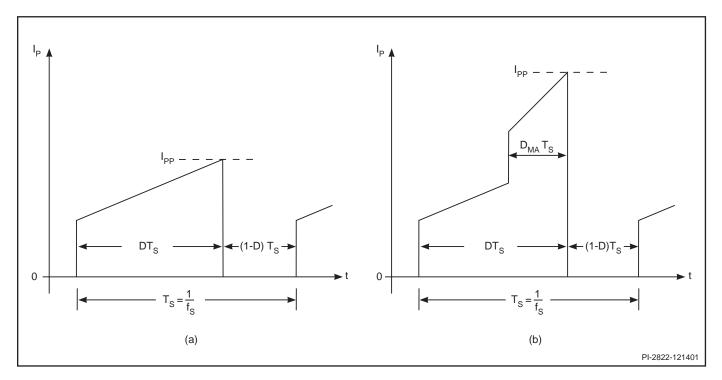

Figure 7 shows typical primary current waveforms for forward converters with and without a magnetic amplifier post regulator. Figure 7(a) is without a magnetic amplifier, whereas Figure 7(b) shows the effect of one magnetic amplifier post regulator. TOPSwitch-GX determines the duty ratio D to regulate the main output, whereas the post regulator sets  $D_{MA}$  independently by its own local feedback to regulate the output voltage from the magnetic amplifier.

Figure 7. Typical Primary Current Waveforms for a Converter Without Magnetic Amplifier (a) and with a Mag Amp (b).

The computation is simply the reflection of peak currents in the secondary circuits by the ideal turns ratios of the transformer. Using the principle that the sum of the ampere turns for an ideal transformer is zero, the instantaneous primary current for a transformer with W secondary windings is just

$$I_{P} = \frac{1}{n_{P}} \sum_{j=1}^{W} i_{j} n_{j}$$

(14)

where  $i_j$  is the current in the secondary winding with turns ratio  $n_j$ . Thus, for a transformer with three secondary windings, the primary current would be the sum  $i_1n_1+i_2n_2+i_3n_3$  divided by the turns ratio of the primary. Note that since all turns ratios are defined with respect to the main output winding, the turns ratio of the main output winding is 1. Equation (14) may also be used with the actual number of primary turns  $N_p$  substituted for the turns ratio  $n_p$ , and the actual secondary turns  $N_i$  substituted for the turns ratios  $n_i$ .

This estimate does not include the effect of magnetizing current in the transformer, which will be determined after the transformer is designed. The magnetization current will raise the peak value of this estimate by typically less than 10% worst case.

The computation in *PI Expert* includes the ripple current in the output inductors to find the peak primary current. Ripple current is ignored to calculate the RMS value. The resulting error in the RMS current is less than 1% for practical values of

inductance and current. The RMS current is computed at the duty ratio that corresponds to  $V_{\text{ACMIN}}$  because worst case steady-state resistive losses occur at that operating point.

### Step 5. Choose the appropriate *TOPSwitch-GX* device.

Select a *TOPSwitch-GX* according to the requirements for peak primary current and acceptable power dissipation. For operation of the converter in continuous conduction mode it is recommended to operate the device at no more than 80% of its current limit for ordinary thermal design. To reduce device dissipation it is possible to use a *TOPSwitch-GX* device that has a lower  $R_{DS(ON)}$  when the current limit is adjusted accordingly. Lowering  $I_{LIMIT}$  externally (using a programming resistor to the X pin), takes advantage of the lower  $R_{DS(ON)}$  of the larger device while maintaining the same level of overload protection.

The external current limit reduction factor is

$$K_I = \frac{\text{External Current Limit}}{\text{Data Sheet Current Limit}}$$

(15)

where  $0.4 \le K_1 \le 1.0$ , and is set by the value of a resistor connected between the X pin and SOURCE pin. Refer to the *TOPSwitch-GX* data sheet for details.

With external current limit reduction, the actual (external) current limit is

$$I_{XLIMIT} = I_{LIMIT} K_I \tag{16}$$

Remember to check the maximum and minimum tolerance on  $I_{\text{LIMIT}}$  from the data sheet for the selected device. Allow margin to guarantee that the peak primary current  $I_{\text{pp}}$  is less than the minimum value of  $I_{\text{XLIMIT}}$  at high temperature. With minimum device  $I_{\text{LIMIT}}$ , check that

$$\begin{split} I_{PP} &\leq 0.96 \; I_{LIMIT} \text{for} \; K_I = 1 \\ I_{PP} &\leq 0.86 \; I_{XIJMIT} \text{for} \; K_I < 1 \end{split} \tag{17}$$

Adjust the system specifications if the peak current is too high for the largest device. While some specifications are fixed, others are adjustable at the discretion of the designer. Raising the minimum input voltage will give lower peak current.

### Step 6. Design the transformer.

The transformer design can be either completed in-house or delegated to a qualified supplier of custom magnetics. An outside supplier needs to know the turns ratios and the recommended restrictions on flux density to start a design. Even if the ultimate design will be done outside, it is beneficial to do a rough design in-house. A proposed design with actual numbers of turns on each winding will reduce the time required to obtain a satisfactory transformer.

The maximum recommended flux density for this application is

$$B_{PEAK} \le 0.3 \text{ tesla (3000 gauss)}$$

(18)

and the recommended maximum change in flux density per switching period (AC flux density) is

$$B_M \le 0.2 \text{ tesla (2000 gauss)} \tag{19}$$

The constraint on  $B_M$  sets the minimum number of turns for a particular core, while the limit on  $B_{PEAK}$  restricts the maximum transient duty ratio. Although peak flux density under steady-state conditions can be calculated, the designer should allow sufficient margin to avoid saturation under transient conditions.

To start the design, select a core that is likely to meet the size and efficiency requirements of the application. Since the voltages and turns ratios are determined, all that remains is to find the actual number of turns and the size of wire for each winding.

Compute the minimum turns for the main output.

$$N_{MAIN} \ge \frac{V_{MAIN} + V_{DMAINF}}{B_M A_e f_s} \tag{20}$$

where  $A_e$  is the effective area of the core. Units in the above expression are volts, tesla, meter<sup>2</sup> and hertz. Round  $N_{MAIN}$  upward to the next integer value.

Compute the turns for the other power windings.

$$N_{P} = n_{P} N_{MAIN}$$

$$N_{AUX} = n_{AUX} N_{MAIN}$$

$$N_{IND} = n_{IND} N_{MAIN}$$

(21)

Round  $N_{_{\rm P}}$  downward to the next integer. Round  $N_{_{\rm AUX}}$  and  $N_{_{\rm IND}}$  to the nearest integer.

Compute the turns for the bias winding.

$$N_B = N_P \left( \frac{8 \text{ volts} + V_{DB}}{V_{DROPOUT}} \right)$$

(22)

Round N<sub>B</sub> upward to the nearest integer value.

Designers should use copper foil instead of wire for windings of few turns that carry high current. It is very important to the success of the design to minimize leakage inductance.

Compute an estimate of the peak magnetizing current.

The primary inductance in henries is

$$L_P = \frac{\mu_0 A_e N_P^2}{\frac{\ell_e}{\mu_r} + \ell_g} \tag{23}$$

where  $\mu_0$  is the permeability of free space,  $A_e$  is the effective area,  $\ell_e$  is the effective path length in the core and  $\ell_g$  is the length of the air gap (see Zero Gap Transformer section). The dimensionless relative permeability  $\mu_e$  is given by

$$\mu_r = \frac{A_L \ell_e}{400\pi A_e} \tag{24}$$

Units in the above two expressions are the SI basic units with the exception of inductance coefficient  $A_L$ , which has the conventional units of  $nH/turn^2$ .

With no gap, the primary inductance in henries is simply

$$L_{P|NO\;GAP} = A_L N_P^2 \times 10^{-9} \tag{25}$$

Now the peak magnetizing current is given by

$$I_{MP} = \frac{V_{MIN}D_{MAX}}{L_{P}f_{S}} \tag{26}$$

Units in the above expression are amperes, volts, henries and hertz. The magnetizing current should be less than 10% of the primary current for reasonable power dissipation in the clamp circuit.

Estimate the power lost in the core from the manufacturer's data on the core material, operating frequency and  $B_{\rm M}$ . Copper losses may be estimated from the resistance and RMS current in each winding. If the estimates indicate excessive loss, repeat the design with a larger core.

### **Zero Gap Transformers**

For highest efficiency in this application with the simple Zener clamp circuit, it is recommended that the transformer core have no air gap. While an air gap reduces the remnant flux density and stabilizes the primary inductance, it increases the stored energy that must be processed by the clamp circuit.

With the use of a suitable reset scheme, transformer saturation is not a problem in the absence of an air gap. Using this methodology and the recommended clamp scheme, the design restricts peak flux density and the clamp circuit produces negative magnetizing current during reset.

The negative magnetizing current during reset prevents flux build-up in the transformer during successive switching periods. Even with no intentional gap in the transformer core, mechanical imperfections will always give a finite effective gap (when calculating with *PI Expert* a value of 0.02 mm is used). If an air gap is desired for other reasons, it should be as small as possible.

#### Step 7. Check primary current.

Use the actual number of turns from the design of the transformer to compute the peak and RMS current on the primary. Primary current was estimated in Step 4 with an ideal turns ratio before the transformer was designed. Add the peak of the magnetizing current to obtain actual peak of the primary current under steady-state conditions.

Designers should be aware that the primary current observed on prototype hardware may be lower than predicted because the circuit that resets the flux in the transformer allows a negative average magnetizing current, as mentioned previously in Step 6 in the section on Zero Gap Transformers. The design, however, must allow for conditions when the magnetizing current adds to the reflected secondary currents.

### Step 8. Determine the input capacitance for holdup time.

The holdup time must be specified at a minimum voltage  $V_{\text{HOLDUP}}$ . This is often, but not always  $V_{\text{MIN}}$ . For maximum flexibility, this methodology allows the designer to determine the value of input capacitance required to obtain a given holdup time from an arbitrary input voltage.

If a DC voltage is specified to mark the beginning of the holdup time, the minimum required input capacitance is

$$C_{IN} \ge \frac{2P_O t_H}{\eta_{DC} \left(V_{HOLDUP}^2 - V_{DROPOUT}^2\right)} \tag{27}$$

where  $P_{_{O}}$  is the total output power that corresponds to the efficiency at the DC bus,  $\eta_{_{DC}}$  and  $t_{_{H}}$  is the holdup time.

If an AC voltage  $V_{\text{ACHOLDUP}}$  is specified to mark the beginning of the holdup time, the minimum required input capacitance (no doubler) is

$$C_{IN} \ge \frac{2P_O}{\eta_{DC}} \left( \frac{2(t_H - t_C) + \frac{1}{f_L}}{2V_{ACHOLDUP}^2 - V_{DROPOUT}^2} \right)$$

(28)

where  $t_c$  is the conduction time of the AC input rectifiers and  $f_L$  is the frequency of the AC power line. Again, note that  $t_c$  will increase significantly if the design has passive PFC.

The efficiency  $\eta_{DC}$  excludes losses in the AC input circuit and EMI filter. No power is dissipated in the AC input circuit during the holdup time because the AC input is disconnected. The lower system efficiency  $\eta$  that includes the AC input losses would give a value of  $C_{IN}$  that is larger than required.

Compare the value from Equation (27) or (28) with the estimate for  $C_{\rm IN}$  in Step 1. Adjust  $C_{\rm IN}$  in Step 1 and repeat the calculations until the computed value is approximately the same as in Step 1.

### Step 9. Calculate stress on rectifiers.

*PI Expert* calculates voltage and current stress on rectifiers for guidance in selection of appropriate components. The recommended derating factor for peak inverse voltage is 80%. Derating for the currents is generally not necessary.

Thus, the recommended voltage rating for the input bridge rectifier is

$$V_{PIVAC} = 1.25\sqrt{2}V_{ACMAX} \tag{29}$$

Current ratings for rectifiers are average values, not RMS. The current rating for the bridge rectifier is computed from

$$I_{DAVBR} = \frac{P_O}{\eta_{DC} V_{UL}} \tag{30}$$

where  $V_{LL}$  is the average DC bus voltage at the lowest steady-state line voltage (no doubler).

$$V_{LL} = \frac{\sqrt{2}}{2} \left[ V_{ACMIN} + \sqrt{V_{ACMIN}^2 - \frac{P_O\left(\frac{1}{2f_L} - t_C\right)}{\eta_{DC}C_{IN}}} \right]$$

(31)

Calculations of the peak inverse voltage on the output rectifiers use  $V_{\text{MAX}}$ ,  $V_{\text{DSOP}}$ , and the output voltages with the turns on the transformer windings.

Calculations of worst case average current in the catch diodes are with the duty ratio that corresponds to the maximum input voltage. A very good approximation to the average rectifier current is then just the output current. Current in the forward diodes is computed with  $D_{MAX}$ . Note that with DC stacked outputs, the rectifiers on the main output must conduct the sum of the currents of the main and auxiliary outputs.

In general, the stress will be different for the forward diode and the catch diode on the same output. Designers will have to consider the one with the greater stress when choosing components that contain both diodes in the same package.

### Step 10. Calculate RMS ripple currents in output capacitors.

Currents in the output capacitors are computed at the maximum loads. In continuous conduction mode, the RMS ripple current is given by

$$I_{RMS} = \frac{K_{\Lambda l} I_{OUTPUT}}{2\sqrt{3}} \tag{32}$$

where  $K_{AI}$  is for the particular output under consideration. This expression is reliable for independent outputs and for a main output with no coupled inductors. For converters with auxiliary outputs, Equation (32) is only an estimate. Ripple currents in the individual windings of coupled inductors depend on magnetic coupling coefficients, parasitic voltage drops, and other quantities in the circuit that are difficult to predict. Therefore, designers must evaluate prototype hardware on the bench to confirm that the assumptions of the design are valid for a particular application.

### Step 11. Calculate parameters for the coupled inductor.

The coupled inductor allows the auxiliary outputs to have better regulation than independent outputs, with the penalty of increased complexity of the inductor.

PI Expert allows two options for the topology of the auxiliary output. The auxiliary output may be referenced to the main output voltage for the best regulation or to output return when necessary. The reference must be at output return to obtain a negative auxiliary output with a positive main output.

Turns ratios for the coupled inductor are the same as the ratios for the transformer. The turns ratio of a coupled inductor for a converter that has one auxiliary output is, in terms of the actual number of turns,

$$\frac{N_{LMAIN}}{N_{LAUX}} = \frac{N_{MAIN}}{N_{AUX}} \tag{33}$$

Inductance is computed for the winding that is on the main

output. The computation is based on  $K_{\Lambda I}$ , which considers the total ampere turns of the coupled inductor, not just the current in one winding. The inductance of the winding for the main output, valid for only the DC stacked configuration, is

$$L_{MAIN} = \frac{V_{MAIN} + V_{DMAINC}}{K_{\Delta I0} \left(I_{MAIN} + I_{AUX} \left(\frac{N_{LAUX}}{N_{LMAIN}} + 1\right)\right) f_S}$$

(34)

PI Expert gives the designer the turns ratio, the total ampere turns, and the peak energy stored in the inductor. The designer has the option to change these parameters by adjustment of the  $K_{AI}$  for each inductor.

These quantities assist the designer to obtain an appropriate inductor of either his own design or one from a qualified supplier. Bench evaluation of the prototype will determine if fine adjustment of the turns is necessary in the final configuration.

### Step 12. Calculate inductance for independent outputs.

Calculation of the inductance for independent outputs is straightforward and similar to the computation of the parameters for the coupled inductor. Design of the component is simplified because there is no turns ratio associated with an inductor that has only one winding. PI Expert computes the inductance and the peak stored energy. This information is useful for selection of magnetic cores from catalogs.

### Step 13. Calculate output inductance for the magnetic amplifier.

PI Expert computes the output inductor for a magnetic amplifier post regulator in the same way as for an independent output. It does not address the magnetic switching element.

### Step 14. Adjust output inductors if necessary.

The designer may modify the K<sub>M</sub> of any inductor to accommodate special requirements. If the value or the estimated physical size of the computed inductor is not satisfactory, adjust the individual  $K_{AI}$  to achieve the desired result.

### Step 15. Calculate component values for external reduction

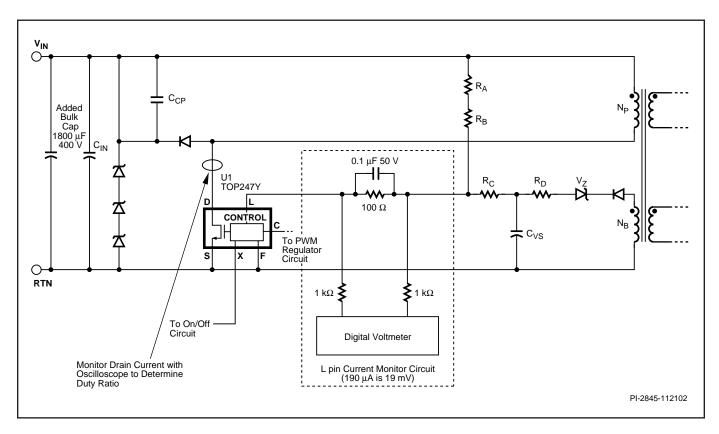

The maximum duty ratio ( $DC_{MAX}$ ) of *TOPSwitch-GX* must be restricted to avoid saturation of the transformer during transient loading. A network of four resistors and a capacitor  $(R_A, R_B, R_C,$  $V_z$ ,  $R_D$  and  $C_{vs}$  in Figure 1 and Figure 1 of Appendix B) determines a variable upper limit on the duty ratio. Adjustment of the maximum duty ratio with input voltage allows enough deviation beyond the steady-state operating point to respond to transients while maintaining enough time in every switching cycle for the transformer to reset.

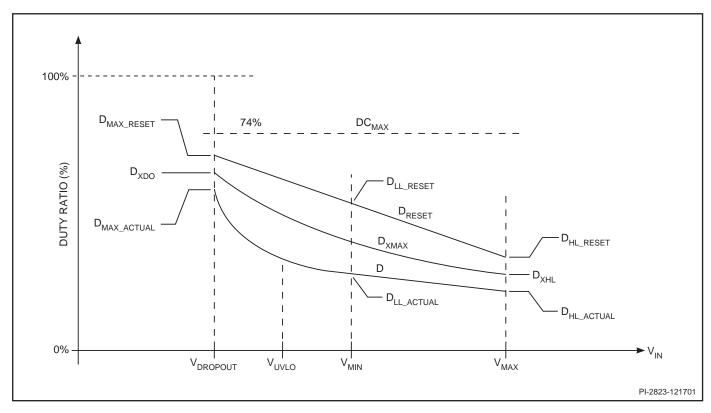

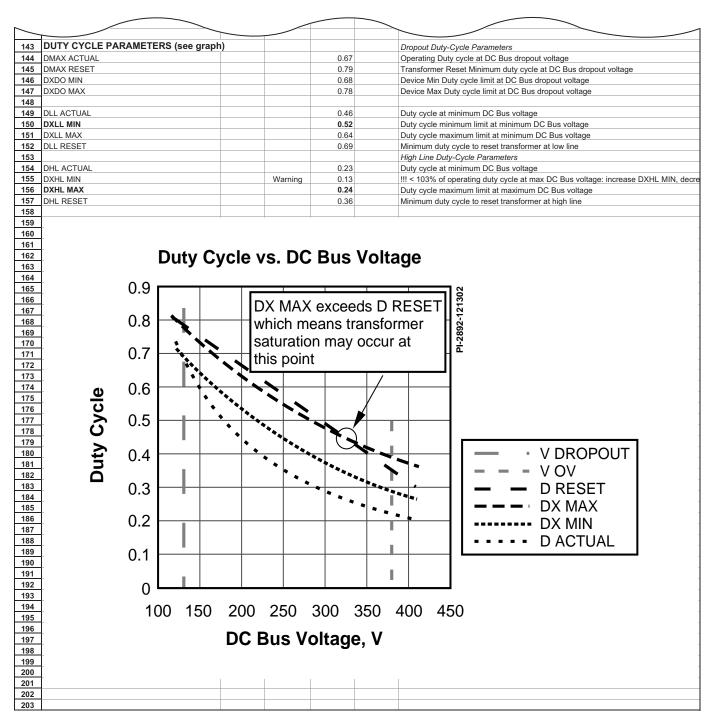

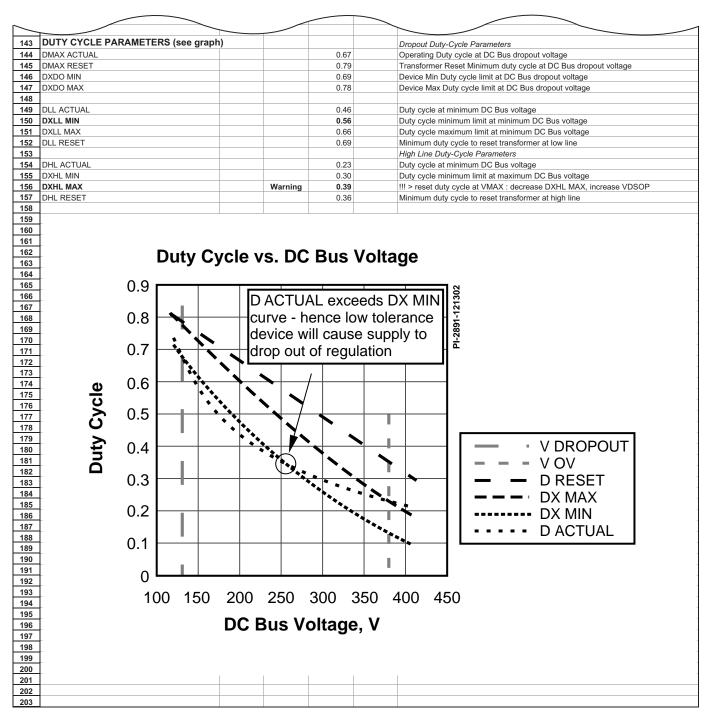

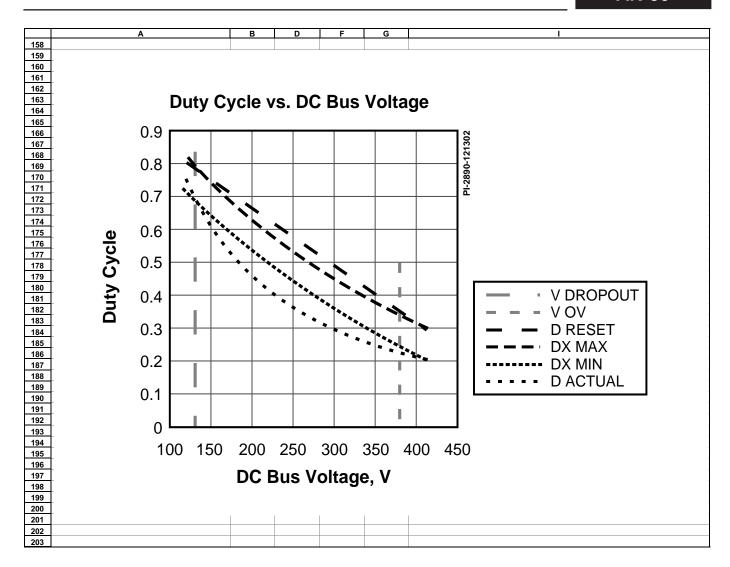

Figure 8. Boundaries of Voltages and Duty Ratio Related to the Selection of  $R_A$ ,  $R_B$ ,  $R_C$  and  $R_D$  with  $C_{VS}$  in Figure 1.

The resistor network also sets the threshold for line undervoltage lockout. Protection from over-voltage is generally not a concern for this topology since it uses a Zener clamp to provide a hard limit on the drain-to-source voltage.

The resistors are matched to the capacitor to form an integrator with an appropriate time constant to give a cycle-by-cycle duty ratio limit. The integration of the voltage on the bias winding gives the external duty ratio limit a desirable relationship to the flux in the transformer. The circuit adjusts the duty ratio limit to set an upper bound on the volt-second product, and to balance the volt-second product during *TOPSwitch-GX* on and off times. The dynamic nature of the circuit allows greater freedom and precision in the design without interference from the line over-voltage threshold limit.

Figure 1 shows the locations of resistors  $R_A$ ,  $R_B$ ,  $R_C$  and  $R_D$  with capacitor  $C_{VS}$ . Several important quantities related to their values are illustrated in Figure 8. The broken vertical lines in Figure 8 mark the boundaries of the DC bus voltage for minimum and maximum operating voltages, the line undervoltage lockout threshold, and the lowest input voltage that will guarantee regulation of the output.

The broken horizontal line shows the maximum guaranteed duty cycle of *TOPSwitch-GX*. A value of 74% is recommended for design.

The lowest curve is the duty ratio D that corresponds to steady-state operation at a given input voltage. The straight line with negative slope is the maximum duty ratio  $D_{\text{RESET}}$  that will still guarantee reset of the transformer for a given  $V_{\text{DSOP}}$ . The converter must always operate with D less than  $D_{\text{RESET}}$  to avoid saturation of the transformer. The curved line between the D and  $D_{\text{RESET}}$  lines is the external duty ratio limit  $D_{\text{XMAX}}$  that is set by the resistors.

The designer must choose the components to set the curve of  $D_{xmax}$  at a desired position between the boundaries of  $D_{reset}$  and D for a given set of specified voltages.

*PI-Expert* prompts the user to enter several parameters that are important to the computation of the resistor values. Some parameters are from the *TOPSwitch-GX* data sheet while others are design choices. The software suggests default and typical values. The designer can enter maximum and minimum values to check worst case situations.

The components are calculated to satisfy the constraints of four parameters:  $D_{XDO}$  (external duty ratio limit at  $V_{DROPOUT}$ ),  $D_{XHL}$  (external duty ratio limit at  $V_{MAX}$ ),  $V_{UVLO}$  (input voltage where the TOPSwitch-GX starts switching), and the maximum transient input voltage  $V_{OV}$  that is greater than  $V_{MAX}$ .

While there are four resistors, only three are unknown because  $R_{_{\rm A}}$  and  $R_{_{\rm B}}$  are identical by definition. They are connected in series to keep the voltage across each one below its maximum rating. The three unknown resistors and one capacitor make four unknown quantities that are determined by the four constraints.

Figure 8 illustrates the general case where  $D_{\text{XDO}}$  is between the actual duty ratio  $D_{MAX\_ACTUAL}$  and  $D_{MAX\_RESET}$  at the input voltage  $V_{DROPOUT}$ . If the converter is not required to respond to transient loads at the end of the holdup time,  $D_{XDO}$  and  $D_{MAX\_ACTUAL}$  can be set to  $D_{MAX\_RESET}$ . Since response to transient loads is usually required at  $V_{MAX}$ , the designer will want to set  $D_{XHL}$  at a comfortable margin between  $\boldsymbol{D}_{\text{HL ACTUAL}}$  and  $\boldsymbol{D}_{\text{HL\_RESET}}$

Begin with the computation of values for  $R_A$  and  $R_B$  to set the line under-voltage threshold  $V_{\text{\tiny ACUV}}$ .

$$R_A = R_B = \frac{V_{ACUV}\sqrt{2}}{2I_{UV}} \tag{35}$$

where  $V_{ACUV}$  is the AC input voltage (non-doubled) required for the converter to start, and  $\boldsymbol{I}_{\text{UV}}$  is the line under-voltage threshold current of the L pin of TOPSwitch-GX from the datasheet. Choose the nearest standard resistor value for  $R_A$  and  $R_B$ .

Define intermediate variables to make the expressions easier to write and interpret.

$$m_{IL} = \frac{D_{IL1} - D_{IL2}}{I_{L2} - I_{L1}} \tag{36}$$

$$I_{LD0} = \frac{D_{IL}}{m_{IL}} + I_L \tag{37}$$

$$R_{AB} \equiv R_A + R_B \tag{38}$$

$$V_{BZL} \equiv V_{DB} + V_Z + V_L \tag{39}$$

In Equation (36),  $D_{IL1}$  and  $D_{IL2}$  are respectively the values of  $DC_{MAX}$  at currents  $I_{L1}$  and  $I_{L2}$  into the L pin. Obtain these values from the data sheet. Use the typical values at first. Then check that the circuit will perform properly at the high and low ends of the tolerance range.

In Equation (37),  $D_{IL}$  is the value of  $DC_{MAX}$  at current  $I_{L}$  into the L pin. Use the same  $D_{_{\rm IL1}}$  with  $I_{_{\rm L1}}$  or  $D_{_{\rm IL2}}$  with  $I_{_{\rm L2}}$  as in Equation (36). Either pair will give the same result.  $I_{1,00}$  has a physical interpretation that cannot be realized: if the duty ratio reduction characteristic continued along its linear slope, it would reach zero at the current I<sub>1 po</sub>.

The voltages  $V_{DB}$ ,  $V_{Z}$  and  $V_{L}$  are respectively the forward drop of the rectifier in series with the Zener diode and R<sub>c</sub>, the Zener

voltage, and the voltage on the L pin as shown in Figure 1. The Zener diode is chosen as required to raise the curve of  $D_{x_{MAX}}$  at the low input voltages. It may not be necessary in all applications. The Zener voltage is 6.8 V in this example.

Next, select a value for  $D_{XHL}$  that is between  $D_{HL\ ACTUAL}$  and

$$D_{HL\_ACTUAL} = \frac{V_{MAIN} + V_{DMAINC}}{\left(V_{MAX} - V_{DS}\right) \frac{N_S}{N_P} - V_{DMAINF} + V_{DMAINC}}$$

$$(40)$$

$$D_{HL\_RESET} = 1 - \frac{V_{MAX}}{V_{DSOP}} \tag{41}$$

Find the range of permissible values for  $D_{XDO}$ . To compute the upper and lower bounds on  $D_{XDO}$ , define the intermediate variable K<sub>xDO</sub>

$$K_{XDO} = m_{IL} \left( I_{LD0} - \frac{V_{MAX}}{R_{AB}} - \frac{D_{XHL}}{m_{IL}} \right) \left( \frac{V_{DROPOUT} \frac{N_B}{N_P} - V_{BZL}}{V_{MAX} \frac{N_B}{N_P} - V_{BZL}} \right)$$

$$(42)$$

The upper bound for  $D_{xxx}$  is then

$$D_{XDO} < m_{IL} \left( I_{LD0} - \frac{V_{DROPOUT}}{R_{AB}} \right) - K_{XDO} \tag{43}$$

and the lower bound for  $\boldsymbol{D}_{\boldsymbol{X}\boldsymbol{D}\boldsymbol{O}}$  is

$$D_{XDO} > \frac{m_{IL} \left(I_{LD0} - \frac{V_{DROPOUT}}{R_{AB}}\right)}{1 + \frac{K_{XDO}}{D_{XHL}}}$$

(44)

Choose an appropriate value for  $\boldsymbol{D}_{\text{XDO}}$  between  $\boldsymbol{D}_{\text{MAX\_RESET}}$  and  $D_{MAX\ ACTUAL}$  that also satisfies the boundaries of (43) and (44).

Next, compute the intermediate constants  $r_1$  and  $r_2$ .

$$r_{1} = \frac{\left(V_{DROPOUT} \frac{N_{B}}{N_{P}} - V_{BZL}\right) D_{XDO}}{I_{LDO} - \frac{V_{DROPOUT}}{R_{AR}} - \frac{D_{XDO}}{m_{II}}}$$

(45)

Figure 9. External Under-Voltage Lockout Circuit.

$$r_{2} = \frac{\left(V_{MAX} \frac{N_{B}}{N_{P}} - V_{BZL}\right) D_{XHL}}{I_{LD0} - \frac{V_{MAX}}{R_{AB}} - \frac{D_{XHL}}{m_{II}}}$$

(46)

Compute the values for the resistors  $R_p$  and  $R_c$ .

$$R_D = \frac{r_1 - r_2}{D_{XDO} - D_{XHL}} \tag{47}$$

$$R_C = r_1 - D_{XDO} R_D \tag{48}$$

Select the nearest standard resistor values for  $R_{C}$  and  $R_{D}$ .

Verify that the parameters are within the desired range with the actual component values.

$$V_{ACUV} = \frac{I_{UV}}{\sqrt{2}} \left( R_A + R_B \right) \tag{49}$$

This is the AC input voltage (non-doubled) where the converter will begin to operate.

The external duty ratio limit at any DC bus voltage  $V_{\rm IN}$  may be computed from the expression

$$D_{MAX} = \frac{v_B + \sqrt{v_B^2 + 4v_A v_C}}{2v_A}$$

(50)

where

$$v_A = \frac{R_D}{m_{IL}} \tag{51}$$

$$v_{B} = V_{BZL} + I_{LD0}R_{D} - \frac{R_{C}}{m_{IL}} - V_{IN} \left( \frac{R_{D}}{R_{AB}} + \frac{N_{B}}{N_{P}} \right)$$

(52)

$$v_C = R_C \left( I_{LD0} - \frac{V_{IN}}{R_{AR}} \right)$$

(53)

Now choose an appropriate value for the capacitor. Proper choice of the capacitor allows the converter to operate safely with transient input voltages greater than  $V_{\text{MAX}}$ . The line overvoltage feature of TOPSwitch-GX is not used in the conventional fashion in this application. The circuit operates in an over-voltage mode that reduces the maximum duty ratio further by reduction of the switching frequency. The value of the capacitor  $C_{\text{VS}}$  is chosen to give the desired behavior in the over-voltage mode.

Select an input voltage  $V_{\rm OV}$  greater than  $V_{\rm MAX}$  that marks the onset of over-voltage operation. Then compute the maximum duty ratio  $D_{\rm XOV}$  that corresponds to the specification in the TOPSwitch-GX data sheet for the Line Over-Voltage Threshold Current  $I_{\rm COV}$ .

$$D_{XOV} = D_{IL} - m_{IL} (I_{OV} - I_L)$$

(54)

Here  $D_{IL}$ ,  $m_{IL}$  and  $I_{L}$  are the same as in Equations (36) and (37).

Finally, compute the capacitor value as

$$C_{VS} = \frac{\left(I_{OV} - \frac{V_{OV}}{R_{AB}}\right) \left((1 - D_{XOV})T_S - t_{R(ON)}\right)}{K_{OVHYS}I_{OVHYS}R_D}$$

(55)

where

$T_s$  is the switching period  $1/f_s$  in normal operation  $t_{R(ON)}$  is the Remote ON Delay  $I_{OVHYS}$  is the hysteresis of the IOV threshold  $K_{OVHYS}$  is a constant selected by the designer.

The first three parameters are taken from the data sheet. The constant  $K_{\text{OVHYS}}$  is selected to provide sufficient ripple voltage

on the capacitor for reliable operation of the circuit. The recommended range for  $K_{OVHYS}$  is 3 to 5. Choose the nearest standard value for capacitor C<sub>vs</sub>.

These expressions to compute the component values have been simplified for ease of presentation. Some variables related to parasitic elements have been ignored.

If any of the results are not satisfactory, choose different standard values for the resistors or a different voltage for the Zener diode. Gross deviations from the desired results may require different values for the parameters chosen at the beginning of this step, since some sets of parameters may not be compatible.

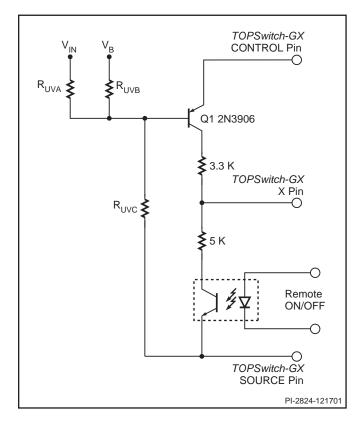

### Step 16. Calculate values for resistors in optional external under-voltage lockout circuit.

The resistor network that determines the characteristics of the external duty ratio limit sets the minimum voltage where the converter begins to operate. The contributions of current from the bias voltage create too much hysteresis for the circuit to be useful as an under-voltage detector after the converter begins to operate. Therefore, the external under-voltage circuit in Figure 9 is recommended for applications where a positive turnoff threshold is desired.

Choose a value  $V_{\text{ACUVL}}$  for the turn-off threshold and a value  $V_{\text{ACUVL}}$  that is approximately midway between  $V_{\text{ACUVL}}$  and

$$V_{ACUVL} < V_{ACUVX} < V_{ACUV} \tag{56}$$

The corresponding DC bus voltages (non-doubled) are

$$V_{UVX} = V_{ACUV} \sqrt{2} \tag{57}$$

$$V_{UVX} = V_{ACUVX} \sqrt{2}$$

(58)

$$V_{UVL} = \sqrt{2V_{ACUVL}^2 - \frac{2P_o\left(\frac{1}{2f_L} - t_C\right)}{\eta_{DC} C_{IN}}}$$

(59)

Define the intermediate variable v<sub>1</sub> that considers the voltage V<sub>C(SHUNT)</sub> on the CONTROL pin and the base-emitter voltage on the transistor.

$$v_1 = V_{C(SHUNT)} - V_{BEQ1} \tag{60}$$

Compute the approximate value of R<sub>UVA</sub> to meet the constraint of maximum power dissipation. Assume a 50% derating for a

Figure 10. Recommended Clamp Circuit.

resistor that can dissipate P<sub>PLIVA</sub> watts.

$$R_{UVA} = \frac{2V_{MAX}^2}{P_{RUVA}} \tag{61}$$

A typical resistor for this purpose will have a power rating of  $P_{RIIVA} = 125$  mW. Choose the nearest standard value for  $R_{IIVA}$ .

Then compute  $R_{UVB}$  and  $R_{UVC}$ .

$$R_{UVB} = R_{UVA} \left( \frac{N_B}{N_P} V_{UVL} - v_1 \over V_{UVX} - V_{UVL} \right)$$

(62)

$$R_{UVC} = R_{UVA} \left( \frac{v_1}{V_{UVX}} \right) \tag{63}$$

Choose the nearest standard values for  $R_{\text{\tiny LIVR}}$  and  $R_{\text{\tiny LIVC}}$ . Then check  $V_{ACUVL}$  and  $V_{ACUVX}$  with the actual resistor values.

Figure 11. General Configuration of Feedback Circuit for Forward Converter with TOPSwitch-GX.

$$V_{UVL} = \frac{v_1 \left(\frac{R_{UVB}}{R_{UVC}} + 1\right)}{\frac{R_{UVB}}{R_{UVA}} + \frac{N_B}{N_P}}$$

(64)

$$V_{ACUVL} = \sqrt{\frac{V_{UVL}^{2}}{2} + \frac{P_{O}\left(\frac{1}{2f_{L}} - t_{C}\right)}{\eta_{DC} C_{IN}}}$$

(65)

$$V_{ACUVX} = \frac{v_1}{\sqrt{2}} \left( 1 + \frac{R_{UVA}}{R_{UVC}} \right) \tag{66}$$

If  $\boldsymbol{V}_{\text{\tiny ACUVL}}$  and  $\boldsymbol{V}_{\text{\tiny ACUVX}}$  are not satisfactory, adjust the values of the resistors.

### Step 17. Choose components for the clamp circuit.

Figure 10 shows connections for the elements of a Zener clamp circuit that is suitable for many applications. Capacitor  $C_{\rm CP}$ , diode D1 and the string of Zener diodes are on the primary side of the transformer. Resistor  $R_{\rm CS}$  and capacitor  $C_{\rm CS}$  are on the secondary side of the transformer.

This arrangement limits the voltage on the drain of the *TOPSwitch-GX* to approximately the sum of the voltages of the string of Zener diodes. It also recovers most of the energy from leakage inductance and magnetization inductance, and returns it to the input or delivers it to the output.

Select the Zener diodes to limit the drain voltage to  $V_{\text{DSOP}}$ . Choose the voltage, size and number of diodes in the string to achieve the desired  $V_{\text{DSOP}}$  and to handle the power dissipation. This arrangement is adequate for applications where the clamp circuit dissipates less than 5 W.

Capacitor  $C_{CP}$  supplements the natural stray capacitance on the drain node to absorb energy that comes mostly from the leakage inductance. The value must be selected empirically because it is difficult to predict natural stray capacitance and leakage inductance accurately enough to calculate a proper value. Energy not absorbed by the capacitance will be dissipated in the Zener string, so  $C_{CP}$  cannot be too small. If  $C_{CP}$  is too large, its voltage will change too slowly to allow the transformer to reset during transients. Typical values for  $C_{CP}$  are in the neighborhood of 2 nF.

Diode D1 must be a slow recovery type such as a 1N5407. The recovery of D1 removes enough charge from  $C_{\rm CP}$  to stabilize its voltage and to discharge some of its stored energy into the primary of the transformer. This energy returns to the input on the next switching cycle.

The remaining components are connected across the forward diode on the main output. Energy from leakage inductance on the secondary and magnetization inductance of the transformer charges  $C_{\rm CS}$  when the TOPSwitch-GX turns off. The energy from  $C_{\rm CS}$  is delivered to the output during the next switching cycle. Resistor  $R_{\rm CS}$  provides damping for oscillations that would otherwise occur from the resonance of  $C_{\rm CS}$  with stray inductance.

Typical values are in the neighborhood of 0.1  $\mu$ F for  $C_{cs}$  and 1  $\Omega$  for  $R_{cs}$ . The resistor must dissipate power that corresponds to the charge and discharge of  $C_{cs}$  each cycle. It typically will dissipate less than 1 watt. Proper values must be determined empirically from evaluation of prototype hardware.

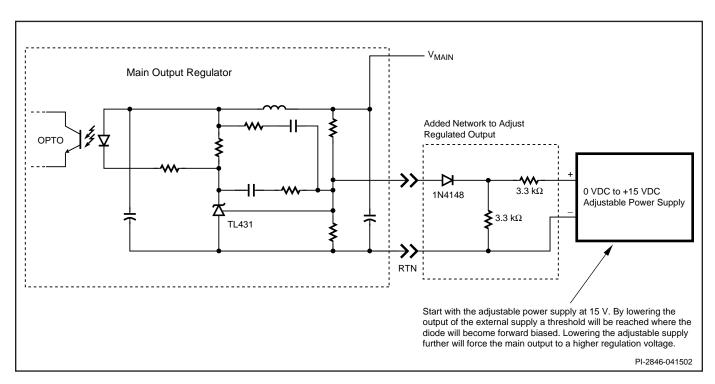

### Step 18. Choose components for the feedback circuit.

The pulse width modulator in *TOPSwitch-GX* sets the duty ratio according to the current into the CONTROL pin. *TOPSwitch-GX* senses the drain current for protection only, and does not use it for control purposes. Thus, forward converters with *TOPSwitch-GX* operate with a voltage-mode control that modulates the converter's duty ratio directly according to an error signal from the regulated output voltage. Voltage mode control provides sufficient loop bandwidth and is fully able to meet all the specifications for PC Main and other high power applications.

The general configuration of the feedback circuit for a forward converter with TOPSwitch-GX is illustrated in Figure 11. It shows a typical connection of a TL431 voltage regulator with an optocoupler and components for frequency compensation. There is an optional connection to  $V_{AUX}$  to improve the regulation of the auxiliary output by sharing regulation with the main output. This general technique is common in all types of multiple output regulators.

While the design of the feedback loop is beyond the scope of this application note, it is useful to consider the general circuit of Figure 11. The components are chosen to provide regulation of output voltages and to shape the frequency characteristics of the control loop. Proper design of the feedback components is important not only for the stability of the system, but also for transient response of the output.

Inductor  $L_{\scriptscriptstyle F}$  with capacitor  $C_{\scriptscriptstyle F}$  reduces high frequency noise on the main output. As such, it introduces phase shift in the small signal response that would make loop compensation difficult if the only feedback for the main output were taken from the voltage on  $C_{\scriptscriptstyle F}$ . To avoid difficulties with the feedback loop, information about the main output is taken from two places.

Low frequency information that is most important to the DC regulation comes mainly through the path formed by resistor divider of R5, R6 and R7. The voltage on R7 is the reference

voltage of the TL431 when  $V_{\text{MAIN}}$  and  $V_{\text{AUX}}$  are at their desired values.

High frequency information that is most important in the transient response comes through the path formed by the optocoupler's diode and R2. This same technique is commonly used with *TOPSwitch-GX* in flyback converter applications.

The values of R1, R3, R4, C1 and C2 are chosen to shape the frequency response. The choices are influenced by the components on the CONTROL pin and equivalent series resistance of the output capacitor, which can be important features of the loop gain. Designers must make proper measurements of loop gain and transient response on prototype hardware to confirm that the converter performs as desired under all specified conditions.

### **Evaluation of Prototype Hardware**

The design that results from the steps of the previous section contains the uncertainties of the initial assumptions. Performance must be validated with measurements on prototype hardware before the design is complete.

At this stage in the procedure, the designer will have enough information to build a circuit that will operate at nominal conditions for evaluation on the bench. The designer must test the circuit at all the limits of specified performance. Measurements will indicate which changes to the original assumptions are necessary. A successful design is obtained after repetition of the procedure with parameters adjusted from measurements on the hardware.

The evaluation should include observation of the drain-to-source voltage on *TOPSwitch-GX* under steady state operation and transient conditions. Apply power to the converter slowly with minimum loads. Then exercise the loads on the outputs in different combinations, first at the nominal input voltage and then at the extremes of input voltage.

Observe the behavior at various static loads before going to transient loading. Check for excessive power dissipation in the clamp circuit. A useful technique is to monitor the average current in the string of Zener diodes in the clamp circuit with a low value resistor in series. A capacitor in parallel with the resistor will develop a voltage proportional to the average current through the diodes. The product of this voltage and the clamp voltage gives an indication of the power dissipation in the Zener diodes.

Monitor the drain current when the output has steady-state overload and during transient loading. The waveform will provide important information about the operation of the converter and the limits of the design. Check that the current

limit of the *TOPSwitch-GX* is sufficient for all the specified conditions.

Check that the transformer does not saturate under all steadystate combinations of line and load. Verify the proper design of the circuit to limit maximum duty ratio with the procedure in Appendix B.

Check the ripple on all the output voltages with several combinations of input voltage and output loading, particularly if the design uses a coupled inductor. Verify that the undervoltage thresholds are within design limits for startup and for shutdown.

### **Key Design Considerations**

While the design of forward converters with *TOPSwitch-GX* has much in common with designs that use discrete transistors and controllers, some important differences must be considered. Attention to these items will significantly reduce the time to arrive at a successful design.

- A proper clamp circuit is required to control the maximum drain voltage. Resonant clamp circuits are not recommended. While the example clamp circuit in this document is suitable for moderate power levels, the circuit will need modification to adapt to applications that require the dissipation of more power.

- Leakage inductance of the transformer affects the power dissipation in the clamp circuit. High leakage inductance will prohibit the use of simple clamp circuits. Be aware that a magnetic amplifier post regulator will greatly increase the effective leakage inductance of the transformer.

- The primary inductance of the transformer affects the power dissipation in the clamp circuit. Maximize the primary inductance to reduce the magnetizing current and the energy that must be processed by clamp circuit.

- Use a slow diode for the rectifier D1 in the clamp circuit. A

fast diode will greatly increase the amount of energy that the

clamp must dissipate.

- Remember that the components R<sub>CS</sub> and C<sub>CS</sub> on the secondary are important components of the clamp circuit. Failure to include this network will cause excessive power dissipation in the clamp components on the primary.

- Confirm in bench evaluations that C<sub>CP</sub> in the clamp circuit on the primary is not too large. Perform transient load tests at low and high input voltages. Monitor the drain voltage waveform for volt-second balance to be certain that the transformer does not saturate.

- Check the temperature of the Zener diodes VR1, VR2 and VR3 in the clamp circuit under maximum load at low input voltage and with repetitive transient loading. If the power supply does not have a latching shutdown for fault conditions, check it under a sustained short circuit on the output. There could be excessive heating if C<sub>CP</sub> is too small, the primary inductance of the transformer is too low, or if the leakage inductance it too high.

- Match the current limit to the load. Use the X pin to program

the current limit lower, especially if a larger TOPSwitch-GX

is selected for thermal or efficiency reasons.

### References

- [1] R. W. Erickson and D. Maksimović, Fundamentals of Power Electronics, Second Edition. Kluwer Academic Publishers, 2001. ISBN 0-7923-7270-0.

- [2] Colonel Wm. T. McLyman, Transformer and Inductor Design Handbook, Second Edition. Marcel Dekker, Inc., 1988. ISBN 0-8247-7828-6.

- [3] Colonel Wm. T. McLyman, Magnetic Core Selection for Transformers and Inductors, A User's Guide to Practice and Specification, Second Edition. Marcel Dekker, Inc, 1997. ISBN 0-8247-9841-4.

- [4] Colonel W. T. McLyman, Designing Magnetic Components for High Frequency dc-dc Converters. Kg Magnetics, Inc., 1993. ISBN 1-883107-00-8.

- [5] Micrometals Inc., 5615 E. La Palma Avenue, Anaheim, CA 92807 USA; www.micrometals.com.

- [6] MAGNETICS, P.O. Box 391, Butler, PA 16003-0391 USA, www.mag-inc.com.

## Appendix A Table of Nomenclature

| Name in AN-30           | Description                                                                                                                                                    |  |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| $\delta_{	extsf{D}}$    | Difference between actual and effective duty ratio that results from leakage inductance in the transformer.                                                    |  |  |  |  |  |  |  |

| η                       | Total system efficiency (lower case Greek letter eta).                                                                                                         |  |  |  |  |  |  |  |

| $\eta_{	exttt{DC}}$     | Efficiency excluding losses in AC input circuit and EMI filter. Used in computation of input capacitance required for holdup time. $\eta_{DC} \ge \eta$ .      |  |  |  |  |  |  |  |

| μ <sub>0</sub>          | Permeability of free space (4π x 10 <sup>-7</sup> H/m).                                                                                                        |  |  |  |  |  |  |  |

| $\mu_{r}$               | Relative permeability of ferrite core material (lower case Greek letter mu). Dimensionless.                                                                    |  |  |  |  |  |  |  |

| A <sub>e</sub>          | Effective cross-sectional area of transformer core.                                                                                                            |  |  |  |  |  |  |  |

| A <sub>L</sub>          | Inductance coefficient of ungapped transformer core.                                                                                                           |  |  |  |  |  |  |  |

| B <sub>M</sub>          | Maximum AC flux density in transformer core.                                                                                                                   |  |  |  |  |  |  |  |

| В <sub>реак</sub>       | Maximum flux density in the power transformer.                                                                                                                 |  |  |  |  |  |  |  |

| C <sub>IN</sub>         | Total bulk capacitance at the DC input to the converter.                                                                                                       |  |  |  |  |  |  |  |

| C <sub>vs</sub>         | Capacitor in circuit for external reduction of DC <sub>MAX</sub> .                                                                                             |  |  |  |  |  |  |  |

| D1                      | Diode in primary clamp circuit.                                                                                                                                |  |  |  |  |  |  |  |

| D                       | Duty ratio of TOPSwitch-GX at a given operating point.                                                                                                         |  |  |  |  |  |  |  |

| D <sub>HL_ACTUAL</sub>  | Duty ratio at the highest operational DC input voltage V <sub>MAX</sub> .                                                                                      |  |  |  |  |  |  |  |

| D <sub>HL_RESET</sub>   | Maximum duty ratio to guarantee reset of the transformer at DC input voltage V <sub>MAX</sub> .                                                                |  |  |  |  |  |  |  |

| D <sub>IL</sub>         | Maximum duty ratio at current I <sub>L</sub> .                                                                                                                 |  |  |  |  |  |  |  |

| D <sub>IL1</sub>        | The DC <sub>MAX</sub> at current I <sub>L1</sub> into the L pin of <i>TOPSwitch-GX</i> .                                                                       |  |  |  |  |  |  |  |

| D <sub>IL2</sub>        | The DC <sub>MAX</sub> at current I <sub>L2</sub> into the L pin of <i>TOPSwitch-GX</i> .                                                                       |  |  |  |  |  |  |  |

| D <sub>LL_ACTUAL</sub>  | Duty ratio at lowest steady state DC input voltage V <sub>MIN</sub> .                                                                                          |  |  |  |  |  |  |  |

| D <sub>LL_RESET</sub>   | Maximum duty ratio to guarantee reset of the transformer at DC input voltage $V_{\mbox{\tiny MIN}}$ .                                                          |  |  |  |  |  |  |  |

| D <sub>MA</sub>         | The duty ratio of the magnetic amplifier.                                                                                                                      |  |  |  |  |  |  |  |

| D <sub>MAX</sub>        | The maximum duty of T <i>OPSwitch-GX</i> at the lowest operational DC input voltage $V_{DROPOUT}$ .                                                            |  |  |  |  |  |  |  |

| D <sub>MAX_ACTUAL</sub> | Actual duty ratio of $TOPSwitch-GX$ at the lowest operational DC input voltage $V_{DROPOUT}$ .                                                                 |  |  |  |  |  |  |  |

| D <sub>MAX_RESET</sub>  | Maximum duty ratio to guarantee reset of the transformer at DC input voltage $V_{\text{DROPOUT}}$ . This is less than maximum duty cycle $DC_{\text{MAX}}$ .   |  |  |  |  |  |  |  |

| D <sub>NOM</sub>        | Duty ratio at nominal input voltage.                                                                                                                           |  |  |  |  |  |  |  |

| D <sub>RESET</sub>      | Maximum duty ratio to guarantee reset of the transformer at a given operating point.                                                                           |  |  |  |  |  |  |  |

| D <sub>xDO</sub>        | Highest maximum duty cycle as set by current into the L pin of <i>TOPSwitch-GX</i> with external components. Occurs at DC input voltage V <sub>DROPOUT</sub> . |  |  |  |  |  |  |  |

| D <sub>XHL</sub>        | The lowest maximum duty cycle as set by current into the L pin of $TOPSwitch-GX$ with external components at DC input voltage $V_{MAX}$ .                      |  |  |  |  |  |  |  |

| D <sub>xov</sub>        | The maximum duty ratio that corresponds to I <sub>ov</sub> .                                                                                                   |  |  |  |  |  |  |  |

| DC <sub>MAX</sub>       | Maximum default duty cycle of TOPSwitch-GX (see Data Sheet).                                                                                                   |  |  |  |  |  |  |  |

| f <sub>L</sub>          | AC line frequency.                                                                                                                                             |  |  |  |  |  |  |  |

| f <sub>s</sub>          | TOPSwitch-GX switching frequency.                                                                                                                              |  |  |  |  |  |  |  |

| i                       | Instantaneous current in secondary winding j of the transformer.                                                                                               |  |  |  |  |  |  |  |

| I <sub>AUX</sub>        | Output current of the auxiliary output                                                                                                                         |  |  |  |  |  |  |  |

| l <sub>DAVBR</sub>      | Current rating for the bridge rectifier.                                                                                                                       |  |  |  |  |  |  |  |

| I <sub>L</sub>          | Current into the L pin of TOPSwitch-GX.                                                                                                                        |  |  |  |  |  |  |  |

| Name in AN-30        | Description                                                                                                    |  |  |  |  |  |  |  |  |