## 512Mbit GDDR3 SDRAM

## Revision 1.2

## September 2005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE.

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

- 1. For updates or additional information about Samsung products, contact your nearest Samsung office.

- 2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

<sup>\*</sup> Samsung Electronics reserves the right to change products or specification without notice.

## **Revision History**

#### Revision 1.2 (September 26, 2005)

- Redefined -BJ11's AC core spec parameters. Refer to the AC characteristics table on page 56.

- Added current spec of -BJ11

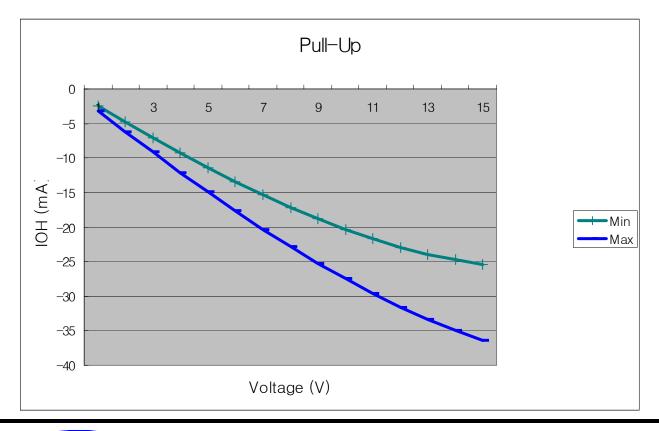

- · IBIS curve added.

- ICC6 changed from 50mA to 35mA for -BC\*\* starting from Sep'01

#### **Revision 1.1 (August 8, 2005)**

- Removed -BJ14 from the spec.

- Added -BJ11 as a preliminary spec. Accordingly, CL12 added as well.

- Removed additive latency (AL) from the spec.

- Minor changes: Corrected typo on page 17, data driver impedance. Note 9 added on page 51. Added supplementary explanation on VDD&VDDQ=2.0V operation on page 51and 52.

- Removed tFAW restriction on -BJ\*\* part only. All -BC\*\* part should follow tFAW spec.

- Added tXSNR on page 56.

#### **Revision 1.0 (March 8, 2005)**

- Removed -BC10/11/12 from the spec.

- Separated VDD spec as below

- VDD & VDDQ = 2.0V + 0.1V distinguished by part number as -BJ

- VDD & VDDQ = 1.8V + 0.1V distinguished by part number as -BC

Accordingly, defined -BJ12/14 and -BC14/16/20 along with supported operating voltage.

- Changed tRCDR and tRP of -BC16 from 9tCK and 8tCK to 10tCK and 9tCK. Accordingly, tRCDW/tRC/tDAL changed each from 5tCK/ 27tCK/17tCK to 6tCK/28tCK/18tCK.

- Changed tRCDR and tRP of -BC20 from 7tCK and 6tCK to 8tCK and 7tCK. Accordingly, tRCDW/tRC/tDAL changed each from 4tCK/ 21tCK/13tCK to 5tCK/22tCK/14tCK.

- Added Vendor ID read timing on page 18 & clock frequency change timing on page 19.

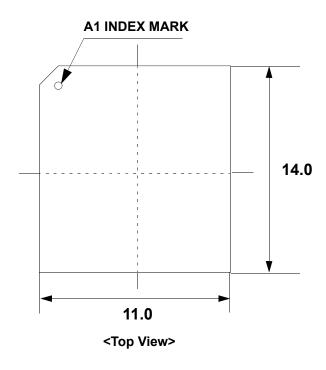

- Changed package dimension from 12mm x 14mm to 11mm x 14mm.

- · DC spec updated.

- Capacitance values changed. Input(Clock,Address,Command) capacitance changed from 2.0pF/2.5pF to 1.5pF/3.0pF and DQ,DQS and DM capacitance changed from 2.0pF/2.5pF to 1.5pF/2.0pF.

## **Revision History**

#### Revision 0.9 (November 11, 2004)

· Corrected typo in boundary scan order table.

#### **Revision 0.8 (October 10, 2004)**

Changed part number from K4J52324QB-G to K4J52324QC-B

```

-Package code attribute re-defined : G .... 144FBGA, Leaded V .... 144FBGA, Lead-free A .... 136FBGA, Leaded B .... 136FBGA, Lead-free

```

#### Revision 0.7 (October 5, 2004)

- · DC spec defined.

- Comment added on how to change the clock frequency after the power-up (page 14)

- Comment added on read to write timing diagram on page 32 which specify the timing interval from data termination enable to the first data-in should be greater than 1tCK.

- Changed CL(Cas Latency) of -GC14 from 9tCK to 10tCK. Changed CL(Cas Latency) of -GC16 from 8tCK to 9tCK

- Typo corrected in boundary scan order table and additional remark for boundary scan added on page 17.

- Changed tDCERR from 0.2tCK to 0.03tCK (Typo)

#### Revision 0.6 (September 15, 2004)

- · Typo corrected

- Removed tWR\_A to avoid confusion. Instead, tWR represent write recovery time for both normal precharge and Auto-precharge cases.

Accordingly tDAL adjusted by tWR for each frequency.

- · Clock jitter spec added.

- · Changed input capacitance.

- Fixed CL of -GC12 to 11tCK where as specified with 10tCK or 11tCK previously.

#### Revision 0.5 (June 4, 2004)

Typo corrected (Package ball out)

#### Revision 0.4 (May 13, 2004)

- Changed tRRD from 12ns to 10ns

- · Added tFAW specification in the spec which defined as five times of tRRD

- Added boundary scan specification & added package dimension

#### **Revision 0.3 (January 26, 2004)**

Changed part number of 512Mb(x32) GDDR3 from K4J53324QB-GC to K4J52324QB-GC

#### Revision 0.2 (January 5, 2004)

- Added Write Latency 5, 6, and 7 (clock) in the spec.

- Added tWR\_A 8 and 9 (clock) in the spec.

#### Revision 0.1 (December 18, 2003)

- · Changed CL of -GC12 from 9tCK to 10tCK

- Changed tCK(max) from 3.0ns to 3.3ns

Revision 0.0 (December 18, 2003) - Target Spec

## 2M x 32Bit x 8 Banks Graphic Double Data Rate 3 Synchronous DRAM with Uni-directional Data Strobe

#### **FEATURES**

- 2.0V + 0.1V power supply for device operation for -BJ\*\*

- 2.0V + 0.1V power supply for I/O interface for -BJ\*\*

- 1.8V + 0.1V power supply for device operation for -BC\*\*

- 1.8V + 0.1V power supply for I/O interface for -BC\*\*

- On-Die Termination (ODT)

- · Output Driver Strength adjustment by EMRS

- · Calibrated output drive

- 1.8V Pseudo Open drain compatible inputs/outputs

- 4 internal banks for concurrent operation

- Differential clock inputs (CK and CK)

- Commands entered on each positive CK edge

- CAS latency: 4, 5, 6, 7, 8, 9, 10, 11, 12 (clock)

- · Programmable Burst length: 4 and 8

- Programmable Write latency: 1, 2, 3, 4, 5, 6 and 7 (clock)

Mirror function with MF pin

- Single ended READ strobe (RDQS) per byte

- Single ended WRITE strobe (WDQS) per byte

- · RDQS edge-aligned with data for READs

- · WDQS center-aligned with data for WRITEs

- · Data Mask(DM) for masking WRITE data

- · Auto & Self refresh modes

- · Auto Precharge option

- 32ms, auto refresh (8K cycle)

- 136 Ball FBGA

- · Maximum clock frequency up to 900MHz

- Maximum data rate up to 1.8Gbps/pin

- · DLL for outputs

- · Boundary scan function with SEN pin

#### ORDERING INFORMATION

| Part NO.        | Max Freq. | Max Data Rate | VDD&VDDQ           | Package       |

|-----------------|-----------|---------------|--------------------|---------------|

| K4J52324QC-BJ11 | 900MHz    | 1.8Gbps/pin   | 2.0V+0.1V          |               |

| K4J52324QC-BJ12 | 800MHz    | 1.6Gbps/pin   | 2.0V <u>+</u> 0.1V |               |

| K4J52324QC-BC14 | 700MHz    | 1.4Gbps/pin   |                    | 136 Ball FBGA |

| K4J52324QC-BC16 | 600MHz    | 1.2Gbps/pin   | 1.8V <u>+</u> 0.1V |               |

| K4J52324QC-BC20 | 500MHz    | 1.0Gbps/pin   |                    |               |

K4J52324QC-A\*\*\* is leaded package part number

#### GENERAL DESCRIPTION

#### FOR 2M x 32Bit x 8 Bank GDDR3 SDRAM

The K4J52324QC is 536,870,912 bits of hyper synchronous data rate Dynamic RAM organized as 8 x 2,097,152 words by 32 bits, fabricated with SAMSUNG's high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 7.2GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of operating frequencies, and programmable latencies allow the device to be useful for a variety of high performance memory system applications.

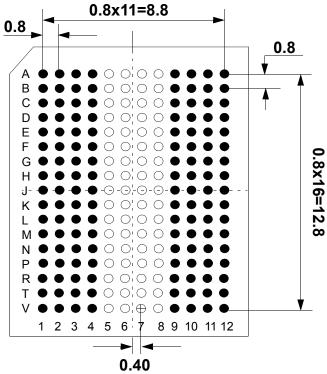

## **PIN CONFIGURATION**

**Normal Package (Top View)**

|   | 1    | 2     | 3     | 4    | 5 | 6 | 7 | 8 | 9             | 10    | 11    | 12   |

|---|------|-------|-------|------|---|---|---|---|---------------|-------|-------|------|

| Α | VDDQ | VDD   | VSS   | ZQ   |   |   |   |   | MF            | VSS   | VDD   | VDDQ |

| В | VSSQ | DQ0   | DQ1   | VSSQ |   |   |   |   | VSSQ          | DQ9   | DQ8   | VSSQ |

| С | VDDQ | DQ2   | DQ3   | VDDQ |   |   |   |   | VDDQ          | DQ11  | DQ10  | VDDQ |

| D | VSSQ | WDQS0 | RDQS0 | VSSQ |   |   |   |   | VSSQ          | RDQS1 | WDQS1 | VSSQ |

| Е | VDDQ | DQ4   | DM0   | VDDQ |   |   |   |   | VDDQ          | DM1   | DQ12  | VDDQ |

| F | VDD  | DQ6   | DQ5   | CAS  |   |   |   |   | <del>CS</del> | DQ13  | DQ14  | VDD  |

| G | VSS  | VSSQ  | DQ7   | BA0  |   |   |   |   | BA1           | DQ15  | VSSQ  | VSS  |

| Н | VREF | A1    | RAS   | CKE  |   |   |   |   | WE            | BA2   | A5    | VREF |

| J | VSSA | RFU1  | RFU2  | VDDQ |   |   |   |   | VDDQ          | CK    | СК    | VSSA |

| K | VDDA | A10   | A2    | A0   |   |   |   |   | A4            | A6    | A8/AP | VDDA |

| L | VSS  | VSSQ  | DQ25  | A11  |   |   |   |   | A7            | DQ17  | VSSQ  | VSS  |

| М | VDD  | DQ24  | DQ27  | A3   |   |   |   |   | A9            | DQ19  | DQ16  | VDD  |

| N | VDDQ | DQ26  | DM3   | VDDQ |   |   |   |   | VDDQ          | DM2   | DQ18  | VDDQ |

| Р | VSSQ | WDQS3 | RDQS3 | VSSQ |   |   |   |   | VSSQ          | RDQS2 | WDQS2 | VSSQ |

| R | VDDQ | DQ28  | DQ29  | VDDQ |   |   |   |   | VDDQ          | DQ21  | DQ20  | VDDQ |

| Т | VSSQ | DQ30  | DQ31  | VSSQ |   |   |   |   | VSSQ          | DQ23  | DQ22  | VSSQ |

| ٧ | VDDQ | VDD   | VSS   | SEN  |   |   |   |   | RESET         | VSS   | VDD   | VDDQ |

#### NOTE:

- 1. RFU1 is reserved for future use

- 2. RFU2 is reserved for future use

## INPUT/OUTPUT FUNCTIONAL DESCRIPTION

| Symbol           | Type             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK           | Input            | Clock: CK and $\overline{\text{CK}}$ are differential clock inputs. CMD, ADD inputs are sampled on the crossing of the positive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK (both directions of crossing). CK and CK should be maintained stable except self-refresh mode.                                                                                                                                                                                                                                                                                 |

| CKE              | Input            | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit, and for self refresh entry. CKE is asynchronous for self refresh exit. CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during self refresh.          |

| CS               | Input            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RAS, CAS,<br>WE  | Input            | Command Inputs: RAS, CAS and WE (along with CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DM0<br>~DM3      | Input            | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of clock. Although DM pins are input only, the DM loading matches the DQ and WDQS loading.                                                                                                                                                                                                                                                                                                                            |

| BA0 ~ BA2        | Input            | <b>Bank Address Inputs:</b> BA0, BA1 and BA2 define to which bank an Active, Read, Write or Precharge command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A0 ~ A11         | Input            | Address Inputs: Provided the row address for Active commands and the column address and Auto Precharge bit for Read/Write commands to select one location out of the memory array in the respective bank. A8 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A8 LOW) or all banks (A8 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1,BA2. The address inputs also provide the op-code during Mode Register Set commands. Row addresses: RA0 ~ RA11, Column addresses: CA0 ~ CA7, CA9. Column address CA8 is used for auto precharge. |

| DQ0<br>~ DQ31    | Input/<br>Output | Data Input/ Output: Bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RDQS0<br>~ RDQS3 | Output           | READ Data Strobe: Output with read data. RDQS is edge-aligned with read data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| WDQS0<br>~ WDQS3 | Input            | WRITE Data Strobe: Input with write data. WDQS is center-aligned to the inout data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NC/RFU           |                  | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{DDQ}$        | Supply           | DQ Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{SSQ}$        | Supply           | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{DD}$         | Supply           | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub>  | Supply           | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $V_{DDA}$        | Supply           | DLL Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{SSA}$        | Supply           | DLL Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>REF</sub> | Supply           | Reference voltage: 0.7*VDDQ , 2 Pins : (H12) for Data input , (H1) for CMD and ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MF               | Input            | Mirror Function for clamshell mounting of DRAMs. VDDQ CMOS input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ZQ               | Reference        | Resistor connection pin for On-die termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RES              | Input            | Reset pin: RESET pin is a VDDQ CMOS input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SEN              | Input            | Scan enable: Must tie to the ground in case not in use. VDDQ CMOS input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### **Mirror Function**

The GDDR3 SDRAM provides a mirror function (MF) ball to change the physical location of the control lines and all address lines which helps to route devices back to back. The MF ball will affect RAS, CAS, WE, CS and CKE on balls H3, F5, H9, F9 and H4 respectively and A0, A1, A2, A3, A4, A5, A6, A7, A8, A9, A10, A11, BA0, BA1 and BA2 on balls K4, H2, K3, M4, K9, H11, K10, L9, K11, M9, K2, L4, G4, G9 and H10 respectively and only detects a DC input. The MF ball should be tied directly to VSS or VDD depending on the control line orientation desired. When the MF ball is tied low the ball orientation is as follows, RAS - H3, CAS - F4, WE - H9, CS - F9, CKE - H4, A0 - K4, A1 - H2, A2 - K3, A3 - M4, A4 - K9, A5 - H11, A6 - K10, A7 - L9, A8 - K11, A9 - M9, A10 - K2, A11 - L4, BA0 - G4, BA1 - G9 and BA2 - H10. The high condition on the MF ball will change the location of the control balls as follows; CS - F4, CAS - F9, RAS - H10, WE - H4, CKE - H9, A0 - K9, A1 - H11, A2 - K10, A3 - M9, A4 - K4, A5 - H2, A6 - K3, A7 - L4, A8 - K2, A9 - M4, A10 - K11, A11 - L9, BA0 - G9, BA1 - G4 and BA2 - H3.

#### **Mirror Function Signal Mapping**

| PIN | MF LOGIC STATE |     |  |  |  |  |  |

|-----|----------------|-----|--|--|--|--|--|

| PIN | HIGH           | LOW |  |  |  |  |  |

| RAS | H10            | H3  |  |  |  |  |  |

| CAS | F9             | F4  |  |  |  |  |  |

| WE  | H4             | Н9  |  |  |  |  |  |

| CS  | F4             | F9  |  |  |  |  |  |

| CKE | H9             | H4  |  |  |  |  |  |

| A0  | K9             | K4  |  |  |  |  |  |

| A1  | H11            | H2  |  |  |  |  |  |

| A2  | K10            | K3  |  |  |  |  |  |

| A3  | M9             | M4  |  |  |  |  |  |

| A4  | K4             | K9  |  |  |  |  |  |

| A5  | H2             | H11 |  |  |  |  |  |

| A6  | K3             | K10 |  |  |  |  |  |

| A7  | L4             | L9  |  |  |  |  |  |

| A8  | K2             | K11 |  |  |  |  |  |

| A9  | M4             | M9  |  |  |  |  |  |

| A10 | K11            | K2  |  |  |  |  |  |

| A11 | L9             | L4  |  |  |  |  |  |

| BA0 | G9             | G4  |  |  |  |  |  |

| BA1 | G4             | G9  |  |  |  |  |  |

| BA2 | H3             | H10 |  |  |  |  |  |

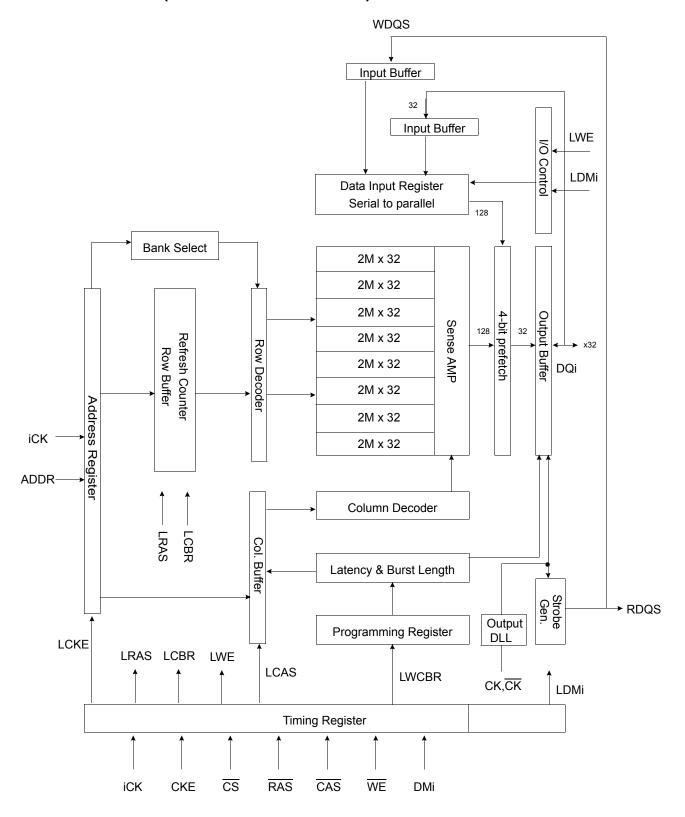

## BLOCK DIAGRAM (2Mbit x 32I/O x 8 Bank)

\* iCK: internal clock

## **FUNCTIONAL DESCRIPTION**

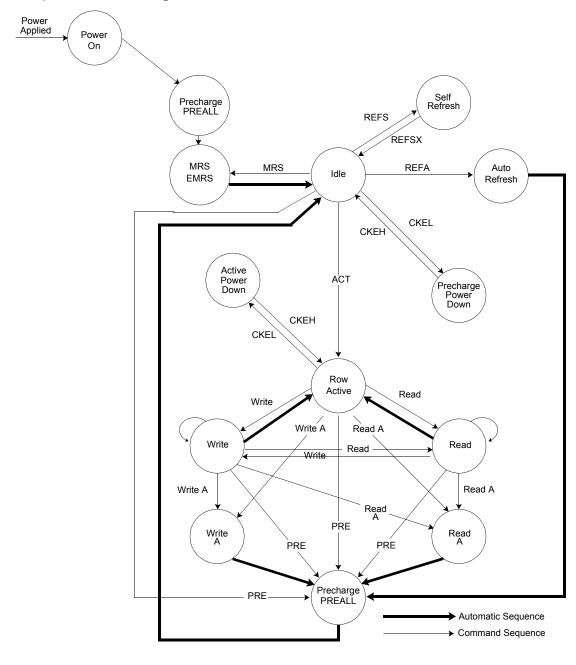

### **Simplified State Diagram**

PREALL = Precharge All Banks MRS = Mode Register Set EMRS = Extended Mode Register Set REFS = Enter Self Refresh REFSX = Exit Self Refresh REFA = Auto Refresh CKEL = Enter Power Down CKEH = Exit Power Down ACT = Active Write A = Write with Autoprecharge Read A = Read with Autoprecharge PRE = Precharge

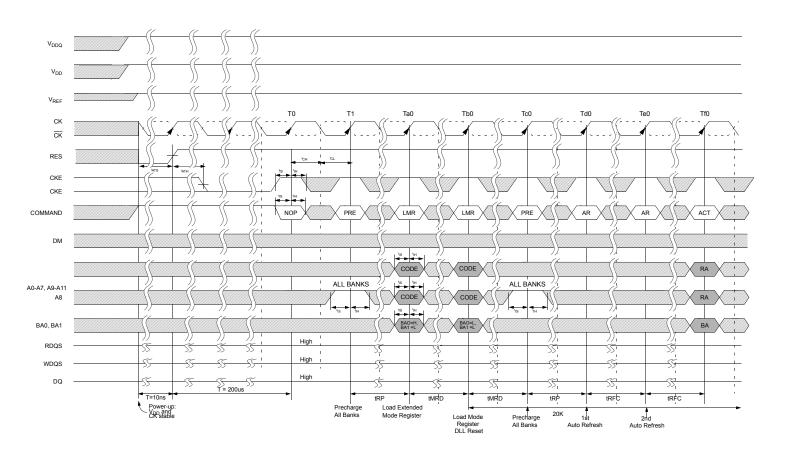

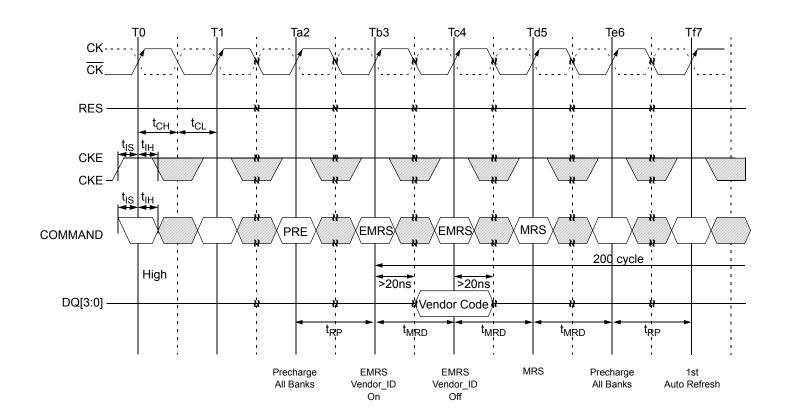

#### INITIALIZATION

GDDR3 SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation.

- 1. Apply power and keep CKE/RESET at low state ( All other inputs may be undefined)

- Apply VDD and VDDQ simultaneously

- Apply VDDQ before Vref. ( Inputs are not recognized as valid until after V<sub>REF</sub> is applied )

- 2. Required minimum 100us for the stable power before RESET pin transition to HIGH

- Upon power-up the address/command active termination value will automatically be set based off the state of RESET and CKE.

- On the rising edge of RESET the CKE pin is latched to determine the address and command bus termination value.

- If CKE is sampled at a zero the address termination is set to 1/2 of ZQ.

- If CKE is sampled at a one the address termination is set to ZQ.

- RESET must be maintained at a logic LOW level and CS at a logic high value during power-up to ensure that the DQ outputs will be in a High-Z state, all active terminators off, and all DLLs off.

- 4. Minimum 200us delay required prior to applying any executable command after stable power and clock.

- Once the 200us delay has been satisfied, a DESELECT or NOP command should be applied, then RESET and CKE should be brought to HIGH,

- 6. Issue a PRECHARGE ALL command following after NOP command.

- 7. Issue a EMRS command (BA1BA0="01") to enable the DLL.

- 8. Issue MRS command (BA0BA1 = "00") to reset the DLL and to program the operating parameters. 20K clock cycles are required between the DLL to lock.

- 9. Issue a PRECHARGE ALL command

- 10 . Issue at least two AUTO refresh command to update the driver impedance and calibrate the output drivers.

Following these requirements, the GDDR3 SDRAM is ready for normal operation.

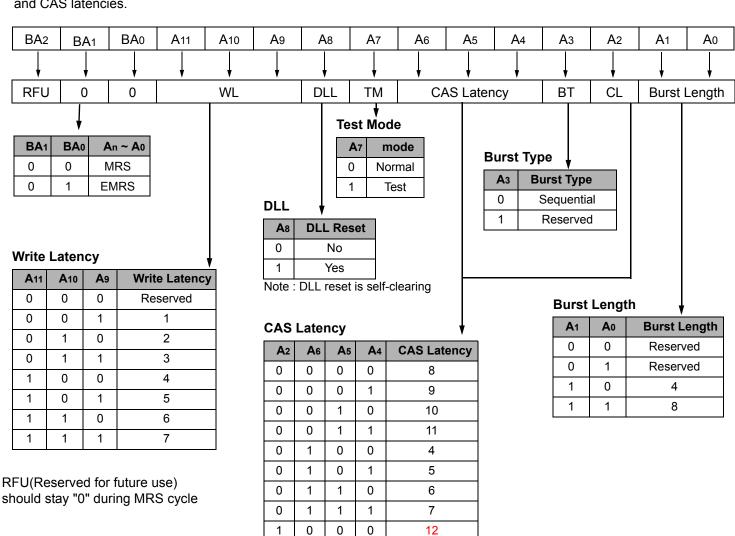

## **MODE REGISTER SET(MRS)**

The mode register stores the data for controlling the various operating modes of GDDR3 SDRAM. It programs CAS latency, addressing mode, test mode and various vendor specific options to make GDDR3 SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after EMRS setting for the proper operation. The mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  (The GDDR3 SDRAM should be in active mode with CKE already high prior to writing into the mode register). The state of address pins  $A_0 \sim A_{11}$  and  $BA_0$ ,  $BA_1$ ,  $BA_2$  in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  going low is written in the mode register. Minimum clock cycles specified as tMRD are required to complete the write operation in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The Burst length uses  $A_0 \sim A_1$ .  $A_1 \sim A_2 \sim A_3 \sim A_4 \sim$

Reserved(13)

Reserved(14)

Reserved(15)

Reserved

Reserved

Reserved

Reserved

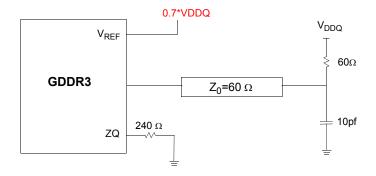

### PROGRAMMABLE IMPEDANCE OUTPUT BUFFER AND ACTIVE TERMINATOR

The GDDR3 SDRAM is equipped with programmable impedance output buffers and Active Terminators. This allows a user to match the driver impedance to the system. To adjust the impedance, an external precision resistor(RQ) is connected between the ZQ pin and Vss. The value of the resistor must be six times of the desired output impedance.

For example, a  $240\Omega$  resistor is required for an output impedance of  $40 \Omega$ . To ensure that output impedance is one sixth the value of RQ (within 10 %), the range of RQ is  $120\Omega$  to  $360\Omega$  ( $20\Omega$  to  $60\Omega$ ) output impedance.

MF,SEN, RES, CK and /CK are not internally terminated. CK and /CK will be terminated on the system module using external 1% resisters. The output impedance is updated during all AUTO REFRESH commands and NOP commands when a READ is not in progress to compensate for variations in voltage supply and temperature. The output impedance updates are transparent to the system. Impedance updates do not affect device operation, and all data sheet timing and current specifications are met during update. To guarantee optimum output driver impedance after power-up, the GDDR3(x32) needs at least 20us after the clock is applied and stable to calibrate the impedance upon power-up. The user may operate the part with less than 20us, but the optimal output impedance is not guaranteed. The value of ZQ is also used to calibrated the internal address/command termination resisters. The two termination values that are selectable during power up are 1/2 of ZQ and ZQ. The value of ZQ is used to calibrate the internal DQ termination resisters. The two termination values that are selectable are 1/4 of ZQ and 1/2 of ZQ.

#### **BURST LENGTH**

Read and write accesses to the GDDR3 SDRAM are burst oriented, with the burst length being programmable, as shown in MRS table. The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. Reserved states should not be used, as unknown operation or incompatibility with future versions may result. When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within the block, meaning that the burst will wrap within the block if a boundary is reached. The block is uniquely selected by A2-Ai when the burst length is set to four (Where Ai is the most significant column address bit for a given configuration). The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. The programmable burst length applies to both READ and WRITE bursts.

#### **BURST TYPE**

Accesses within a given burst must be programmed to be sequential; this is referred to as the burst type and is selected via bit M3. This device does not support the interleaved burst mode found in DDR SDRAM devices. The ordering of accesses within a burst is determined by the burst length, the burst type, and the starting column address, as shown in below table: Burst Definition

#### **Burst Definition**

| Burst<br>Length | Start | ing Column A | Address | Order of Accesses<br>Within a Burst |

|-----------------|-------|--------------|---------|-------------------------------------|

| Lengin          |       |              |         | Type= Sequential                    |

| 4               | A2    | A1           | A0      |                                     |

| 4               | 0     | 0            | 0       | 0 - 1 - 2 - 3                       |

|                 | A2    | A1           | A0      |                                     |

| 8               | 0     | 0            | 0       | 0 - 1 - 2 - 3 - 4 - 5 - 6 - 7       |

|                 | 1     | 0            | 0       | 4 - 5 - 6 - 7 - 0 - 1 - 2 - 3       |

NOTE: 1. For a burst length of four, A2-A7 select the block of four burst; A0-A1 select the starting column within the block and must be set to zero

2. For a burst length of eight, A3-A7 select the block of eight burst; A0-A2 select the starting column within the block.

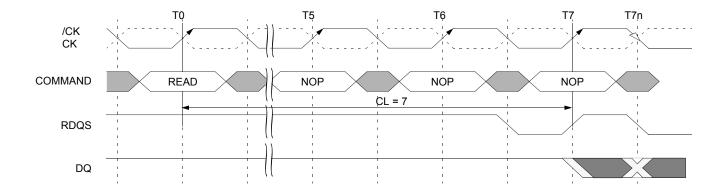

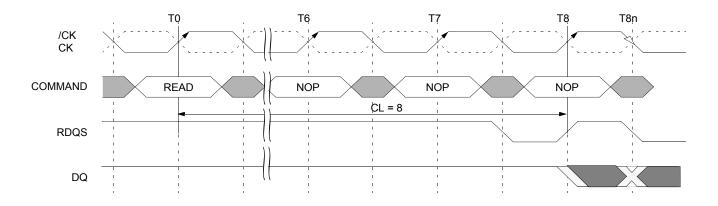

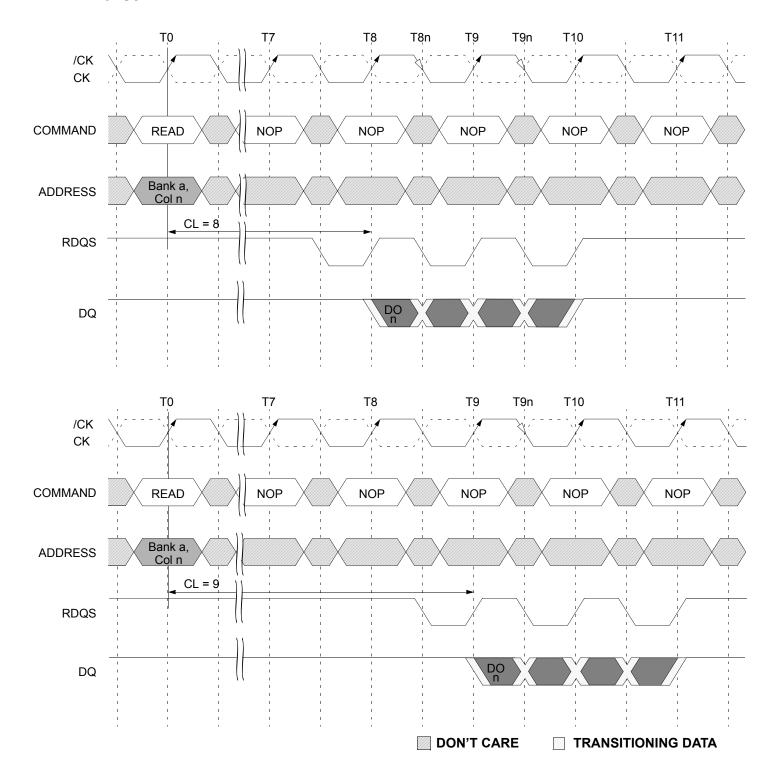

## **CAS LATENCY (READ LATENCY)**

The CAS latency is the delay, in clock cycles, between the registration of a READ command and the availability of the first bit of output data. The latency can be set to  $4\sim11$  clocks. If a READ command is registered at clock edge n, and the latency is m clocks, the data will be available nominally coincident with clock edge n+m. Below table indicates the operating frequencies at which each CAS latency setting can be used. Reserved states should not be used as unknown operation or incompatibility with future versions may result.

**CAS Latency**

|       | Allowable operating frequency (MHz ) |       |       |      |       |  |  |  |  |  |  |

|-------|--------------------------------------|-------|-------|------|-------|--|--|--|--|--|--|

| SPEED | CL=11                                | CL=10 | CL=9  | CL=8 | CL=7  |  |  |  |  |  |  |

| -11   | ≤ 900                                | -     | -     | -    | -     |  |  |  |  |  |  |

| -12   | ≤ 800                                |       |       |      |       |  |  |  |  |  |  |

| -14   |                                      | ≤ 700 | -     | -    | -     |  |  |  |  |  |  |

| -16   |                                      |       | ≤ 600 | -    | -     |  |  |  |  |  |  |

| -20   |                                      |       |       | -    | ≤ 500 |  |  |  |  |  |  |

Burst Length = 4 in the cases shown Shown with nominal  $t_{AC}$  and nominal  $t_{DSDQ}$

■ DON'T CARE ■ TRANSITIONING DATA

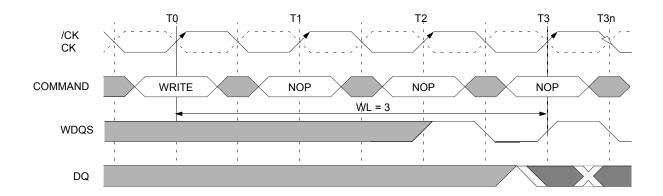

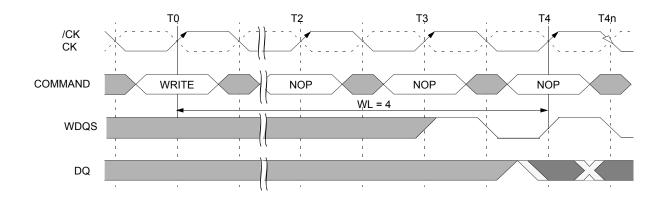

#### WRITE LATENCY

The Write latency (WL) is the delay, in clock cycles, between the registration of a WRITE command and the availability of the first bit of input data. The latency can be set from 1 to 7 clocks depending in the operating frequency and desired current draw. When the write latencies are set to 1 or 2 or 3 clocks, the input receivers never turn off when the WRITE command is registered. If a WRITE command is registered at clock edge n, and the latency is m clocks, the data will be available nominally coincident with clock edge n+m. Reserved states should not be used as unknown operation or incompatibility with future versions may result.

Burst Length = 4 in the cases shown

**■ DON'T CARE ■ TRANSITIONING DATA**

#### **TEST MODE**

The normal operating mode is selected by issuing a MODE REGISTER SET command with bits A7 set to zero, and bits A0-A6 and A8-A11 set to the desired values. Test mode is entered by issuing a MODE REGISTER SET command with bit A7 set to one, and bits A0-A6 and A8-A11 set to the desired values. Test mode functions are specific to each Dram Manufacturer and its exact functions are hidden from the user.

#### **DLL RESET**

The normal operating mode is selected by issuing a MODE REGISTER SET command with bit A7 set to zero, and bits A0-A6 and A8-A11 set to the desired values. A DLL reset is initiated by issuing a MODE REGISTER SET command with bit A8 set to one, and bits A0-A7 and A9-A11 set to the desired values. When a DLL Reset is complete the GDDR3 SDRAM reset bit 8 of the mode register to a zero. After DLL Reset MRS, Power down can not be issued within 10 clock.

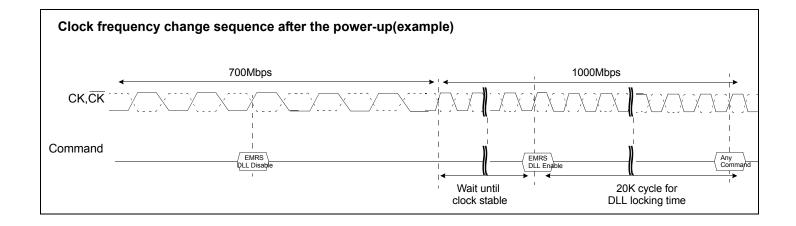

In case the clock frequency need to be changed after the power-up, 512Mb GDDR3 doesn't require DLL reset. Instead, DLL should be disabled first before the frequency changed and then change the clock frequency as needed. After the clock frequency changed, there needed some time till clock become stable and then enable the DLL and then 20K cycle required to lock the DLL

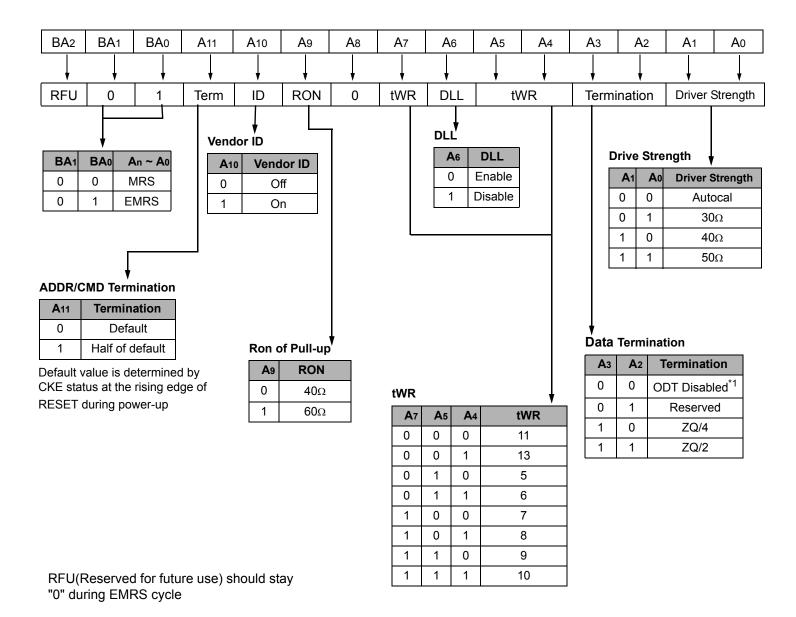

## **EXTENDED MODE REGISTER SET(EMRS)**

The extended mode register stores the data output <u>driver strength</u> and <u>on-die</u> termination options. The extended mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and high on BA0(The GDDR3 SDRAM should be in all bank precharge with CKE already high prior to writing into the <u>extended mode register</u>). The state of address pins A0  $\sim$  A11 and BA0,BA1,BA2 in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  going low are written in the extended mode register. The minimum clock cycles specified as tMRD are required to complete the write operation in the extended mode register. 4 kinds of the output driver strength are supported by EMRS (A1, A0) code. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. "High" on BA0 is used for EMRS. Refer to the table for specific codes.

<sup>\*</sup> ZQ : Resistor connection pin for On-die termination

<sup>\* 1 :</sup> ALL ODT will be disabled

#### **DLL ENABLE/DISABLE**

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization and upon returning to normal operation after disabling the DLL for debugging or evaluation. (When the device exits self refresh mode, the DLL is enabled automatically.) Any time the DLL is enabled, 20K clock cycles must occur before a READ command can be issued.

#### **DATA TERMINATION**

The Data Termination, DT, is used to determine the value of the internal data termination resisters. The GDDR3 SDRAM supports  $60\Omega$  and  $120\Omega$  termination. The termination may also be disabled for testing and other purposes.

#### DATA DRIVER IMPEDANCE

The Data Driver impedance (DZ) is used to determine the value of the data drivers impedance. When autocalibration is used the data driver impedance is set to RQ/6 and it's tolerance is determined by the calibration accuracy of the device. When any other value is selected the target impedance is set nominally to the desired impedance. However, the accuracy is now determined by the device's specific process corner, applied voltage and operating temperature.

### MANUFACTURERS VENDOR CODE AND REVISION IDENTIFICATION

The Manufacturers Vendor Code, V, is selected by issuing a EXTENDED MODE REGISTER SET command with bits A10 set to one, and bits A0-A9 and A11 set to the desired values. When the V function is enabled the GDDR3 SDRAM will provide its manufacturers vendor code on DQ[3:0] and revision identification on DQ[7:4]

| Manufacturer | DQ[3:0] |

|--------------|---------|

| Samsung      | 1       |

## **Vendor ID Read**

☐ DON'T CARE ☐ TRANSITIONING DATA

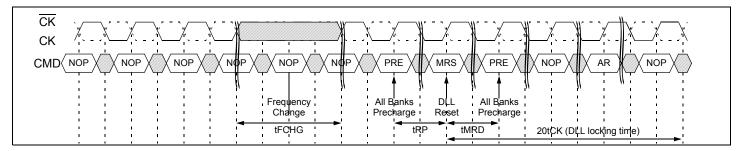

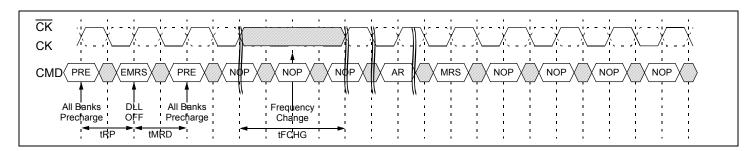

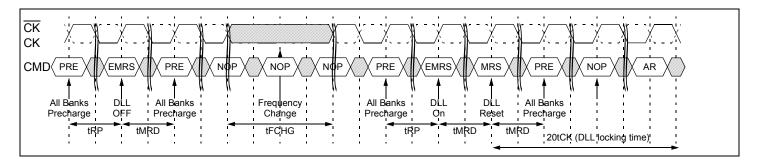

## Clock frequency change sequence during the device operation

#### Both existing tCK and desired tCK are in DLL-On mode

- Change frequency from existing frequency to desired frequency

- Issue Precharge All Banks command

- Issue MRS command to reset the DLL while other fields are valid and required 20K tCK to lock the DLL

- Issue Precharge All Banks command. Issue at least Auto-Refresh command

#### Existing tCK is in DLL-on mode while desired tCK is in DLL-off mode

- Issue Precharge All Banks command

- Issue EMRS command to disable the DLL

- Issue Precharge All Banks command

- Change the frequency from existing to desired.

- Issue Auto-Refresh command at least two. Issue MRS command

#### Clock frequency change in case existing tCK is in DLL-off mode while desired tCK is in DLL-on mode

- Issue Precharge All Banks command and issue EMRS command to disable the DLL.

- Issue Precharge All Banks command.

- Change the clock frequency from existing to desired

- Issue Precharge All Banks command.

- Issue EMRS command to enable the DLL

- Issue MRS command to reset the DLL and required 20K tCK to lock the DLL.

- Issue Precharge All Banks command.

- Issue Auto-Refresh command at least two

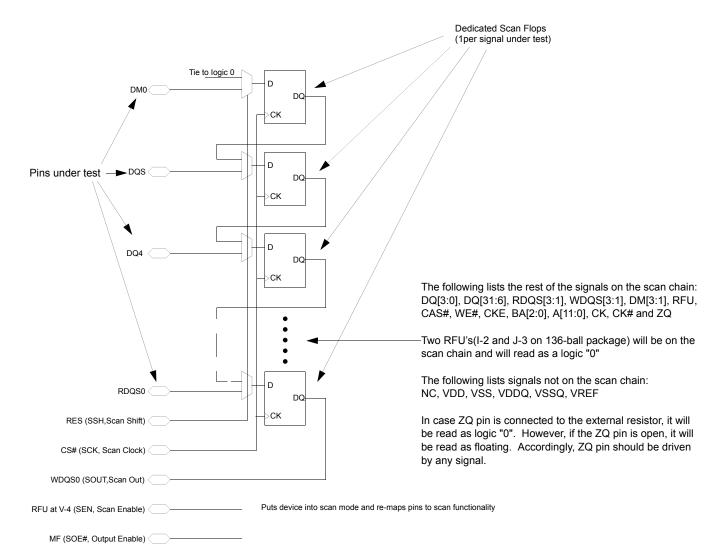

### **BOUNDARY SCAN FUNCTION**

#### **GENERAL INFORMATION**

The 512Mb GDDR3 incorporates a modified boundary scan test mode as an optional feature. This mode doesn't operate in accordance with IEEE Standard 1149.1 - 1990. To save the current GDDR3 ball-out, this mode will scan parallel data input and output and the scanned data through WDQS0 pin controlled by an add-on pin, SEN which is located at V-4 of 136 ball package. For the normal device operation other than boundary scan, there required device re-initialization by device power-off and then power-on.

#### DISABLING THE SCAN FEATURE

It is possible to operate the 512Mb GDDR3 without using the boundary scan feature. SEN(at V-4 of 136 ball package) should be tied LOW(VSS) to prevent the device from entering the boundary scan mode. The other pins which are used for scan mode, RES, MF, WDQS0 and CS# will be operating at normal GDDR3 functionalities when SEN is deasserted.

Figure 1. Internal Block Diagram (Reference Only)

#### **BOUNDARY SCAN EXIT ORDER**

| BIT# | BALL |

|------|------|------|------|------|------|------|------|------|------|------|------|

| 1    | D-3  | 13   | E-10 | 25   | K-11 | 37   | R-10 | 49   | L-3  | 61   | G-4  |

| 2    | C-2  | 14   | F-10 | 26   | K-10 | 38   | T-11 | 50   | M-2  | 62   | F-4  |

| 3    | C-3  | 15   | E-11 | 27   | K-9  | 39   | T-10 | 51   | M-4  | 63   | F-2  |

| 4    | B-2  | 16   | G-10 | 28   | M-9  | 40   | T-3  | 52   | K-4  | 64   | G-3  |

| 5    | B-3  | 17   | F-11 | 29   | M-11 | 41   | T-2  | 53   | K-3  | 65   | E-2  |

| 6    | A-4  | 18   | G-9  | 30   | L-10 | 42   | R-3  | 54   | K-2  | 66   | F-3  |

| 7    | B-10 | 19   | H-9  | 31   | N-11 | 43   | R-2  | 55   | L-4  | 67   | E-3  |

| 8    | B-11 | 20   | H-10 | 32   | M-10 | 44   | P-3  | 56   | J-3  |      |      |

| 9    | C-10 | 21   | H-11 | 33   | N-10 | 45   | P-2  | 57   | J-2  |      |      |

| 10   | C-11 | 22   | J-11 | 34   | P-11 | 46   | N-3  | 58   | H-2  |      |      |

| 11   | D-10 | 23   | J-10 | 35   | P-10 | 47   | M-3  | 59   | H-3  |      |      |

| 12   | D-11 | 24   | L-9  | 36   | R-11 | 48   | N-2  | 60   | H-4  |      | _    |

#### \*Note:

- 1. When the device is in scan mode, the mirror function will be disabled and none of the pins are remapped.

- 2. Since the other input of the MUX for DM0 tied to GND, the device will output the continuous zeros after scanning a bit #67, if the chip stays in scan shift mode.

- 3. Two RFU balls(#57and #58) in the scan order, will be read as a logic"0".

#### **SCAN PIN DESCRIPTION**

| Package Ball | Symbol | Normal Function | Туре   | Description                                                                                                                                                                                                                                              |

|--------------|--------|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V-9          | SSH    | RES             | Input  | Scan shift. Capture the data input from the pad at logic LOW and shift the data on the chain at logic HIGH.                                                                                                                                              |

| F-9          | SCK    | CS              | Input  | Scan Clock. Not a true clock, could be a single pulse or series of pulses. All scan inputs will be referenced to rising edge of the scan clock.                                                                                                          |

| D-2          | SOUT   | WDQS0           | Output | Scan Output.                                                                                                                                                                                                                                             |

| V-4          | SEN    | RFU             | Input  | Scan Enable. Logic HIGH would enable the device into scan mode and will be disabled at logic LOW. Must be tied to GND when not in use.                                                                                                                   |

| A-9          | SOE    | MF              | Input  | Scan Output Enable. Enables (registered HIGH) SOUT data. This pin will be tied to VDD or GND through a resistor (typically 1K $\Omega$ ) for normal operation. Tester needs to overdrive this pin guarantee the required input logic level in scan mode. |

#### \*Note:

- 1. When SEN is asserted, no commands are to be executed by the GDDR3. This applies to both user commands and manufacturing commands which may exist while RES is

- 2. All scan functionalities are valid only after the appropriate power-up and initialization sequence. (RES and CKE, to set the ODT of the C/A)

- 3. In scan mode, the ODT for the address and control lines set to a nominal termination value of ZQ. The ODT for DQ's will be disabled. It is not necessary for the termination to be calibrated

- 4. In a double-load clam-shell configuration, SEN will be asserted to both devices. Separate two SOE's should be provided to top and bottom devices to access the scanned output. When either of the devices is in scan mode, SOE for the other device which not in a scan will be disabled.

#### SCAN DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

| PARAMETER/CONDITON           | SYMBOL               | MIN                    | MAX                    | UNITS | NOTES |

|------------------------------|----------------------|------------------------|------------------------|-------|-------|

| Input High (Logic 1) Voltage | V <sub>IH</sub> (DC) | V <sub>REF</sub> +0.15 | -                      | V     | 1,2   |

| Input Low (Logic 0) Voltage  | V <sub>IL</sub> (DC) | -                      | V <sub>REF</sub> -0.15 | V     | 1,2   |

<sup>\*</sup>Note: 1. The parameter applies only when SEN is asserted.

SCK

SEN

SSH LOW

SSH VALID

Pins

under Test

Figure 2. Scan Capture Timing

Not a true clock, but a single pulse or series of pulses

SCK

SEN

SOE

DON'T CARE

SCK

SEN

SSH

SOE

SOUT

SCAN Shift Timing

tSES

tSES

SCAN Out

bit 0

tSAC

Scan Out

bit 0

tSAC

Scan Out

bit 0

TRANSITIONING DATA

<sup>2.</sup> All voltages referenced to GND.

#### SCAN AC ELECTRICAL CHARACTERISTICS

| PARAMETER/CONDITON                             | SYMBOL | MIN | MAX | UNITS | NOTES |

|------------------------------------------------|--------|-----|-----|-------|-------|

| Clock                                          |        |     |     |       |       |

| Clock cycle time                               | tSCK   | 40  | -   | ns    | 1     |

| Scan Command Time                              |        |     |     |       |       |

| Scan enable setup time                         | tSES   | 20  | -   | ns    | 1,2   |

| Scan enable hold time                          | tSEH   | 20  | -   | ns    | 1     |

| Scan command setup time for SSH, SOE# and SOUT | tSCS   | 14  | -   | ns    | 1     |

| Scan command hold time for SSH, SOE# and SOUT  | tSCH   | 14  | -   | ns    | 1     |

| Scan Capture Time                              |        |     |     |       |       |

| Scan capture setup Time                        | tSDS   | 10  | -   | ns    | 1     |

| Scan capture hold Time                         | tSCH   | 10  | -   | ns    | 1     |

| Scan Shift Time                                |        |     |     |       |       |

| Scan clock to valid scan output                | tSAC   | -   | 6   | ns    | 1     |

| Scan clock to scan output hold                 | tSOH   | 1.5 | -   | ns    | 1     |

<sup>\*</sup>Note: 1. The parameter applies only when SEN is asserted.

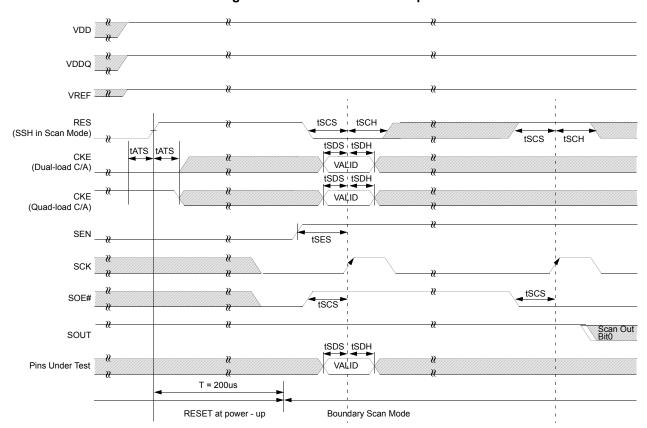

Figure 4. Scan Initialization Sequence

Note: To set the pre-defined ODT for C/A, a boundary scan mode should be issued after an appropriate ODT initialization sequence with RES and CKE signals

<sup>2.</sup> Scan Enable should be issued earlier than other Scan Commands by 3ns.

### **COMMANDS**

Below Truth table-COMMANDs provides a guick reference of available commands. This is followed by a verbal description of each command. Two additional Truth Tables appear following the operation section: these tables provide current state/next state information.

#### TRUTH TABLE - COMMANDS

| Name (Function)                                        | CS | RAS | CAS | WE | ADDR     | NOTES |

|--------------------------------------------------------|----|-----|-----|----|----------|-------|

| DESELECT (NOP)                                         | Н  | Х   | Х   | Х  | X        | 8, 11 |

| NO OPERATION (NOP)                                     | L  | Н   | Н   | Н  | X        | 8     |

| ACTIVE (Select bank and activate row)                  | L  | L   | Н   | Н  | Bank/Row | 3     |

| READ (Select bank and column, and start READ burst)    | L  | Н   | L   | Н  | Bank/Col | 4     |

| WRITE (Select bank and column, and start WRITE burst)  | L  | Н   | L   | L  | Bank/Col | 4     |

| PRECHARGE (Deactivate row in bank or banks)            | L  | L   | Н   | L  | Code     | 5     |

| AUTO REFRESH or SELF REFRESH (Enter self refresh mode) | L  | L   | L   | Н  | X        | 6, 7  |

| LOAD MODE REGISTER                                     | L  | L   | L   | L  | Op-Code  | 2     |

| DATA TERMINATOR DISABLE                                | Х  | Н   | L   | Н  | Х        |       |

## **TRUTH TABLE - DM Operation**

| Name (Function) | DM | DQS   | NOTES |

|-----------------|----|-------|-------|

| Write Enable    | L  | Valid |       |

| Write Inhibit   | Н  | X     | 10    |

- **Note:** 1. CKE is HIGH for all commands except SELF REFRESH.

- 2. BA0~BA1 select either the mode register or the extended mode register (BA0=0, BA1=0 select the mode register; BA0=1, BA1=0 select extended mode register; other combinations of BA0~BA1 are reserved). A0~A11 provide the op-code to be written to the selected mode register.

- 3. BA0~BA2 provide bank address and A0~A11 provide row address.

- 4. BA0~BA2 provide bank address; A0~A7 and A9 provide column address; A8 HIGH enables the auto precharge feature (non persistent), and A8 LOW disables the auto precharge feature.

- 5. A8 LOW: BA0~BA2 determine which bank is precharged. A8 HIGH: All banks are precharged and BA0~BA2 are "Don't Care."

- 6. This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

- 7. Internal refresh counter controls row addressing; All inputs and I/Os are "Don't Care" except for CKE.

- 8. DESELECT and NOP are functionally interchangeable.

- 9. Cannot be in powerdown or self-refresh state.

- 10. Used to mask write data; provided coincident with the corresponding data.

- 11. Except DATA Termination disable.

#### **DESELECT**

The DESELECT function (/CS high) prevents new commands from being executed by the DDR(x32). The GDDR3(x32) SDRAM is effectively deselected. Operations already in progress are not affected.

## **NO OPERATION (NOP)**

The NO OPERATION (NOP) command is used to instruct selected GDDR3(x32) to perform a NOP (/CS LOW). This prevents unwanted commands from being registered during idle or wait states. Operations already in progress are not affected.

#### LOAD MODE REGISTER

The mode registers are loaded via inputs A0-A11. See mode register descriptions in the Register Definition section. The Load Mode Register command can only be issued when all banks are idle, and a subsequent executable command cannot be issued until tMRD is met.

#### **ACTIVE**

The ACTIVE command is used to open (or activate) a row in a particular bank for a subsequent access. The value on the BA0,BA1, BA2 inputs selects the bank, and the address provided on inputsA0-A11 selects the row. This row remains active (or open) for accesses until a PRECHARGE command is issued to that bank. A PRECHARGE command must be issued before opening a different row in the same bank.

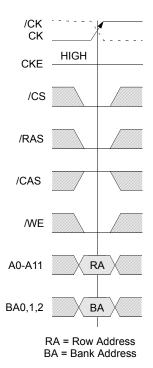

#### **READ**

The READ command is used to initiate a burst read access to an active row. The value on the BA0, BA1, BA2 inputs selects the bank, and the address provided on inputs A0-A7, A9 selects the starting column location. The value on input A8 determines whether or not auto precharge is used. If auto precharge is selected, the row being accessed will be precharged at the end of the READ burst; if auto precharge is not selected, the row will remain open for subsequent accesses.

#### **WRITE**

The WRITE command is used to initiate a burst write access to an active row. The value on the BA0, BA1, BA2 inputs selects the bank, and the address provided on inputs A0-A7, A9 selects the starting column location. The value on inputs A8 determines whether or not auto precharge is used. If auto precharge is selected, the row being accessed will be precharged at the end of the WRITE burst; if auto precharge is not selected, the row will remain open for subsequent accesses. Input data appearing on the DQs is written to the memory array subject to the DM input logic level appearing coincident with the data. If a given DM signal is registered LOW. the corresponding data will be written to memory; If the DM signal is registered HIGH, the corresponding data inputs will be ignored, and a WRITE will not be executed to that byte/column location.

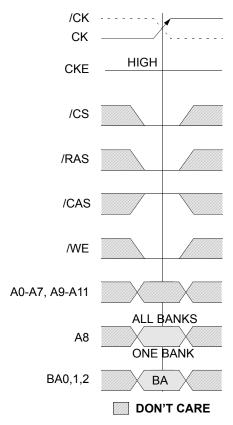

#### **PRECHARGE**

The PRECHARGE command is used to deactivate the open row in a particular bank or the open row in all banks. The bank(s) will be available for a subsequent row access a specified time (t<sub>RP</sub>) after the PRECHARGE command is issued. Input A8 determines whether one or all banks are to be precharged, and in the case where only one banks are to be precharged, inputs BA0,BA1,BA2 select the bank. Otherwise BA0, BA1,BA2 are treated as "Don't Care." Once a bank has been precharged, it is in the idle state and must be activated prior to any READ or WRITE command will be treated as a NOP if there is no open row is already in the process of precharging.

#### **AUTO PRECHARGE**

Auto precharge is a feature which performs the same individual-bank precharge function described above, but without requiring an explicit command. This is accomplished by using A8 to enable auto precharge in conjunction with a specific READ or WRITE command. A precharge of the bank/row that is addressed with the READ or WRITE command is automatically performed upon completion of the READ or WRITE burst. Auto precharge is nonpersistent in that it is either enable or disabled for each individual READ or WRITE command. Auto precharge ensures that the precharge is initiated at the earliest valid state within a burst. This "earliest valid stage" is determined as if an explicit PRECHARGE command was issued at the earliest possible time, without violating  $t_{RAS(min)}$ , as described for each burst type in the Operation section of this data sheet. The user must not issue another command to the same bank until the precharge time( $t_{RP}$ ) is completed.

#### **AUTO REFRESH**

Auto Refresh is used during normal operation of the GDDR3 SDRAM and is analogous to /CAS-BEFORE-/RAS (CBR) REFRESH in FPM/EDO DRAMs. This command is nonpersistent, so it must be issued each time a refresh is required. The addressing is generated by the internal refresh controller. This makes the address bits a "Don't Care" during an Auto Refresh command. The 512Mb(x32) GDDR3 requires Auto Refresh cycles at an average interval of 3.9us (maximum). A maximum Auto Refresh commands can be posted to any given GDDR3(x32) SDRAM, meaning that the maximum absolute interval between any Auto Refresh command and the next Auto Refresh command is 9 x 3.9us(35.1us). This maximum absolute interval is to allow GDDR3(x32) SDRAM output drivers and internal terminators to automatically recalibrate compensating for voltage and temperature changes.

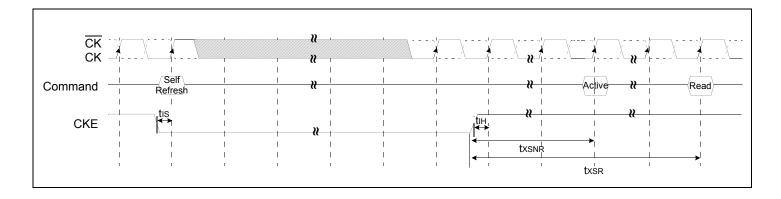

#### SELF REFRESH

The SELF REFRESH command can be used to retain data in the GDDR3(x32) SDRAM ,even if the rest of the system is powered down. SELF REFRESH command can be issued only in case all banks are in precharge state. When in the self refresh mode, the GDDR3(x32) SDRAM retains data without external clocking. The SELF REFRESH command is initiated like an AUTO REFRESH command except CKE is disabled (LOW). The DLL is automatically disabled upon entering SELF REFRESH and is automatically enabled and reset upon exiting SELF REFRESH. The active termination is also disabled upon entering Self Refresh and enabled upon exiting Self Refresh. (20K clock cycles must then occur before a READ command can be issued). Input signals except CKE are "Don't Care" during SELF REFRESH. The procedure for exiting self refresh requires a sequence of commands. First, CK and /CK must be stable prior to CKE going back HIGH. Once CKE is HIGH, the GDDR3(x32) must have NOP commands issued for tXSNR because time is required for the completion of any internal refresh in progress. A simple algorithm for meeting both refresh, DLL requirements and out-put calibration is to apply NOPs for 20K clock cycles before applying any other command to allow the DLL to lock and the output drivers to recalibrate.

## DATA TERMINATOR DISABLE (BUS SNOOPING FOR READ COMMAND)

The DATA TERMINATOR DISABLE COMMAND is detected by the device by snooping the bus for READ commands excluding /CS. The GDDR3 DRAM will disable its Data terminators when a READ command is detected. The terminators are disable CL-1 Clocks after the READ command is detected. In a two rank system both dram devices will snoop the bus for READ commands to either device and both will disable their terminators if a READ command is detected. The command and address terminators and always enabled.

#### **ON-DIE TERMINATION**

Bus snooping for READ commands other than /CS is used to control the on-die termination in the dual load configuration. The GDDR3 SDRAM will disable the on-die termination when a READ command is detected, regardless of the state of /CS, when the ODT for the DQ pins are set for dual loads ( $120\Omega$ ). The on-die termination is disabled x clocks after the READ command where x equals CL-1 and stay off for a duration of BL/2 + 2, as below figure, Data Termination Disable Timing. In a two-rank system, both DRAM devices snoop the bus for READ commands to either device and both will disable the on-die termination if a READ command is detected. The on-die termination for all other pins on the device are always on for both a single-rank system and a dual-rank system.

The on-die termination value on address and control pins is determined during power-up in relation to the state of CKE on the first transition of RESET. On the rising edge of RESET, if CKE is sampled LOW, then the configuration is determined to be a single-rank system. The on-die termination is then set to one-half ZQ for the address pins. On the rising edge of RESET, if CKE is sampled HIGH, then the configuration is determined to be a dual-rank system. The on-die termination for the DQs, WDQS, and DM pins is set in the EMRS.

## **Data Termination Disable Timing**

**Note :** 1. DO n = data-out from column n.

- 2. Burst length = 4.

- 3. Three subsequent elements of data-out appear in the specified order following DO n.

- 4. Shown with nominal  $t_{AC}$  and  $t_{DQSQ}$ .

- 5. RDQS will start driving high one-half cycle prior to the first falling edge.

- 6. The Data Terminators are disabled starting at CL-1 and the duration is BL/2 + 2

- 7. READS to either rank disable both ranks' termination regardless of the logic level of /CS.

# OPERATIONS BANK/ROW ACTIVATION

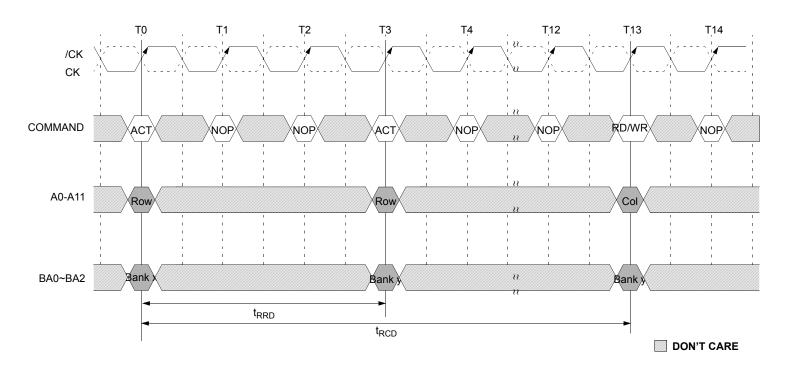

Before any READ or WRITE commands can be issued to a banks within the GDDR3 SDRAM, a row in that bank must be "opened." This is accomplished via the ACTIVE command, which selects both the bank and the row to be activated.

After a row is opened with an ACTIVE command, a READ or WRITE command may be issued to that row, subject to the  $t_{RCD}$  specification.  $t_{RCD(min)}$  should be divided by the clock period and rounded up to the next whole number to determine the earliest clock edge after the ACTIVE command in which a READ or WRITE command can be entered. For example, a  $t_{RCD}$  specification of 16ns with a 800MHz clock (1.25ns period) results in 12.8 clocks rounded to 13. This is reflected in below figure, which covers any case where  $12 < t_{RCD(min)}/t_{CK} \le 13$ .

The same procedure is used to convert other specification limits from time units to clock cycles).

A subsequent ACTIVE command to a different row in the same bank can only be issued after the previous active row has been "closed" (precharged). The minimum time interval between successive ACTIVE commands to the same bank is defined by  $t_{RC}$ .

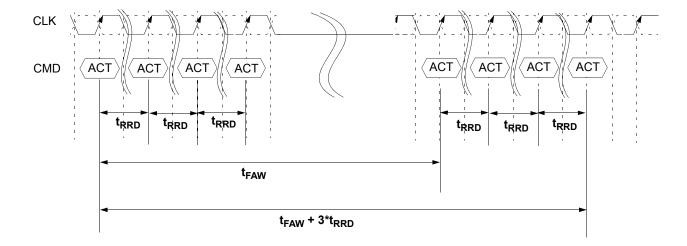

A subsequent ACTIVE command to another bank can be issued while the first bank is being accessed, which results in a reduction of total row access overhead. The minimum time interval between successive ACTIVE commands to different banks is defined by t<sub>RRD</sub>.

Activating a Specific Row in a Specific Bank

## Example : Meeting t<sub>RCD</sub>

#### **READs**

READ bursts are initiated with a READ command, as below figure. The starting column and bank addresses are provided with the READ command and auto precharge is either enabled or disabled for that burst access. If auto precharge is enabled, the row being accessed is precharged at the completion of the burst after  $t_{RAS(min)}$  has been met. For the generic READ commands used in the following illustrations, auto precharge is disabled.

During READ bursts, the valid data-out element from the starting column address will be available following the CAS Latency after the READ command. Each subsequent data-out element will be valid nominally at the next positive or negative strobe edge. READ burst figure shows general timing for 2 of the possible CAS latency settings. The GDDR3(x32) drives the output data edge aligned to the crossing of CK and /CK and to RDQS. The initial HIGH transition LOW of RDQS is known as the read preamble; the half cycle coincident with the last data-out element is known as the read postamble.

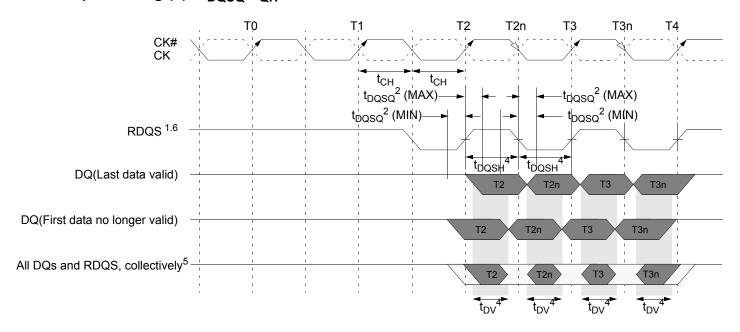

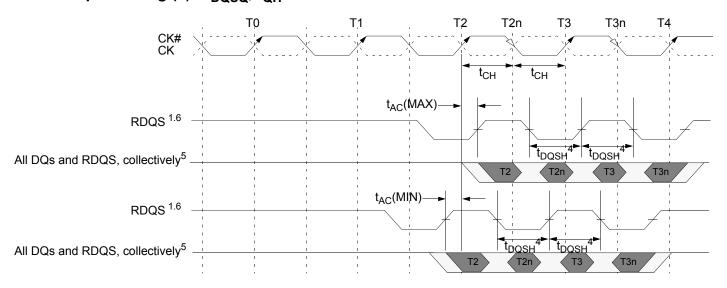

Upon completion of a burst, assuming no other commands have been initiated, the DQs will go High-Z. A detailed explanation of  $t_{DQSQ}$  (valid data-out skew),  $t_{DV}$  (data-out window hold), the valid data window are depicted in Data Output Timing (1) figure. A detailed explanation of  $t_{AC}$  (DQS and DQ transition skew to CK) is shown in Data Output Timing (2) figure.

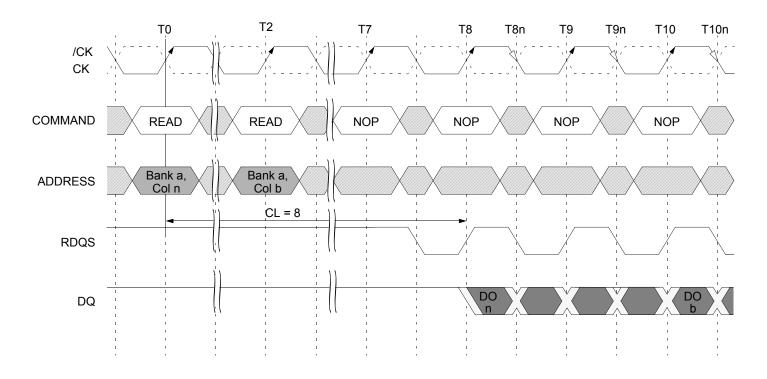

Data from any READ burst may be concatenated with data from a subsequent READ command. A continuous flow of data can be maintained. The first data element from the new burst follows the last element of a completed burst. The new READ command should be issued x cycles after the first READ command, where x equals the number of data element nibbles (nibbles are required by the 4*n*-prefetch architecture) depending on the burst length. This is shown in consecutive READ bursts figure. Nonconsecutive read data is shown for illustration in nonconsecutive READ bursts figure. Full-speed random read accesses within a page (or pages) can be performed as shown in Random READ accesses figure. Data from a READ burst cannot be terminated or truncated.

During READ commands the GDDR3 Dram disables its data terminators.

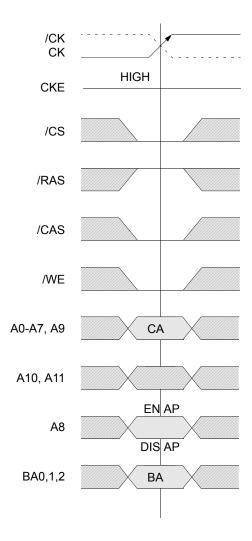

CA = Column Address

BA = Bank Address

EN AP = Enable Auto Precharge

DIS AP = Disable Auto Precharge

DON'T CARE

**READ Command**

## Data Output Timing (1) - t<sub>DQSQ</sub>, t<sub>QH</sub> and Data Valid Window

## Data Output Timing (2) - t<sub>DQSQ</sub>, t<sub>QH</sub> and Data Valid Window

$\textbf{Note:} \ \ \textbf{1.} \ \textbf{t}_{DQSQ} \ \textbf{represents the skew between the 8 DQ lines and the respective RDQS pin.}$

- 2. t<sub>DQSQ</sub> is derived at each RDQS clock edge and is not cumulative over time and begins with first DQ transition and ends with the last valid transition of DQs.

- 3. t<sub>AC</sub> is show in the nominal case

- 4. t<sub>DOHP</sub> is the lesser of tDQSL or tDQSH strobe transition collectively when a bank is active.

- 5. The data valid window is derived for each RDQS transitions and is defined by t<sub>DV</sub>.

- 6. There are 4 RDQS pins for this device with RDQS0 in relation to DQ0-DQ7, RDQS1 in relation DQ8-DQ15, RDQS2 in relation to DQ16-24 and RDQS3 in relation to DQ25-DQ31.

- 7. This diagram only represents one of the four byte lanes.

- 8. t<sub>AC</sub> represents the relationship between DQ, RDQS to the crossing of CK and /CK.

## **READ Burst**

**NOTE:** 1. DO n=data-out from column n.

- 2. Burst length = 4

- 3. Three subsequent elements of data-out appear in the programmed order following DQ n.

- 4. Shown with nominal  $t_{AC}$  and  $t_{DQSQ}$ .

- 5. RDQS will start driving high 1/2 clock cycle prior to the first falling edge.

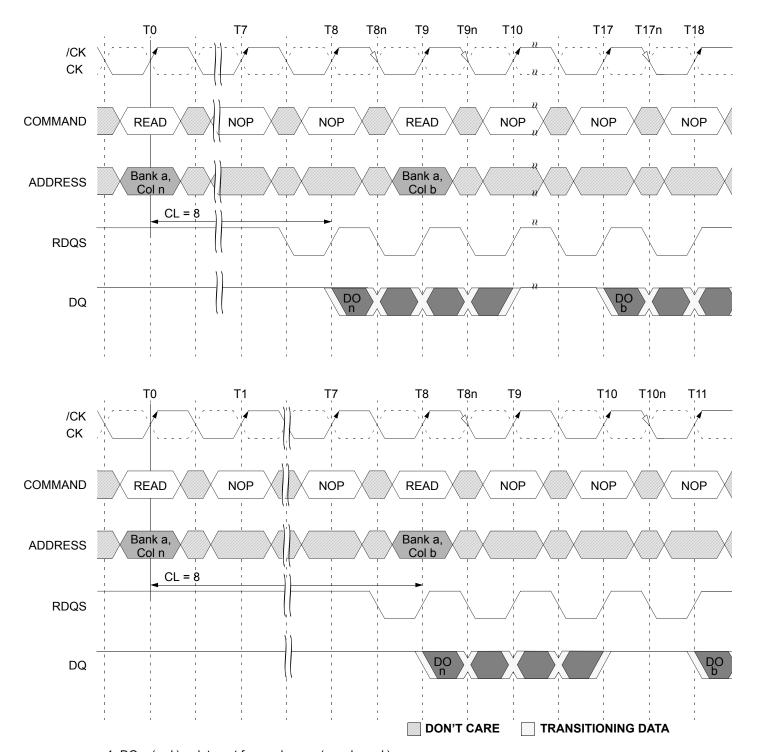

## **Consecutive READ Bursts**

DON'T CARE TRANSITIONING DATA

**NOTE**: 1. DO n (or b) = data-out from column n (or column b).

- 2. Burst length = 4

- 3. Three subsequent elements of data-out appear in the programmed order following DQ *n*.

- 4. Three subsequent elements of data-out appear in the programmed order following DQ b.

- 5. Shown with nominal  $t_{AC}$  and  $t_{DQSQ.}$

- 6. Example applies when READ commands are issued to different devices or nonconsecutive READs.

- 7. RDQS will start driving high one half-clock cycle prior to the first falling edge of RDQS.

### **Nonconsecutive READ Bursts**

**NOTE**: 1. DO n (or b) = data-out from column n (or column b).

- 2. Burst length = 4

- 3. Three subsequent elements of data-out appear in the programmed order following DQ n.

- 4. Three subsequent elements of data-out appear in the programmed order following DQ b.

- 5. Shown with nominal  $t_{AC}$  and  $t_{DQSQ}$ .

- 6. Example applies when READ commands are issued to different devices or nonconsecutive READs.

- 7. RDQS will start driving high one half-clock cycle prior to the first falling edge of RDQS.

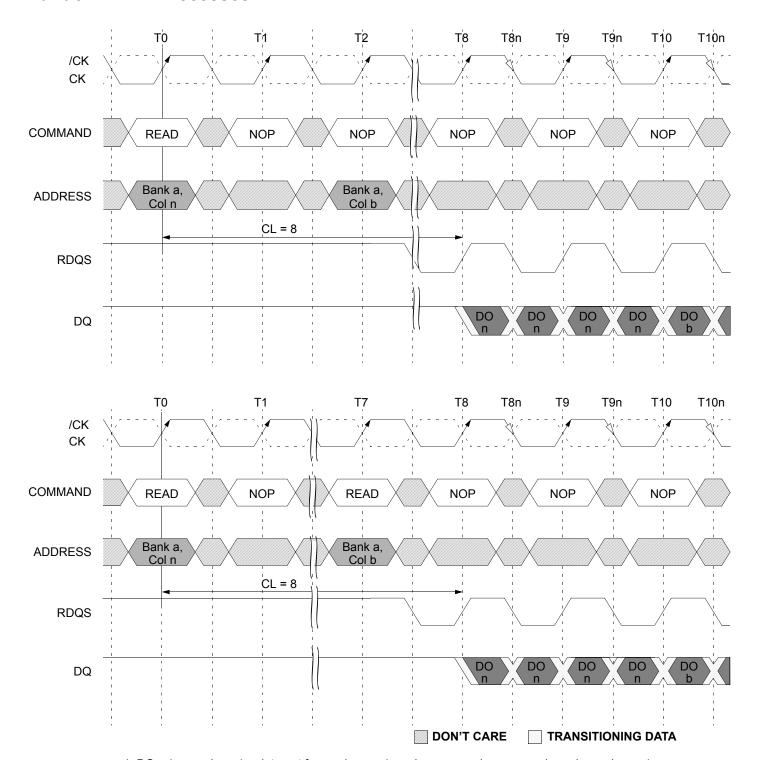

### **Random READ Accesses**

- **NOTE**: 1. DO n (or x or b or g) = data-out from column n (or column x or column x or column b or column a).

- 2. Burst length = 4

- 3. n' or x or b' or g' indicates the next data-out following DO n or DO x or DO b OR DO g, respectively

- 4. READs are to an active row in any bank.

- 5. Shown with nominal t<sub>AC</sub> and t<sub>DOSO</sub>.

- 6. RDQS will start driving high one half-clock cycle prior to the first falling edge of RDQS.

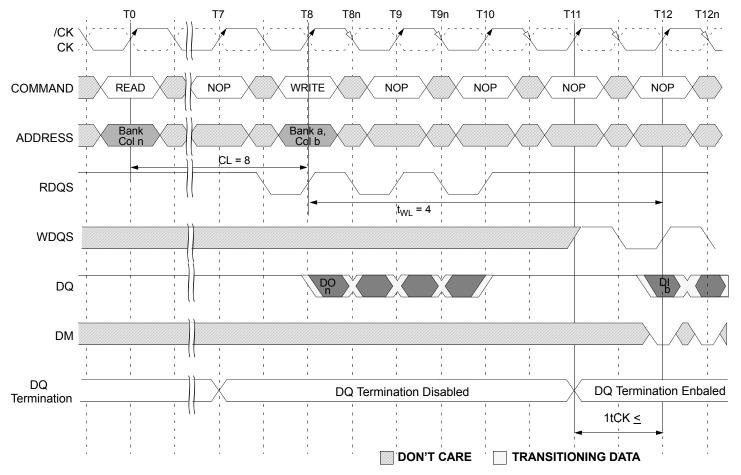

### **READ to WRITE**

NOTE:

- 1. DO n = data-out from column n.

- 2. DI b = data-in from column b.

- 3. Burst length = 4

- 4. One subsequent element of data-out appears in the programmed order following DO *n*.

- 5. Data-in elements are applied following DI *b* in the programmed order.

- 6. Shown with nominal t<sub>AC</sub> and t<sub>DQSQ</sub>.

- 7. t<sub>DQSS</sub> in nominal case.

- 8. RDQS will start driving high one half-clock cycle prior to the first falling edge of RDQS.

- 9. The gap between data termination enable to the first data-in should be greater than 1tCK

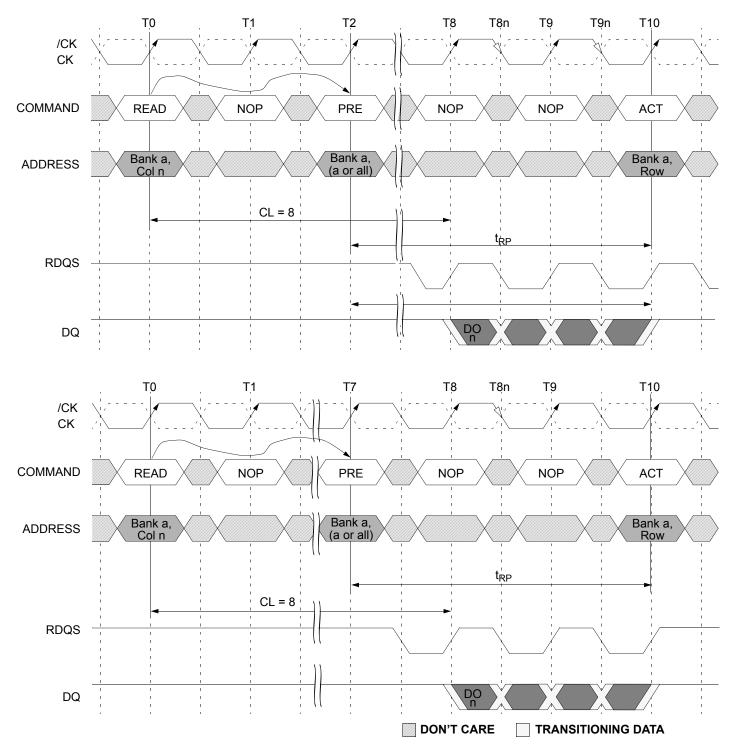

### **READ to PRECHARGE**

**NOTE**: 1. DO n (or b) = data-out from column n (or column b).

- 2. Burst length = 4

- 3. Three subsequent elements of data-out appear in the programmed order following DQ n.

- 4. Three subsequent elements of data-out appear in the programmed order following DQ b.

- 5. Shown with nominal  $t_{AC}$  and  $t_{DQSQ}$

- 6. Example applies when READ commands are issued to different devices or nonconsecutive READs.

- 7. RDQS will start driving high one half-clock cycle prior to the first falling edge of RDQS.

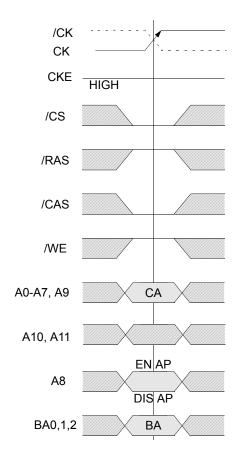

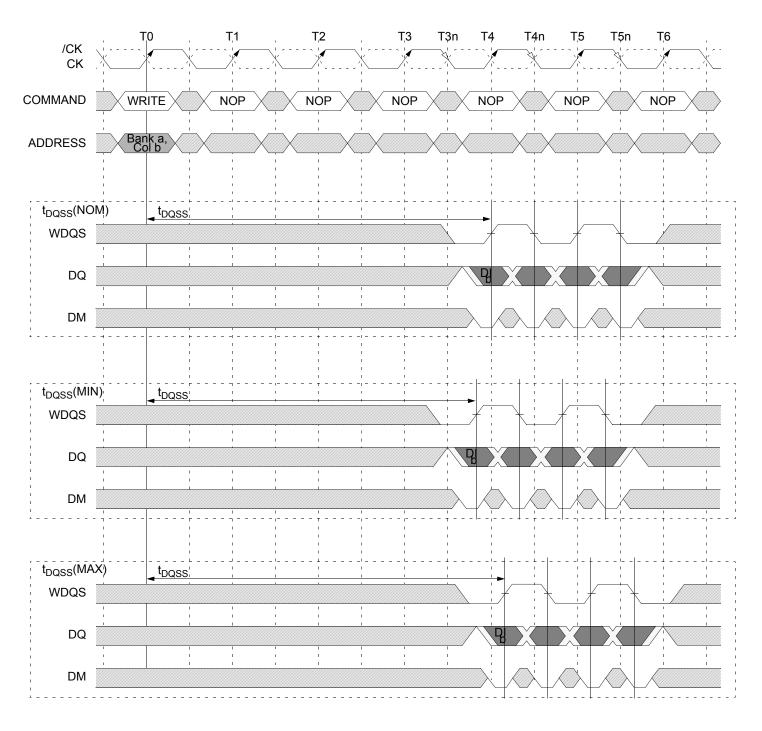

### **WRITEs**

WRITE bursts are initiated with a WRITE command, as shown in Figure. The starting column and bank addresses are provided with the WRITE command, and auto precharge is either enabled or disabled for that access. If auto precharge is enabled, the row being accessed is precharged at the completion of the burst. For the generic WRITE commands used in the following illustrations, auto precharge is disabled.

During WRITE bursts, the first valid data-in element will be registered in a rising edge of WDQS following the WRITE latency set in the mode register and subsequent data elements will be registered on successive edges of WDQS. Prior to the first valid WDQS edge a half cycle is needed and specified as the WRITE Preamble; the half cycle in WDQS following the last data-in element is known as the write postamble.

The time between the WRITE command and the first valid falling edge of WDQS ( $t_{DQSS}$ ) is specified with a relative to the write latency. All of the WRITE diagrams show the nominal case, and where the two extreme cases (i.e.,  $t_{DQSS(min)}$  and  $t_{DQSS(max)}$ ) might not be intuitive, they have also been included. Write Burst figure shows the nominal case and the extremes of tDQSS for a burst of 4. Upon completion of a burst, assuming no other commands have been initiated, the DQs will remain High-Z and any additional input data will be ignored. Data for any WRITE burst may not be truncated with a subsequent WRITE command. The new WRITE command can be issued on any positive edge of clock following the previous WRITE command after the burst has completed. The new WRITE command should be issued x cycles after the first WRITE command should be equals the number of desired nibbles (nibbles are required by 4n-prefetch architecture).

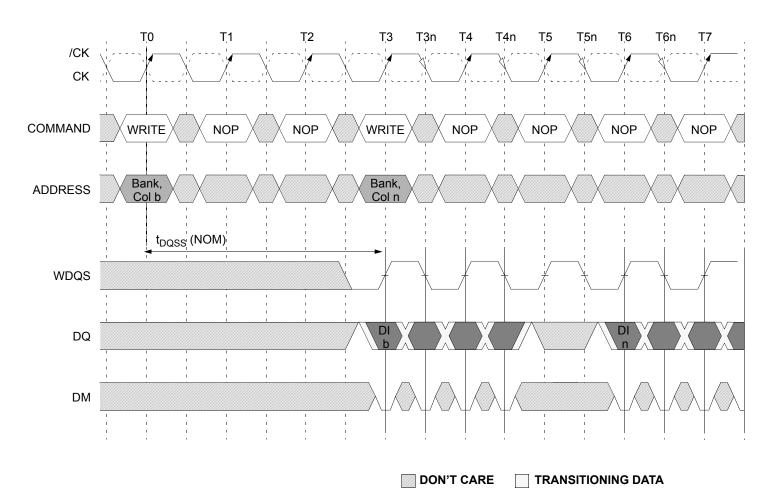

An example of nonconsecutive WRITEs is shown in Nonconsecutive WRITE to READ figure. Full-speed random write accesses within a page or pages can be performed as shown in Random WRITE cycles figure. Data for any WRITE burst may be followed by a subsequent READ command.

Data for any WRITE burst may be followed by a subsequent PRE-CHARGE command. To follow a WRITE the WRITE burst,  $t_{WR}$  should be met as shown in WRITE to PRECHARGE figure.

Data for any WRITE burst can not be truncated by a subsequent PRE-CHARGE command.

CA = Column Address

BA = Bank Address

EN AP = Enable Auto Precharge

DIS AP = Disable Auto Precharge

DON'T CARE

**WRITE Command**

## **WRITE Burst**

DON'T CARE TRANSITIONING DATA

**NOTE**: 1. DI b = data-in for column b.

2. Three subsequent elements of data-in are applied in the programmed order following DI b.

3. A burst of 4 is shown.

4. A8 is LOW with the WRITE command (auto precharge is disabled).

5. Write latency is set to 4

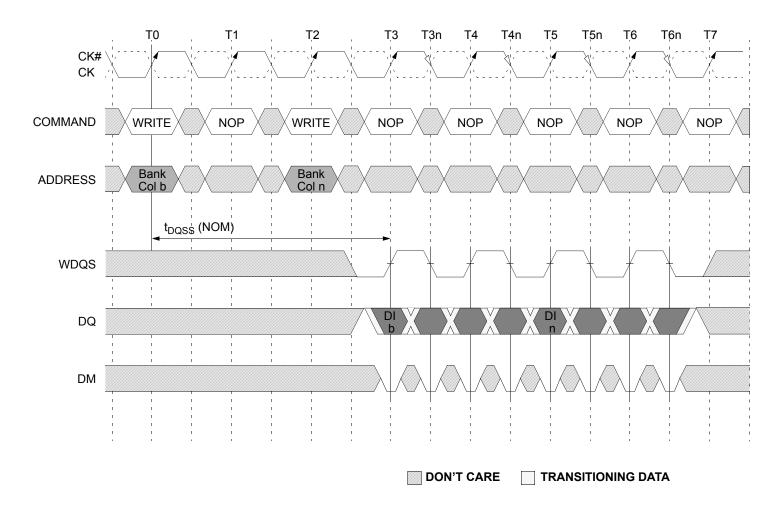

# **Consecutive WRITE to WRITE**

- **NOTE**: 1. DI b, etc. = data-in for column b, etc.

- 2. Three subsequent elements of data-in are applied in the programmed order following DI b.

- 3. Three subsequent elements of data-in are applied in the programmed order following DI *n*.

- 4. Burst of 4 is shown.

- 5. Each WRITE command may be to any bank of the same device.

- 6. Write latency is set to 3

# **Nonconsecutive WRITE to WRITE**

**NOTE**: 1. DI b, etc. = data-in for column b, etc.

2. Three subsequent elements of data-in are applied in the programmed order following DI b.

3. Three subsequent elements of data-in are applied in the programmed order following DI n.

4. burst of 4 is shown.

5. Each WRITE command may be to any bank.

6. Write latency is set to 3

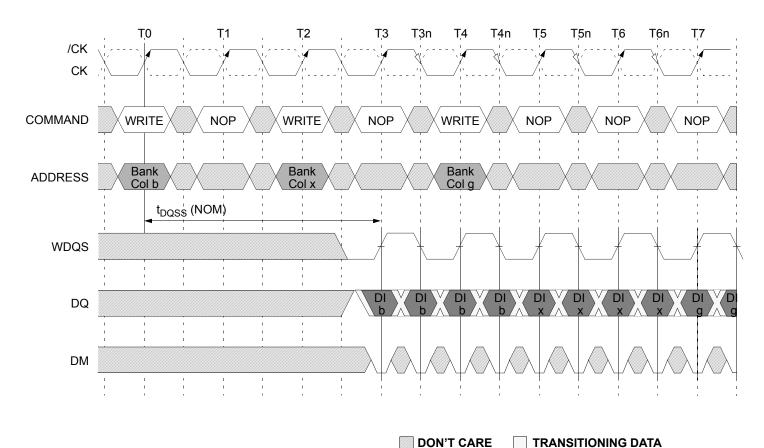

# **Random WRITE Cycles**

NOTE:

- 1. DI b, etc. = data-in for column b, etc.

- 2. b: etc. = the next data in following DI b. etc., according to the programmed burst order.

- 3. Programmed burst length = 4 cases shown.

- 4. Each WRITE command may be to any bank.

- 5. Last write command will have the rest of the nibble on T8 and T8n

- 6. Write latency is set to 3

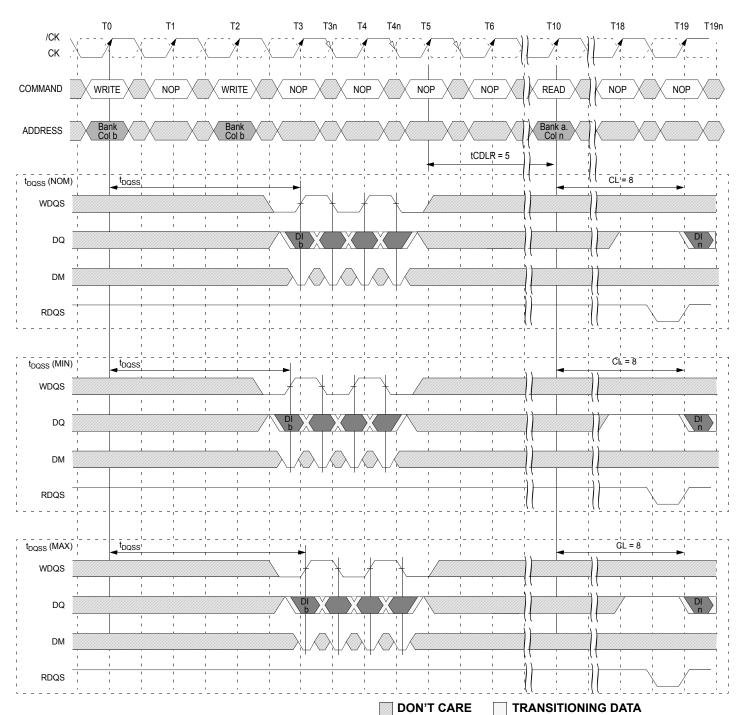

## WRITE to READ

NOTE:

- 1. DI b = data-in for column b.

- 2. Three subsequent elements of data-in the programmed order following DI b.

- 3. A burst of 4 is shown.

- 4.  $t_{\text{CDLR}}$  is referenced from the first positive CK edge after the last data-in pair.

- 5. The READ and WRITE commands are to the same device. However, the READ and WRITE commands may be to different devices, in which case  $t_{CDLR}$  is not required and the READ command could be applied earlier.

- 6. A8 is LOW with the WRITE command (auto precharge is disabled).

- 7. WRITE latency is set to 3

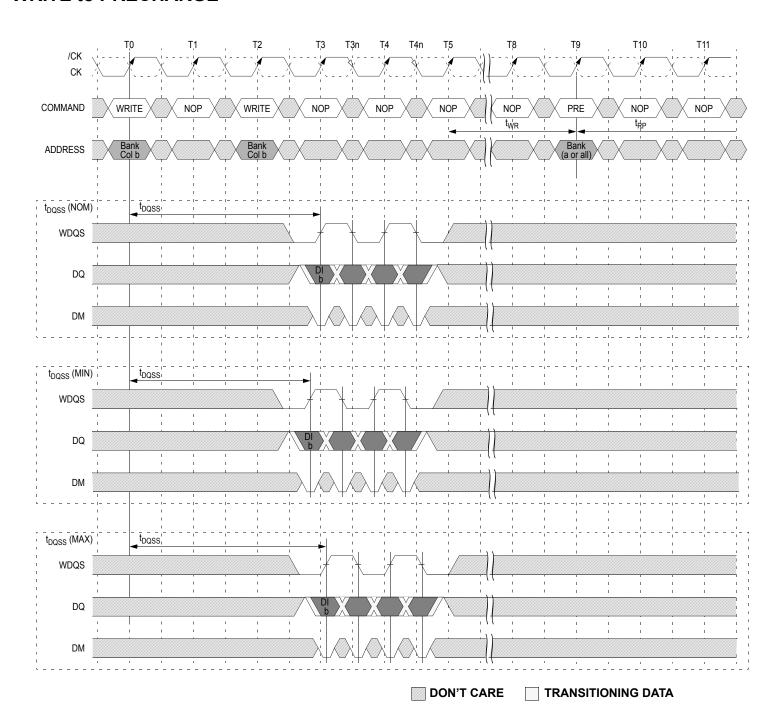

## **WRITE to PRECHARGE**

**NOTE**: 1. DI b = data-in for column b.

2. Three subsequent elements of data-in the programmed order following DI b.

3. A burst of 4 is shown.

4. A8 is LOW with the WRITE command (auto precharge is disabled).

5. WRITE latency is set to 3

### **PRECHARGE**

The PRECHARGE command is used to deactivate the open row in a particular bank or the open row in all banks. The bank(s) will be available for a subsequent row access some specified time ( $t_{RP}$ ) after the PRECHARGE command is issued. Input A8 determines whether one or all banks are to be precharged, and in the case where only one bank is to be precharged, inputs BA0, BA1, BA2 select the bank. When all banks are to be precharged, inputs BA0, BA1, BA2 are treated as "Don't Care." Once a bank has been precharged, it is in the idle state and must be activated prior to any READ or WRITE commands being issued to the bank.

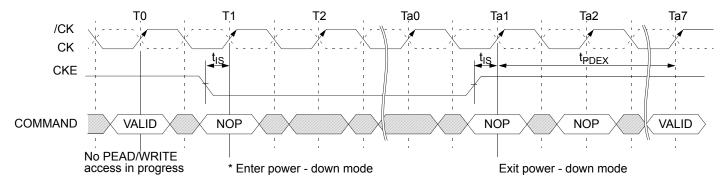

## **POWER-DOWN (CKE NOT ACTIVE)**

Unlike SDR SDRAMs,GDDR3(x32) SDRAM requires CKE to be active at all times an access is in progress; from the issuing of a READ or WRITE command until completion of the burst. For READs, a burst completion is defined when the Read Postamble is satisfied; For WRITEs, a burst completion is defined BL/2 cycles after the Write Postamble is satisfied.

Power-down is entered when CKE is registered LOW. If power-down occurs when there is a row active in any bank, this mode is referred to as active power-down. Entering power-down deactivates the input and output buffers, excluding CK,/CK and CKE. For maximum power savings, the user has the option of disabling the DLL prior to entering power-down. However, power-down duration is limited by the refresh requirements of the device, so in most applications, the self-refresh mode is preferred over the DLL-disabled power-down mode.

When in power-down, CKE LOW and a stable clock signal must be maintained at the inputs of the GDDR3 SDRAM, while all other input signals are "Don't Care" except data terminator disable command.

The power-down state is synchronously exited when CKE is registered HIGH (in conjunction with a NOP or DESELECT command). A valid executable command may be applied tPDEX later.

BA=Bank Address (if A8 is LOW; otherwise "Don't Care")

## **PRECHARGE Command**

### Power-Down

\* Once the device enters the power down mode, it should be in NOP state at least for 10ns. The minimum duration for the power down mode once CKE brought to down should be at least 10ns.

### **GDDR3 tFAW Definition**