Edited by Bill Travis

# Where is the wiper?

Chuck Wojslaw and Dave Gillooly, Catalyst Semiconductor, Sunnyvale, CA

OU ENJOY SIGNIFICANT advantages when using DPPs (digitally programmable potentiometers) with increment/decrement serial interfaces. Programming the serial interface is simple and fast, and you can adjust the potentiometer in real-time applications. The interface, however, provides no information about wiper position, and this information is important in some applications. If, for example, you use the potentiometer to control a parameter in a closed-loop, real-time application, the data reflecting the final wiper settings can be valuable in evaluating both the product performance and the circuit design. The circuit in Figure 1 keeps a digital record of the DPP's wiper position by using two presettable CD4029 up/down counters, IC, and IC<sub>3</sub>. The counters monitor the control signals  $\overline{INC}$  and  $U/\overline{D}$  of the DPP,  $IC_1$ .

During power-up, the wiper assumes position  $(00)_{10}$ , which it takes from previously programmed nonvolatile memory. Also during power-up, R<sub>1</sub> and C<sub>1</sub> differentiate the 5V power supply; this

| /here is the wiper?                                          | 107 |

|--------------------------------------------------------------|-----|

| LD code creates<br>WM generators                             | 108 |

| quare-wave modulator has variable<br>equency and pulse width | 110 |

| xpanded-scale indicator revisited                            | 112 |

| utterworth filter has adjustable<br>roup delay               | 114 |

| ingle transistor sequences<br>nultiple supplies              | 116 |

| 5 /                                                          |     |

5V 0 8 Figure 1 U/DO IC<sub>1</sub> CAT5113/5114 INC O CS O DB0 (LSB) O DB1 4 O DB2 5V 0 O DB3 C<sub>1</sub> 1 nF PE 15 10 15 10  $R_1$ 1k C 5 6 Q1  $IC_2$ • • DB4 4 11 Q2 0 DB5  $IC_3$ JAM1 12 CD4029BS 12 14 Q3 O DB6 14 13 JAM2 13 Q4 O DB7 (FLAG) 2 3 ЈАМЗ JAM4 1  $Q_5$ 7 Q BUS CO CI BIN/DEC 5V C PIN 16=V<sub>CC</sub>=5V PIN 8=Vss=0V

<sup>gn</sup>ideas

Two up/down counters keep track of a digitally programmable potentiometer's wiper position.

differentiated signal serves to preset the binary counters to  $(0000\ 0000)_2$ . Thus, the DPP and the external IC<sub>2</sub>/IC<sub>3</sub> counters are at the same point after power-up. The level-sensitive up/down signal establishes the direction of movement of the DPP's wiper and the direction of the count. The edge-sensitive INC signal advances both the wiper and the counter. The INC pin of the DPP responds to negative-edge triggering, and the clock input of the counter responds to positive-edge triggering. If the signal driving the INC line is a pulse (a common occurrence), the two inputs are compatible.

The Q outputs of the counters (DB0 to DB7) indicate in binary notation the location of the wiper. You can use the same circuit, using two counters, for

DPPs having as many as 256 taps. The DPP does not "wrap around" when the wiper advances to its upper or lower limit. The counters, however, do wrap around. To identify the case in which the digital counter is not in synch with the DPP, you can use the MSBs of the counters as flags. DB7 can serve as a flag for the 32-tap CAT5114 and the 100-tap CAT5113. You can change the initial count during power-up to something other than zero by preprogramming the DPP and setting high and low levels on the JAM inputs of the digital counters to the desired value.

# **PLD code creates PWM generators**

Clive Bolton, Bolton Engineering Inc, Melrose, MA

PLD (programmable-logic-HE device) code in Listing 1 creates arbitrary-resolution, pulse-widthmodulated (PWM) generators. PWM generators are useful as low-bandwidth D/A converters in hardware of microprocessor-based systems. When you pass it through a simple RC lowpass filter, a PWM waveform becomes a voltage that's approximately equal to the PWM duty cycle times the supply voltage. In practical systems, the driving hardware is imperfect, so the minimum value is never zero, and the maximum value never equals the positive-voltage rail.

The software module in **Listing 1** automatically generates the required hardware from two compile-time parameters: PWM\_WIDTH and AVALUE. PWM\_ WIDTH sets the number of possible steps in the PWM comparison. For example, 6 bits yields 2<sup>6</sup>, or 64, steps. AVALUE sets the value at which the PWM initializes upon power-up or reset (set to one-half scale in the example in **Listing 1**).

The module has two major sections: a holding register, which stores the PWM value, and a counter, which generates the PWM waveform. You can update the holding register independently of the PWM counter. The holding register's value automatically strobes into the PWM counter when the counter overflows. The module takes the CLOCK, ACLR, EN-ABLE, WRITE, and DATA[PWM] WIDTH-1..0] inputs. CLOCK is the master system clock; all signals other than ACLR must be synchronous with the clock's rising edge. ACLR initializes the hardware to the power-up state and loads AVALUE into the holding register. When ENABLE=0, the PWM output becomes 0 (off); when ENABLE=1, the PWM generator produces the PWM waveform at the Q output. Asserting WRITE for one clock cycle strobes the data presented on DATA[PWM\_ WIDTH-1..0] into the holding register. The PLD code uses Altera's (www. altera.com) AHDL high-level design language; you can directly compile the code

#### LISTING 1–AHDL CODE FOR PWM GENERATOR INCLUDE "LPH\_COUNTER.INC", INCLUDE "LPN COMPARE.INC"; INCLUDE "LPN FF.INC"; **PARAMETERS** PWM WIDTH -- Bits (set to 6 for testing) \* 6. -- Async reset value AVALUE - B\*100000\* 11 SUBDESIGN DWM INPUT; clock aclr INPUT; enable IMPUT - VCC -- seros PNM output INPUT: -- writes into write holding register data[PWM WIDTH-1..0] INPUT / OUTPUT: q period pulse OUIPUT; -- for debug and ext sync cout OUIPUT, VARTARLE. LPM COUNTER WITH (LPM WIDTH -PWM WIDTH, LPM DIRECTION - "DOWN") ; LPM COUNTER WITH (LPM\_WIDTH = PMM\_WIDTH. cntr LPM DIRECTION - "DOWN") ; pwm ff 8877. LPM FF WITH (LPM WIDTH - FWM WIDTH, pws\_reg LPH AVALUE = AVALUE); pwm\_preout period\_pulse NODE NODE -- for debug and ext sync cout NODE BEGIN ASSERT REFORT \*PMM WIDTH: \*\* PWM WIDTH SEVERITY INFO: \* PWN Holding Register \* pwm reg.clock - clock; pwm\_reg.aset - aclr: pwm\_reg.enable . write: pwm\_reg.data[] - data[]; \* PWH Counter \* = clock; cntr.clock cntr.aclr = aclr; cntr.cnt\_en = enable; period pulse = DFF(entr.cout, clock, !aclr, VCC); & FWM Counter & pwm.clock = clock; - aclr; pwm.aclr pwm.sload = cntr.cout; pwm.deta[] = pwm\_reg.q[]; - enable; pwm.cnt\_en cout = pwn.cout; & FWM Output F/F & pwm\_ff.clk = clock; pwm\_ff.clrn = imclr; pwm\_ff.s = !cout AND period pulse; -- turn FF on at beginning of interval. = cout OR !enable; pwm\_ff.r -- turn off at carry overflow. pwm\_precut = pwm\_ff.q; - DFF(enable AND pwm\_precut, à clock, lacir, VCC), END:

into any of Altera's PLDs. Using an EP1K10TC100-3 PLD, a design with parameters set to the default values in **List-ing 1** operates as fast as 139 MHz. Although we wrote the code for Altera's

devices, you can readily translate the design structure and flow into VHDL or Verilog. You can download **Listing 1** from the Web version of this Design Idea at www.edn.com. Is this the best Design Idea in this issue? Select at www.edn.com.

#### Square-wave modulator has variable frequency and pulse width

Michael Fisch, Agere Systems, Longmont, CO

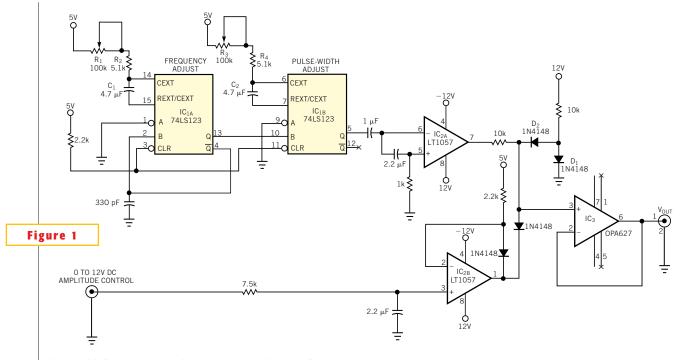

FEW YEARS AGO, I worked at a diskdrive company. We had a plating facility that required square waves to drive the high-voltage plating operation. The challenge was that the square wave's pulse width had to be variable, along with the duty cycle. Also, the amplitude of the pulses had to be adjustable. The circuit in **Figure 1** satisfies all these criteria. The circuit delivers a unipolar (adjustable from 0 to 12V) pulse with adjustable frequency and pulse width. The first half of a dual, retriggerable monostable multivibrator, IC<sub>1A</sub>, generates the frequency of the pulse train. The 100-k $\Omega$  potentiometer, R<sub>1</sub>, along with R<sub>2</sub> and C<sub>1</sub>, sets the adjustable frequency. R<sub>3</sub>, R<sub>4</sub>, and C<sub>2</sub> set the adjustable pulse width in the second section of the multivibrator, IC<sub>1B</sub>. The accoupled op amp, IC<sub>2A</sub>, running openloop, delivers a ±12V pulse output. D<sub>1</sub> and D<sub>2</sub> clamp the negative-going excursions of the pulse train to ground. The other half of the op amp,  $IC_{2B}$ , serves as a level shifter that allows amplitude control over the range 0 to 12V. You can modulate the amplitude at low frequency by varying the amplitude-control voltage.

This variable-frequency circuit allows amplitude modulation of its pulse-train output.

#### **Expanded-scale indicator revisited**

Abel Raynus, Armatron International Inc, Melrose, MA

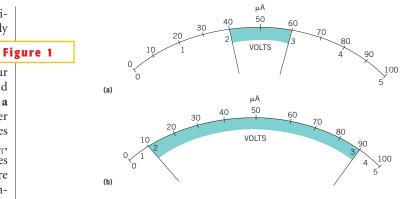

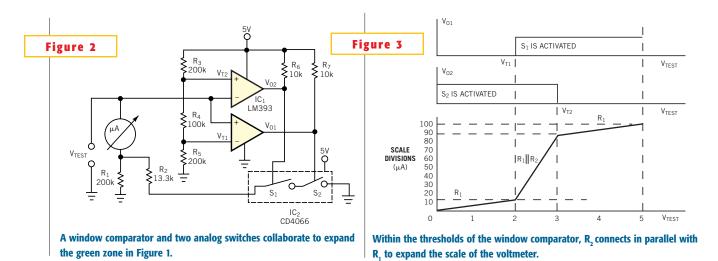

HE VISUALIZATION AID that a previous Design Idea describes allows only the expansion of the upper end of the scale (Reference 1). But what can you do if, according to your project requirements, you need to expand the middle region of the scale? Figure 1a illustrates the challenge. A voltmeter comprises a 100-µA dc meter and a series resistor. The voltage under test, V<sub>TEST</sub>, ranges from 0 to 5V. The voltage changes between 2 and 3V (the "green zone") are of interest. But at the same time, you cannot ignore the voltages from 0 to 2V and from 3 to 5V, and you need to be able to observe these voltages. With a linear scale, the green zone consumes only 20% of the full-scale range. Your objective is to expand this zone to 80%, leaving 10% at the lower end and 10% at the upper end of the scale (Figure 1b). The circuit in Figure 2 solves the problem. The window comparator, IC<sub>1</sub>, controls the variable impedance of the voltmeter. Analog switches S<sub>1</sub> and S<sub>2</sub> provide a contact-logic AND function and put resistor R, in parallel with R<sub>1</sub> only upon closure of both switches. This closure occurs when  $V_{TEST}$ is between the threshold voltages  $V_{T1}$  and  $V_{T_2}$  (**Figure 3**). You can calculate the re-

In a, the 2 to 3V "green zone" occupies only 20% of the scale; in b, this zone expands to 80%.

sistor values as follows:

$$R_{1} = \frac{2V}{10 \,\mu A} = 200 k\Omega;$$

$$R_{1} \| R_{2} = \frac{3 - 2V}{90 - 10 \,\mu A} = 12.5 k\Omega;$$

$$R_2 = \frac{R_1 \bullet R_1 \| R_2}{R_1 - R_1 \| R_2} = \frac{200 \bullet 12.5}{200 - 12.5} = 13.3 \text{ k}\Omega$$

You can calculate resistors  $R_3$ ,  $R_4$ , and  $R_5$  from the equations for the threshold voltages:

$$V_{T1} = \frac{R_5}{R_3 + R_4 + R_5} V_{CC};$$

$$V_{T2} = \frac{R_4 + R_5}{R_3 + R_4 + R_5} V_{CC}.$$

In this case,  $V_{CC} = 5V$ ,  $V_{T1} = 2V$ ,  $V_{T2} = 3V$ ; hence,  $R_3 = R_5 = 200 \text{ k}\Omega$ , and  $R_4 = 100 \text{ k}\Omega$ .

Reference

1. Raynus, Abel, "Indicator features expanded scale'" *EDN*, Feb 21, 2002, pg 86.

## Butterworth filter has adjustable group delay

William Stutz, Maxim Integrated Products, Sunnyvale, CA

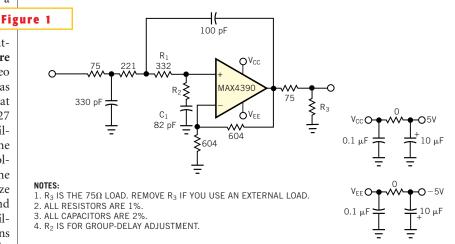

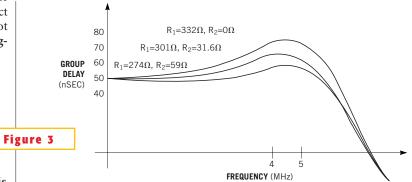

HE SALLEN-KEY REALIZATION OF a 5.25-MHz, three-pole Butterworth filter has a gain of 2V/V and can drive  $75\Omega$  back-terminated coax with an overall gain of 1 (Figure 1). Used to reconstruct component-video (Y, Pb, Pr) and RGB signals, this filter has an insertion loss greater than 20 db at 13.5 MHz and greater than 40 db at 27 MHz (Figure 2). Like the antialiasing filter before an ADC, this filter removes the higher frequency replicas of a signal following a DAC. To preserve quality in the video waveform, you should minimize group-delay variations in the filter and any group-delay differential between filters. That requirement mandates a means for adjusting the filter's group delay without affecting its bandwidth. In Figure 1, the addition of R<sub>2</sub> in series with C<sub>2</sub> and R<sub>3</sub> creates a lag-lead network.

Keeping the sum of R<sub>1</sub> and R<sub>2</sub> constant and equal to the original R<sub>1</sub> value preserves bandwidth by preserving **Figure 2** the dominant-pole frequency. Increasing the R<sub>1</sub> value, on the other hand, introduces a "lead" term that lowers group delay by reducing the rate of change in phase. For  $R_2=0\Omega$  and  $R_1 = 332\Omega$  in the circuit shown, the average group-delay variation over the filter bandwidth is about 25 nsec. Raising R, to 31.6 $\Omega$  and lowering R<sub>1</sub> to 301 $\Omega$  decreases the variation to approximately 15 nsec, and setting  $R_2 = 59\Omega$  with  $R_1 = 274\Omega$ decreases it to approximately 7 nsec. The last case has a less-than 0.5-dB effect on band-edge selectivity but does not change the filter's 3-dB bandwidth (Figure 3).

0 dB -20 -40 3' 6 6 1 6 6 1 3 6 6 1 3 100 MHz 100 Hz 10 kHz 1 MHz

Is this the best Design Idea in this issue? Select at www.edn.com.

Selected values of R<sub>1</sub> and R<sub>2</sub> allow control of group-delay variation over the filter's passband.

### Single transistor sequences multiple supplies

David Chen, Linear Technology Corp, Milpitas, CA

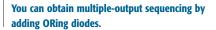

ANY DSP CHIPS, microprocessors, FPGAs, and ASICs require multiple power supplies that must deliver different voltages in a specific startup sequence. Out-of-sequence voltages can cause excessive input current, logic errors, or even device failure. To sequence different supplies, a common

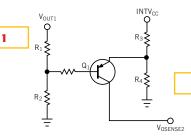

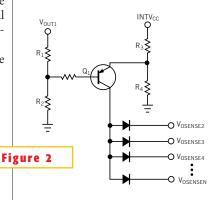

approach is to regulate a low-Figure 1er voltage from a higher voltage using a<br/>linear regulator. Another approach is to<br/>use a series of Schottky diodes. Although<br/>simple in concept, these approaches can<br/>be expensive and difficult to implement<br/>in applications that require more than<br/>two power supplies. Figure 1 shows a<br/>simple, low-cost approach that requires

only one pnp transistor to provide the necessary logic. **Figure 2** shows a dual power supply that uses the described circuitry to sequence the outputs.

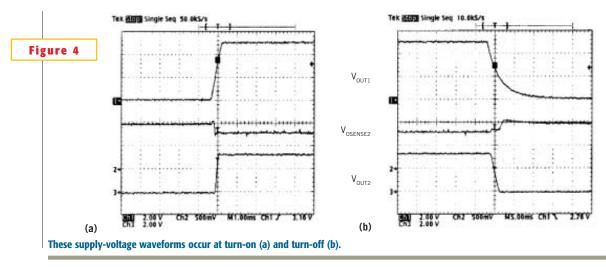

When  $V_{OUT1}$  is low,  $V_{OSENSE2}$ , the voltage

This dual-output supply uses the simple circuit in Figure 1.

feedback for  $V_{\rm OUT2}$ , goes high, and the second supply,  $V_{\rm OUT2}$ , shuts off (**Figure 3**). When  $V_{\rm OUT1}$  approaches its nominal level,  $Q_1$  turns off.  $Q_1$  then relinquishes control of  $V_{\rm OSENSE2}$ , and  $V_{\rm OUT2}$  resumes its normal start-up process. The process is similar for power-down sequencing. When  $V_{\rm OUT1}$  is high,  $V_{\rm OUT2}$  operates nor-

mally. When  $V_{\rm OUT1}$  goes from high to low,  $V_{\rm OSENSE2}$  goes high and shuts off  $V_{\rm OUT2}.$  More specifically,  $R_3$  and  $R_4$  set the clamping voltage for the  $V_{\rm OSENSE2}$  pin when  $V_{\rm OUT1}$  is low, and  $R_1$  and  $R_2$  determine the  $V_{\rm OUT1}$  voltage level at which  $Q_1$  turns off. In cases of multiple supplies, you need only add ORing diodes at the collector of

$Q_1$  (Figure 3). The design uses an LTC1628 dual-output controller. You can see the sequenced-output waveforms in Figures 4a (at turn-on) and 4b (at turn-off).