Evaluation Kit

Design Resources

and Models

Click here to ask an associate for production status of specific part numbers.

# DeepCover Secure Authenticator with 1-Wire SHA-256 with 4Kb User EEPROM

### **DS28EL25**

### **General Description**

DeepCover® embedded security solutions cloak sensitive data under multiple layers of advanced physical security to provide the industry's most secure key storage possible. The Deepcover Secure Authenticator (DS28EL25) combines crypto-strong, bidirectional, secure challengeand-response authentication functionality with an implementation based on the FIPS 180-3-specified Secure Hash Algorithm (SHA-256). A 4Kb user-programmable EEPROM array provides nonvolatile storage of application data and additional protected memory holds a readprotected secret for SHA-256 operations and settings for user memory control. Each device has its own guaranteed unique 64-bit ROM identification number (ROM ID) that is factory programmed into the chip. This unique ROM ID is used as a fundamental input parameter for cryptographic operations and also serves as an electronic serial number within the application. A bidirectional security model enables two-way authentication between a host system and slave-embedded DS28EL25. Slave-to-host authentication is used by a host system to securely validate that an attached or embedded DS28EL25 is authentic. Hostto-slave authentication is used to protect DS28EL25 user memory from being modified by a nonauthentic host. The SHA-256 message authentication code (MAC), which the DS28EL25 generates, is computed from data in the user memory, an on-chip secret, a host random challenge, and the 64-bit ROM ID. The DS28EL25 communicates over the single-contact 1-Wire® bus at overdrive speed. The communication follows the 1-Wire protocol with the ROM ID acting as node address in the case of a multiple-device 1-Wire network.

### **Applications**

- Authentication of Network-Attached Appliances

- Printer Cartridge ID/Authentication

- Reference Design License Management

- System Intellectual Property Protection

- Sensor/Accessory Authentication and Calibration

- Secure Feature Setting for Configurable Systems

- Key Generation and Exchange for Cryptographic Systems

#### **Features**

- Symmetric Key-Based Bidirectional Secure Authentication Model Based on SHA-256

- Dedicated Hardware-Accelerated SHA Engine for Generating SHA-256 MACs

- Strong Authentication with a High Bit Count, User-Programmable Secret, and Input Challenge

- 4096 Bits of User EEPROM Partitioned Into 16 Pages of 256 Bits

- User-Programmable and Irreversible EEPROM Protection Modes Including Authentication, Write and Read Protect, and OTP/EPROM Emulation

- Unique, Factory-Programmed 64-Bit Identification Number

- Single-Contact 1-Wire Interface Communicates with Host at Up to 76.9kbps

- Operating Range: 1.8V ±5%, -40°C to +85°C

- Low-Power 5μA (typ) Standby

- ±8kV Human Body Model ESD Protection (typ)

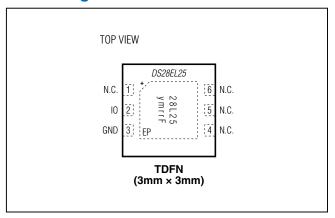

- 6-Pin TDFN Package

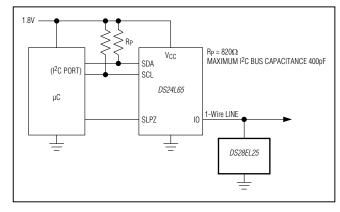

## **Typical Application Circuit**

Ordering Information appears at end of data sheet.

1-Wire and DeepCover are registered trademarks of Maxim Integrated Products, Inc.

219-0022; Rev 1; 6/21

## **DS28EL25**

# DeepCover Secure Authenticator with 1-Wire SHA-256 with 4Kb User EEPROM

#### **ABSOLUTE MAXIMUM RATINGS**

| IO Voltage Range to GND0.5V to 4.0V      | Storage Temperature Range55°C to +125°C |

|------------------------------------------|-----------------------------------------|

| IO Sink Current20mA                      | Lead Temperature (soldering, 10s)+300°C |

| Operating Temperature Range40°C to +85°C | Soldering Temperature (reflow)+260°C    |

| Junction Temperature +150°C              |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                                   | SYMBOL            | CONDITIONS                                | MIN TY              | P MAX            | UNITS |  |

|-------------------------------------------------------------|-------------------|-------------------------------------------|---------------------|------------------|-------|--|

| IO PIN: GENERAL DATA                                        |                   |                                           |                     |                  |       |  |

| 1-Wire Pullup Voltage                                       | V <sub>PUP</sub>  | (Note 2)                                  | 1.71                | 1.89             | V     |  |

| 1-Wire Pullup Resistance                                    | R <sub>PUP</sub>  | V <sub>PUP</sub> = 1.8V ±5% (Note 3)      | 300                 | 750              | Ω     |  |

| Input Capacitance                                           | C <sub>IO</sub>   | (Notes 4, 5)                              | 150                 | 00               | pF    |  |

| Input Load Current                                          | ΙL                | IO pin at V <sub>PUP</sub>                | 5                   | 19.5             | μA    |  |

| High-to-Low Switching Threshold                             | V <sub>TL</sub>   | (Notes 6, 7)                              | 0.65 x              | V <sub>PUP</sub> | V     |  |

| Input Low Voltage                                           | V <sub>IL</sub>   | (Notes 2, 8)                              |                     | 0.3              | V     |  |

| Low-to-High Switching Threshold                             | V <sub>TH</sub>   | (Notes 6, 9)                              | 0.75 x              | V <sub>PUP</sub> | V     |  |

| Switching Hysteresis                                        | V <sub>HY</sub>   | (Notes 6, 10)                             | 0.3                 | 3                | V     |  |

| Output Low Voltage                                          | V <sub>OL</sub>   | I <sub>OL</sub> = 4mA (Note 11)           |                     | 0.4              | V     |  |

| Recovery Time                                               | t <sub>REC</sub>  | R <sub>PUP</sub> = 750Ω (Notes 2, 12)     | 5                   |                  | μs    |  |

| Time-Slot Duration                                          | t <sub>SLOT</sub> | (Notes 2, 13)                             | 13                  |                  | μs    |  |

| IO PIN: 1-Wire RESET, PRESENC                               | E-DETECT          | CYCLE                                     |                     |                  |       |  |

| Reset Low Time                                              | t <sub>RSTL</sub> | (Note 2)                                  | 48                  | 80               | μs    |  |

| Reset High Time                                             | t <sub>RSTH</sub> | (Note 14)                                 | 48                  |                  | μs    |  |

| Presence-Detect Sample Time                                 | t <sub>MSP</sub>  | (Notes 2, 15)                             | 8                   | 10               | μs    |  |

| IO PIN: 1-Wire WRITE                                        |                   |                                           |                     |                  |       |  |

| Write-Zero Low Time                                         | t <sub>WOL</sub>  | (Notes 2, 16)                             | 8                   | 16               | μs    |  |

| Write-One Low Time                                          | t <sub>W1L</sub>  | (Notes 2, 16)                             | 0.25                | 2                | μs    |  |

| IO PIN: 1-Wire READ                                         |                   |                                           |                     |                  |       |  |

| Read Low Time                                               | t <sub>RL</sub>   | (Notes 2, 17)                             | 0.25                | 2 - δ            | μs    |  |

| Read Sample Time                                            | t <sub>MSR</sub>  | (Notes 2, 17)                             | t <sub>RL</sub> + δ | 2                | μs    |  |

| EEPROM                                                      |                   |                                           |                     |                  |       |  |

| Programming Current                                         | I <sub>PROG</sub> | V <sub>PUP</sub> = 1.89V (Notes 5, 18)    |                     | 1                | mA    |  |

| Programming Time for a 32-Bit<br>Segment or Page Protection | t <sub>PRD</sub>  | (Note 19)                                 |                     | 10               | ms    |  |

| Programming Time for the Secret                             | t <sub>PRS</sub>  | Refer to the full data sheet.             |                     | 200              | ms    |  |

| Write/Erase Cycling Endurance                               | N <sub>CY</sub>   | T <sub>A</sub> = +85°C (Notes 21, 22)     | 100k                | -                | _     |  |

| Data Retention                                              | t <sub>DR</sub>   | T <sub>A</sub> = +85°C (Notes 23, 24, 25) | 10                  |                  | Years |  |

#### **DS28EL25**

# DeepCover Secure Authenticator with 1-Wire SHA-256 with 4Kb User EEPROM

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER           | SYMBOL            | CONDITIONS                    | MIN | TYP | MAX | UNITS |

|---------------------|-------------------|-------------------------------|-----|-----|-----|-------|

| SHA-256 ENGINE      |                   |                               |     |     |     |       |

| Computation Current | I <sub>CSHA</sub> | Refer to the full data sheet. |     |     | 1   | mA    |

| Computation Time    | tcsha             | Refer to the full data sheet. |     |     | 3   | ms    |

- **Note 1:** Limits are 100% production tested at  $T_A = +25^{\circ}$ C and/or  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.

- Note 2: System requirement.

- **Note 3:** Maximum allowable pullup resistance is a function of the number of 1-Wire devices in the system and 1-Wire recovery times. The specified value here applies to systems with only one device and with the minimum 1-Wire recovery times.

- **Note 4:** Typical value represents the internal parasite capacitance when V<sub>PUP</sub> is first applied. Once the parasite capacitance is charged, it does not affect normal communication.

- Note 5: Guaranteed by design and/or characterization only; not production tested.

- **Note 6:** V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub> are a function of the internal supply voltage, which is a function of V<sub>PUP</sub>, R<sub>PUP</sub>, 1-Wire timing, and capacitive loading on IO. Lower V<sub>PUP</sub>, higher R<sub>PUP</sub>, shorter t<sub>REC</sub>, and heavier capacitive loading all lead to lower values of V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub>.

- Note 7: Voltage below which, during a falling edge on IO, a logic-zero is detected.

- Note 8: The voltage on IO must be less than or equal to V<sub>ILMAX</sub> at all times when the master is driving IO to a logic-zero level.

- Note 9: Voltage above which, during a rising edge on IO, a logic-one is detected.

- Note 10: After  $V_{TH}$  is crossed during a rising edge on IO, the voltage on IO must drop by at least  $V_{HY}$  to be detected as logic-zero.

- Note 11: The I-V characteristic is linear for voltages less than 1V.

- Note 12: Applies to a single device attached to a 1-Wire line.

- Note 13: Defines maximum possible bit rate. Equal to 1/(t<sub>W0LMIN</sub> + t<sub>RECMIN</sub>).

- Note 14: An additional reset or communication sequence cannot begin until the reset high time has expired.

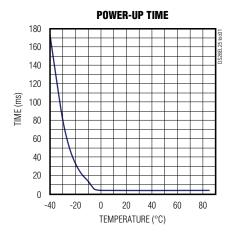

- Note 15: Interval after t<sub>RSTL</sub> during which a bus master can read a logic 0 on IO if there is a DS28EL25 present. The power-up presence detect pulse could be outside this interval. See the *Typical Operating Characteristics* for details.

- Note 16:  $\epsilon$  in Figure 11 represents the time required for the pullup circuitry to pull the voltage on IO up from V<sub>IL</sub> to V<sub>TH</sub>. The actual maximum duration for the master to pull the line low is  $t_{W1LMAX} + t_F \epsilon$  and  $t_{W0LMAX} + t_F \epsilon$ , respectively.

- Note 17:  $\delta$  in Figure 11 represents the time required for the pullup circuitry to pull the voltage on IO up from  $V_{IL}$  to the input-high threshold of the bus master. The actual maximum duration for the master to pull the line low is  $t_{RLMAX} + t_{F}$ .

- Note 18: Current drawn from IO during the EEPROM programming interval or SHA-256 computation. The pullup circuit on IO during the programming and computation interval should be such that the voltage at IO is greater than or equal to V<sub>PUPMIN</sub>. A low-impedence bypass of R<sub>PUP</sub> activated during programming and computation is the recommended way to meet this requirement.

- Note 19: Refer to the full data sheet.

#### Note 20: Refer to the full data sheet.

- Note 21: Write-cycle endurance is tested in compliance with JESD47G.

- Note 22: Not 100% production tested; guaranteed by reliability monitor sampling.

- Note 23: Data retention is tested in compliance with JESD47G.

- **Note 24:** Guaranteed by 100% production test at elevated temperature for a shorter time; equivalence of this production test to the data sheet limit at operating temperature range is established by reliability testing.

- **Note 25:** EEPROM writes can become nonfunctional after the data retention time is exceeded. Long-term storage at elevated temperatures is not recommended.

## **DS28EL25**

DeepCover Secure Authenticator with 1-Wire SHA-256 with 4Kb User EEPROM

## **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) \text{ (Note 1)}$

Note 26: Refer to the full data sheet.

## **Typical Operating Characteristics**

$(V_{PUP} = 1.71V, V_{IL} = 0.3V)$

## **Pin Configuration**

## **Pin Description**

| PIN           | NAME | FUNCTION                                                                                                                                                                                       |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3             | GND  | Ground Reference                                                                                                                                                                               |

| 2             | Ю    | 1-Wire Bus Interface. Open-drain signal that requires an external pullup resistor.                                                                                                             |

| 1, 4,<br>5, 6 | N.C. | Not Connected                                                                                                                                                                                  |

| _             | EP   | Exposed Pad (TDFN only). Solder evenly to the board's ground plane for proper operation. Refer to Application Note 3273: <i>Exposed Pads: A Brief Introduction</i> for additional information. |

**DS28EL25**

DeepCover Secure Authenticator with 1-Wire SHA-256 with 4Kb User EEPROM

**Note to readers:** This document is an abridged version of the full data sheet. Additional device information is available only in the full version of the data sheet. To request the full data sheet, go to <a href="https://www.maximintegrated.com/DS28EL25">www.maximintegrated.com/DS28EL25</a> and click on **Request Full Data Sheet**.

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE           |

|-------------|----------------|-----------------------|

| DS28EL25Q+T | -40°C to +85°C | 6 TDFN-EP* (2.5k pcs) |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE   | PACKAGE | OUTLINE | LAND        |

|-----------|---------|---------|-------------|

| TYPE      | CODE    | NO.     | PATTERN NO. |

| 6 TDFN-EP | T633+2  | 21-0137 | 90-0058     |

T = Tape and reel.

<sup>\*</sup>EP = Exposed pad.

## **DS28EL25**

# DeepCover Secure Authenticator with 1-Wire SHA-256 with 4Kb User EEPROM

## **Revision History**

| REVISION NUMBER | REVISION<br>DATE | DESCRIPTION                                                    | PAGES<br>CHANGED |

|-----------------|------------------|----------------------------------------------------------------|------------------|

| 0               | 12/12            | Initial release                                                | _                |

| 1               | 6/21             | Updated Electrical Characteristics table, Detailed Description | 2, 32            |