## DS80CH11 System Energy Manager

# **PRODUCT SPECIFICATION**

V2.1

011200 1/88

# TABLE OF CONTENTS

| 1.0 | GENE   | RAL DESCRIPTION                                 |

|-----|--------|-------------------------------------------------|

|     | 1.1    | OVERVIEW                                        |

|     | 1.2    | DETAILED FEATURE SUMMARY                        |

|     | 1.3    | CONVENTIONS                                     |

|     | 1.4    | ADDITIONAL REFERENCES                           |

| 2.0 | PIN DE | 8 SCRIPTION                                     |

|     | 2.1    | PIN FUNCTION SUMMARY                            |

|     | 2.2    | PIN CHARACTERISTICS                             |

| 3.0 | CORE   | MICROCONTROLLER                                 |

|     | 3.1    | CORE MICRO OVERVIEW                             |

|     | 3.2    | INSTRUCTION SET SUMMARY                         |

|     | 3.3    | SPEED IMPROVEMENT                               |

|     | 3.4    | INSTRUCTION SET ADDITIONAL REFERENCES           |

|     | 3.5    | RESET                                           |

|     | 3.6    | INTERRUPT CONTROL                               |

| 4.0 | МЕМО   | <b>RY RESOURCES</b>                             |

|     | 4.1    | OVERVIEW                                        |

|     | 4.2    | DATA MEMORY ACCESS                              |

|     |        | 4.2.1 Stretch Memory Cycle                      |

|     |        | 4.2.2 Dual Data Pointer                         |

|     | 4.3    | EXTERNAL MEMORY INTERFACE                       |

|     | 4.4    | DIRECT (SCRATCHPAD) RAM ACCESS                  |

|     | 4.5    | SPECIAL FUNCTION REGISTERS                      |

| 5.0 | CORE   | <b>I/O RESOURCES</b>                            |

|     | 5.1    | PROGRAMMABLE TIMERS                             |

|     | 5.2    | SERIAL PORTS                                    |

|     | 5.3    | WATCHDOG TIMER                                  |

|     | 5.4    | PARALLEL I/O PORTS                              |

|     |        | 5.4.1 Alternate Pin Function Summary            |

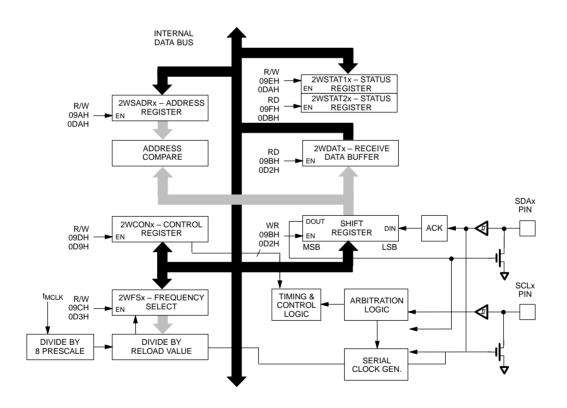

| 6.0 | 2–Wire | SERIAL INTERFACE                                |

|     | 6.1    | INTRODUCTION                                    |

|     | 6.2    | REGISTER DESCRIPTION                            |

|     |        | 6.2.1 2WFSx – 2–Wire Frequency Select Registers |

|     |        | 6.2.2 2WDATx - 2-Wire Data I/O Registers        |

|     |        | 6.2.3 2WSADRx – 2–Wire Slave Address Registers  |

|     |        | 6.2.4 2WCONx – 2–Wire Control Registers         |

|     |        | 6.2.5 2WSTAT1x – 2–Wire Status Register 1       |

|     |        | 6.2.6 2WSTAT2x – 2–Wire Status Register 2       |

|     | 6.3    | OPERATION DESCRIPTION                           |

|     |        | 6.3.1 Master Transmit                           |

|     |        | 6.3.2 Master Receive                            |

|     |        | 6.3.3 Slave Receive                             |

|     |        |                                                 |

|      |            | 6.3.4 Slave Transmit                                                |   |

|------|------------|---------------------------------------------------------------------|---|

| 7.0  |            | 6.3.5 Bus Monitor Mode Operation                                    |   |

| 7.0  |            |                                                                     |   |

|      | 7.1        |                                                                     |   |

|      | 7.2        | ANALOG POWER / SLEEP MODE                                           |   |

|      | 7.3        |                                                                     |   |

|      | 7.4        | SAR A/D CONVERTER                                                   |   |

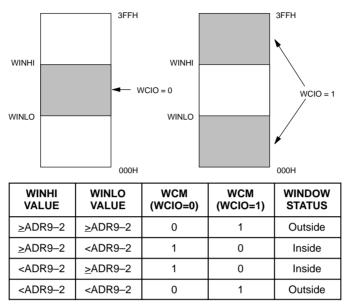

|      | 7.5<br>7.6 | WINDOW COMPARATOR                                                   | - |

|      | 7.6<br>7.7 | A/D OPERATION                                                       |   |

|      | 7.8        | A/D SPECIAL FUNCTION REGISTERS                                      |   |

|      | 1.0        | 7.8.1 ADCON1 – A/D Control Register 1                               |   |

|      |            | 7.8.2 ADCON1 – A/D Control Register 2                               |   |

|      |            | 7.8.3 ADMSB – A/D Result Most Significant Byte                      |   |

|      |            | 7.8.4 ADLSB – A/D Result Least Significant Byte                     |   |

|      |            | 7.8.5 WINHI – A/D Window Comparator High Byte                       |   |

|      |            | 7.8.6 WINLO – A/D Window Comparator Low Byte                        |   |

| 8.0  |            | /ITY MONITOR/LED CONTROL                                            |   |

| 0.0  | 8.1        | OVERVIEW                                                            |   |

|      | 8.2        |                                                                     |   |

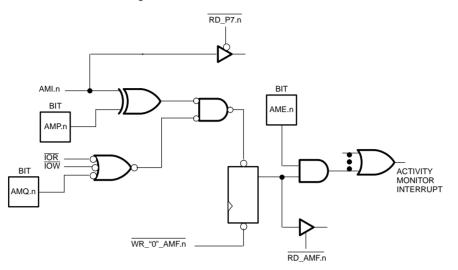

|      | o.∠<br>8.3 | AME – ACTIVITY MONITOR ENABLE REGISTER                              | - |

|      | 8.4        | AMQ – ACTIVITY MONITOR QUALIFIER REGISTER                           |   |

|      | 8.5        | AMP – ACTIVITY MONITOR QUALITER REGISTER                            |   |

|      | 8.6        | AMF – ACTIVITY MONITOR FLAG REGISTER                                |   |

|      | 8.7        | LED CONTROL                                                         |   |

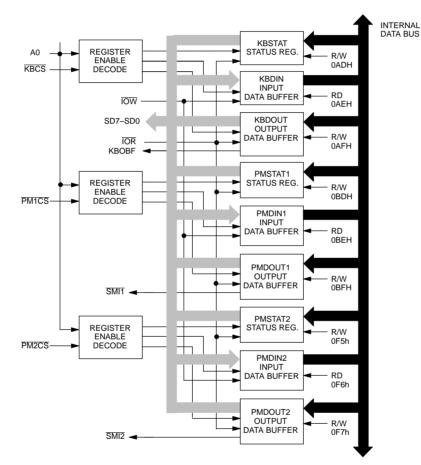

| 9.0  | -          |                                                                     |   |

| 3.0  | 9.1        | OVERVIEW                                                            |   |

|      | 9.2        |                                                                     |   |

|      | 9.3        | KBOIN / PMDIN – DATA REGISTERS                                      |   |

|      | 9.4        | KBSTAT / PMSTAT – STATUS REGISTERS                                  |   |

|      | 9.5        | KBDOUT / PMDOUT – OUTPUT DATA REGISTERS                             |   |

| 10.0 |            | OARD SCANNING PORTS                                                 |   |

| 10.0 | 10.1       | OVERVIEW                                                            |   |

|      | 10.1       | KEY SCAN OUTPUTS                                                    |   |

|      | 10.2       | KEY SCAN INPUTS                                                     |   |

|      | 10.4       | KDE – KEY DETECT ENABLE REGISTER                                    |   |

|      | 10.5       | KDF – KEYBOARD DETECT FLAG REGISTER                                 |   |

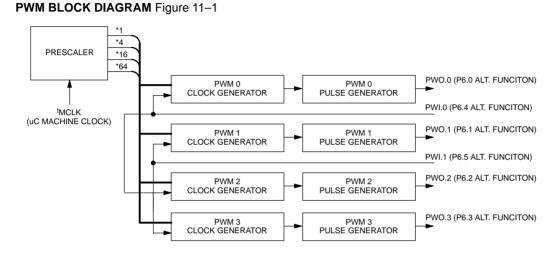

| 11.0 |            | E WIDTH MODULATORS                                                  |   |

|      | 11.1       |                                                                     |   |

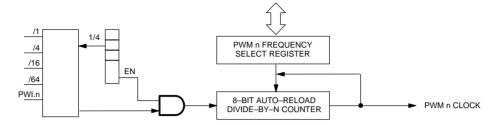

|      | 11.2       | PRESCALER                                                           |   |

|      | 11.3       | PWM CLOCK GENERATORS                                                |   |

|      | 11.4       | PWM PULSE GENERATORS                                                |   |

|      | 11.5       | PWM SPECIAL FUNCTION REGISTERS                                      |   |

|      |            | 11.5.1 PW01CS / PW23CS – PWM 0, 1 / PWM 2, 3 Clock Select Registers |   |

|      |            | 11.5.2 PW01CON / PW23CON – PWM 0, 1 / PWM 2, 3 Control Register     |   |

|      |            | 11.5.3 PWnFG – PWM n Frequency Generator Registers                  |   |

|      |            | 11.5.4 PWMn – PWM n Value Registers                                 |   |

| 12.0 | MICRO      | OCONTROLLER POWER MANAGEMENT                                        |   |

|      | 12.1       | POWER-DOWN / POWER-UP OPERATION                                     |   |

|      |            |                                                                     |   |

011200 3/88

|      |         | 12.1.1   | Microcontroller Power Fail Reset          | 66 |

|------|---------|----------|-------------------------------------------|----|

|      | 12.2    | LOW PO   | OWER OPERATING MODES                      | 66 |

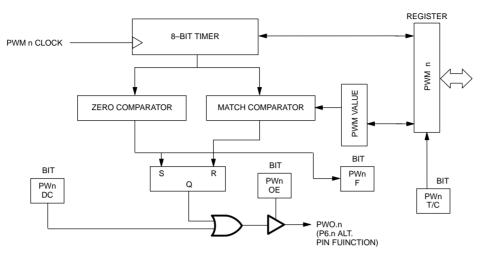

|      |         | 12.2.1   | Slow Clock Mode                           | 66 |

|      |         | 12.2.1.1 | Crystaless Slow Clock Mode                | 67 |

|      |         | 12.2.1.2 | Slow Clock Mode Operation                 | 67 |

|      |         | 12.2.1.3 | Clock Divider                             | 67 |

|      |         | 12.2.1.4 | Switchback                                | 68 |

|      |         | 12.2.1.5 | Status                                    | 68 |

|      |         | 12.2.1.6 | Crystal / Ring Operation                  | 68 |

|      |         | 12.2.2   | Idle Mode                                 | 71 |

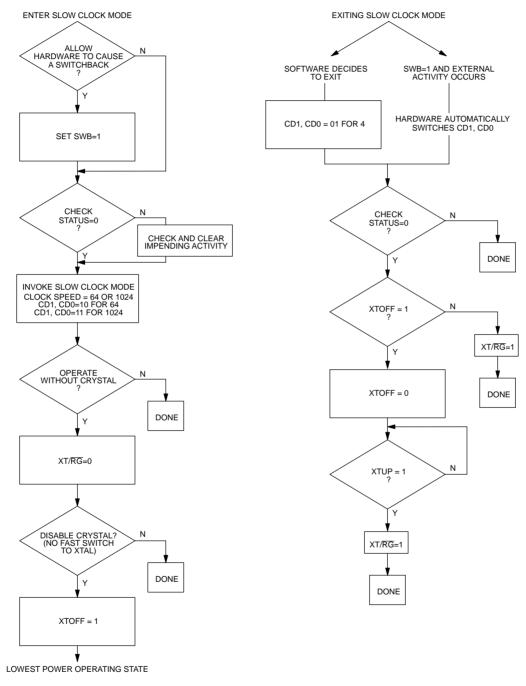

|      |         | 12.2.3   | Stop Mode and Enhancements                | 71 |

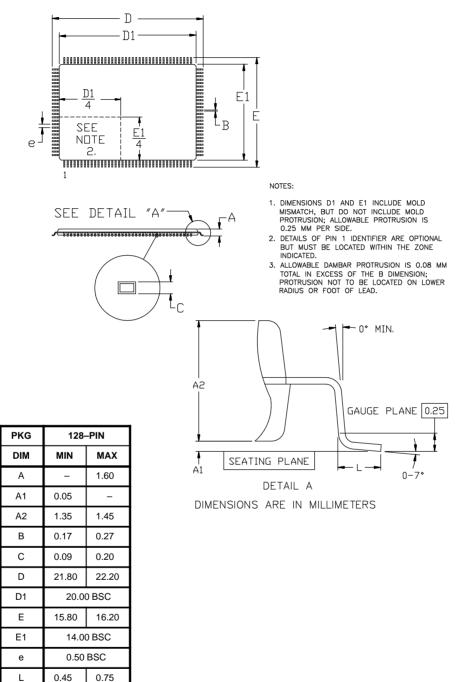

| 13.0 | +5.0V E | ELECTRI  | CAL SPECIFICATIONS                        | 74 |

|      | 13.1    | ABSOL    | JTE MAXIMUM RATINGS*                      | 74 |

|      | 13.2    | MICRO    | CONTROLLER DC ELECTRICAL CHARACTERISTICS  | 74 |

|      | 13.3    | MICRO    | CONTROLLER AC ELECTRICAL CHARACTERISTICS  | 76 |

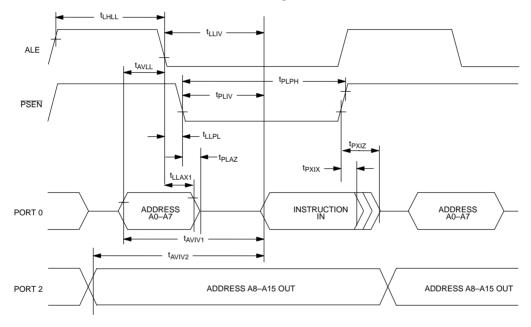

|      |         | 13.3.1   | External Program Memory Characteristics   | 76 |

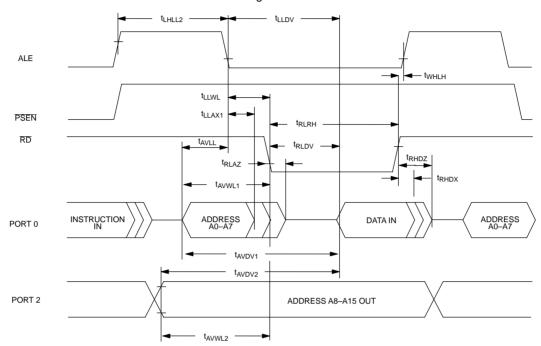

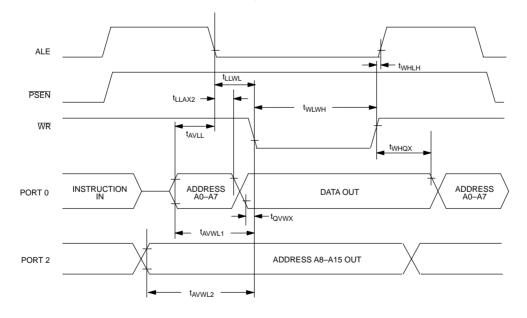

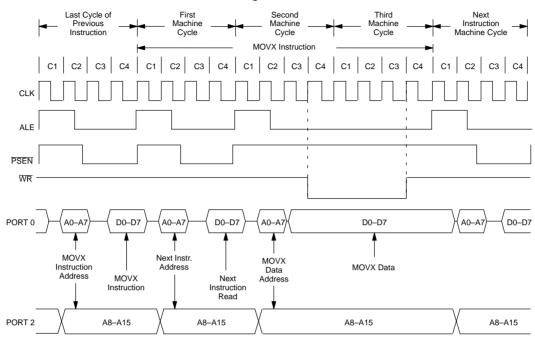

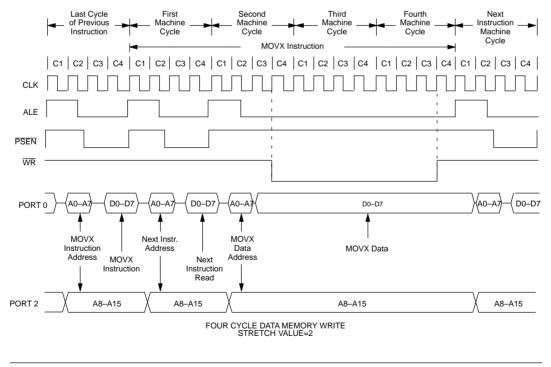

|      |         | 13.3.2   | MOVX Using Stretch Memory Cycles          | 77 |

|      |         | 13.3.3   | External Clock Characteristics            | 78 |

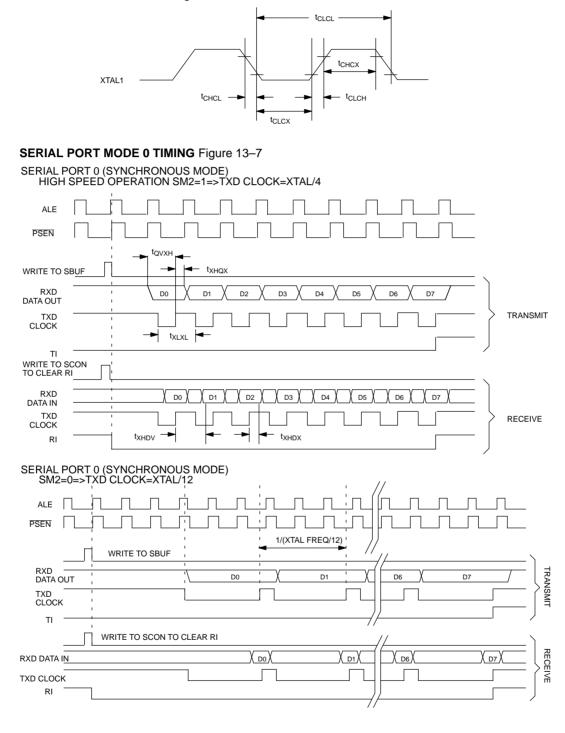

|      |         | 13.3.4   | Serial Port Mode 0 Timing Characteristics | 78 |

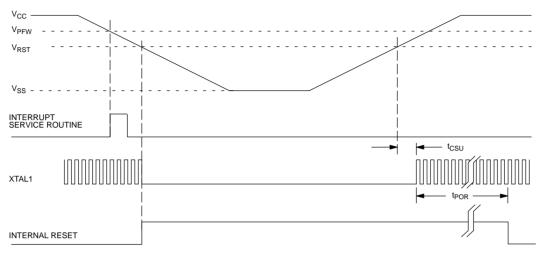

|      |         | 13.3.5   | Power Cycle Timing Characteristics        | 79 |

|      | 13.4    | SYSTEM   | MINTERFACE DC ELECTRICAL CHARACTERISTICS  | 83 |

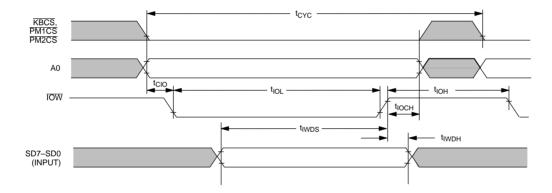

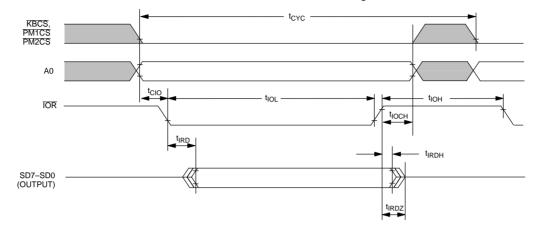

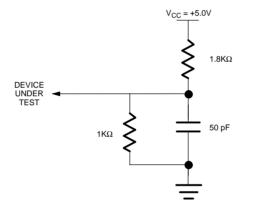

|      | 13.5    | HOST I/  | F AC TIMING CHARACTERISTICS               | 84 |

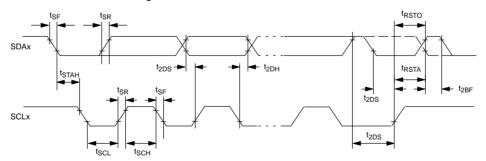

|      | 13.6    | 2–Wire   | AC TIMING CHARACTERISTICS                 | 86 |

|      | 13.7    | A/D CO   | NVERTER SPECIFICATIONS                    | 87 |

|      |         | 13.7.1   | Absolute Maximum Ratings                  | 87 |

|      |         | 13.7.2   | A/D Electrical Characteristics            | 87 |

|      |         |          |                                           |    |

011200 4/88

#### 1.0 GENERAL DESCRIPTION

#### 1.1 OVERVIEW

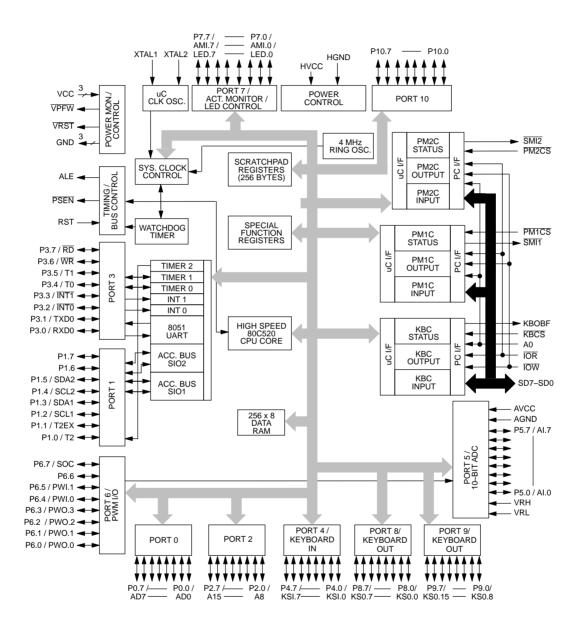

The System Energy Manager is a highly integrated microcontroller that provides several key features for systems including key scanning and control, battery and power management, as well as two 2–Wire serial I/O Ports. It incorporates the Dallas 8051–compatible high–speed microcontroller core which has been redesigned to eliminate wasted clock and memory cycles. Every standard 8051 instruction is executed between 1.5 and 3 times faster than the original for the same crystal speed. Looking at it another way, the high–speed core achieves the same throughput as a standard 8051 while using much less power as a result of fewer required clock cycles. As a result, the firmware can easily support many tasks required by mobile systems within a single component.

The controller is designed to off–load battery and power management tasks from the host CPU and thereby make possible an efficient solution for systems. In addition to the microcontroller core, it incorporates an 8–channel, 10–bit A/D converter with external reference so that its firmware can perform battery management tasks without burdening the host CPU. A fourchannel 8-bit pulse-width modulator allows digital control of functions such as LCD contrast and brightness. An 8-bit port is provided for key scan inputs. A total of 88 parallel I/O pins are available for key scanning, system configuration, and power management control.

The System Energy Manager scans a key matrix and interfaces to the host CPU via an 8042–compatible port. The benefits of sophisticated power management and permanently powered functions are thereby attained without adding to the system's chip count.

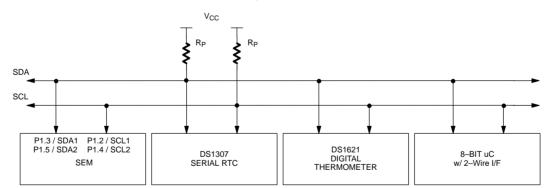

Two 2–wire, bi–directional serial buses are incorporated to facilitate the management of slave peripheral devices on the motherboard, such as digital temperature sensors and potentiometers, and to support external low–speed I/O devices such as monitor configuration channels, pen tablets, and joysticks.

Because a direct interface to the X–bus is provided, the controller is not dependent on a particular core logic chip or chip set. Independent chip select inputs for the keyboard controller, power management #1, and power management #2 registers are provided.

#### CONTROLLER BLOCK DIAGRAM Figure 1-1

011200 6/88

#### 1.2 DETAILED FEATURE SUMMARY

#### • High Speed 80C32 Compatible Core:

- High performance 4 clocks / machine cycle (8032 = 12)

- Low Power: typically 1/3 power for equivalent 8032 throughput

- Maximum clock speed up to 25 MHz at 5.0V

- Ultra–low stop mode power (typ. 1 uA) and "IDLE" mode (typ. 10 mA)

- Multiple wake–up sources from STOP including key scan, 2–wire, host I/F, or external interrupt

- Three 16-bit timers, 1 serial port

- 256 byte scratchpad

- 256 bytes MOVX RAM

#### • Keyboard Control:

- Replaces 8042 and key scan microcontroller

- 2 Parallel I/O ports for key scan outputs

- One interrupt–driven 8–bit input port to initiate key–scan sequence

#### • Input/Output:

- Total of eleven 8-bit I/O ports; all pins can be individually programmed to serve as general purpose digital input/output.

- Each 8-bit port supports one or more special functions:

- Port 0, 2, 3: External program / data memory interface

Port 1, 3: UART, 2–Wire serial, timers, and external interrupt I/O.

- Port 4, 8, 9: Key scan input / output

- Port 5: A/D inputs

- Port 6: PWM Outputs

- Port 7: Activity monitor, LED Control Port 10: GPIO

#### Analog Input/Output:

Eight–channel, 10–bit A/D with power down mode supports charging NiMH rechargeable cells  4-channel, 8-bit PWM supports LCD brightness and contrast control

#### • 2–Wire Bi–directional Serial Buses

- Master/slave multi-drop operation

- Manages on-board slaves or external I/O devices

#### Power Control

- Generates system power on reset

- Programmable power down pin states

#### **1.3 CONVENTIONS**

The following conventions are used throughout this specification:

- "SEM" is the short form name used to indicate the System Energy Manager.

- Signals that are active low are followed by a pound symbol (#) or backslash (\), or are indicated with an overbar.

- If a range of signals is described, such as SA0 through SA10, the range is given as SA10–0, with the most– significant digit first and the least–significant digit last, separated by a hyphen.

- Numbers written in this specification can be written as decimal, hexadecimal, or binary. Hexadecimal numbers are followed by an "H" suffix. Binary numbers are followed by a "B" suffix. For example, decimal 27 = 1BH = 00011011B.

#### 1.4 ADDITIONAL REFERENCES

The SEM incorporates the Dallas 8051 compatible High Speed Micro core including the CPU and many of its core peripherals. The operational details of these elements are contained in the Dallas High Speed Micro User's Guide.

#### 2.0 PIN DESCRIPTION

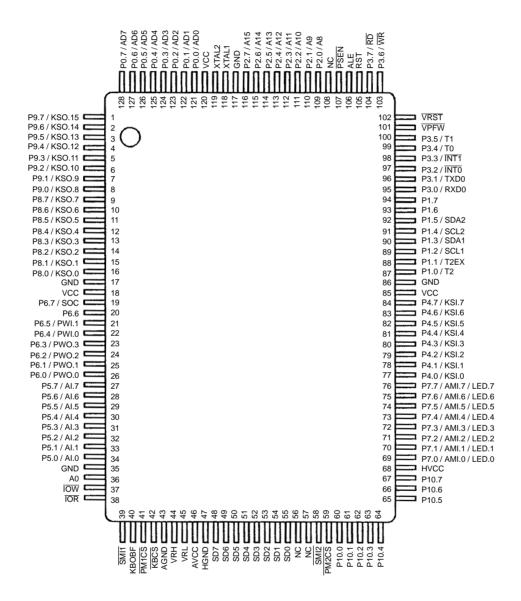

#### 128-TQFP PIN ASSIGNMENT Figure 2-1

011200 8/88

#### **PIN FUNCTION SUMMARY** 2.1 PIN SYMBOL DESCRIPTION 36 A0 Command / Data Select: Input. Address input used by the host processor in data transfers to the keyboard controller and power management #1 and #2 interface ports to indicate whether the transfer is command (A0=1) or data (A0=0). 43 AGND Analog Ground. 106 ALE Address Latch Enable: Output. This signal functions as a clock to latch the external address LSB from the multiplexed address/data bus on Port 0. This signal is commonly connected to the latch enable of an external 373 family transparent latch. ALE has a pulse width of 1.5 XTAL1 cycles and a period of 4 XTAL1 cycles. ALE is forced high when the SEM is in a Reset condition. AVCC 46 Analog VCC. 17 GND Digital circuit ground. 35 86 117 47 HGND Host Interface Ground: 68 HVCC Host Interface VCC: IOR 38 I/O Read: Input. I/O Read is used to signal a read operation is in effect on the host address/data bus. IOW 37 I/O Write: Input. I/O Write is used to signal a write operation is in effect on the host address/data bus. KBCS 42 Keyboard Chip Select: (Input, active low). This is a chip select signal used to enable the keyboard control host interface port. KBOBF Keyboard Output Buffer Full: (Output, active high). This signal is set when the key-40 board control host interface data buffer contains data to be read by the host. KBOBF will be driven low when host reads the keyboard control data buffer register. 56 NC No Connection. 57 108 121 P0.0 (AD0) Port 0 / Address/Data Outputs 7-0: I/O. Port 0 is an open-drain 8-bit bi-directional P0.1 (AD1) I/O port. As an alternate function Port 0 can function as the multiplexed address/data 122 P0.2 (AD2) bus to access off-chip memory. During the time when ALE is high, the LSB of a memory 123 124 P0.3 (AD3) address is presented. When ALE falls to a logic 0, the port transitions to a bi-directional 125 P0.4 (AD4) data bus. This bus is used to read external ROM and read/write external RAM memory P0.5 (AD5) or peripherals. When used as a memory bus, the port provides active high drivers. The 126 127 P0.6 (AD6) reset condition of Port 0 is tri-state. Pull-up resistors are required when using Port 0 as P0.7 (AD7) 128 an I/O port.

| PIN                                                  | SYMBOL                                                                                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 87<br>88<br>89<br>90<br>91<br>92<br>93<br>94         | P1.0 (T2)<br>P1.1 (T2EX)<br>P1.2 SCL1<br>P1.3 SDA1<br>P1.4 SCL2<br>P1.5 SDA2<br>P1.6<br>P1.7                                 | Port 1/ (Alternate Functions): – I/O. Port 1 provides eight lines which can be individually selected as bi–directional I/O port pins or as the alternate functions listed below:         Alternate         Port       Function       Description         P1.0       T2       External I/O for Timer/Counter 2         P1.1       T2EX       Timer/Counter 2 Capture/Reload Trigger         P1.2       SCL1       2–Wire Serial Clock 1         P1.3       SDA1       2–Wire Serial Data 1         P1.4       SCL2       2–Wire Serial Clock 2         P1.5       SDA2       2–Wire Serial Data 2         P1.6       (None)         P1.7       (None)         Note that P1.7 – P1.2 are high–drive pins which are always open–drain and must be used with external pull–ups when used as I/O port pins. P1.1 and P1.0 have internal pull–up resistors. |

| 109<br>110<br>111<br>112<br>113<br>114<br>115<br>116 | P2.0 (A8)<br>P2.1 (A9)<br>P2.2 (A10)<br>P2.3 (A11)<br>P2.4 (A12)<br>P2.5 (A13)<br>P2.6 (A14)<br>P2.7 (A15)                   | <b>Port 2 / Address Outputs A15–8:</b> – I/O. Port 2 is a pseudo–bi–directional I/O port with internal pull–up resistors. As an alternate function Port 2 can function as MSB of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 95<br>96<br>97<br>98<br>99<br>100<br>103<br>104      | P3.0(RXD0)<br>P3.1 (TXD0)<br>P3.2 (INT0)<br>P3.3 (INT1)<br>P3.4 (T0)<br>P3.5 (T1)<br>P3.6 (WR)<br>P3.7 (RD)                  | Port 3 / (Alternate Functions): – I/O. Port 3 provides eight lines each of which can serve as psuedo-bi-directional I/O port pins or as the alternate functions as listed below. Internal pull-up resistors are always present on these pins.         Alternate         Port       Function       Description         P3.0       RXD0       Serial Port 0 Input         P3.1       TXD0       Serial Port 0 Output         P3.2       INTO       External Interrupt 0         P3.3       INT1       External Interrupt 1         P3.4       T0       Timer 0 External Input         P3.5       T1       Timer 1 External Input         P3.6       WR       External Data Memory Write Strobe         P3.7       RD       External Data Memory Read Strobe                                                                                             |

| 77<br>78<br>79<br>80<br>81<br>82<br>83<br>84         | P4.0 (KSI.0)<br>P4.1 (KSI.1)<br>P4.2 (KSI.2)<br>P4.3 (KSI.3)<br>P4.4 (KSI.4)<br>P4.5 (KSI.5)<br>P4.6 (KSI.6)<br>P4.7 (KSI.7) | <b>Port 4 / KSI.7–0:</b> – I/O / Keyboard Scan Inputs. Port 4 provides eight lines which can be individually selected as psuedo–bi–directional I/O port pins or as an interrupt Inputs for key scanning. Port 4 pins incorporate Schmitt inputs with pull–up resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

011200 10/88

|                                              | 1                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN                                          | SYMBOL                                                                                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 34<br>33<br>32<br>31<br>30<br>29<br>28<br>27 | P5.0 (Al.0)<br>P5.1 (Al.1)<br>P5.2 (Al.2)<br>P5.3 (Al.3)<br>P5.4 (Al.4)<br>P5.5 (Al.5)<br>P5.6 (Al.6)<br>P5.7 (Al.7)         | <b>Port 5 / AI.7–0:</b> – I/O / A/D inputs. Port 5 provides eight lines which can be individually selected as open–drain psuedo–bi–directional I/O port pins or as A/D inputs. Pull–up resistors are required when using Port 5 as an I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 26<br>25<br>24<br>23<br>22<br>21<br>20<br>19 | P6.0 (PWO.0)<br>P6.1 (PWO.1)<br>P6.2 (PWO.2)<br>P6.3 (PWO.3)<br>P6.4 (PWI.0)<br>P6.5 (PWI.1)<br>P6.6<br>P6.7 / SOC           | Port 6 / PW0.3 – 0: – I/O / Pulse–Width Modulated Outputs. Port 6 provides eight lines which can all serve as psuedo–bi–directional I/O port pins with internal pull–up resistors. Six lines can be individually selected to serve the pulse–width modulator function indicated below:         Alternate       Description         Port       Function       Description         P6.0       PWO.0       PWM 0 output (active high drive when enabled)         P6.1       PWO.1       PWM 1 output (active high drive when enabled)         P6.2       PWO.2       PWM 2 output (active high drive when enabled)         P6.3       PWO.3       PWM 3 output (active high drive when enabled)         P6.4       PWI.0       Optional clock input for PWM channels 0 and 2         P6.5       PWI.1       Optional clock input for PWM channels 1 and 3         P6.6       (none)       External A / D start of conversion signal |  |  |  |

| 69                                           | P7.0 (AMI.0)                                                                                                                 | <b>Port 7 / AMI.7–0 / LED.7–0:</b> – I/O / Activity Monitor Inputs / LED Control. Port 7 provides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 70                                           | (LED.0)<br>P7.1 (AMI.1)<br>(LED.1)                                                                                           | eight lines which can serve as a psuedo-bi-directional I/O port pins with internal pull-<br>ups or as Activity Monitor inputs. When used as Activity Monitor inputs, these pins are<br>typically connected to the chip select line of an external peripheral device, and can be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 71                                           | P7.2 (AMÍ.2)<br>(LED.2)                                                                                                      | programmed to sense active-high or active-low signals. Any pin which is programmed as an Activity Monitor input by setting its AMEn bit to a 1 will have its pull-up device dis-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 72                                           | P7.3 (AMI.3)<br>(LED.3)                                                                                                      | abled and thereby function as an <u>open-drain</u> pin in order to eliminate unnecessary cur-<br>rent drain. All port 7 pins are capable of controlling LED's.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 73                                           | P7.4 (AMÍ.4)<br>(LED.4)                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 74                                           | P7.5 (AMÍ.5)                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 75                                           | (LED.5)<br>P7.6 (AMI.6)                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 76                                           | (LED.6)<br>P7.7 (AMI.7)<br>(LED.7)                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 16<br>15<br>14<br>13<br>12<br>11<br>10<br>9  | P8.0 (KSO.0)<br>P8.1 (KSO.1)<br>P8.2 (KSO.2)<br>P8.3 (KSO.3)<br>P8.4 (KSO.4)<br>P8.5 (KSO.5)<br>P8.6 (KSO.6)<br>P8.7 (KSO.7) | <b>Port 8/KSO.7–0:</b> – I/O. Port 8 provides eight lines of <u>open–drain</u> psuedo–bi–directional I/O port pins. Typically, these lines are used for key–scan outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PIN                                          | SYMBOL                                                                                                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8<br>7<br>6<br>5<br>4<br>3<br>2<br>1         | P9.0 (KSO.8)<br>P9.1 (KSO.9)<br>P9.2 (KSO.10)<br>P9.3 (KSO.11)<br>P9.4 (KSO.12)<br>P9.5 (KSO.13)<br>P9.6 (KSO.14)<br>P9.7 (KSO.15) | <b>Port 9 / KSO.15–8:</b> – I/O. Port 9 provides eight lines of <u>open–drain</u> psuedo–bi–directional I/O port pins. Typically, these lines are used for key–scan outputs.                                                                                                                                                                               |

| 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67 | P10.0<br>P10.1<br>P10.2<br>P10.3<br>P10.4<br>P10.5<br>P10.6<br>P10.7                                                               | Port10: –I/O. Port 10 provides eight lines of general purpose Input or Output.                                                                                                                                                                                                                                                                             |

| 41                                           | PM1CS                                                                                                                              | <b>Power Management #1 Chip Select:</b> (Input, active low). This is a chip select signal used to enable the power management #1 host interface port.                                                                                                                                                                                                      |

| 59                                           | PM2CS                                                                                                                              | <b>Power Management #2 Chip Select:</b> (Input, active low). This is a chip select signal used to enable the power management #2 host interface port.                                                                                                                                                                                                      |

| 107                                          | PSEN                                                                                                                               | <b>Program Store Enable:</b> Output. This signal goes low when off-chip program memory is being accessed via Ports 0 and 2. It is commonly connected to optional external ROM memory as a chip enable. PSEN will provide an active low pulse and is driven high when external ROM is not being accessed.                                                   |

| 105                                          | RST                                                                                                                                | <b>Reset:</b> Input, active high The RST input pin contains a Schmitt voltage input to recog-<br>nize external active high Reset inputs. The pin also employs an internal pull–down<br>resistor to allow for a combination of wired OR external Reset sources. An RC is not<br>required for power–up, as the controller provides this function internally. |

| 55<br>54<br>53<br>52<br>51<br>50<br>49<br>48 | SD0<br>SD1<br>SD2<br>SD3<br>SD4<br>SD5<br>SD6<br>SD7                                                                               | <b>System Data Bus:</b> (Bi–directional). SD7–0 are data bus lines used for data transfers between the host processor and the keyboard interface buffer and power management #1 and #2 interface buffers.                                                                                                                                                  |

| 39                                           | <u>SMI1</u>                                                                                                                        | <b>System Management Interrupt #1:</b> (Output, active low). This signal is driven low when the power management #1 host interface data buffer contains data to be read by the host. SMI1 will be returned to a High Level when host reads the power management #1 data buffer register.                                                                   |

| 58                                           | SMI2                                                                                                                               | <b>System Management Interrupt #2:</b> (Output, active low). This signal is driven low when the power management #2, host interface data buffer contains data to be read by the host. SMI2 will be returned to a high level when the host reads the power management #2 data buffer register.                                                              |

011200 12/88

| PIN             | SYMBOL         | DESCRIPTION                                                                                                                                                                                                                                             |

|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18<br>85<br>120 | VCC            | Digital Power Supply Input: For microcontroller and associated functions.                                                                                                                                                                               |

| 101             | VPFW           | <b>Power Fail Warning:</b> Output, active low. The VPFW pin signals an impending power failure when VCC drops below VPFW voltage threshold.                                                                                                             |

| 44              | VRH            | <b>A/D Positive Voltage Reference:</b> The VRH pin is the positive reference (upper voltage limit) of the A/D Converter.                                                                                                                                |

| 45              | VRL            | <b>A/D Negative Voltage Reference:</b> The VRL pin is the negative reference (lower voltage limit) of the A/D Converter.                                                                                                                                |

| 102             | VRST           | <b>Power Fail Reset:</b> Output, active low. The VRST pin signals a "power not good" condition to the system when system VCC has dropped below the VRST voltage threshold.                                                                              |

| 118<br>119      | XTAL1<br>XTAL2 | $\mu$ C Crystal Oscillator Inputs. XTAL1 and XTAL2 provide support for parallel resonant, AT cut crystals. XTAL1 acts also as an input if there is an external clock source in place of a crystal. XTAL2 serves as the output of the crystal amplifier. |

#### 2.2 PIN CHARACTERISTICS

| PIN | NAME        | POWER DOWN<br>MODE STATE | I/O BUFFER TYPE                       | RESET<br>STATE |

|-----|-------------|--------------------------|---------------------------------------|----------------|

| 36  | A0          | -                        | I                                     | -              |

| 43  | AGND        | -                        | _                                     | -              |

| 106 | ALE         | Low                      | 0                                     | Low            |

| 46  | AVCC        | -                        | -                                     | -              |

| 17  | GND         | -                        | _                                     | _              |

| 35  | GND         | -                        | -                                     | -              |

| 86  | GND         | -                        | -                                     | -              |

| 117 | GND         | -                        | _                                     | -              |

| 47  | HGND        | -                        | -                                     | _              |

| 68  | HVCC        | -                        | -                                     | _              |

| 38  | IOR         | -                        | I                                     | -              |

| 37  | IOW         | -                        | I                                     | -              |

| 42  | KBCS        | -                        | I                                     | -              |

| 40  | KBOBF       | Hold                     | 0                                     | Low            |

| 57  | NC          | -                        | -                                     | -              |

| 56  | NC          | -                        | -                                     | _              |

| 108 | NC          | -                        | -                                     | -              |

| 121 | P0.0 / AD0  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 122 | P0.1 / AD1  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 123 | P0.2 / AD2  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 124 | P0.3 / AD3  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 125 | P0.4 / AD4  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 126 | P0.5 / AD5  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 127 | P0.6 / AD6  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 128 | P0.7 / AD7  | High–Z                   | Open–Drain (port)<br>CMOS drive (bus) | High–Z         |

| 87  | P1.0 / T2   | Hold                     | Pull–up                               | Weak High      |

| 88  | P1.1 / T2EX | Hold                     | Pull–up                               | Weak High      |

| 89  | P1.2 / SCL1 | Hold                     | Open-drain                            | High–Z         |

| 90  | P1.3 / SDA1 | Hold                     | Open-drain                            | High–Z         |

011200 14/88

| PIN | NAME         | POWER DOWN<br>MODE STATE | I/O BUFFER TYPE | RESET<br>STATE |

|-----|--------------|--------------------------|-----------------|----------------|

| 91  | P1.4 /SCL2   | Hold                     | Open-drain      | High–Z         |

| 92  | P1.5 /SDA2   | Hold                     | Open-drain      | High–Z         |

| 93  | P1.6         | Hold                     | Open-drain      | High–Z         |

| 94  | P1.7         | Hold                     | Open-drain      | High–Z         |

| 109 | P2.0 / A8    | Hold                     | Pull-up         | Weak High      |

| 110 | P2.1 / A9    | Hold                     | Pull-up         | Weak High      |

| 111 | P2.2 / A10   | Hold                     | Pull-up         | Weak High      |

| 112 | P2.3 / A11   | Hold                     | Pull-up         | Weak High      |

| 113 | P2.4 / A12   | Hold                     | Pull–up         | Weak High      |

| 114 | P2.5 / A13   | Hold                     | Pull-up         | Weak High      |

| 115 | P2.6 / A14   | Hold                     | Pull-up         | Weak High      |

| 116 | P2.7 / A15   | Hold                     | Pull-up         | Weak High      |

| 95  | P3.0 / RXD0  | Hold                     | Pull-up         | Weak High      |

| 96  | P3.1 / TXD0  | Hold                     | Pull-up         | Weak High      |

| 97  | P3.2 / ĪNT0  | Hold                     | Pull-up         | Weak High      |

| 98  | P3.3 / ĪNT1  | Hold                     | Pull-up         | Weak High      |

| 99  | P3.4 / T0    | Hold                     | Pull-up         | Weak High      |

| 100 | P3.5 / T1    | Hold                     | Pull–up         | Weak High      |

| 103 | P3.6 / WR    | Hold                     | Pull–up         | Weak High      |

| 104 | P3.7 / RD    | Hold                     | Pull–up         | Weak High      |

| 77  | P4.0 / KSI.0 | Hold                     | Pull–up         | Weak High      |

| 78  | P4.1 / KSI.1 | Hold                     | Pull-up         | Weak High      |

| 79  | P4.2 / KSI.2 | Hold                     | Pull–up         | Weak High      |

| 80  | P4.3 / KSI.3 | Hold                     | Pull–up         | Weak High      |

| 81  | P4.4 / KSI.4 | Hold                     | Pull–up         | Weak High      |

| 82  | P4.5 / KSI.5 | Hold                     | Pull–up         | Weak High      |

| 83  | P4.6 / KSI.6 | Hold                     | Pull–up         | Weak High      |

| 84  | P4.7 / KSI.7 | Hold                     | Pull–up         | Weak High      |

| 34  | P5.0 / AI.0  | Hold                     | Open-drain      | High–Z         |

| 33  | P5.1 / AI.1  | Hold                     | Open-drain      | High–Z         |

| 32  | P5.2 / AI.2  | Hold                     | Open-drain      | High–Z         |

| 31  | P5.3 / AI.3  | Hold                     | Open-drain      | High–Z         |

011200 15/88

#### 2.2 PIN CHARACTERISTICS (cont'd)

| PIN | NAME                    | POWER DOWN<br>MODE STATE | I/O BUFFER TYPE                                      | RESET<br>STATE |

|-----|-------------------------|--------------------------|------------------------------------------------------|----------------|

| 30  | P5.4 / AI.4             | Hold                     | Open-drain                                           | High–Z         |

| 29  | P5.5 / AI.5             | Hold                     | Open-drain                                           | High–Z         |

| 28  | P5.6 / AI.6             | Hold                     | Open-drain                                           | High–Z         |

| 27  | P5.7 / AI.7             | Hold                     | Open-drain                                           | High–Z         |

| 26  | P6.0 / PWO.0            | Hold                     | Pull–up (PWMn disabled)<br>CMOS drive (PWMn enabled) | Weak High      |

| 25  | P6.1 / PWO.1            | Hold                     | Pull–up (PWMn disabled)<br>CMOS drive (PWMn enabled) | Weak High      |

| 24  | P6.2 / PWO.2            | Hold                     | Pull–up (PWMn disabled)<br>CMOS drive (PWMn enabled) | Weak High      |

| 23  | P6.3 / PWO.3            | Hold                     | Pull–up (PWMn disabled)<br>CMOS drive (PWMn enabled) | Weak High      |

| 22  | P6.4 / PWI.0            | Hold                     | Pull–up                                              | Weak High      |

| 21  | P6.5 / PWI.1            | Hold                     | Pull-up                                              | Weak High      |

| 20  | P6.6                    | Hold                     | Pull–up                                              | Weak High      |

| 19  | P6.7 / SOC              | Hold                     | Pull–up                                              | Weak High      |

| 69  | P7.0 / AMI.0 /<br>LED.0 | Hold                     | Pull–up                                              | Weak High      |

| 70  | P7.1 / AMI.1 /<br>LED.1 | Hold                     | Pull–up                                              | Weak High      |

| 71  | P7.2 / AMI.2 /<br>LED.2 | Hold                     | Pull–up                                              | Weak High      |

| 72  | P7.3 / AMI.3 /<br>LED.3 | Hold                     | Pull–up                                              | Weak High      |

| 73  | P7.4 / AMI.4/<br>LED.4  | Hold                     | Pull–up                                              | Weak High      |

| 74  | P7.5 / AMI.5/<br>LED.5  | Hold                     | Pull–up                                              | Weak High      |

| 75  | P7.6 / AMI.6/<br>LED.6  | Hold                     | Pull–up                                              | Weak High      |

| 76  | P7.7 / AMI.7/<br>LED.7  | Hold                     | Pull-up                                              | Weak High      |

| 16  | P8.0 / KSO.0            | Hold                     | Open-drain                                           | High–Z         |

| 15  | P8.1 / KSO.1            | Hold                     | Open-drain                                           | High–Z         |

| 14  | P8.2 / KSO.2            | Hold                     | Open–drain                                           | High–Z         |

| 13  | P8.3 / KSO.3            | Hold                     | Open-drain                                           | High–Z         |

| 12  | P8.4 / KSO.4            | Hold                     | Open-drain                                           | High–Z         |

| 11  | P8.5 / KSO.5            | Hold                     | Open–drain                                           | High–Z         |

| 10  | P8.6 / KSO.6            | Hold                     | Open–drain                                           | High–Z         |

011200 16/88

| PIN | NAME          | POWER DOWN<br>MODE STATE | I/O BUFFER TYPE | RESET<br>STATE |

|-----|---------------|--------------------------|-----------------|----------------|

| 9   | P8.7 / KSO.7  | Hold                     | Open-drain      | High–Z         |

| 8   | P9.0 / KSO.8  | Hold                     | Open-drain      | High–Z         |

| 7   | P9.1 / KSO.9  | Hold                     | Open-drain      | High–Z         |

| 6   | P9.2 / KSO.10 | Hold                     | Open-drain      | High–Z         |

| 5   | P9.3 / KSO.11 | Hold                     | Open-drain      | High–Z         |

| 4   | P9.4 / KSO.12 | Hold                     | Open-drain      | High–Z         |

| 3   | P9.5 / KSO.13 | Hold                     | Open-drain      | High–Z         |

| 2   | P9.6 / KSO.14 | Hold                     | Open-drain      | High–Z         |

| 1   | P9.7 / KSO.15 | Hold                     | Open-drain      | High–Z         |

| 60  | P10.0         | Hold                     | Pull-up         | Weak Hig       |

| 61  | P10.1         | Hold                     | Pull-up         | Weak Hig       |

| 62  | P10.2         | Hold                     | Pull–up         | Weak Hig       |

| 63  | P10.3         | Hold                     | Pull–up         | Weak Hig       |

| 64  | P10.4         | Hold                     | Pull-up         | Weak Hig       |

| 65  | P10.5         | Hold                     | Pull-up         | Weak Hig       |

| 66  | P10.6         | Hold                     | Pull-up         | Weak Hig       |

| 67  | P10.7         | Hold                     | Pull–up         | Weak Hig       |

| 41  | PM1CS         | -                        | I               | -              |

| 59  | PM2CS         | -                        | I               | -              |

| 107 | PSEN          | Low                      | 0               | Low            |

| 105 | RST           | -                        | I               | -              |

| 55  | SD0           | (note 2)                 | Bi-directional  | (note 2)       |

| 54  | SD1           | (note 2)                 | Bi-directional  | (note 2)       |

| 53  | SD2           | (note 2)                 | Bi-directional  | (note 2)       |

| 52  | SD3           | (note 2)                 | Bi-directional  | (note 2)       |

| 51  | SD4           | (note 2)                 | Bi-directional  | (note 2)       |

| 50  | SD5           | (note 2)                 | Bi-directional  | (note 2)       |

| 49  | SD6           | (note 2)                 | Bi-directional  | (note 2)       |

| 48  | SD7           | (note 2)                 | Bi-directional  | (note 2)       |

| 39  | SMI1          | Hold                     | 0               | High           |

| 58  | SMI2          | Hold                     | 0               | High           |

| 18  | VCC           | -                        | _               | -              |

| 85  | VCC           | -                        | _               | -              |

| 120 | VCC           | -                        | _               |                |

011200 17/88

#### 2.2 PIN CHARACTERISTICS (cont'd)

| PIN | NAME  | POWER DOWN<br>MODE STATE | I/O BUFFER TYPE | RESET<br>STATE |

|-----|-------|--------------------------|-----------------|----------------|

| 101 | VPFW  | (note 3)                 | 0               | (note 3)       |

| 44  | VRH   | -                        | _               | -              |

| 45  | VRL   | -                        | _               | -              |

| 102 | VRST  | (note 3)                 | 0               | (note 3)       |

| 118 | XTAL1 | -                        | I               | -              |

| 119 | XTAL2 | Н                        | 0               | _              |

#### **PIN STATE DESCRIPTIONS**

| High–Z    | High Impedance                                |

|-----------|-----------------------------------------------|

| Enabled   | Power applied; electrically functioning input |

| Unchanged | Previous state not affected                   |

#### NOTES:

- 1. As shown above, the original port pins P1.7–P1.2 have been modified to open–drain instead of having "Internal" pull–up resistors.

- 2. This signal is independently powered from the HVCC on pin 68. As a result, the state of the reset pin and the power down mode have no effect on its operation.

- 3. VRST and VPFW reflects the state of VCC with respect to the power-fail reset and power-fail warning trip points, respectively, and is unaffected by the RST pin and power down mode state.

#### 3.0 CORE MICROCONTROLLER

#### 3.1 CORE MICRO OVERVIEW

The SEM incorporates the Dallas High Speed Micro core which is a fully static CMOS 8051 compatible microcontroller with a new internal architecture designed for high performance. The higher speed operation of the microcontroller core comes not just from increasing the clock frequency, but from a newer, more efficient design of the internal architecture. The major features of the High Speed Micro Core include:

- 4 clocks/machine cycle (8032 = 12)

- · Wasted cycles removed

- Runs DC to 25 Mhz clock rates @ 5V

- Single-cycle instruction in 160 ns

- Uses less power for equivalent work

- Dual data pointer

- Optional variable length MOVX to access fast/slow RAM /peripherals

#### 3.2 INSTRUCTION SET SUMMARY

All instructions in the SEM perform the same functions as their 80C32 counterparts. Their affect on bits, flags, and other status functions are identical. However, the timing of each instruction is different. This applies both in absolute and relative number of clocks.

For absolute timing of real-time events, the timing of software loops will need to be calculated using the table below. However, counter/timers default to run at the older 12 clocks per increment. Therefore, while software runs at higher speed, timer-based events need no modification to operate as before. Timers can be set to run at 4 clocks per increment cycle to take advantage of higher speed operation.

The relative time of two instructions might be different in the new architecture than it was previously. For example, in the original architecture, the "MOVX A, @ DPTR" instruction and the "MOV direct, direct" instruction used two machine cycles or 24 oscillator cycles. Therefore, they required the same amount of time. In the GEM, the MOVX instruction can be done in two machine cycles or 8 oscillator cycles but the "MOV direct, direct" uses three machine cycles or 12 oscillator cycles. While both are faster than their original counterparts, they now have different execution times from each other. This is because in most cases, the SEM uses one cycle for each byte. The timing of each instruction should be examined for familiarity with the changes. Note that a machine cycle now requires just four clocks, and provides one ALE pulse per cycle. Many instructions require only one cycle, but some require five. In the original architecture, all were one or two cycles except for MUL and DIV.

#### **INSTRUCTION SET SUMMARY** Table 3-1

#### Legends:

| A        | - | Accumulator                              |

|----------|---|------------------------------------------|

| Rn       | _ | Register R7–R0                           |

| direct   | - | Internal Register address                |

| @Ri      | - | Internal Register pointed-to by R0 or R1 |

|          |   | (except MOVX)                            |

| rel      | - | 2's complement offset byte               |

| bit      | - | direct bit-address                       |

| #data    | - | 8-bit constant                           |

| #data 16 | - | 16-bit constant                          |

| addr 16  | - | 16-bit destination address               |

| addr 11  | - | 11-bit destination address               |

|          |   |                                          |

## INSTRUCTION SET SUMMARY Table 3-1 (cont'd)

| INSTRUCTION                    | BYTE | OSCILLATOR<br>CYCLES | INSTRUCTION       | BYTE   | OSCILLATOR<br>CYCLES |

|--------------------------------|------|----------------------|-------------------|--------|----------------------|

| Arithmetic Instructions:       |      |                      |                   |        |                      |

| ADD A, Rn                      | 1    | 4                    | INC A             | 1      | 4                    |

| ADD A, direct                  | 2    | 8                    | INC Rn            | 1      | 4                    |

| ADD A, @Ri                     | 1    | 4                    | INC direct        | 2      | 8                    |

| ADD A, #data                   | 2    | 8                    | INC @Ri           | 1      | 4                    |

| ADDC A, Rn                     | 1    | 4                    | INC DPTR          | 1      | 12                   |

| ADDC A, direct                 | 2    | 8                    | DEC A             | 1      | 4                    |

| ADDC A, @Ri                    | 1    | 4                    | DEC Rn            | 1      | 4                    |

| ADDC A, #data                  | 2    | 8                    | DEC direct        | 2      | 8                    |

| SUBB A, Rn                     | 1    | 4                    | DEC @Ri           | 1      | 4                    |

| SUBB A, direct                 | 2    | 8                    | MUL AB            | 1      | 20                   |

| SUBB A, @Ri                    | 1    | 4                    | DIV AB            | 1      | 20                   |

| SUBB A, #data                  | 2    | 8                    | DA A              | 1      | 4                    |

| Logical Instructions:          |      |                      |                   |        |                      |

| ANL A, Rn                      | 1    | 4                    | XRL A, Rn         | 1      | 4                    |

| ANL A, direct                  | 2    | 8                    | XRL A, direct     | 2      | 8                    |

| ANL A, @Ri                     | 1    | 4                    | XRL A, @Ri        | 1      | 4                    |

| ANL A, #data                   | 2    | 8                    | XRL A, #data      | 2      | 8                    |

| ANL direct, A                  | 2    | 8                    | XRL direct, A     | 2      | 8                    |

| ANL direct, #data              | 3    | 12                   | XRL direct, #data | 3      | 12                   |

| ORL A, Rn                      | 1    | 4                    | CLR A             | 1      | 4                    |

| ORL A, direct                  | 2    | 8                    | CPL A             | 1      | 4                    |

| ORL A, @Ri                     | 1    | 4                    | RL A              | 1      | 4                    |

| ORL A, #data                   | 2    | 8                    | RLC A             | 1      | 4                    |

| ORL direct, A                  | 2    | 8                    | RR A              | 1      | 4                    |

| ORL direct, #data              | 3    | 12                   | RRC A<br>SWAP A   | 1<br>1 | 4<br>4               |

|                                |      |                      | SWAF A            | I      | 4                    |

| Data Transfer<br>Instructions: |      |                      |                   |        |                      |

| MOV A, Rn                      | 1    | 4                    | MOVC A, @A+DPTR   | 1      | 12                   |

| MOV A, direct                  | 2    | 8                    | MOVC A, @A+PC     | 1      | 12                   |

| MOV A, @Ri                     | 1    | 4                    | MOVX A, @Ri       | 1      | 8–36                 |

| MOV A, #data                   | 2    | 8                    | MOVX A, @DPTR     | 1      | 8–36                 |

| MOV Rn, A                      | 1    | 4                    | MOVX @Ri, A       | 1      | 8–36                 |

| MOV Rn, direct                 | 2    | 8                    | MOVX @DPTR, A     | 1      | 8–36                 |

| MOV Rn, #data                  | 2    | 8                    | PUSH direct       | 2      | 8                    |

| MOV direct, A                  | 2    | 8                    | POP direct        | 2      | 8                    |

| MOV direct, Rn                 | 2    | 8                    | XCH A, Rn         | 1      | 4                    |

| MOV direct1, direct2           | 3    | 12                   | XCH A, direct     | 2      | 8                    |

| MOV direct, @Ri                | 2    | 8                    | XCH A, @Ri        | 1      | 4                    |

| MOV direct, #data              | 3    | 12                   | XCHD A, @Ri       | 1      | 4                    |

| MOV @Ri, A                     | 1    | 4                    |                   |        |                      |

| MOV @Ri, direct                | 2    | 8                    |                   |        |                      |

| MOV @Ri, #data                 | 2    | 8                    |                   |        |                      |

| MOV DPTR, #data 16             | 3    | 12                   |                   |        |                      |

011200 20/88

#### **INSTRUCTION SET SUMMARY** Table 3–1 (cont'd)

| Bit Manipulation<br>Instructions:  |   |    |                       |   |    |

|------------------------------------|---|----|-----------------------|---|----|

| CLR C                              | 1 | 4  | ANL C, bit            | 2 | 8  |

| CLR bit                            | 2 | 8  | ANL C, bit            | 2 | 8  |

| SETB C                             | 1 | 4  | ORL C, bit            | 2 | 8  |

| SETB bit                           | 2 | 8  | ORL C, bit            | 2 | 8  |

| CPL C                              | 1 | 4  | MOV C, bit            | 2 | 8  |

| CPL bit                            | 2 | 8  | MOV bit, C            | 2 | 8  |

| Program Branching<br>Instructions: |   |    |                       |   |    |

| ACALL addr 11                      | 2 | 12 | CJNE A, direct, rel   | 3 | 16 |

| LCALL addr 16                      | 3 | 16 | CJNE A, #data, rel    | 3 | 16 |

| RET                                | 1 | 16 | CJNE Rn, #data, rel   | 3 | 16 |

| RETI                               | 1 | 16 | CJNE @ Ri, #data, rel | 3 | 16 |

| AJMP addr 11                       | 2 | 12 | NOP                   | 1 | 4  |

| LJMP addr 16                       | 3 | 16 | JC rel                | 2 | 12 |

| SJMP rel                           | 2 | 12 | JNC rel               | 2 | 12 |

| JMP @A+DPTR                        | 1 | 12 | JB bit, rel           | 3 | 16 |

| JZ rel                             | 2 | 12 | JNB bit, rel          | 3 | 16 |

| JNZ rel                            | 2 | 12 | JBC bit, rel          | 3 | 16 |

| DJNZ Rn, rel                       | 2 | 12 |                       |   |    |

| DJNZ direct, rel                   | 3 | 16 |                       |   |    |

The Table above shows the speed for each class of instruction. Note that many of the instructions have multiple opcodes. There are 255 opcodes for 111 instructions. Of the 255 opcodes, 159 are three times faster than the original 80C32. While a system than emphasizes those instructions will see the most improvement, the large total number that receive a three to one improvement assure a dramatic speed increase for any system. The speed improvement summary is provided below.

#### 3.3 SPEED IMPROVEMENT

The following table summarizes the speed improvement of the High Speed Micro core over a standard 12 clock / machine cycle 8052 device.

| #Opcodes | Speed Improvement |

|----------|-------------------|

| 159      | 3.0 x             |

| 51       | 1.5 x             |

| 43       | 2.0 x             |

| 2        | <u>2.4 x</u>      |

| 255      | Average: 2.5      |

# 3.4 INSTRUCTION SET ADDITIONAL REFERENCES

The user should refer to the Dallas High Speed Micro User's Guide for a complete description of the instruction set including its address modes, coding, and timing for the SEM.

#### 3.5 RESET

The High–Speed Micro has three ways of entering a reset state:

- Power-On / Fail Reset

- Watchdog Timer Reset

- External Reset

The operation of the CPU timing and states during a reset are documented in the Dallas High Speed Micro User's Guide under the "Reset Conditions" section. The Watchdog Timer reset is documented in the Watchdog Timer section of the Dallas High Speed Micro User's Guide. The operation of the Power–On / Fail reset is described in the Power Management section of this document.

#### 3.6 INTERRUPT CONTROL

The SEM provides 16 sources of interrupt with three priority levels. The Power–fail Interrupt (PFI), if enabled, always has the highest priority. There are two remaining user selectable priorities: high and low. If two interrupts that have the same priority occur simulta-

neously, the hardware–determined precedence given below determines which is a acted upon. Except for the PFI, all interrupts that are new to the 8051 family have a lower natural priority than the originals.

| NAME  | DESCRIPTION                   | VECTOR | NATURAL<br>PRIORITY | 8051/DALLAS |

|-------|-------------------------------|--------|---------------------|-------------|

| PFI   | Power Fail Interrupt          | 33h    | 1                   | DALLAS      |

| INT0  | External Interrupt 0          | 03h    | 2                   | 8051        |

| TF0   | Timer 0                       | 0Bh    | 3                   | 8051        |

| INT1  | External Interrupt 1          | 13h    | 4                   | 8051        |

| TF1   | Timer 1                       | 1Bh    | 5                   | 8051        |

| SCON0 | TI0 or RI0 from Serial Port 0 | 23h    | 6                   | 8051        |

| TF2   | Timer 2                       | 2Bh    | 7                   | 8051        |

| AMI   | Activity Monitor Interrupt    | 3Bh    | 8                   | DALLAS      |

| 2WI1  | 2–Wire Serial Port 1          | 43h    | 9                   | DALLAS      |

| ADI   | A/D End of Conversion         | 4Bh    | 10                  | DALLAS      |

| 2WI2  | 2–Wire Serial Port 2          | 53h    | 11                  | DALLAS      |

| KBI   | Keyboard Buffer Input         | 5Bh    | 12                  | DALLAS      |

| PBI1  | Power Mgmt. Buffer Input #1   | 63h    | 13                  | DALLAS      |

| KDI   | Key Detect Input              | 6Bh    | 14                  | DALLAS      |

| WDI   | WatchDog Periodic Interrupt   | 73h    | 15                  | DALLAS      |

| PBI2  | Power Mgmt. Buffer Input #2   | 7Bh    | 16                  | DALLAS      |

#### **INTERRUPT PRIORITY** Table 3–2

#### **INTERRUPT CONTROL SUMMARY** Table 3–3

| INTERRUPT<br>SOURCE | FLAG(S) | FLAG<br>LOC.        | ENABLE | ENABLE<br>LOC. | PRIORITY | PRIORITY<br>LOC. |

|---------------------|---------|---------------------|--------|----------------|----------|------------------|

| Power Fail          | PFI     | WDCON.4             | EPFI   | WDCON.5        | N/A      | N/A              |

| External 0          | IE0     | TCON.1              | EX0    | IE.0           | PX0      | IP.0             |

| Timer 0             | TF0     | TCON.5              | ET0    | IE.1           | PT0      | IP.1             |

| External 1          | IE1     | TCON.3              | EX1    | IE.2           | PX1      | IP.2             |

| Timer 1             | TF1     | TCON.7              | ET1    | IE.3           | PT1      | IP.3             |

| Serial Port 0       | R10,T10 | SCON0.0/<br>SCON0.1 | ES0    | IE.4           | PS0      | IP.4             |

| Timer 2             | TF2     | T2CON.7             | ET2    | IE.5           | PT2      | IP.5             |

| Activity monitor    | AMF7–0  | AMF.7-0             | EAM    | IE.6           | PAM      | IP.6             |

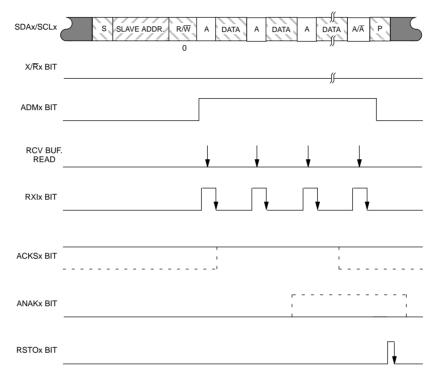

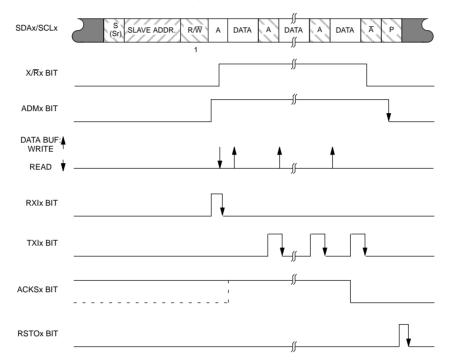

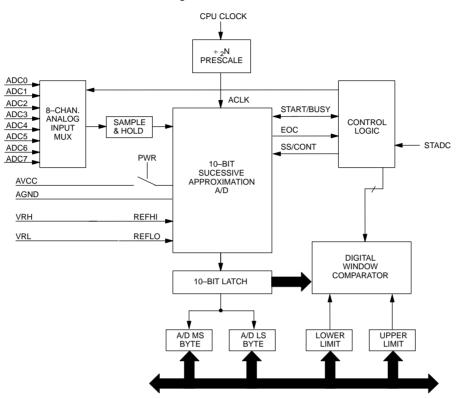

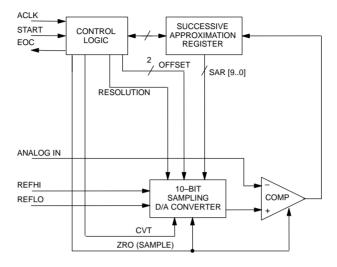

011200 22/88