#### Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

#### MAX14774, MAX14779

## **Product Highlights**

- Design with Wide Signal Range

- Wide ±25V Analog Input Signal Range

- Single 3.0V to 5.5V Supply Voltage

- 1.62V to 5.5V Flexible Logic Input Levels

- High Performance Analog Switch

- 2.5Ω (max) On-Resistance at +85°C

- $18m\Omega$  (typ) On-Resistance Flatness

- ±100nA (max) On-Leakage Current at +85°C for MAX14774

- ±200nA (max) On-Leakage Current at +85°C for MAX14779

- ±200mA (max) Continuous Current Through Each Switch

- Short Circuit Protection on Each Switch

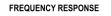

- 147MHz (typ) Signal Bandwidth for MAX14774

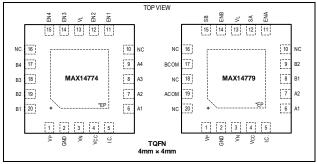

- Small 4mm x 4mm 20-Pin TQFN Package

- -40°C to +125°C Operating Temperature Range

#### **Key Applications**

- ATE Systems

- Switching Full Speed USB, CAN, RS-232/485, TTL, Audio

- Instrumentation Systems

The MAX14774/MAX14779 analog switches support analog signals up to  $\pm 25V$  using a single 3.0V to 5.5V supply. The MAX14774 has four independent analog switches with separate control inputs, while the MAX14779 has two SPDT analog switches. Both parts support separate logic level inputs, allowing flexible CMOS input levels from 1.62V to 5.5V.

The MAX14774/MAX14779 feature a  $2.5\Omega$  (max) onresistance and an  $18m\Omega$  (typ) flatness at  $+85^{\circ}$ C. The MAX14774 has a low  $\pm 100$ nA (max) on-leakage current at  $+85^{\circ}$ C, while the MAX14779 has  $\pm 200$ nA (max). Each switch can carry up to  $\pm 200$ mA (max) of continuous current in either direction. The switches maintain the performance over the entire common-mode voltage range. Both parts are specified for  $-40^{\circ}$ C to  $+125^{\circ}$ C industrial temperature range and are available in a 20 pin (4mm x 4mm) TQFN package.

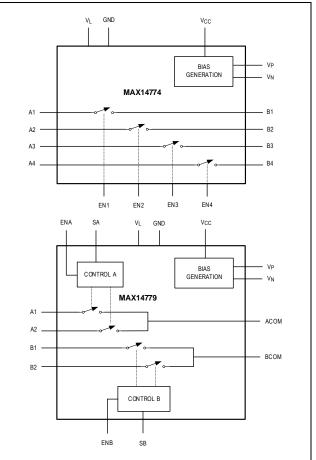

#### **Simplified Block Diagram**

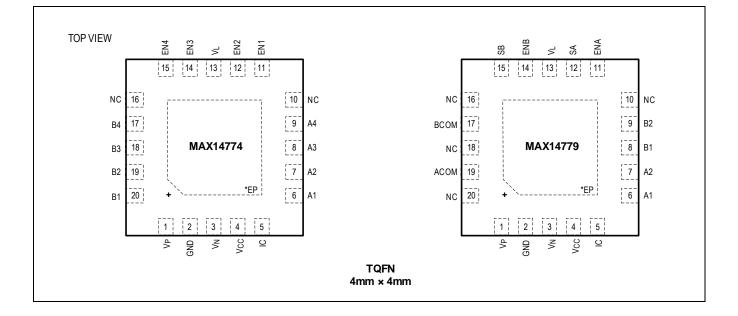

## **Pin Configuration**

Ordering Information appears at end of data sheet.

19-101540; Rev 0; 5/22

#### Quad SPST/Dual SPDT Beyond-The-Rails **Analog Switches**

#### **Absolute Maximum Ratings**

| $V_{CC},V_L$ to GND0.3V to +6V                                                        |

|---------------------------------------------------------------------------------------|

| EN_, SA, SB to GND0.3V to +6V                                                         |

| A_, B_ to GND (V_N – 0.3V) to the lesser of (V_P + 0.3V) and (V_N + 70V)              |

| $V_{\mbox{P}}$ to GND0.3V to +52V                                                     |

| $V_{\mbox{N}},\mbox{EP}$ to GND The greater of -40V and (V_{\mbox{P}} - 70V) to +0.3V |

| $V_P$ to $V_N$ 0.3V to +70V                                                           |

| Absolute Voltage Difference Between I/Os ( A B_ )+70V                                 |

| Continuous Current Into Any Pin ±200mA                                                |

| Continuous Power Dissipation                                                          |

| Single-Layer Board (T <sub>A</sub> = +70°C, derate 20.8mW/°C above +70°C) |

|---------------------------------------------------------------------------|

| Multilayer Board (T_A = +70°C, derate $30.3mW/^{\circ}C$ above +70°C)     |

| Temperature Ratings                                                       |

| Operating Temperature Range40°C to +125°C                                 |

| Junction Temperature+150°C                                                |

| Storage Temperature40°C to +150°C                                         |

| Lead Temperature (soldering, 10s)+300°C                                   |

| Soldering Temperature (reflow)+260°C                                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

| 20 TQFN                                               |                                       |  |  |  |  |

|-------------------------------------------------------|---------------------------------------|--|--|--|--|

| Package Code                                          | T2044+4C                              |  |  |  |  |

| Outline Number                                        | <u>21-100172</u>                      |  |  |  |  |

| Land Pattern Number                                   | <u>90-0409</u>                        |  |  |  |  |

| Thermal Resistance, Single Layer Board:               |                                       |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 48°C/W                                |  |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 2°C/W                                 |  |  |  |  |

| Thermal Resistance, Four Layer Board:                 | Thermal Resistance, Four Layer Board: |  |  |  |  |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 33°C/W                                |  |  |  |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$   | 2°C/W                                 |  |  |  |  |

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

## **Electrical Characteristics**

| PARAMETER                                              | SYMBOL                            | COND                                                                                                | ITIONS                  | MIN    | ТҮР  | MAX    | UNITS |

|--------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------|--------|------|--------|-------|

| POWER SUPPLY                                           |                                   |                                                                                                     |                         |        |      |        |       |

| V <sub>CC</sub> Supply Voltage                         | V <sub>CC</sub>                   |                                                                                                     |                         | 3.0    |      | 5.5    | V     |

| N/ Oursely Ourseat                                     |                                   |                                                                                                     | V <sub>CC</sub> = 3.3V  |        | 2.15 | 4.53   |       |

| V <sub>CC</sub> Supply Current                         | Icc                               | EN_ = high                                                                                          | V <sub>CC</sub> = 5.5V  |        | 0.80 | 2.06   | mA    |

| Positive High Voltage<br>Charge Pump Output<br>Voltage | VP                                | (Note 2)                                                                                            |                         | 30.60  |      | 36.50  | V     |

| Negative High Voltage<br>Charge Pump Output<br>Voltage | V <sub>N</sub>                    | (Note 2)                                                                                            |                         | -29.50 |      | -24.94 | V     |

| Logic Level Supply<br>Voltage                          | VL                                |                                                                                                     |                         | 1.62   |      | 5.5    | V     |

| Logic Level Supply<br>Current                          | ۱ <sub>L</sub>                    | EN_, A_, B_ = low of                                                                                | r high                  | -1     |      | +1     | μA    |

| SWITCH CHARACTERIS                                     |                                   |                                                                                                     |                         |        |      |        |       |

| Analog Signal Range                                    | V <sub>A_</sub> , V <sub>B_</sub> |                                                                                                     |                         | -25    |      | +25    | V     |

| Continuous Current<br>Through Switch                   | I <sub>A_</sub>                   | EN_ = high                                                                                          |                         | -200   |      | +200   | mA    |

| On-Resistance                                          | R <sub>ON</sub> +2                | -25V ≤ V <sub>A</sub> _,V <sub>B</sub> _ ≤<br>+25V, I <sub>IN</sub> =<br>±200mA ( <i>Figure 1</i> ) | T <sub>A</sub> = +85°C  |        | 1.15 | 2.5    | Ω     |

|                                                        |                                   |                                                                                                     | T <sub>A</sub> = +125°C |        | 1.15 | 3      |       |

| On-Resistance Flatness                                 | $\Delta R_{ON}$                   | $-25V \le V_A \le +25V, I_{IN} = \pm 200$ mA                                                        |                         |        | 18   | 120    | mΩ    |

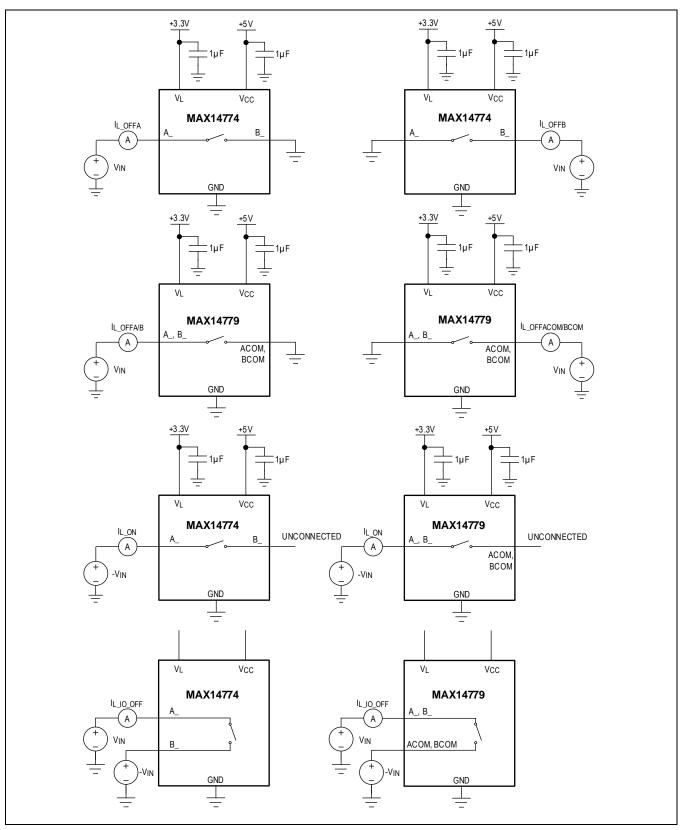

|                                                        | IL_OFFA                           | -25V ≤ V <sub>A</sub> _ ≤ +25V,<br>V <sub>B</sub> _ = 0V ( <u><i>Figure 2</i></u> )                 | T <sub>A</sub> = +85°C  | -100   |      | +100   | nA    |

| MAX14774 Off-Leakage                                   |                                   |                                                                                                     |                         | -300   |      | +300   |       |

| Current                                                | IL_OFFB                           | $-25V \le V_{B_{-}} \le +25V,$<br>$V_{A_{-}} = 0V (Figure 2)$                                       | T <sub>A</sub> = +85°C  | -100   |      | +100   |       |

|                                                        |                                   |                                                                                                     | T <sub>A</sub> = +125°C | -300   |      | +300   |       |

|                                                        |                                   | $-25V \le V_{A_{-}}, V_{B_{-}} \le$                                                                 | T <sub>A</sub> = +85°C  | -200   |      | +200   |       |

| MAX14779 Off-Leakage                                   | I <sub>L_OFFA/B</sub>             | +25V, V <sub>ACOM</sub> ,<br>V <sub>BCOM</sub> = 0V<br>( <u><i>Figure 2</i></u> )                   | T <sub>A</sub> = +125°C | -550   |      | +550   |       |

| Current                                                |                                   | -25V ≤ V <sub>ACOM</sub> ,                                                                          | T <sub>A</sub> = +85°C  | -200   |      | +200   | nA    |

|                                                        | IL_OFFACOM/B<br>COM               | V <sub>BCOM</sub> ≤ +25V,<br>V <sub>A</sub> _, V <sub>B</sub> _= 0V<br>( <u><i>Figure 2</i></u> )   | T <sub>A</sub> = +125°C | -550   |      | +550   |       |

| MAX14774 On-Leakage                                    |                                   | $-25V \le V_{A_{-}} \le +25V,$                                                                      | T <sub>A</sub> = +85°C  | -100   |      | +100   |       |

| Current                                                | IL_ON                             | B_ is unconnected<br>( <u>Figure 2</u> )                                                            | T <sub>A</sub> = +125°C | -300   |      | +300   | nA    |

|                                                        |                                   | $-25V \le V_{A_{-}}, V_{B_{-}} \le$                                                                 | T <sub>A</sub> = +85°C  | -200   |      | +200   |       |

| MAX14779 On-Leakage<br>Current                         | IL_ON                             | +25V, ACOM,<br>BCOM is<br>unconnected<br>( <u>Figure 2</u> )                                        | T <sub>A</sub> = +125°C | -550   |      | +550   | nA    |

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

| PARAMETER                                 | SYMBOL             |                                                                                                                              | ITIONS                                                              | MIN                  | TYP | MAX                  | UNITS |  |

|-------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------|-----|----------------------|-------|--|

| Power-Off Input-Output<br>Leakage Current | IL_IO_OFF          | $V_{CC} = 0V$ or unconnected, $3V \le  V_{A_{-}} - V_{B_{-}}  \le 50V$ . Current measured at A_, B_ pins ( <i>Figure 2</i> ) |                                                                     | -5                   |     | +5                   | μA    |  |

| DIGITAL LOGIC (EN_, S_                    | _)                 |                                                                                                                              |                                                                     |                      |     |                      |       |  |

| Input Voltage Low<br>Threshold            | VIL                |                                                                                                                              |                                                                     |                      |     | $0.3 	ext{ x V}_{L}$ | V     |  |

| Input Voltage High<br>Threshold           | V <sub>IH</sub>    |                                                                                                                              |                                                                     | 0.7 x V <sub>L</sub> |     |                      | V     |  |

| Input Logic Leakage<br>Current            | Ι <sub>ΙL</sub>    | $V_{S_{-}}, V_{EN_{-}} = 0V \text{ or } V$                                                                                   | $V_{S_{-}}, V_{EN_{-}} = 0V \text{ or } V_{L}$                      |                      |     | +1                   | μA    |  |

| DYNAMIC CHARACTERI                        | STICS              |                                                                                                                              |                                                                     |                      |     |                      |       |  |

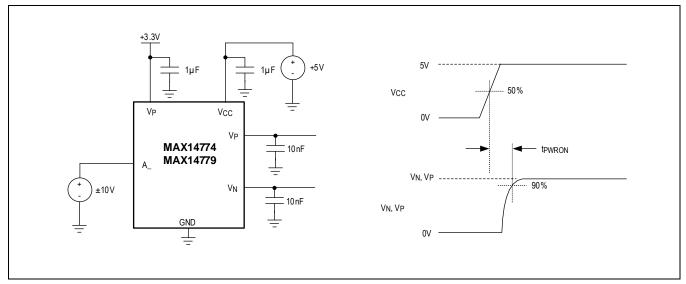

| Power-Up Time                             | t <sub>PWRON</sub> | $V_{A_{-}} = \pm 10V, C_{VP} = 0$<br>3) (Note 3)                                                                             | C <sub>VN</sub> = 10nF ( <u><i>Figure</i></u>                       |                      | 2.2 |                      | ms    |  |

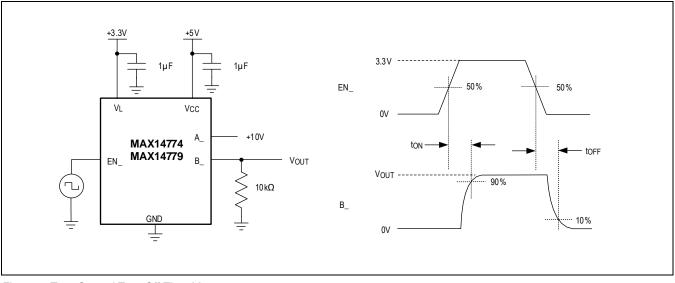

| Enable Turn-On Time                       | t <sub>ON</sub>    | $V_{A_{-}} = \pm 10V, R_{L} =$                                                                                               | MAX14774                                                            |                      | 28  | 60                   |       |  |

| Enable rum-On nime                        | UN                 | 10kΩ ( <u><i>Figure 4</i></u> )                                                                                              | MAX14779                                                            |                      | 326 | 600                  | μs    |  |

| Enable Turn-Off Time                      | tOFF               | $V_{A_{-}} = \pm 10V, R_{L} =$                                                                                               | MAX14774                                                            |                      | 48  | 160                  |       |  |

|                                           | OFF                | 10kΩ ( <u><i>Figure 4</i></u> )                                                                                              | MAX14779                                                            |                      | 48  | 160                  | μs    |  |

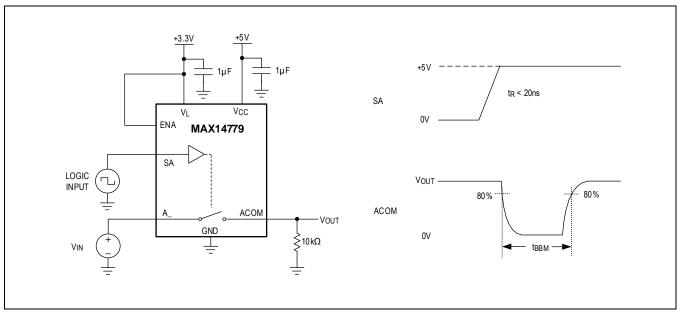

| MAX14779 Break-<br>Before-Make Time       | <sup>t</sup> BBM   | $V_{A_{-}} = \pm 10V, R_{L} = 10$                                                                                            | )kΩ ( <u>Figure 5</u> )                                             |                      | 289 | 500                  | μs    |  |

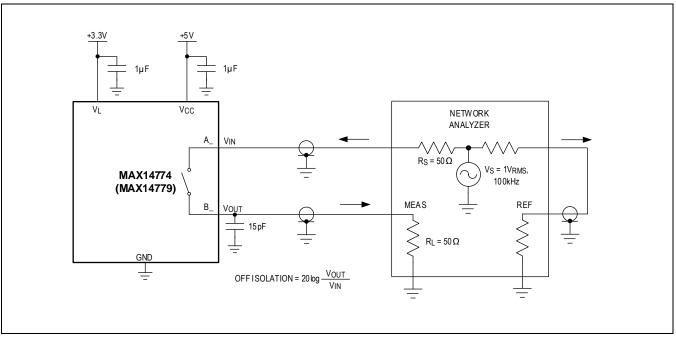

|                                           |                    | $V_{A_{-}} = 1V_{RMS}, f =$                                                                                                  | $V_{CC} = 3V \text{ to } 5.5V$                                      |                      | -80 |                      | dB    |  |

| MAX14774 Off-Isolation                    | V <sub>ISO</sub>   |                                                                                                                              | V <sub>CC</sub> = 0V or<br>unconnected                              |                      | -75 |                      |       |  |

|                                           |                    | V <sub>A</sub> _ = 1V <sub>RMS</sub> , f =                                                                                   | $V_{CC} = 3V$ to 5.5V                                               |                      | -80 |                      |       |  |

| MAX14779 Off-Isolation                    | V <sub>ISO</sub>   | $100 \text{kHz}, \text{R}_{\text{L}} = 50\Omega,$ $C_{\text{L}} = 15 \text{pF} (\underline{Figure})$ $\underline{6}$         | V <sub>CC</sub> = 0V or<br>unconnected                              |                      | -75 |                      | dB    |  |

|                                           |                    | V <sub>A</sub> _ = 1V <sub>RMS</sub> , f =                                                                                   | $V_{CC} = 3V \text{ to } 5.5V$                                      |                      | -90 |                      |       |  |

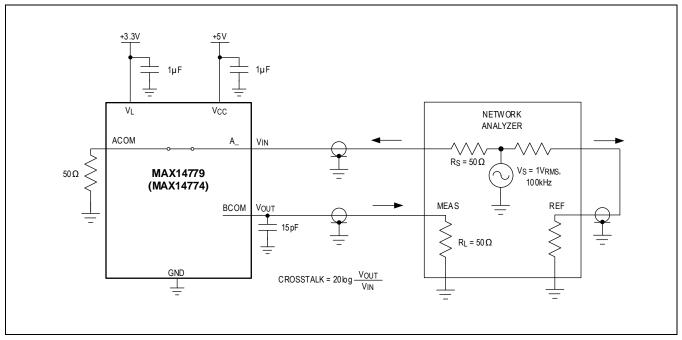

| MAX14774 Crosstalk                        | V <sub>CT</sub>    | 100kHz, $R_S = R_L =$<br>50 $\Omega$ , $C_L =$ 15pF<br>( <i>Figure 7</i> )                                                   | V <sub>CC</sub> = 0V or<br>unconnected                              |                      | -75 |                      | dB    |  |

|                                           |                    | V <sub>A</sub> _ = 1V <sub>RMS</sub> , f =                                                                                   | $V_{CC} = 3V$ to 5.5V                                               |                      | -90 |                      |       |  |

| MAX14779 Crosstalk                        | V <sub>CT</sub>    | 100kHz, $R_S = R_L =$<br>50 $\Omega$ , $C_L =$ 15pF<br>( <i>Figure 7</i> )                                                   | V <sub>CC</sub> = 0V or<br>unconnected                              |                      | -80 |                      | dB    |  |

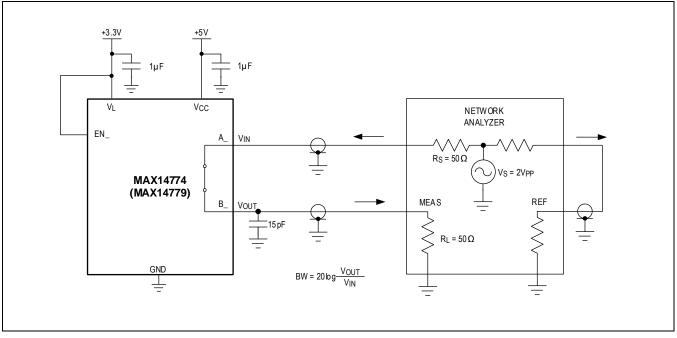

|                                           |                    | $V_{A_{-}} = 2V_{PP}, R_{S} =$                                                                                               | MAX14774                                                            | 147                  |     |                      |       |  |

| -3dB Bandwidth                            | BW                 | R <sub>L</sub> = 50Ω, C <sub>L</sub> =<br>15pF ( <u><i>Figure 8</i></u> )                                                    | MAX14779                                                            |                      | 78  |                      | MHz   |  |

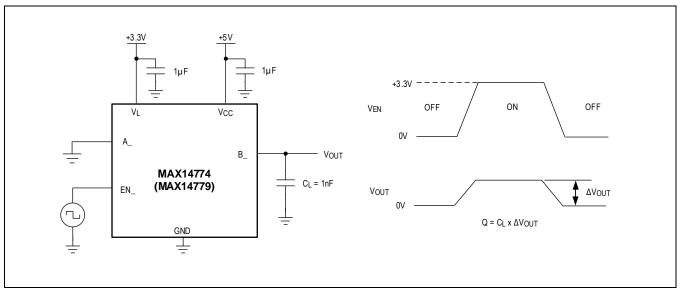

| Charge Injection                          | Q                  | $V_{A_{-}} = GND, C_{L} =$                                                                                                   | MAX14774                                                            |                      | 780 |                      | рС    |  |

|                                           |                    | 1nF ( <i><u>Figure 9</u></i> )                                                                                               | MAX14779                                                            |                      | 850 |                      | 40    |  |

| MAX14774 Input                            | C <sub>ON</sub>    | A_, B_ pins, f = 12M                                                                                                         | Hz, $EN_=high$                                                      |                      | 37  |                      |       |  |

| Capacitance                               | C <sub>OFF</sub>   |                                                                                                                              | At A_ when B_ = GND, or at B_ when A_<br>= GND, f = 1MHz, EN_ = low |                      | 31  |                      | pF    |  |

|                                           | C <sub>ON</sub>    | A_, B_ pins, f = 12M                                                                                                         | Hz, EN_ = high                                                      |                      | 61  |                      | pF    |  |

$(V_{CC} = 3.0V \text{ to } 5.5V, V_L = 3.3V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = 5V, T_A = +25^{\circ}C.)$  (*Note 1*)

#### Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

|                                          |                   |                                                                     |     | 00   |     | , ,   |

|------------------------------------------|-------------------|---------------------------------------------------------------------|-----|------|-----|-------|

| PARAMETER                                | SYMBOL            | CONDITIONS                                                          | MIN | TYP  | MAX | UNITS |

| MAX14779 Input<br>Capacitance            | C <sub>OFF</sub>  | At ACOM when A_ = GND or at BCOM when B_ = GND, f = 1MHz, EN_ = low |     | 54   |     |       |

| THERMAL SHUTDOWN                         |                   |                                                                     |     |      |     |       |

| Thermal Shutdown<br>Threshold            | T <sub>SHDN</sub> | Temperature rising                                                  |     | +162 |     | °C    |

| Thermal Shutdown<br>Threshold Hysteresis | T <sub>HYST</sub> |                                                                     |     | 23   |     | °C    |

| ESD PROTECTION                           |                   | •                                                                   | •   |      |     | •     |

| All pins                                 | V <sub>ESD</sub>  | Human Body Model                                                    |     | ±2   |     | kV    |

$(V_{CC} = 3.0V \text{ to } 5.5V, V_L = 3.3V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = 5V, T_A = +25^{\circ}C.)$  (*Note 1*)

Note 1: All units are production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

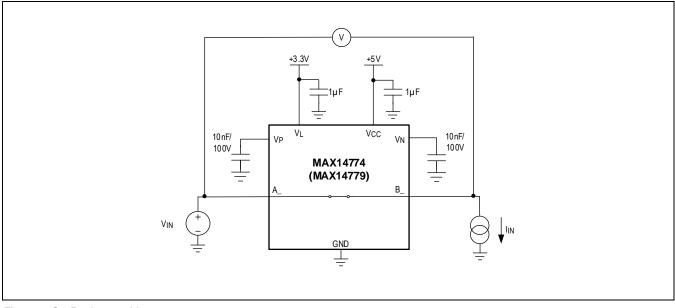

Note 2: Do not use V<sub>P</sub> or V<sub>N</sub> to power external circuitry. Connect at least 10nF/100V capacitor to both V<sub>P</sub> and V<sub>N</sub> with respect to GND.

Note 3: Power-up time is the time needed for  $V_P$  and  $V_N$  to reach steady-state.

#### **Timing Diagrams and Test Circuits**

Figure 1. On-Resistance Measurement

Figure 2. Leakage Current Measurements

Figure 3. Power-Up Time Measurement

Figure 4. Turn-On and Turn-Off Time Measurement

Figure 5. Break Before Make Time Measurement

Figure 6. Off Isolation Measurement

Figure 7. Crosstalk Measurement

Figure 8. Frequency Response Measurement

Figure 9. Charge Injection Measurement

#### Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

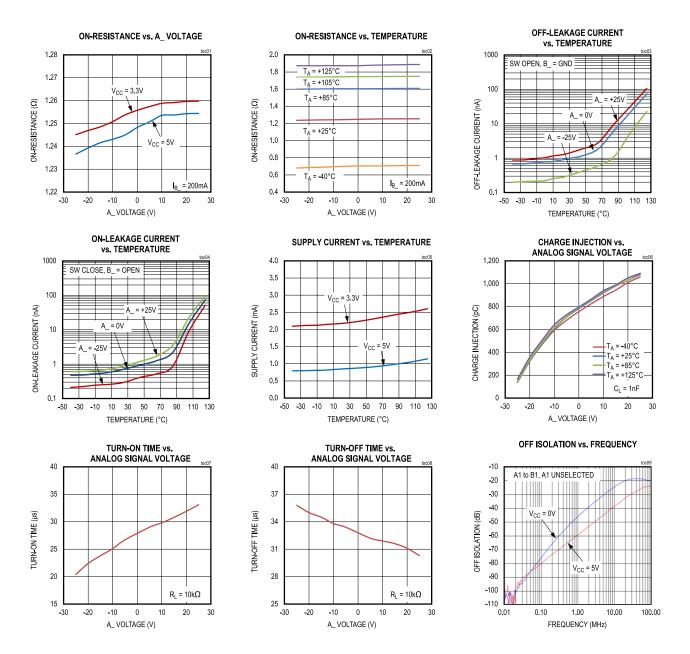

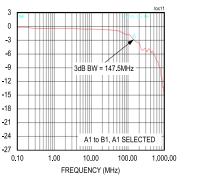

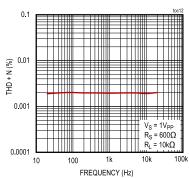

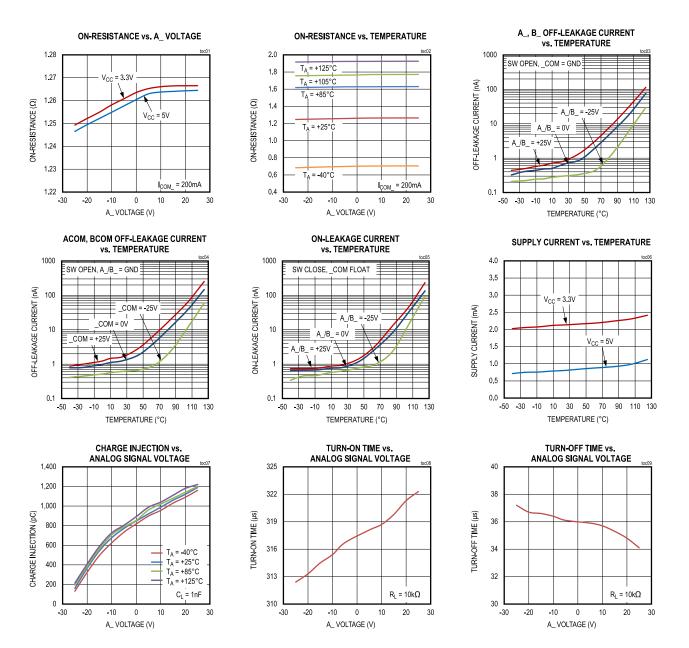

#### **Typical Operating Characteristics – MAX14774**

$V_{CC} = 5V$ ,  $V_L = 3.3V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

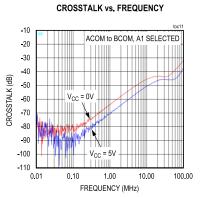

#### CROSSTALK vs. FREQUENCY -10 ADJACENT CHANNELS A1 to B2, A1 SELECTED -20 -30 -40 CROSSTALK (dB) -50 V<sub>CC</sub> = 0V -60 -70 -80 -90 -100 V<sub>CC</sub> = 5V -110 0.10 10.00 100.00 0.01 1.00 FREQUENCY (MHz)

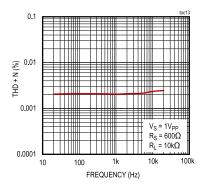

#### THD + N vs. FREQUENCY

ON-RESPONSE (dB)

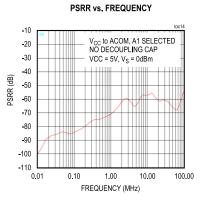

PSRR vs. FREQUENCY

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

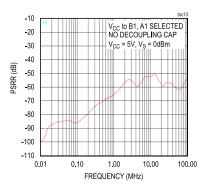

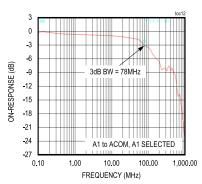

#### **Typical Operating Characteristics – MAX14779**

$V_{CC} = 5V$ ,  $V_L = 3.3V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

#### -10 A1 to ACOM, A2 SELECTED A1 = 1V<sub>RMS</sub> -20 -30 -40 $V_{CC} = 0V$ OFF ISOLATION (dB) -50 -60 -70 -80 V<sub>CC</sub> = 5V -90 -100 -110 0.10 1.00 10.00 100.00 0.01 FREQUENCY (MHz)

OFF ISOLATION vs. FREQUENCY

#### FREQUENCY RESPONSE

THD + N vs. FREQUENCY

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

## **Pin Configurations**

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

# **Pin Descriptions**

| PIN       |                   |                 |                                                                                                                                              |  |  |

|-----------|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX14774  | MAX14779          | NAME            | FUNCTION                                                                                                                                     |  |  |

| 1         | 1                 | VP              | Positive Charge-Pump Output. Bypass $V_P$ to GND with a 10nF/100V ceramic capacitor                                                          |  |  |

| 1         | I                 | <b>۲</b> ۲      | placed as close as possible to the device.                                                                                                   |  |  |

| 2         | 2                 | GND             | Ground.                                                                                                                                      |  |  |

| 3         | 3                 | V <sub>N</sub>  | Negative Charge-Pump Output. Bypass $V_N$ to GND with a 10nF/100V ceramic capacitor                                                          |  |  |

|           |                   |                 | placed as close as possible to the device.<br>Power Supply Input. Connect to a supply voltage between 3.0V to 5.5V. Bypass $V_{CC}$ to       |  |  |

| 4         | 4                 | V <sub>CC</sub> | GND with a $1\mu$ F ceramic capacitor placed as close as possible to the device.                                                             |  |  |

| 5         | 5                 | I.C.            | Internally Connected. Connect to GND.                                                                                                        |  |  |

|           |                   |                 | Logic Supply Input. Connect to a supply voltage between 1.62V to 5.5V. Bypass $V_{L}$ to GND                                                 |  |  |

| 13        | 13                | $V_L$           | with a $1\mu$ F ceramic capacitor placed as close as possible to the device.                                                                 |  |  |

| EP        | EP                | EP              | Exposed Pad. Connect to V <sub>N</sub> .                                                                                                     |  |  |

| 10, 16    | 10, 16, 18,<br>20 | N.C.            | Not Connected.                                                                                                                               |  |  |

| ANALOG I/ | 0                 |                 | ·                                                                                                                                            |  |  |

| 6         | 6                 | A1              | Analog Switch Terminal A1.                                                                                                                   |  |  |

| 7         | 7                 | A2              | Analog Switch Terminal A2.                                                                                                                   |  |  |

| 8         | -                 | A3              | Analog Switch Terminal A3.                                                                                                                   |  |  |

| 9         | -                 | A4              | Analog Switch Terminal A4.                                                                                                                   |  |  |

| -         | 19                | ACOM            | Analog Switch Terminal ACOM.                                                                                                                 |  |  |

| 17        | -                 | B4              | Analog Switch Terminal B4.                                                                                                                   |  |  |

| 18        | -                 | B3              | Analog Switch Terminal B3.                                                                                                                   |  |  |

| 19        | 9                 | B2              | Analog Switch Terminal B2.                                                                                                                   |  |  |

| 20        | 8                 | B1              | Analog Switch Terminal B1.                                                                                                                   |  |  |

| -         | 17                | BCOM            | Analog Switch Terminal BCOM.                                                                                                                 |  |  |

| CONTROL   | INPUTS            |                 |                                                                                                                                              |  |  |

| 11        | -                 | EN1             | Switch 1 Control Input. Drive EN1 high to close switch 1. Drive EN1 low to open switch 1.                                                    |  |  |

| 12        | -                 | EN2             | Switch 2 Control Input. Drive EN2 high to close switch 2. Drive EN2 low to open switch 2.                                                    |  |  |

| 14        | -                 | EN3             | Switch 3 Control Input. Drive EN3 high to close switch 3. Drive EN3 low to open switch 3.                                                    |  |  |

| 15        | -                 | EN4             | Switch 4 Control Input. Drive EN4 high to close switch 4. Drive EN4 low to open switch 4.                                                    |  |  |

| -         | 11                | ENA             | Switch A Enable Input. Drive ENA low to open A1 and A2 switches, independent of the SA input logic. Drive ENA high to enable SA control.     |  |  |

| -         | 12                | SA              | Switch A Control Input. Drive SA high to close switch A2. Drive SA low to close switch A1.<br>SA operation is conditional on ENA being high. |  |  |

| -         | 14                | ENB             | Switch B Enable Input. Drive ENB low to open B1 and B2 switches, independent of the SB input logic. Drive ENB high to enable SB control.     |  |  |

| -         | 15                | SB              | Switch B Control Input. Drive SB high to close switch B2. Drive SB low to close switch B1.<br>SB operation is conditional on ENB being high. |  |  |

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

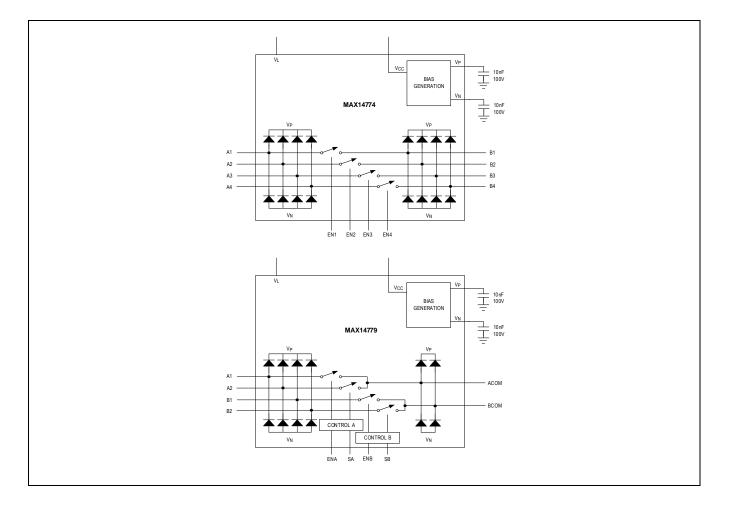

# **Functional Diagrams**

#### **Detailed Description**

The MAX14774 quad SPST and the MAX14779 dual SPDT Beyond-The-Rails switches support switching analog signals of up to  $\pm 25V$  using a single 3.0V to 5.5V supply. The MAX14774 is a quad SPST switch configuration with four EN\_ control inputs, and the MAX14779 is a dual SPDT switch configuration with two EN\_ and two S\_ control inputs. Both the MAX14774 and MAX14779 have a flexible 1.62V to 5.5V CMOS logic interface.

The switches feature  $2.5\Omega$  (max) on-resistance and  $18m\Omega$  (typ) flatness at 85°C. The MAX14774 has a low on-leakage current of ±100nA (max) while the MAX14779 has ±200nA (max) at 85°C. The switches maintain the performance over the entire common-mode voltage range to maximum signal integrity. Each device can carry up to 200mA (max) of continuous current in either direction while operating from -40°C to +125°C.

#### **Integrated Bias Generation**

The MAX14774/MAX14779 contain a total of three charge pumps to generate bias voltages for the internal switches: a 5V regulated charge pump, a positive high-voltage charge pump (V<sub>P</sub>), and a negative high-voltage charge pump (V<sub>N</sub>). When the V<sub>CC</sub> is above 4.75V (typ), the 5V charge pump is bypassed and V<sub>CC</sub> provides the input for the high-voltage charge pumps, reducing overall supply current. The voltage at V<sub>N</sub> is -27V (typ), the voltage at V<sub>P</sub> is +33V (typ), and the analog signal range is ±25V.

An external 10nF/100V (min) capacitor is required for each high-voltage charge pump between V<sub>P</sub>/V<sub>N</sub> and GND.

#### Logic Interface Supply

The MAX14774/MAX14779 feature a separate supply control input V<sub>L</sub> that sets the high and low thresholds for all logic inputs EN\_ and S\_. It allows flexible interfacing to controllers with a different logic level other than V<sub>CC</sub>. Drive V<sub>L</sub> with a voltage between 1.62V and 5.5V.

#### **Control Logic**

The MAX14774 is a quad SPST analog switch with four enable inputs EN1, EN2, EN3, and EN4. See <u>Table 1</u> for the switching logic.

| ENABLE PIN | POSITION | FUNCTION           |

|------------|----------|--------------------|

| EN1        | 0        | B1 Open            |

| ENI        | 1        | B1 connected to A1 |

| EN2        | 0        | B2 Open            |

| ENZ        | 1        | B2 connected to A2 |

| ENIO       | 0        | B3 Open            |

| EN3        | 1        | B3 connected to A3 |

| <b>EN4</b> | 0        | B4 Open            |

| EN4        | 1        | B4 connected to A4 |

#### Table 1. MAX14774 Control Logic

The MAX14779 is a dual SPDT analog switch with two enable inputs ENA and ENB, and two digital select inputs SA and SB. See <u>Table 2</u> for the switching logic.

#### Table 2. MAX14779 Control Logic

| ENA POSITION | SA POSITION | ACOM CONNECTED TO |

|--------------|-------------|-------------------|

| 0            | Х           | Open              |

| 1            | 0           | A1                |

| 1            | 1           | A2                |

| ENB POSITION | SB POSITION | BCOM CONNECTED TO |

| 0            | X           | Open              |

| 1            | 0           | B1                |

| 1            | 1           | B2                |

X is Don't Care.

#### **Applications Information**

#### **Non-Powered Condition**

To understand the behavior of the MAX14774/MAX14779 when not powered (i.e.,  $V_{CC} = 0V$ ), the transient and DC signal conditions should be considered separately.

Every A\_ and B\_ pin has internal diodes connected to V<sub>P</sub> and V<sub>N</sub>. Applying a positive voltage on A\_ or B\_ charges the capacitor on V<sub>P</sub> through the diode to V<sub>P</sub>. Applying a negative voltage on A\_ or B\_ charges the capacitor on V<sub>N</sub> through the diode to V<sub>N</sub>. Switch terminals A\_ and B\_ support voltages ranging from -25V to +25V when the devices are unpowered.

Under transient conditions, the voltages applied to the A\_ or B\_ pins charge the capacitors on V<sub>P</sub> and V<sub>N</sub> and at the same time the internal off-leakage current ( $I_{L_IO_OFF}$ ) discharges these capacitors. Thus, the input impedance into the A\_ or B\_ pin is determined by the capacitors on V<sub>P</sub>/V<sub>N</sub> and their charge states.

Under DC conditions, when a voltage is applied to an A\_ or B\_ pin with V<sub>CC</sub> unpowered, the switch is open when the voltage difference between the A\_ and B\_ pin is larger than 3V. Under these conditions, the DC leakage current flows into the pin. When  $|V_{A_{-}} - V_{B_{-}}| < 3V$ , the switch is not fully open, and currents up to a few mA can flow between the A\_ and B\_ pins.

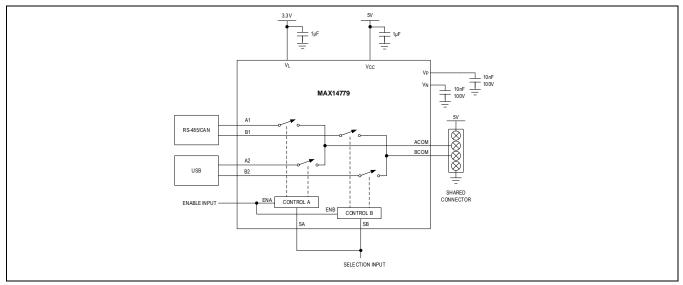

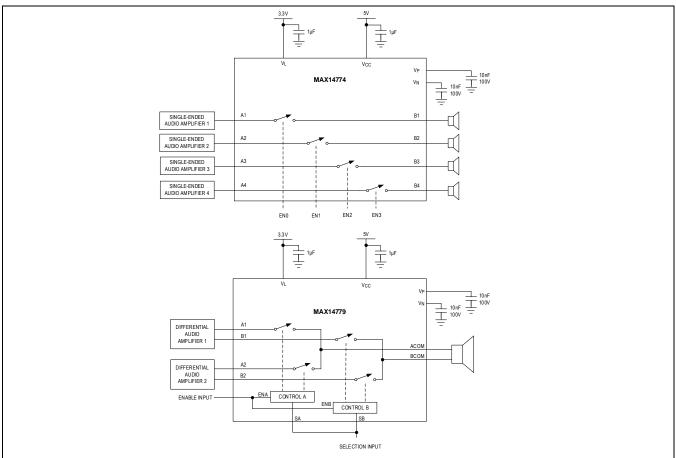

## **Typical Application Circuits**

#### Switching between RS-485/CAN and USB Transceivers

#### **Switching Audio Amplifiers**

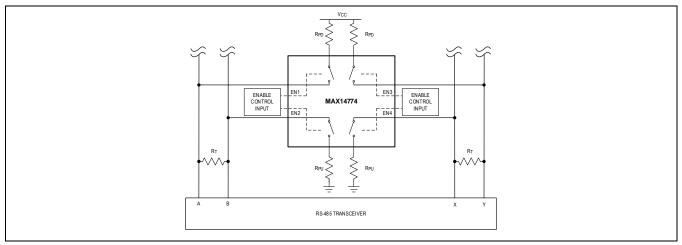

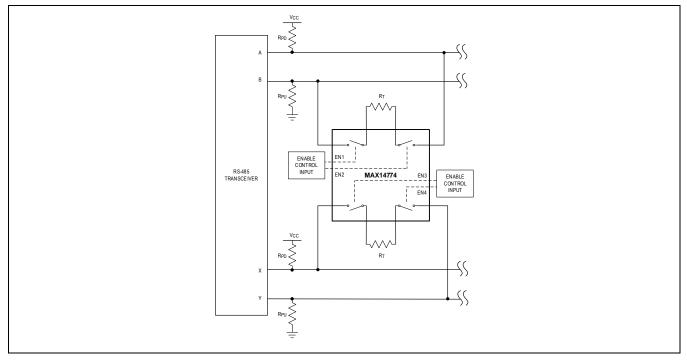

#### **RS-485 Fail-Safe Biasing Switch**

#### **RS-485 Termination Resistor Switch**

#### **Ordering Information**

| PART NUMBER  | CONFIGURATION | TEMPERATURE RANGE | PIN-PACKAGE |

|--------------|---------------|-------------------|-------------|

| MAX14774ATP+ | Quad SPST     | -40°C to +125°C   | 20 TQFN     |

| MAX14779ATP+ | Dual SPDT     | -40°C to +125°C   | 20 TQFN     |

+Denotes a lead(Pb)-free/RoHS-compliant package.

#### **Chip Information**

PROCESS: BICMOS

## Quad SPST/Dual SPDT Beyond-The-Rails Analog Switches

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION              |  |

|--------------------|------------------|--------------------------|--|

| 0                  | 5/22             | Release for Market Intro |  |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.