Resources

Click here to ask an associate for production status of specific part numbers.

## **Dual IO-Link Master Transceiver with Integrated** Framers and L+ Supply Controllers

### MAX14819/MAX14819A

#### **General Description**

The MAX14819/MAX14819A low-power, dual-channel, IO-Link® master transceiver with sensor/actuator powersupply controllers is fully compliant with the latest IO-Link and binary input standards and test specifications, IEC 61131-2, IEC 61131-9 SDCI, and IO-Link 1.1.3. This master transceiver also includes two auxiliary digital input (DI) channels.

The MAX14819/MAX14819A is configurable to operate either with external UARTs or using the integrated framers on the IC.

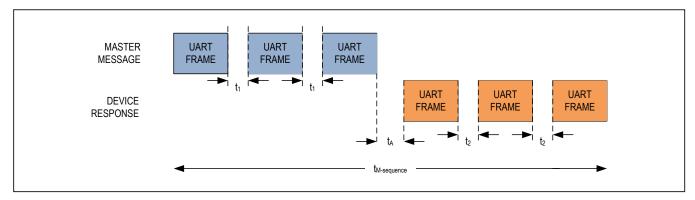

To ease selection of microcontroller, the master transceiver features frame handlers with UARTs and FIFOs. These are designed to simplify time critical control of all IO-Link M-sequence frame types. The MAX14819/MAX14819A also features autonomous cycle timers, reducing the need for accurate controller timing. Integrated establish-communication sequencers also simplify wake-up management.

The device message response delay on the MAX14819A can be disabled when using the frame handler and MAX14819A features higher L+ thresholds than the MAX14819. The MAX14819A receivers also feature increased high-frequency signal isolation compared to the MAX14819.

The MAX14819/MAX14819A integrates two low-power sensor supply controllers with advanced current limiting, reverse current-blocking, and reverse polarity protection capability to enable low-power robust solutions.

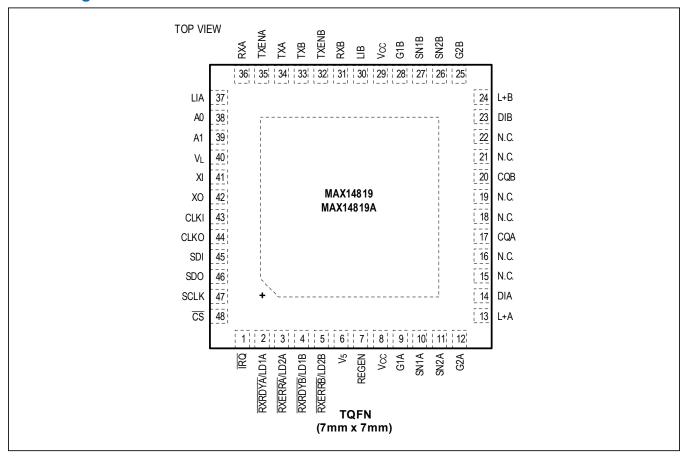

The MAX14819/MAX14819A is available in a 48-pin (7mm x 7mm) TQFN package and is specified over the extended -40°C to +125°C temperature range.

### **Applications**

- IO-Link Master Systems

- IO-Link Gateways

#### **Benefits and Features**

- Low-Power Architecture

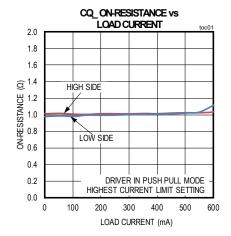

- 1Ω (typ) Driver On-Resistance

- 1.9mA (typ) Total Supply Current for 2 Channels

- · Current Limiters with 15mV Sense Voltage

- Integrated IO-Link Framer Eliminates Need for **External UARTs**

- Integrated Cycle Timer Relieves Microcontroller from Timing-Critical Tasks

- High Configurability and Integration Reduce SKUs

- Two Auxiliary Type 1/Type 3 Digital Inputs

- Supports NPN Sensors

- Dual 24V Sensor Supply Controllers Include:

- Large Capacitive Load Charge Capability

- 2A and Higher Load Currents

- Integrated Protection Enables Robust Systems

- · Reverse Polarity Protection on All Interface Pins

- Overvoltage Tolerance on All Interface Pins

- C/Q and DI Fully Compliant with IEC 61131-2

- C/Q Compliant with IO-Link 1.1.3.

- Reverse Current Blocking on L+ and C/Q

- · 65V Absolute Max Ratings for TVS Flexibility

- · Glitch Filters for Improved Burst Resilience

- -40°C to +125°C Operating Temperature Range

Ordering Information appears at end of data sheet.

IO-Link is a registered trademark of Profibus User Organization (PNO).

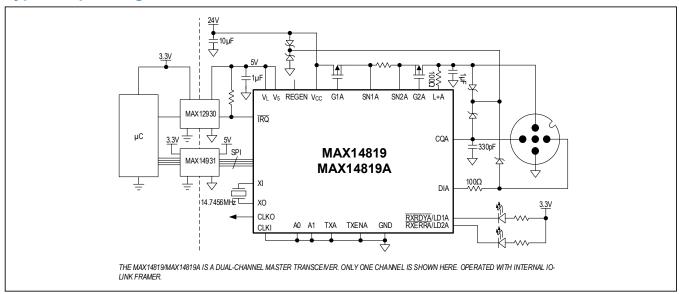

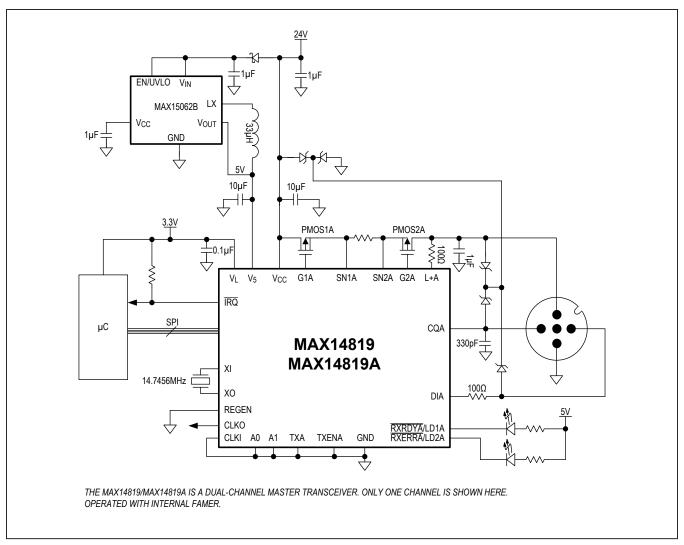

## **Typical Operating Circuit**

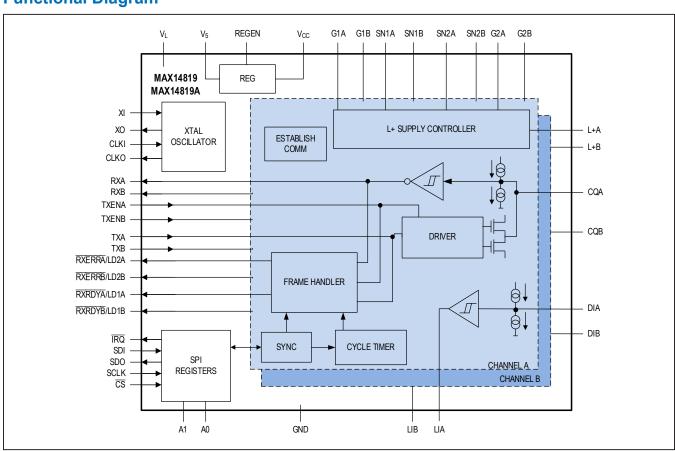

## **Functional Diagram**

## Dual IO-Link Master Transceiver with Integrated Framers and L+ Supply Controllers

### **Absolute Maximum Ratings**

| (All voltages referenced to GND, unless otherwise noted.)                               | Logic Outputs                                       |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------|

| V <sub>CC</sub> max [(V <sub>PM</sub> - 70V), (V <sub>CQ</sub> - 70V)] to +65V          | SDO, ĪRQ, LI_, RX_, RXRDY_/LD1_,                    |

| V <sub>5</sub> , V <sub>L</sub> 0.3V to +6V                                             | RXERR_/LD2_, CLKO0.3V to (V <sub>L</sub> + 0.3V)    |

| REGEN0.3V to the min(V <sub>CC</sub> + 0.3V or +6V)                                     | Continuous Current Into GND and V <sub>CC</sub> ±2A |

| CQA, CQB(V <sub>CC</sub> - 70V) to +65V                                                 | Continuous Current Into CQA and CQB±1A              |

| DIA, DIB, L+A, L+B(V <sub>PM</sub> - 70V) to +65V                                       | Continuous Current Into V <sub>5</sub> ±100mA       |

| SN1A, SN1B0.3V to +65V                                                                  | Continuous Current Into Any Other Pin±50mA          |

| SN2A(V <sub>SN1A</sub> - 0.3V) to (V <sub>SN1A</sub> + 0.3V)                            | Continuous Power Dissipation                        |

| SN2B(V <sub>SN1B</sub> - 0.3V) to (V <sub>SN1B</sub> + 0.3V)                            | TQFN (derate 40mW/°C above +70°C)3.2W               |

| G1A, G2Amax (-0.3V, [V <sub>SN1A</sub> - 14V]) to (V <sub>SN1A</sub> + 0.3V)            | Operating Temperature Range40°C to +125°C           |

| G1B, G2Bmax (-0.3V, [V <sub>SN1B</sub> - 14V]) to (V <sub>SN1B</sub> + 0.3V)            | Maximum Junction TemperatureInternally Limited      |

| XI, XO0.3V to (V <sub>5</sub> + 0.3V)                                                   | Storage Temperature Range65°C to +150°C             |

| Logic Inputs                                                                            | Soldering Temperature (reflow)+260°C                |

| $\overline{\text{CS}}$ , SDI, SCLK, A_, TXEN_, TX_, CLKI0.3V to (V <sub>L</sub> + 0.3V) |                                                     |

$V_{PM}$  = max (0V,  $V_{CC}$ , DIA, DIB, SN1A, SN1B, L+A, L+B)

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

| PACKAGE TYPE: 48 TQFN-EP               |          |  |  |  |  |

|----------------------------------------|----------|--|--|--|--|

| Package Code                           | T4877+4C |  |  |  |  |

| Outline Number                         | 21-0144  |  |  |  |  |

| Land Pattern Number                    | 90-0130  |  |  |  |  |

| MULTILAYER BOARD                       |          |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 25°C/W   |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 1°C/W    |  |  |  |  |

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

## Dual IO-Link Master Transceiver with Integrated Framers and L+ Supply Controllers

#### **DC Electrical Characteristics**

$(V_{CC} = 9V \text{ to } 36\text{V}, V_5 = 4.5\text{V to } 5.5\text{V}, V_L = 1.62\text{V to } 5.5\text{V}, V_{GND} = 0\text{V}, \text{ all logic inputs at } V_L \text{ or GND}; T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$

| PARAMETER                                                     | SYMBOL                   | CONE                                                                                     | DITIONS          | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------|------------------|------|------|------|-------|

| V <sub>CC</sub> POWER                                         |                          |                                                                                          |                  |      |      |      | •     |

| V <sub>CC</sub> Supply Voltage                                | V <sub>CC</sub>          |                                                                                          |                  | 9    |      | 36   | V     |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold             | V <sub>CCUVLO</sub>      | V <sub>CC</sub> rising                                                                   |                  | 7    |      | 9    | V     |

| V <sub>CC</sub> Undervoltage-Lockout-<br>Threshold Hysteresis | V <sub>CCUVLO_HYST</sub> |                                                                                          |                  |      | 340  |      | mV    |

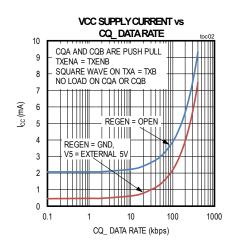

| V <sub>CC</sub> Supply Current                                | lcc                      | REGEN = GND,<br>L+EnA = L+EnB =<br>1, external clock<br>selected, CQ_ in                 | CQ_ outputs low  |      | 0.4  | 0.75 | - mA  |

| VCC Supply Suitent                                            | icc                      | push-pull<br>configuration,<br>CL[1:0] = 00, no<br>load on CQ_                           | CQ_ outputs high |      | 0.5  | 0.85 | III/A |

| V <sub>CC</sub> Warning Threshold                             | V <sub>CC_WRN</sub>      |                                                                                          |                  | 16   |      | 18   | V     |

| V <sub>CC</sub> Warning Threshold<br>Hysteresis               | V <sub>CC_WHY</sub>      |                                                                                          |                  |      | 500  |      | mV    |

| V <sub>5</sub> POWER                                          |                          |                                                                                          |                  |      |      |      |       |

| V <sub>5</sub> Supply Voltage                                 | V <sub>5</sub>           | REGEN = GND                                                                              |                  | 4.5  | 5    | 5.5  | V     |

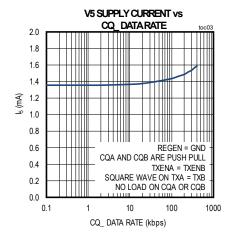

| V. Supply Current                                             | L                        | REGEN = GND,<br>L+EnA = L+EnB =<br>1, external clock<br>selected, CQ_ in                 | CQ_ outputs low  |      | 1.4  | 1.9  | - mA  |

| V <sub>5</sub> Supply Current                                 | I <sub>V5</sub>          | push-pull<br>configuration,<br>CL[1:0] = 00, no<br>load on CQ_                           | CQ outputs high  |      | 1.4  | 1.9  | IIIA  |

| V <sub>5</sub> LINEAR REGULATOR                               |                          |                                                                                          |                  |      |      |      |       |

| V <sub>5</sub> Output Voltage                                 | V <sub>5</sub>           | REGEN unconnect CQ_ disabled, L+E                                                        |                  | 4.75 |      | 5.25 | V     |

| V <sub>5</sub> Current Limit                                  | I <sub>CL_V5</sub>       | REGEN unconnect<br>L+EnA = L+EnB = 0                                                     | _                | 20   |      |      | mA    |

| V <sub>5</sub> Load Regulation                                | dV <sub>V5</sub>         | REGEN unconnected, CQ_ disabled,<br>L+EnA = L+EnB = 0, 0mA ≤ I <sub>LOAD</sub> ≤<br>20mA |                  |      | -0.1 |      | mV/mA |

| REGEN Pullup Current                                          | I <sub>REGEN</sub>       | V <sub>REGEN</sub> = 0V                                                                  |                  | 5    |      | 30   | μΑ    |

| REGEN Threshold                                               | V <sub>TH_REGEN</sub>    |                                                                                          |                  | 0.2  | 1.8  | 2.6  | V     |

## Dual IO-Link Master Transceiver with Integrated Framers and L+ Supply Controllers

### **DC Electrical Characteristics (continued)**

$(V_{CC}$  = 9V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 1.62V to 5.5V,  $V_{GND}$  = 0V, all logic inputs at  $V_L$  or GND;  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                           | SYMBOL                                 | COND                                                   | ITIONS                                          | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------------------|----------------------------------------|--------------------------------------------------------|-------------------------------------------------|------|-----|------|-------|

| V <sub>L</sub> POWER                                |                                        |                                                        |                                                 |      |     |      |       |

| V <sub>L</sub> Logic-Level Supply<br>Voltage        | V <sub>L</sub>                         |                                                        |                                                 | 1.62 |     | 5.5  | V     |

| V <sub>L</sub> Undervoltage Threshold               | V <sub>LUVLO</sub>                     | V <sub>L</sub> falling                                 |                                                 | 0.4  |     | 1.5  | V     |

| V <sub>L</sub> Undervoltage Threshold<br>Hysteresis | V <sub>LUVHYS</sub>                    |                                                        |                                                 |      | 50  |      | mV    |

| V <sub>L</sub> Logic-Level Supply<br>Current        | IL                                     | All logic inputs at V <sub>L</sub> outputs unconnected |                                                 |      |     | 5    | μА    |

| CQ_ DRIVER                                          | 1                                      |                                                        |                                                 |      |     |      | 1     |

| Driver On-Resistance                                | R <sub>OH</sub>                        | High-side enabled, I                                   | LOAD = -200mA                                   |      | 1.0 | 2    | Ω     |

| Driver On-Resistance                                | R <sub>OL</sub>                        | Low-side enabled, I <sub>L</sub>                       | _OAD = +200mA                                   |      | 1.0 | 2.2  |       |

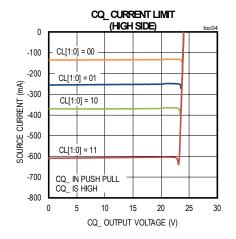

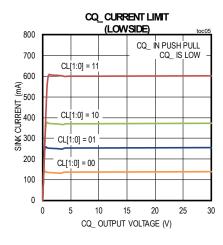

|                                                     |                                        |                                                        | CL[1:0] = 00                                    | 100  |     | 150  |       |

|                                                     |                                        | $V_{CO} = (V_{CC} - 3V)$                               | CL[1:0] = 01                                    | 190  |     | 280  | mA    |

| Driver Current Limit                                | I <sub>CL</sub>                        | $V_{CQ} = (V_{CC} - 3V)$<br>or $3V$                    | CL[1:0] = 10                                    | 280  |     | 410  |       |

|                                                     |                                        |                                                        | CL[1:0] = 11                                    | 500  |     | 650  |       |

| CQ_, DI_ RECEIVER                                   |                                        |                                                        |                                                 |      |     |      |       |

| CQ_, DI_ Input Threshold                            | V <sub>TH</sub>                        | CQ_ driver disabled                                    | IEC3Th_/DiEC3Th<br>= 0                          | 10.5 |     | 13.0 | V     |

| High                                                | V IH                                   | CQ_ unver disabled                                     | IEC3Th_/DiEC3Th<br>= 1                          | 7.5  |     | 11.0 | V     |

| CQ_, DI_ Input Threshold                            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \  | CO driver disabled                                     | IEC3Th_/DiEC3Th<br>= 0                          | 8.0  |     | 11.5 |       |

| Low                                                 | V <sub>TL</sub>                        | CQ_ driver disabled                                    | IEC3Th_/DiEC3Th<br>= 1                          | 6.0  |     | 8.0  | V     |

| CQ_, DI_ Input Threshold                            |                                        |                                                        | IEC3Th_/DiEC3Th<br>= 0                          |      | 2   |      | - V   |

| Hysteresis                                          | V <sub>HYS</sub>                       | CQ_ driver disabled                                    | IEC3Th_/DiEC3Th<br>= 1                          |      | 2   |      | V     |

|                                                     |                                        | V <sub>CQ_</sub> > 5V,                                 | 2mA pulldown<br>enabled<br>(SinkSel_[1:0] = 10) | 2    | 2.5 | 2.75 | - m^  |

| CQ_ Current Sink                                    | nk I <sub>CQ_SNK</sub> SourceSink_ = 0 | SourceSink_ = 0                                        | 5mA pulldown<br>enabled<br>(SinkSel_[1:0] = 01) | 5    | 5.8 | 6.6  | mA    |

## Dual IO-Link Master Transceiver with Integrated Framers and L+ Supply Controllers

### **DC Electrical Characteristics (continued)**

$(V_{CC}$  = 9V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 1.62V to 5.5V,  $V_{GND}$  = 0V, all logic inputs at  $V_L$  or GND;  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | SYMBOL              | COND                                                                                                                                                | ITIONS                                            | MIN   | TYP  | MAX  | UNITS |

|-----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------|------|------|-------|

| CQ Current Source                       | loo one             | (V <sub>CC</sub> - V <sub>CQ</sub> ) > 5V,                                                                                                          | 2mA pullup enabled<br>(SinkSel_[1:0] = 10)        | -2.75 | -2.5 | -2   | - mA  |

| CQ_ Current Source                      | I <sub>CQ_SRC</sub> | SourceSink_ = 1                                                                                                                                     | 5mA pullup enabled (SinkSel_[1:0] = 01)           | -6.6  | -5.8 | -5   | IIIA  |

| CQ_ Weak Pulldown Current               | I <sub>CQ_PD</sub>  | Driver disabled (Drv<br>SourceSink = 0, wea<br>(SinkSel_[1:0] = 11)                                                                                 | ak pulldown enabled                               | 150   |      | 250  | μA    |

| CQ_ Weak Pullup Current                 | lcq_pu              | Driver disabled (Drv<br>SourceSink = 1, wea<br>(SinkSel_[1:0] = 11)                                                                                 | ak pullup enabled                                 | -250  |      | -150 | μA    |

| CQ_ Input Current                       | lca                 | CQ_ driver enabled<br>CQ_set to high imper<br>pulldown disabled (S<br>receiver enabled, V <sub>C</sub><br>-1V < V <sub>CQ</sub> < (V <sub>CC</sub>  | edance, pullup and SinkSel_[1:0] = 00), CC = 24V, | -60   |      | +400 | μА    |

| CQ_ Input Current, Extended Range       | lcq_ext             | CQ_ driver enabled<br>CQ_set to high imper<br>pulldown disabled (S<br>receiver enabled, V <sub>C</sub><br>(V <sub>CC</sub> - 65V) < V <sub>CQ</sub> | edance, pullup and SinkSel_[1:0] = 00), CC = 24V, | -200  |      | +500 | μА    |

| CQ_ Leakage Current                     | lcq_lkg             | CQ_ driver disabled<br>and pulldown disabl<br>00), receiver enable<br>(V <sub>CC</sub> - 65V) < V <sub>CQ</sub> _                                   | d, V <sub>CC</sub> = 24V,                         | -100  |      | +100 | μA    |

| CQ_ Push-Pull High<br>Impedance Current | lcq_Hiz             | CQ_ driver enabled<br>push-pull, pullup and<br>(SinkSel_[1:0] = 00)<br>V <sub>CC</sub> = 24V, 0V < V <sub>C</sub>                                   | , receiver enabled,                               | -50   |      | +50  | μА    |

| DI_ Current Sink                        | I <sub>DI_SNK</sub> | V <sub>DI</sub> _ > 5V, DiCSink                                                                                                                     | = 1                                               | 2     | 2.5  | 3    | mA    |

| DI_ Current Source                      | I <sub>DI_SRC</sub> | V <sub>CC</sub> - V <sub>DI</sub> _ > 5V, Dic                                                                                                       | CSource = 1                                       | -3    | -2.5 | -2   | mA    |

| DI_ Input Current                       | I <sub>DI</sub>     | Pullup and pulldown disabled, DI_<br>receiver enabled, V <sub>CC</sub> = 24V,<br>-1V < V <sub>DI_</sub> < (V <sub>CC</sub> + 1V)                    |                                                   | -5    |      | +50  | μA    |

| DI_ Input Current, Extended<br>Range    | <sup>I</sup> DI_EXT | Pullup and pulldown<br>receiver enabled, V <sub>0</sub><br>(V <sub>CC</sub> - 65V) < V <sub>DI</sub>                                                | CC = 24V,                                         | -100  |      | +100 | μА    |

## Dual IO-Link Master Transceiver with Integrated Framers and L+ Supply Controllers

### **DC Electrical Characteristics (continued)**

$(V_{CC} = 9V \text{ to } 36V, V_5 = 4.5V \text{ to } 5.5V, V_L = 1.62V \text{ to } 5.5V, V_{GND} = 0V, \text{ all logic inputs at } V_L \text{ or GND}; T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = 24V, V_5 = 5V, V_L = 3.3V, \text{ and } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.}$  (Note 1)

| PARAMETER                                              | SYMBOL                | CONDITIONS                                                                                      | MIN                     | TYP     | MAX                  | UNITS |

|--------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|-------------------------|---------|----------------------|-------|

| LOGIC INPUTS (CS, SDI, SCL                             | K, A1, A0, TXEN       | IA, TXENB, TXA, TXB, CLKI)                                                                      |                         |         |                      |       |

| Logic Input Voltage Low                                | V <sub>IL</sub>       |                                                                                                 |                         |         | 0.2 x V <sub>L</sub> | V     |

| Logic Input Voltage High                               | V <sub>IH</sub>       |                                                                                                 | 0.8 x V <sub>L</sub>    |         |                      | V     |

| Logic Input Leakage Current                            | I <sub>LEAK</sub>     | Logic input = GND or V <sub>L</sub>                                                             | -1                      |         | +1                   | μA    |

| LOGIC OUTPUTS (SDO, IRQ,                               | LIA, LIB, RXA, F      | RXB, RXRDYA/LD1A, RXERRA/LD2A, RXI                                                              | RDYB/LD1B               | , RXERF | RB/LD2B, C           | CLKO) |

| Logic Output Voltage Low                               | V <sub>OL</sub>       | I <sub>OUT</sub> = -5mA                                                                         |                         |         | 0.4                  | V     |

| Logic Output Voltage High                              | V <sub>OH</sub>       | RX_, LI_, SDO, and CLKO, I <sub>OUT</sub> = 5mA                                                 | V <sub>L</sub> - 0.4    |         |                      | V     |

| Output Leakage Current                                 | ІОН                   | RXRDY_/LD1_, RXERR_/LD2_, IRQ, output is high impedance, output is pulled up to 5V              | -1                      |         | +1                   | μA    |

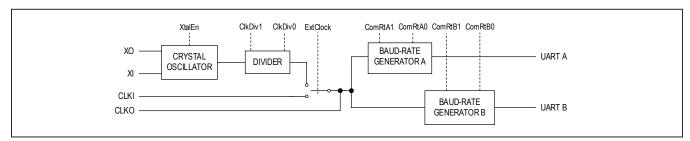

| CRYSTAL OSCILLATOR (XI, )                              | (O)                   |                                                                                                 |                         |         |                      |       |

| Crystal Oscillator Current<br>Supply                   | I <sub>V5_XTAL</sub>  | f <sub>XTAL</sub> = 14.7456MHz, V <sub>5</sub> supply current increase versus external clocking |                         | 240     |                      | μA    |

| Crystal Equivalent Series<br>Resistance                | ESR <sub>XTAL</sub>   | f <sub>XTAL</sub> = 14.7456MHz (Note 2)                                                         |                         |         | 75                   | Ω     |

| Crystal Shunt Capacitance                              | C <sub>OXTAL</sub>    | f <sub>XTAL</sub> = 14.7456MHz (Note 2)                                                         |                         |         | 8                    | pF    |

| Input Capacitance                                      | CIN                   | XI                                                                                              |                         | 10      |                      | pF    |

| піриї Сарасііапсе                                      | CIN                   | XO                                                                                              |                         | 10      |                      | ρF    |

| INTERNAL OSCILLATOR                                    |                       |                                                                                                 |                         |         |                      |       |

| Internal Oscillator Current<br>Consumption             | I <sub>V5_OSC</sub>   | (Notes 3, 4)                                                                                    |                         | 55      |                      | μA    |

| EXTERNAL CLOCK INPUT (C                                | LKI)                  |                                                                                                 |                         |         |                      |       |

| External Clock Frequency                               | f <sub>ECLK</sub>     |                                                                                                 |                         | 3.686   |                      | MHz   |

| External Clock Detection                               | f <sub>ECLK_DET</sub> | Minimum CLKI frequency for operation                                                            | 0.5                     |         | 2                    | MHz   |

| CLKI Capacitance                                       | C <sub>CLKI</sub>     |                                                                                                 |                         | 2       |                      | pF    |

| L+ SENSOR SUPPLIES WITH                                | CURRENT LIMI          | TING AND REVERSE BLOCKING (L+A, L                                                               | +B)                     |         |                      |       |

| Reverse Current Blocking<br>Threshold                  | V <sub>TH_RCB</sub>   | V <sub>RCB</sub> = (V <sub>SN1</sub> V <sub>CC</sub> )                                          |                         |         | 160                  | mV    |

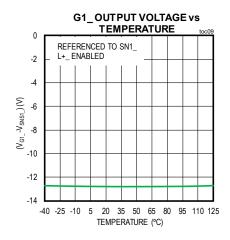

| G1_/G2_ Gate-to-Source<br>On-Voltage                   | V <sub>G_ON</sub>     | V <sub>SN1</sub> _ > 18V                                                                        | V <sub>SN1_</sub> - 14V |         | V <sub>SN1</sub>     | ٧     |

| G2_ Minimum Gate-to-Source<br>Voltage Under Regulation | V <sub>G2_REG</sub>   |                                                                                                 | V <sub>SN1</sub> - 0.8V |         |                      | ٧     |

| G1_ Gate Turn-Off Switch<br>Resistance                 | R <sub>G1_OFF</sub>   | G1_ pulled to SN1_                                                                              |                         | 50      |                      | Ω     |

| G2_ Gate Turn-Off Switch<br>Resistance                 | R <sub>G2_OFF</sub>   | G2_ pulled to SN2_                                                                              |                         | 50      |                      | Ω     |

## Dual IO-Link Master Transceiver with Integrated Framers and L+ Supply Controllers

### **DC Electrical Characteristics (continued)**

$(V_{CC}$  = 9V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 1.62V to 5.5V,  $V_{GND}$  = 0V, all logic inputs at  $V_L$  or GND;  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                  | SYMBOL                | CON                                                                                                          | IDITIONS                                                           | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------|------|-------|-------|

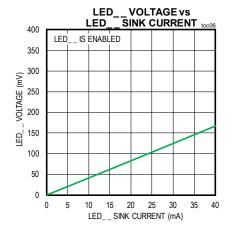

| L+_ Current-Limit Threshold                | V <sub>CL_T</sub>     | V <sub>CL_T</sub> = (V <sub>SN1_</sub> -                                                                     | V <sub>SN2</sub> _), L+CL2X_ = 0                                   | 12.75 | 15   | 18.5  | mV    |

| L+_ Double Current-Limit Threshold         | V <sub>CL_2T</sub>    | V <sub>CL_2T</sub> = (V <sub>SN1</sub> _<br>V <sub>CC</sub> = V <sub>SN1</sub> _ = 2                         | - V <sub>SN2</sub> _), L+CL2X_ = 1,<br>4V, V <sub>L+</sub> _ > 18V | 25.5  | 30   | 36    | mV    |

| SN1_ Supply Current                        | I <sub>SN1ACT</sub>   | V <sub>L+</sub> > 18V, L+En_                                                                                 | _ = 1, L+CL2X_ = 1                                                 |       | 0.23 | 0.325 | mA    |

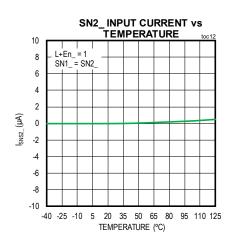

| SN2_ Input Current                         | I <sub>SN2</sub>      | V <sub>SN2</sub> = V <sub>SN1</sub>                                                                          |                                                                    | -10   |      | +10   | μA    |

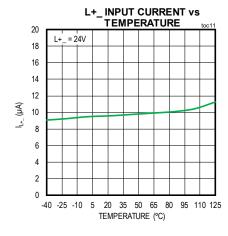

| L+_ Input Current                          | IL+                   | V <sub>L+</sub> _ = 30V                                                                                      |                                                                    |       |      | 20    | μA    |

| L+_ Extended Range Input<br>Current        | I <sub>L+_EXT</sub>   | V <sub>CC</sub> = V <sub>SN1</sub> = 2<br>< 60V                                                              | 4V, (V <sub>CC</sub> - 60V) < V <sub>L+</sub> _                    | -50   |      | +50   | μA    |

|                                            |                       | I . vision                                                                                                   | MAX14819                                                           | 16    |      | 18    | V     |

| L. Dawer Cond Throubald                    | V <sub>TL+_R</sub>    | L+_ rising                                                                                                   | MAX14819A                                                          | 18    |      | 20    | ] V   |

| L+_ Power Good Threshold                   | V                     | L+ falling                                                                                                   | MAX14819                                                           | 15.5  |      | 17.5  | V     |

|                                            | V <sub>TL+_F</sub>    | L+_ lalling                                                                                                  | MAX14819A                                                          | 17.5  |      | 19.5  | v     |

| L+_ Power Good Hysteresis                  | V <sub>TL+H</sub>     |                                                                                                              |                                                                    |       | 0.4  |       | V     |

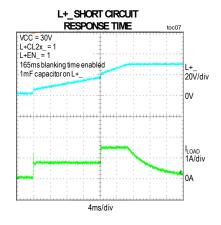

| L+_ Dynamic Blanking<br>Threshold          | V <sub>LPDTHR</sub>   |                                                                                                              |                                                                    |       | 8.8  |       | V     |

| THERMAL MANAGEMENT                         |                       |                                                                                                              |                                                                    |       |      |       |       |

| Thermal-Warning Threshold                  | T <sub>WRN</sub>      | Die junction temp<br>TempW and Temp                                                                          | •                                                                  |       | +135 |       | °C    |

| Thermal-Warning Threshold Hysteresis       | T <sub>WRN_HYS</sub>  | Die junction temperature falling,<br>TempW bit cleared                                                       |                                                                    |       | 15   |       | °C    |

| CQ_ Thermal-Shutdown<br>Temperature        | T <sub>SHUT</sub>     | Driver temperature rising, temperature at which the driver is turned off. ThShut and ThuShutInt bits are set |                                                                    |       | +160 |       | °C    |

| Thermal-Shutdown<br>Temperature Hysteresis | T <sub>SHUT_HYS</sub> | Driver temperatur cleared                                                                                    | e falling. ThShut bit is                                           |       | 15   |       | °C    |

## Dual IO-Link Master Transceiver with Integrated Framers and L+ Supply Controllers

#### **AC Electrical Characteristics**

( $V_{CC}$  = 18V to 30V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 1.62V to 5.5V,  $V_{GND}$  = 0V;  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

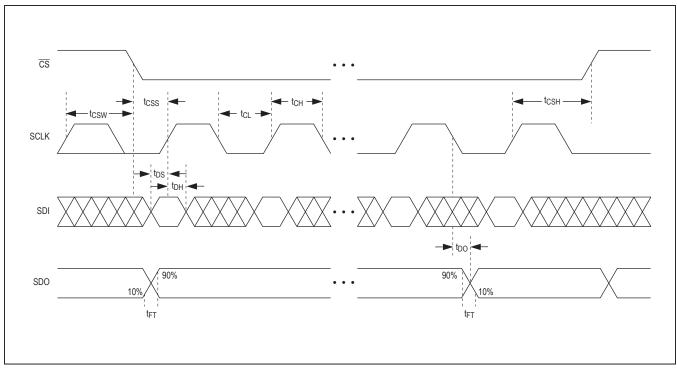

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SYMBOL             |                                           | CONDITIONS                                      |                     | MIN      | TYP  | MAX  | UNITS |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------|-------------------------------------------------|---------------------|----------|------|------|-------|

| CQ_ DRIVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                           |                                                 |                     |          |      |      |       |

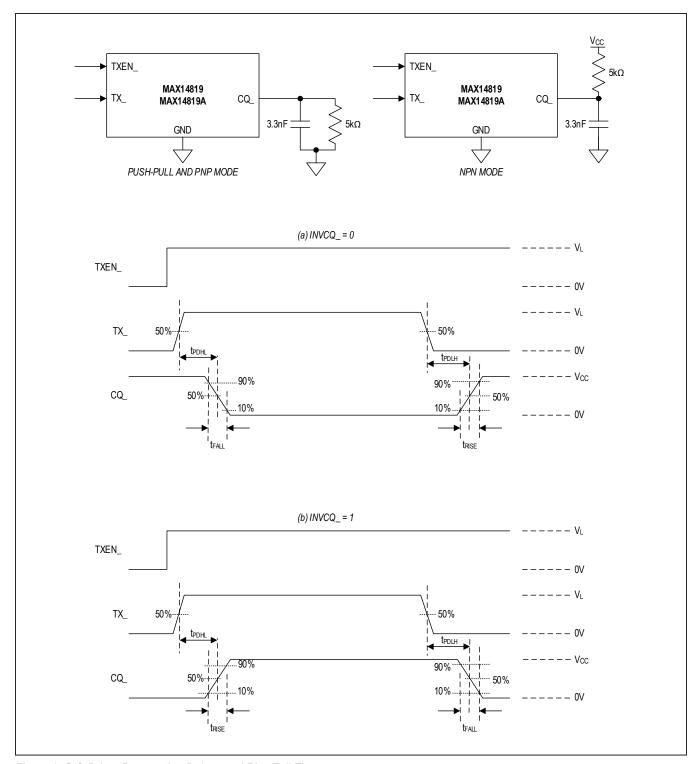

| District Dis |                    | Push-pull and PNP configuration, Figure 1 |                                                 |                     | 0.45     | 0.90 |      |       |

| Driver Low-to-High Propagation<br>Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>PDLH</sub>  |                                           | NPN configuration, Figure 1 no capacitive load) |                     |          | 5    |      | μs    |

| Driver High-to-Low Propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    | Push-pull and l                           | NPN configurati                                 | on, <u>Figure 1</u> |          | 0.43 | 0.90 |       |

| Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>PDHL</sub>  | PNP configuration (no capacitive          |                                                 |                     |          | 5    |      | μs    |

| Driver Skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t <sub>SKEW</sub>  | tpdlh - tpdhl                             | , Figure 1                                      |                     |          |      | 0.2  | μs    |

| Driver Rise Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | t <sub>RISE</sub>  | Push-pull and l                           | PNP configurati                                 | on, <u>Figure 1</u> | 0.25     | 0.42 | 0.75 | μs    |

| Driver Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | t <sub>FALL</sub>  | Push-pull and l                           | NPN configurati                                 | on, <u>Figure 1</u> | 0.25     | 0.42 | 0.75 | μs    |

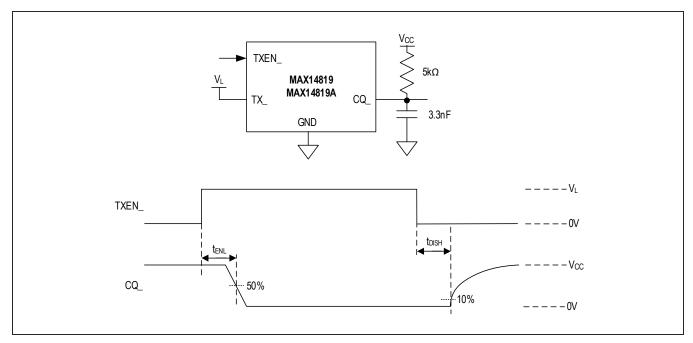

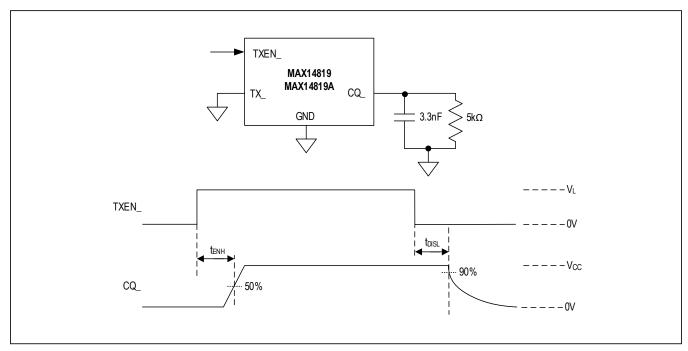

| Driver Enable Time High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>ENH</sub>   | Push-pull and                             | PNP configurati                                 | on, <u>Figure 2</u> |          | 0.45 | 0.9  | μs    |

| Driver Enable Time Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>ENL</sub>   | Push-pull and l                           | NPN configurati                                 | on, <u>Figure 3</u> |          | 0.26 | 0.9  | μs    |

| Driver Disable Time High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>DISH</sub>  | Push-pull and l                           | PNP configurati                                 | on, <u>Figure 2</u> |          | 1.9  | 3    | μs    |

| Driver Disable Time Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>DISL</sub>  | Push-pull and l                           | NPN configurati                                 | on, <u>Figure 3</u> |          | 1.7  | 3    | μs    |

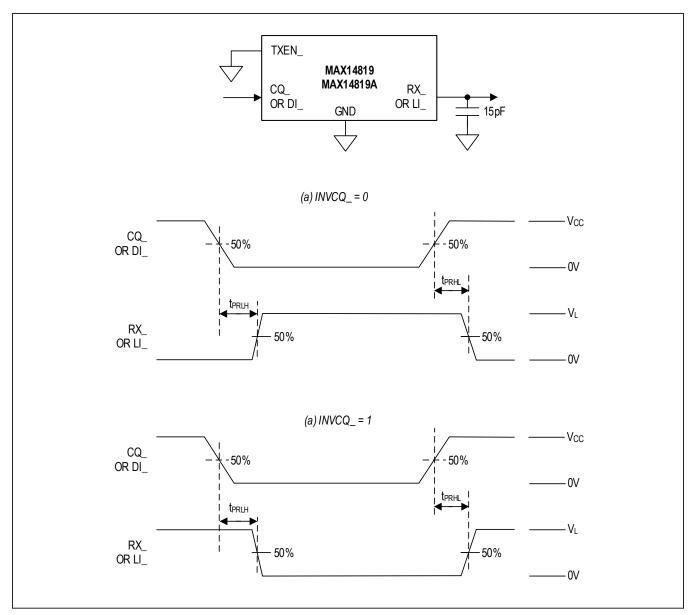

| CQ_ RECEIVER (Figure 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                                           |                                                 |                     |          |      |      |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | CQFilterEn =                              | 0                                               | MAX14819            |          | 0.28 | 0.5  |       |

| CQ_ Receiver Low-to-High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>CPRLH</sub> | MAX1481                                   | MAX14819A                                       |                     | 0.53     | 8.0  | μs   |       |

| Propagation Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CPRLH              | CQFilterEn =                              | 1                                               | MAX14819            |          | 1.2  | 2    | μο    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | OQT INCOLEN_                              |                                                 | MAX14819A           |          | 1.5  | 2.3  |       |

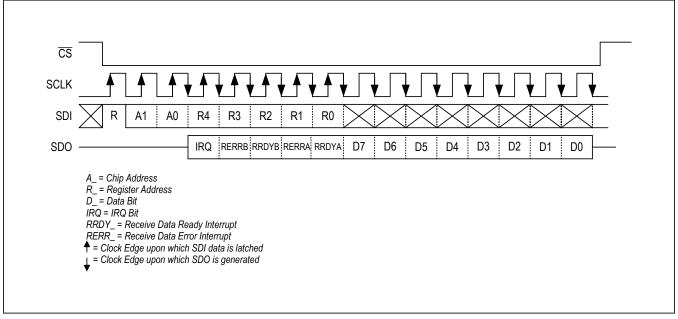

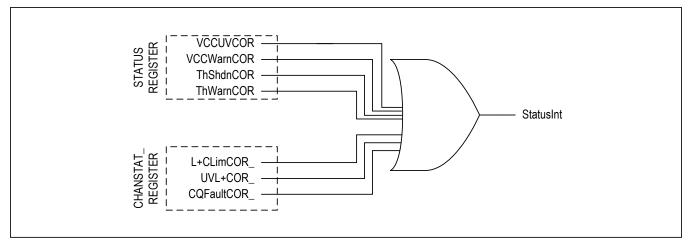

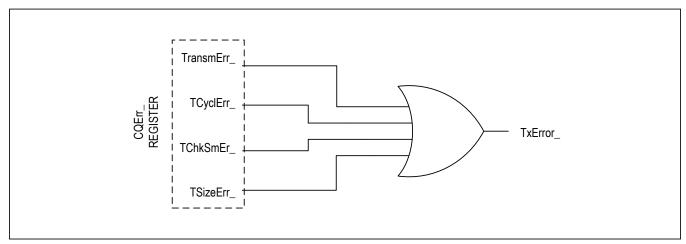

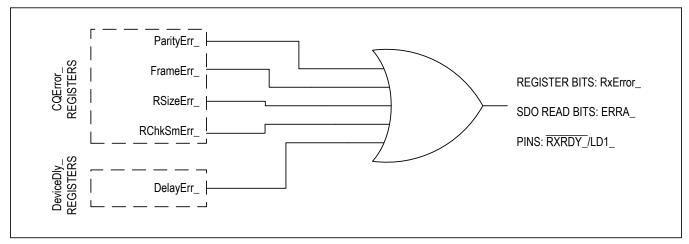

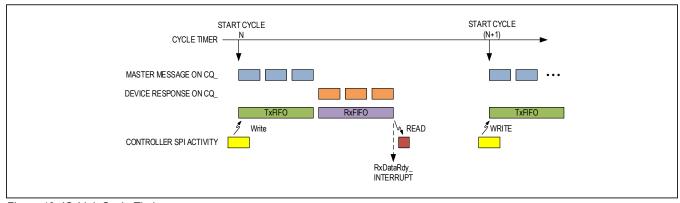

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | CQFilterEn =                              | 0                                               | MAX14819            |          | 0.25 | 0.5  |       |