EVALUATION KIT AVAILABLE

## Low-Capacitance VGA 2:2 Dual-Graphics Crossover Switch

### **General Description**

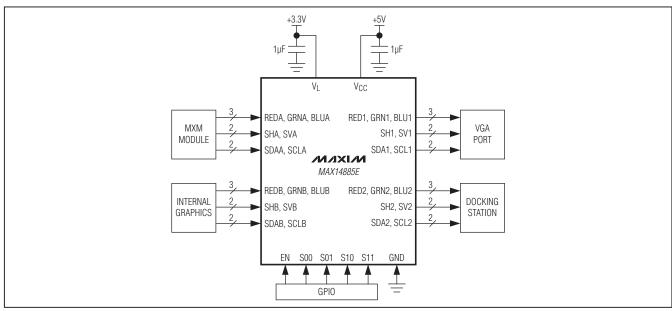

The MAX14885E integrates high-bandwidth analog switches, level-translating buffers, and level-translating FET switches. The device implements a complete 2:2 dual-graphics crossover solution for VGA signal switching. The MAX14885E provides 12 very high-frequency 700MHz (typ) SPST switches for RGB signals, four low-frequency clamping switches for display data channel (DDC) signals, two pairs of level-translating buffers for the HSYNC and VSYNC signals, and integrated extended ESD protection. The MAX14885E is used to select one of two sources to either of two destinations (see the *Typical Operating Circuit*) within a laptop computer.

Horizontal and vertical synchronization (SH\_/SV\_) inputs feature level-shifting buffers to support low-voltage controllers and standard 5V TTL-level monitors. DDC, consisting of SDA\_ and SCL\_, are FET switches that protect the low-voltage VGA source from potential damage from high-voltage presence on the monitor while reducing capacitive load.

All 14 output terminals of the MAX14885E feature high-ESD protection to  $\pm$ 15kV Human Body Model (HBM) and  $\pm$ 6kV IEC 61000-4-2 Contact Discharge (see the *Pin Description*). All other pins are protected to  $\pm$ 2kV HBM.

The MAX14885E is specified over the extended -40°C to +85°C temperature range, and is available in a 40-pin TQFN (5mm x 5mm) package.

### **Features**

- Low Quiescent Current ≤ 5µA (max)

- + Low 5Ω (typ) On-Resistance (RGB Signals)

- + High Bandwidth, 700MHz (typ), RGB

- DDC Level Shifting, Isolation with Internal Pullup Termination, and Protection

- Horizontal and Vertical Sync Level Shifting and Buffering

- Inputs Compatible with V<sub>L</sub>, Outputs TTL Compatible

- Source/Sink ±10mA on Each SH\_, SV\_ Output

- Independent Selectable Logic Inputs for Switching

- High ESD Protection on Outputs ±15kV ESD HBM ±6kV IEC 61000-4-2 Contact Discharge

- Small, 40-Pin TQFN (5mm x 5mm) Package

#### Applications

Notebook Computer—Switchable Graphics

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX14885EETL+ | -40°C to +85°C | 40 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

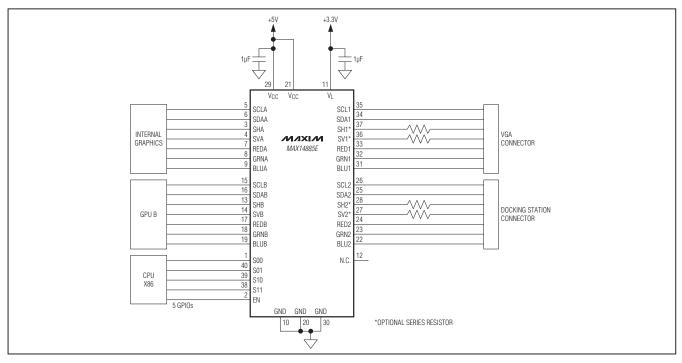

## **Typical Application Circuit**

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

(Voltages referenced to GND.)

| (                                                        |

|----------------------------------------------------------|

| VCC0.3V to +6V                                           |

| VL0.3V to +6V                                            |

| RED_, GRN_, BLU_, SCL1, SCL2, SDA1,                      |

| SDA2, SH1, SH2, SV1, SV20.3V to (V <sub>CC</sub> + 0.3V) |

| SCLA, SCLB, SDAA, SDAB, SHA, SHB,                        |

| SVA, SVB, S00, S01, S10, S11, EN0.3V to (VL + 0.3V)      |

| Continuous Current Through RED_,                         |

| GRN_, BLU_ Switches                                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

TQFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +4.5V to +5.5V, V<sub>L</sub> = +2.3V to V<sub>CC</sub>, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5.0V, V<sub>L</sub> = +3.3V and T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                                   | PARAMETER SYMBOL CONDITIONS |                                                                                  | MIN                                 | ТҮР | MAX | UNITS |    |

|-------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------|-------------------------------------|-----|-----|-------|----|

| Supply Voltage                                              | Vcc                         |                                                                                  |                                     | 4.5 |     | 5.5   | V  |

| Logic Supply Voltage                                        | VL                          | $V_L \leq V_{CC}$                                                                |                                     | 2.3 | 3.3 | 5.5   | V  |

| V <sub>CC</sub> Supply Current                              | Icc                         | VCC = +5.5V, VL = +3.6V, VEN = 0V,<br>VSHA, VSHB, VSVA, VSVB = 0V or VL          |                                     |     | 0.2 | 5     | μA |

|                                                             | ١L                          | V <sub>CC</sub> = +5.5V, V <sub>L</sub> =<br>+3.6V, SCL_ and<br>SDA_ unconnected | Ven, Vsha, Vshb,<br>Vsva, Vsvb = 0V |     | 0.2 | 5     | μA |

| VL Supply Current                                           |                             |                                                                                  | Ven, Vsha, Vshb,<br>Vsva, Vsvb = Vl |     | 0.3 | 0.5   | mA |

| On-Resistance (RED_, GRN_,<br>BLU_)                         | RHFON                       | $V_{IN} = +0.7V, I_{IN} = +10mA$                                                 |                                     |     | 5   | 8     | Ω  |

| On-Resistance Match (RED_,<br>GRN_, BLU_)                   | ΔRon                        | $0V \leq V_{IN} \leq +0.7V, \ I_{IN} = -10mA$                                    |                                     |     |     | 1     | Ω  |

| On-Resistance Flatness (RED_,<br>GRN_, BLU_)                | RFLAT(ON)                   | $0V \le V_{IN} \le +0.7V$ , $I_{IN} = -10mA$                                     |                                     |     | 0.5 | 1     | Ω  |

| Leakage Current (RED_, GRN_,<br>BLU_)                       | ILK                         | V <sub>EN</sub> = 0V                                                             |                                     | -1  |     | +1    | μA |

| On-Resistance (SDA_, SCL_)                                  | RDDCON                      | $V_{IN} = +0.7V, I_{IN} = \pm 10mA$                                              |                                     |     | 25  |       | Ω  |

| V <sub>CC</sub> Pullup Resistor (SDA1,<br>SDA2, SCL1, SCL2) |                             | Resistor to V <sub>CC</sub>                                                      |                                     |     | 20  |       | kΩ |

| VL Pullup Resistor (SDAA, SDAB,<br>SCLA, SCLB)              |                             | Resistor to $V_L$                                                                |                                     |     | 3   |       | kΩ |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +4.5V \text{ to } +5.5V, V_L = +2.3V \text{ to } V_{CC}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +5.0V, V_L = +3.3V \text{ and } T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                          | SYMBOL      | CONDITIONS                                                                                                                               | MIN          | TYP | MAX          | UNITS |

|----------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--------------|-------|

| DIGITAL INPUTS (EN, S00, S01,                      | S10, S11, S | HA, SHB, SVA, SVB)                                                                                                                       |              |     |              |       |

| Input Threshold Low                                | VIL         | $+2.3V \le V_L \le V_{CC}$                                                                                                               | 0.25 x<br>VL |     |              | V     |

| here it Threehold Link                             |             | $+3.3V \le V_L \le V_{CC}$                                                                                                               |              |     | 0.55 x<br>VL | V     |

| Input Threshold High                               | Vih         | $+2.3V \le V_L \le +3.3V$                                                                                                                |              |     | 0.6 x<br>VL  | V     |

| Input Hysteresis                                   | VHYST       | $+2.3V \le V_L \le V_{CC}$                                                                                                               |              | 100 |              | mV    |

| VL Pulldown Resistor                               |             | Resistor to V <sub>L</sub> (EN, S00, S01, S10, S11, SHA, SHB, SVA, SVB)                                                                  |              | 100 |              | kΩ    |

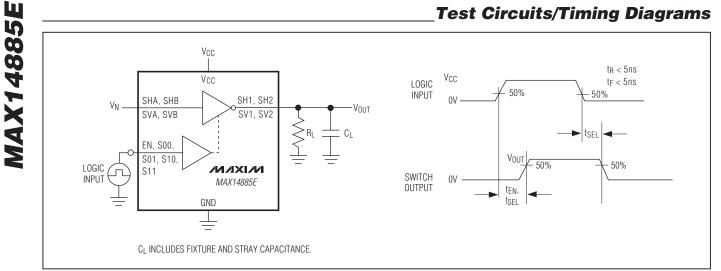

| Enable Time                                        | ten         | $R_L = 2.2k\Omega$ , $C_L = 10pF$ , Figure 1 (EN)                                                                                        |              | 1   |              | μs    |

| Select Time                                        | tSEL        | $R_L = 2.2k\Omega$ , $C_L = 10pF$ , Figure 1 (S00, S01, S10, S11)                                                                        |              | 1   |              | μs    |

| DIGITAL OUTPUTS (SH1, SV1, S                       | SH2, SV2)   |                                                                                                                                          |              |     |              |       |

| Output-Voltage Low                                 | Vol         | IOUT = +10mA, VCC = +4.5V                                                                                                                |              |     | 0.6          | V     |

| Output-Voltage High                                | Voh         | $I_{OUT} = -10 mA, V_{CC} = +4.5 V$                                                                                                      | 3            |     |              | V     |

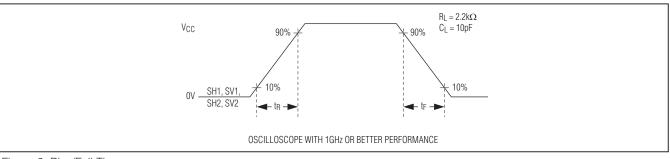

| Rise/Fall Time                                     | tR/F        | $R_L = 2.2k\Omega$ , $C_L = 10pF$ , Figure 2 (Note 3)                                                                                    |              | 2   | 4            | ns    |

| RGB AC PERFORMANCE                                 |             |                                                                                                                                          |              |     |              |       |

| Bandwidth                                          | fBW         | $R_{S} = R_{L} = 50\Omega$                                                                                                               |              | 700 |              | MHz   |

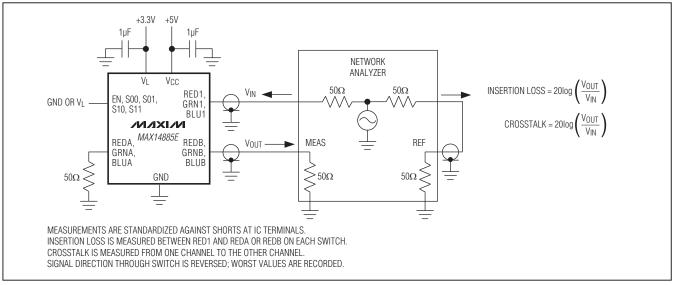

| On-Loss                                            |             | $ \begin{array}{l} f = 10 MHz, \ R_S = R_L = 50 \Omega, \\ 0 V \leq V_{BIAS} \leq +0.7 V, \ Figure \ 3 \end{array} $                     |              | 0.7 |              | dB    |

| Crosstalk (RED_, GRN_, BLU_)                       |             | $R_S = R_L = 50\Omega$ , f = 50MHz, Figure 3                                                                                             |              | -40 |              | dB    |

| Off-Capacitance                                    | COFF        | V <sub>EN</sub> = 0V, RED_, GRN_, BLU_ to GND,<br>f = 1MHz, REDA/REDB to RED1/RED2,<br>GRNA/GRNB to GRN1/GRN2, BLUA/BLUB<br>to BLU1/BLU2 |              | 3.5 |              | pF    |

| On-Capacitance                                     | CON         | f = 1MHz, REDA/REDB to RED1/RED2,<br>GRNA/GRNB to GRN1/GRN2, BLUA/BLUB<br>to BLU1/BLU2 (Note 3)                                          |              | 10  | 12           | pF    |

| ESD PROTECTION                                     | ·           | ·                                                                                                                                        | ·            |     |              |       |

| RED1, GRN1, BLU1, RED2,<br>GRN2, BLU2, SDA1, SCL1, |             | HBM (Note 4)                                                                                                                             |              | ±15 |              | kV    |

| SDA2, SCL2, SH1, SV1, SH2,<br>SV2                  |             | IEC 61000-4-2 Contact Discharge (Note 4)                                                                                                 |              | ±6  |              | 11.1  |

| All Other Terminals                                |             | НВМ                                                                                                                                      |              | ±2  |              | kV    |

Note 2: The device is 100% production tested at  $T_A = +25^{\circ}$ C. Limits over the operating temperature range are guaranteed by design and not production tested.

Note 3: Guaranteed by design. Not production tested.

Note 4: Tested terminal to GND,  $1\mu F$  bypass capacitors on VCC and VL.

Figure 1. Enable/Select Time

Figure 2. Rise/Fall Time

Figure 3. Insertion Loss and Crosstalk

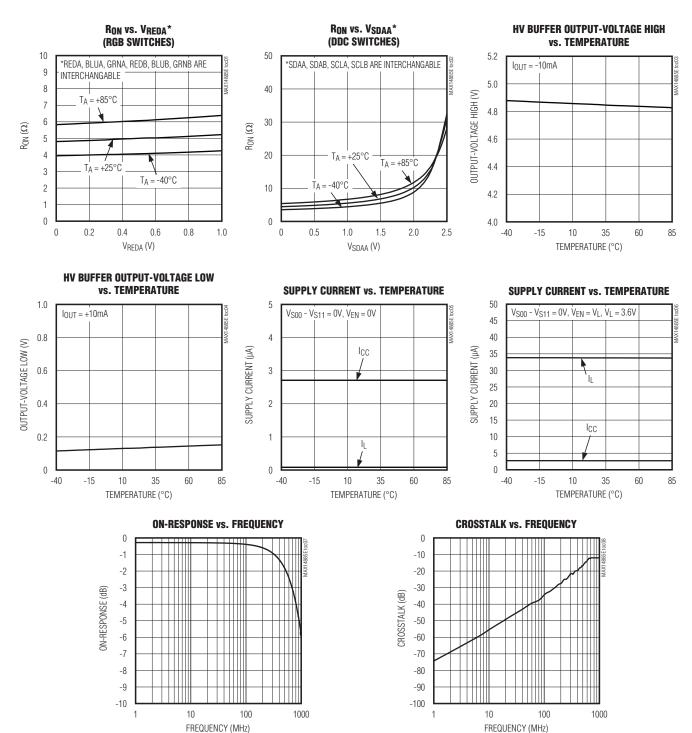

$(V_{CC} = +5.0V, V_L = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Typical Operating Characteristics**

MAX14885E

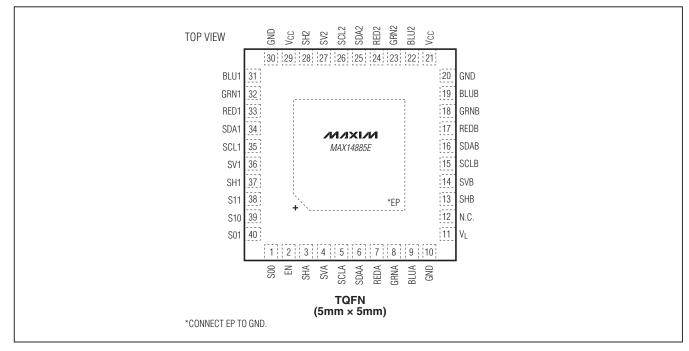

Pin Configuration

## Pin Description

| PIN        | NAME | FUNCTION                                                                                                                                                                     |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | S00  | Select Input. S00 selects SDA_ and SCL_ signal path (see Table 1).                                                                                                           |

| 2          | EN   | Enable Input. Drive EN high for normal operation. Drive EN low to disable the device (all switch outputs in three-state and SH1, SH2, SV1, and SV2 are low).                 |

| 3          | SHA  | Horizontal Sync Input 1                                                                                                                                                      |

| 4          | SVA  | Vertical Sync Input 1                                                                                                                                                        |

| 5          | SCLA | DDC Clock Input 1                                                                                                                                                            |

| 6          | SDAA | DDC Data Input 1                                                                                                                                                             |

| 7          | REDA | RGB Red Input 1                                                                                                                                                              |

| 8          | GRNA | RGB Green Input 1                                                                                                                                                            |

| 9          | BLUA | RGB Blue Input 1                                                                                                                                                             |

| 10, 20, 30 | GND  | Ground                                                                                                                                                                       |

| 11         | VL   | Supply Voltage. +2.3V $\leq$ V <sub>L</sub> $\leq$ V <sub>CC</sub> . Bypass V <sub>L</sub> to GND with a 1µF or larger ceramic capacitor as close to the device as possible. |

| 12         | N.C. | No Connection. Connect N.C. to GND or leave unconnected.                                                                                                                     |

| 13         | SHB  | Horizontal Sync Input 2                                                                                                                                                      |

| 14         | SVB  | Vertical Sync Input 2                                                                                                                                                        |

| 15         | SCLB | DDC Clock Input 2                                                                                                                                                            |

| 16         | SDAB | DDC Data Input 2                                                                                                                                                             |

## Pin Description (continued)

| PIN    | NAME | FUNCTION                                                                                                                                                      |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17     | REDB | RGB Red Input 2                                                                                                                                               |

| 18     | GRNB | RGB Green Input 2                                                                                                                                             |

| 19     | BLUB | RGB Blue Input 2                                                                                                                                              |

| 21, 29 | VCC  | Supply Voltage. V <sub>CC</sub> = $+5.0V \pm 10\%$ . Bypass V <sub>CC</sub> to GND with a 1µF or larger ceramic capacitor as close to the device as possible. |

| 22     | BLU2 | RGB Blue Output 2*                                                                                                                                            |

| 23     | GRN2 | RGB Green Output 2*                                                                                                                                           |

| 24     | RED2 | RGB Red Output 2*                                                                                                                                             |

| 25     | SDA2 | DDC Data Output 2*                                                                                                                                            |

| 26     | SCL2 | DDC Clock Output 2*                                                                                                                                           |

| 27     | SV2  | Vertical Sync Output 2*                                                                                                                                       |

| 28     | SH2  | Horizontal Sync Output 2*                                                                                                                                     |

| 31     | BLU1 | RGB Blue Output 1*                                                                                                                                            |

| 32     | GRN1 | RGB Green Output 1*                                                                                                                                           |

| 33     | RED1 | RGB Red Output 1*                                                                                                                                             |

| 34     | SDA1 | DDC Data Output 1*                                                                                                                                            |

| 35     | SCL1 | DDC Clock Output 1*                                                                                                                                           |

| 36     | SV1  | Vertical Sync Output 1*                                                                                                                                       |

| 37     | SH1  | Horizontal Sync Output 1*                                                                                                                                     |

| 38     | S11  | Select Input. S11 selects RED_, GRN_, BLU_, SH_ and SV_ signal path (see Table 2).                                                                            |

| 39     | S10  | Select Input. S10 selects RED_, GRN_, BLU_, SH_ and SV_ signal path (see Table 2).                                                                            |

| 40     | S01  | Select Input. S01 selects SDA_ and SCL_ signal path (see Table 1).                                                                                            |

|        | EP   | Exposed Pad. Connect EP to GND. Do not use EP as a sole ground connection.                                                                                    |

\*Terminal with ±15kV Human Body Model (HBM) and ±6kV IEC 61000-4-2 Contact Discharge protection.

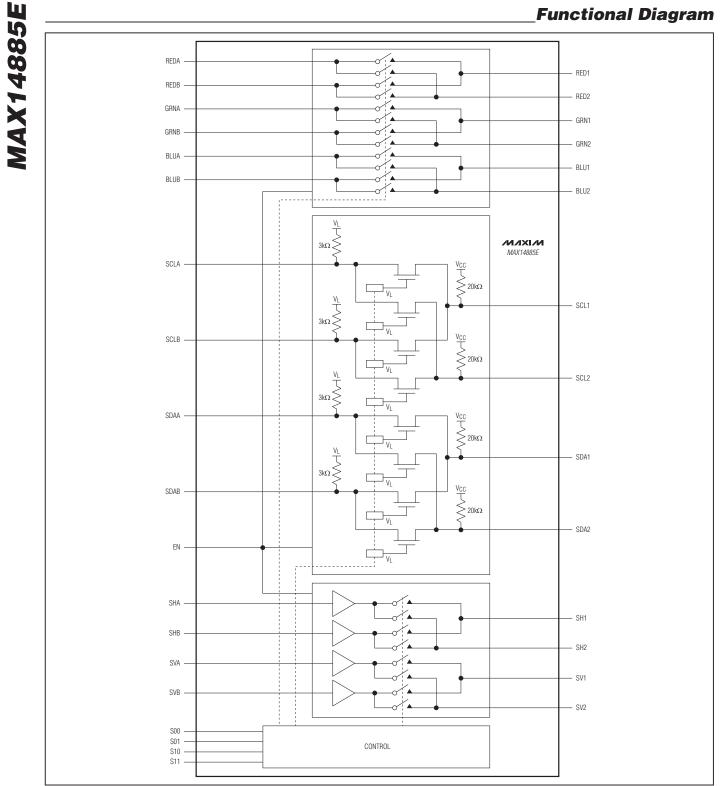

**Functional Diagram**

## **Typical Operating Circuit**

## **Detailed Description**

The MAX14885E integrates high-bandwidth analog switches and level-translating buffers to implement a complete 2:2 dual-graphics crossover function for VGA signals. The device provides switching for RGB, HSYNC, VSYNC, SDA, and SCL signals—all signals required in notebook VGA switching applications. The MAX14885E permits the system to select between internal standard graphics and add-in graphics (MXM or other) to be routed to either the VGA port on the laptop or to the connector on the docking station.

The HSYNC and VSYNC inputs feature level-shifting buffers to support 5V TTL output logic levels from low-voltage graphics controllers. These buffered switches can be driven from +2.3V up to VL. RGB signals are routed with high-performance analog switches. SDA\_ and SCL\_ are DDC signals with pullups to their respective voltages. The MAX14885E translates the low-voltage SH\_, SV\_ signals to 5V TTL-level compatible signals, protecting the low voltage GPU from potentially harmful levels present in a monitor.

Drive EN logic-low to shut down the MAX14885E. In shutdown mode, all switches are high impedance, providing high signal rejection. Four select inputs are provided to individually select groups of switches. The RGB, HSYNC, and VSYNC signals are controlled by S11 and S10. The SDA and SCL signals are controlled by S01 and S00.

#### **RGB Switches**

**MAX14885E**

The MAX14885E provides 12 SPST high-bandwidth switches to route standard VGA red, green, and blue signals (Table 2). The RED\_, GRN\_, and BLU\_ analog switches are identical, and any of the three switches can be used to route red, green, or blue video signals. The RED1, RED2, GRN1, GRN2, BLU1, and BLU2 outputs are ESD protected to  $\pm$ 15kV HBM and  $\pm$ 6kV IEC 61000-4-2 Contact Discharge.

#### Horizontal/Vertical Sync Level Shifter

The SHA, SHB, SVA, and SVB inputs are buffered to provide level-shifting and drive capability for horizontal/ vertical sync signals that meet the VESA specification. The SH\_ and SV\_ level shifters are identical, and each level shifter can be used for either horizontal or vertical signals. The SH1, SH2, SV1, and SV2 outputs are ESD protected to  $\pm 15$ kV HBM and  $\pm 6$ kV IEC 61000-4-2 Contact Discharge. Because of the high-speed nature of S and V buffers, users may add small series resistors (e.g.,  $25\Omega$ ). See the *Typical Operating Circuit*.

**Display Data Channel Switches (DDC)**

The MAX14885E provides four logic-level translating switches to route DDC signals (Table 1). VL is normally set to +3.3V to provide logic shifting for VESA DDC (I<sup>2</sup>C)-compatible signals. The MAX14885E protects the low-voltage graphics controller from +5V that presents itself in VESA-compatible monitors. The SDA\_ and SCL\_ switches are identical, and each switch can be used to route either SDA or SCL signals. The SDA1, SDA2, SCL1, and SCL2 outputs are ESD protected to ±15kV HBM and ±6kV IEC 61000-4-2 Contact Discharge. These outputs are pulled up to VCC internally by  $20k\Omega$  resistors. Users

### Table 1. DDC Truth Table

| EN | S01 | S00 | FUNCTION                     |  |  |

|----|-----|-----|------------------------------|--|--|

| 0  | X   | Х   | All switches high impedance  |  |  |

| 1  | 0   | 0   | SDAA to SDA1<br>SCLA to SCL1 |  |  |

| 1  | 0   | 1   | SDAB to SDA1<br>SCLB to SCL1 |  |  |

| 1  | 1   | 0   | SDAA to SDA2<br>SCLA to SCL2 |  |  |

| 1  | 1   | 1   | SDAB to SDA2<br>SCLB to SCL2 |  |  |

X = Don't care.

### Table 2. RGB/HSYNC, VSYNC Truth Table

| EN | S11 | S10 | FUNCTION                                                                                                          |                          |  |

|----|-----|-----|-------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| 0  | Х   | Х   | All switches high impedance and<br>V <sub>SH1</sub> , V <sub>SH2</sub> , V <sub>SV1</sub> , V <sub>SV2</sub> = 0V |                          |  |

| 1  | 0   | 0   | REDA to RED1<br>GRNA to GRN1<br>BLUA to BLU1                                                                      | SHA to SH1<br>SVA to SV1 |  |

| 1  | 0   | 1   | REDB to RED1<br>GRNB to GRN1<br>BLUB to BLU1                                                                      | SHB to SH1<br>SVB to SV1 |  |

| 1  | 1   | 0   | REDA to RED2<br>GRNA to GRN2<br>BLUA to BLU2                                                                      | SHA to SH2<br>SVA to SV2 |  |

| 1  | 1   | 1   | REDB to RED2<br>GRNB to GRN2<br>BLUB to BLU2                                                                      | SHB to SH2<br>SVB to SV2 |  |

X = Don't care.

can elect to parallel these resistors to achieve higher drive, if necessary.

#### **ESD** Protection

As with all Maxim devices, ESD protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. Additionally, the RED1, RED2, GRN1, GRN2, BLU1, BLU2, SH1, SH2, SV1, SV2, SDA1, SDA2, SCL1, and SCL2 terminals of the MAX14885E are designed for protection to the following limits:

- ±15kV using the HBM

- ±6kV using the Contact Discharge Method specified in IEC 61000-4-2

For optimum ESD performance, bypass VCC and VL pins to ground with 1µF or larger ceramic capacitors as close as possible to these supply pins.

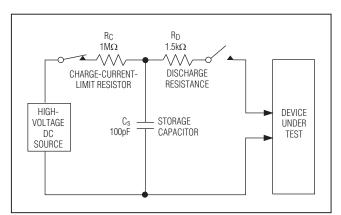

Figure 4. Human Body ESD Test Model

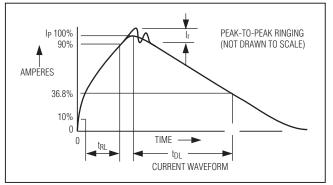

Figure 5. Human Body Current Waveform

MAX14885E

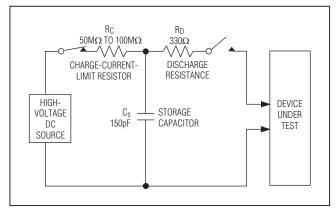

Figure 6. IEC 61000-4-2 ESD Test Model

#### Human Body Model (HBM)

Figure 4 shows the HBM, and Figure 5 shows the current waveform it generates when discharged into a low-impedance state. This model consists of a 100pF capacitor charged to the ESD voltage of interest that is then discharged into the device through a  $1.5k\Omega$  resistor.

#### IEC 61000-4-2

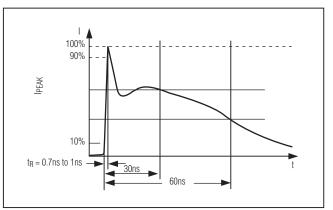

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. The MAX14885E helps users design equipment that meets Level 4 of IEC 61000-4-2. The main difference between tests done using the HBM and IEC 61000-4-2 is higher peak current in IEC 61000-4-2. Because series resistance is lower in the IEC 61000-4-2 ESD test model (Figure 6), the ESD-withstand voltage measured to this standard is generally lower than that measured using the HBM. Figure 7 shows the current waveform for the  $\pm$ 6kV IEC 61000-4-2 Level 4 ESD Contact Discharge test. The Air-Gap Discharge test involves approaching the device with a charged probe. The Contact Discharge Method connects the probe to the device before the probe is energized.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report test setup, methodology, and results.

#### Applications Information

The MAX14885E provides the switching and level-shifting necessary to drive a standard VGA port from either an internal graphics controller or an add-in module (MXM or GPU). The RGB signals are switched through the 12 low-capacitance SPST switches, and internal buffers drive the HSYNC and VSYNC signals to VGA standard

Figure 7. IEC 61000-4-2 ESD Generator Current Waveform

5V TTL levels. The DDC switches provide level shifting. Connect V<sub>L</sub> to +3.3V for normal operation. See the *Typical Application Circuit*.

#### **Power-Supply Decoupling and Sequencing** Bypass each V<sub>CC</sub> and V<sub>L</sub> terminals to ground with a 1 $\mu$ F or larger ceramic capacitor as close as possible to the device. Refer to Application Note 5314: *Power Sequencing the MAX14885E VGA Crossover Switch* for guidance on power sequencing of the V<sub>L</sub> and V<sub>CC</sub> power rails.

#### **PCB** Layout

High-speed switches such as the MAX14885E require proper PCB layout for optimum performance. Ensure that impedance-controlled PCB traces for high-speed signals are matched in length and as short as possible. Connect the exposed pad to ground.

### **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE |         |                | LAND<br>PATTERN NO. |  |

|-----------------|---------|----------------|---------------------|--|

| 40 TQFN-EP      | T4055+1 | <u>21-0140</u> | <u>90-0016</u>      |  |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                      | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------------------------------------------------------|------------------|

| 0                  | 1/10             | Initial release                                                                                  | _                |

| 1                  | 1/12             | Updated <i>Power-Supply Decoupling and Sequencing</i> section to reference Application Note 5314 | 11               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_ Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2012 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.