Click here to ask an associate for production status of specific part numbers.

#### **MAX16136**

## High-Precision Supervisory ICs with Window Watchdog and Overvoltage Indicator

#### **General Description**

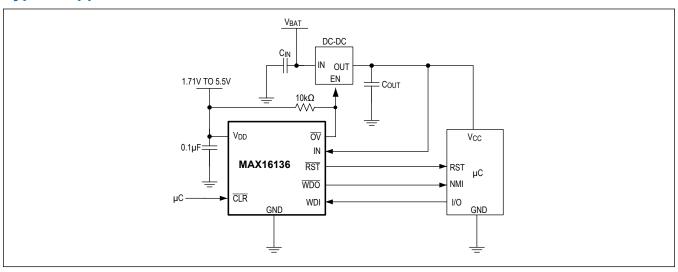

The MAX16136, a low voltage, ±1% accurate window-detector supervisor circuit monitors a single system supply voltage and the integrity of code execution by a microprocessor or microcontroller. This device features an active-low, open-drain output that asserts whenever the monitored supply rail falls outside of the factory-trimmed undervoltage/overvoltage window threshold. The reset output remain asserted for the programmed reset timeout period after the monitored supply voltage falls within the undervoltage/overvoltage window threshold.

The MAX16136 offers factory-trimmed voltage thresholds from 0.5V to 5V in approximately 20mV increment. A variety of factory trimmed undervoltage/overvoltage thresholds from ±4% to ±11% are available to accommodate different supply voltages and tolerances.

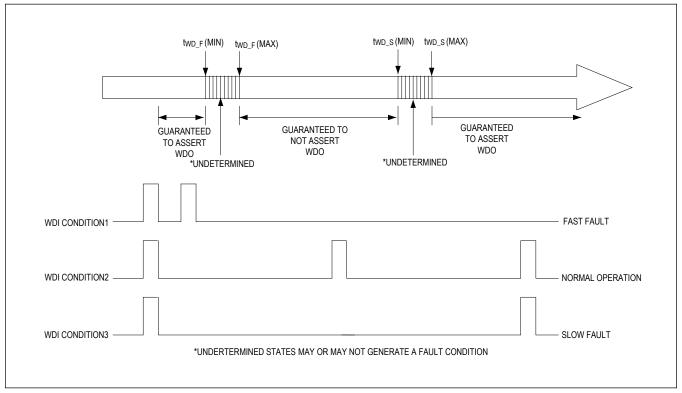

A window-watchdog timer circuit monitors microprocessor or microcontroller activity. During normal operation, the microprocessor or microcontroller must repeatedly toggle the watchdog input (WDI) low within the fast watchdog timeout ( $t_{WD\_F}$ ) and slow watchdog timeout ( $t_{WD\_S}$ ). If the microcontroller or microprocessor does not toggle WDI within the window-timeout period, the supervisor asserts the watchdog output (WDO) to signal that the system is not executing code as expected. The watchdog output pulse can be used to reset the microprocessor or microcontroller, or it may be used to interrupt the system to warn of execution errors.

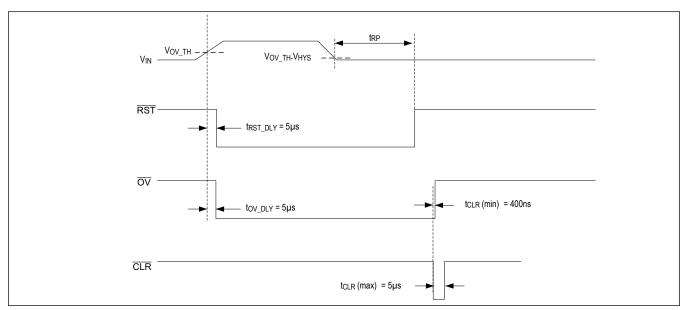

In addition, the MAX16136 features an overvoltage fault output  $(\overline{OV})$  that latches low when the monitored rail exceeds the overvoltage threshold. The latched output can be cleared by pulling  $\overline{CLR}$  low.

The MAX16136 is available in a small, 2mm x 2mm, 8-pin TDFN side-wettable package with exposed pad and operates over the automotive temperature range of -40°C to +125°C.

## **Applications**

- Advanced Driver-Assistance Systems (ADAS)

- Automotive

- Multivoltage ASICs

- Servers

- Storage Equipment

#### **Benefits and Features**

- ±1% Accuracy

- Enables ASIL Compliance at System Level

- · FMEDA Results Available upon Request

- 0.5V to 5V Threshold Range with 20mV Increments

- ±4% to ±11% Undervoltage/Overvoltage Thresholds

- Latched Overvoltage Fault Output

- Clear Fault Input

- 5µs Overvoltage Fault Delay

- Window Watchdog Timeout

- Factory-Set Reset Timeout

- Open-Drain Reset Output

- 8-Pin TDFN Side-Wettable Package

- -40°C to +125°C Operating Temperature Range

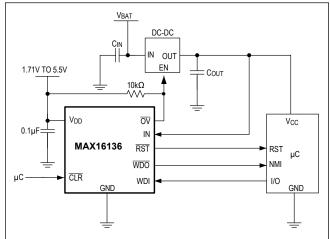

## **Typical Application Circuit**

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to +6V                       | Operating Temperature Range       | 40°C to +125°C |

|---------------------------------------------------------|-----------------------------------|----------------|

| IN, WDO, RST, CLR, OV, WDI to GND0.3V to +6V            | Junction Temperature              | +150°C         |

| Input/Output Continuous Current, WDO, RST, CLR, OV, WDI | Soldering Temperature (Reflow)    | +260°C         |

| ±20mA                                                   | Storage Temperature Range         | 65°C to +150°C |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)   | Lead Temperature (Soldering, 10s) | +300°C         |

| TDFN (derate 11.7mW/°C above 70°C)                      |                                   |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 8 TDFN

| Package Code                           | T822Y+3C         |  |  |  |

|----------------------------------------|------------------|--|--|--|

| Outline Number                         | <u>21-100185</u> |  |  |  |

| Land Pattern Number                    | <u>90-100070</u> |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 85.3°C/W         |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 8.9°C/W          |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DD}$  = 1.71V to 5.5V.  $T_A$  =  $T_J$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C under normal conditions, unless otherwise noted.)

| PARAMETER                                              | SYMBOL                        | CONDITIONS                                                                                                          | MIN  | TYP  | MAX  | UNITS                    |

|--------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------------|

| POWER SUPPLY                                           |                               |                                                                                                                     |      |      |      | ,                        |

| Operating Voltage                                      | \/                            | Comparators functional                                                                                              | 1.71 |      | 5.5  | _ v                      |

| Range                                                  | $V_{DD}$                      | Output guaranteed to be at known state 1.1                                                                          |      |      |      |                          |

| Supply Current                                         | I <sub>DD</sub>               | RST, OV , WDO not asserted                                                                                          |      | 15   | 35   | μA                       |

| Undervoltage Lockout<br>Threshold                      | V <sub>UVLO</sub>             | V <sub>DD</sub> rising                                                                                              | 1.3  | 1.50 | 1.68 | V                        |

| Undervoltage Lockout<br>Hysteresis                     | V <sub>UVLO_HYS</sub>         | V <sub>DD</sub> falling                                                                                             |      | 47   |      | mV                       |

| INPUT VOLTAGE (IN)                                     |                               |                                                                                                                     |      |      |      |                          |

| Nominal Input Threshold Voltage Range                  | V <sub>IN_NOM</sub>           |                                                                                                                     | 0.5  |      | 5    | V                        |

| Nominal Input Threshold<br>Voltage Programming<br>Step | V <sub>IN_NOM_</sub> STE<br>P |                                                                                                                     |      | 20   |      | mV                       |

| Undervoltage/<br>Overvoltage<br>Programming Range      | TOL                           | Reset occurs when V <sub>IN_NOM</sub> falls outside of V <sub>IN_NOM</sub> x (1 ± TOL)                              | ±4   |      | ±11  | % of V <sub>IN_NOM</sub> |

| INPUT THRESHOLD ACC                                    | CURACY                        |                                                                                                                     |      |      |      | •                        |

| Undervoltage Threshold Accuracy                        | V <sub>UVTH_A</sub>           | All V <sub>IN_TH</sub> setting, V <sub>IN_NOM</sub> falling, V <sub>UVTH</sub> = V <sub>IN_NOM</sub> x (1 - TOL%)   | -1   |      | +1   | %                        |

| Overvoltage Threshold Accuracy                         | V <sub>OVTH_A</sub>           | All V <sub>IN_TH</sub> setting, V <sub>IN_NOM</sub> rising,<br>V <sub>OVTH</sub> = V <sub>IN_NOM</sub> x (1 + TOL%) | -1 - |      | +1   | %                        |

| Undervoltage/<br>Overvoltage Hysteresis                | V <sub>HYS</sub>              |                                                                                                                     |      | 0.25 |      | %V <sub>TH</sub>         |

| Input Current                                          | I <sub>IN</sub>               |                                                                                                                     |      | 1.3  | 5    | μA                       |

| Overvoltage Fault-to-OV<br>Assert Delay                | t <sub>OV DLY</sub>           | (V <sub>OVTH</sub> - 1%) to (V <sub>OVTH</sub> + 1%)                                                                |      | 5    |      | μs                       |

| OV Fault Glitch<br>Immunity                            |                               | V <sub>OVTH</sub> + 5%                                                                                              |      | 200  |      | ns                       |

| RST Leakage Current                                    |                               | $V_{\overline{RST}} = V_{\overline{OV}} = V_{\overline{WDO}} = 5.5V$                                                |      | 0.01 | 1    | μA                       |

| CLEAR INPUT (CLR)                                      |                               |                                                                                                                     |      |      |      |                          |

| CLR Input Glitch<br>Immunity                           |                               |                                                                                                                     | 50   |      |      | ns                       |

| CLR Minimum Input<br>Pulse Width                       | t <sub>CLR</sub>              | ( <u>Note 1</u> ) ( <u>Note 2</u> )                                                                                 | 0.4  |      |      | μs                       |

| CLR Internal Pullup<br>Resistance                      |                               |                                                                                                                     |      | 50   |      | kΩ                       |

| WATCHDOG                                               |                               |                                                                                                                     |      |      |      |                          |

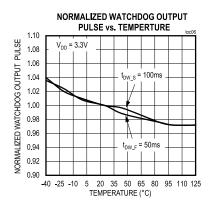

| Fast Watchdog Timeout<br>Accuracy                      | t <sub>WD_F</sub>             | V <sub>DD</sub> = 3.3V ( <u>Note 3</u> )                                                                            | -20  |      | +20  | %                        |

| Slow Watchdog Timeout<br>Accuracy                      | t <sub>WD_S</sub>             | V <sub>DD</sub> = 3.3V ( <u>Note 3</u> )                                                                            | -20  |      | +20  | %                        |

| Minimum Watchdog<br>Input Pulse                        |                               | After WDO asserts                                                                                                   | 24   |      |      | μs                       |

## **Electrical Characteristics (continued)**

$(V_{DD} = 1.71V \text{ to } 5.5V. T_A = T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$  under normal conditions, unless otherwise noted.)

| PARAMETER                               | SYMBOL                                         | CONDITIONS                                                                                                                      |                                                     | MIN                      | TYP | MAX                      | UNITS |

|-----------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|-----|--------------------------|-------|

| WDO Pulse Duration                      | t <sub>WDOF</sub>                              | WDI Input signal per                                                                                                            | WDI Input signal period < t <sub>WD_F</sub>         |                          | 50  |                          | ms    |

| WDO Fuise Duration                      | t <sub>WDOS</sub>                              | WDI Input signal per                                                                                                            | riod > t <sub>WD_S</sub>                            |                          | 100 |                          | 1115  |

| RESET OUTPUT (RST)                      |                                                |                                                                                                                                 |                                                     |                          |     |                          |       |

| Reset Timeout Period<br>Accuracy        | t <sub>RP</sub>                                | From time V <sub>IN</sub> enters overvoltage/<br>undervoltage threshold-window to time<br>RST goes high, V <sub>DD</sub> = 3.3V |                                                     | -20                      |     | +20                      | %     |

| IN-to-RST Propagation Delay             | t <sub>D</sub>                                 | (V <sub>OVTH</sub> - 1%) to (V <sub>O</sub>                                                                                     | OVTH + 1%)                                          |                          | 5   |                          | μs    |

| IN-to-RST Reset<br>Propagation Delay    | t <sub>D</sub>                                 | (V <sub>UVTH</sub> + 1%) to (V <sub>I</sub>                                                                                     | <sub>UVTH</sub> - 1%)                               |                          | 15  |                          | μs    |

| INPUT VOLTAGE (WDI,                     | CLR)                                           |                                                                                                                                 |                                                     |                          |     |                          | •     |

| WDI, CLR Input Voltage Low              |                                                |                                                                                                                                 |                                                     |                          |     | 0.3 x<br>V <sub>DD</sub> | V     |

| WDI, CLR Input Voltage<br>High          |                                                |                                                                                                                                 |                                                     | 0.7 x<br>V <sub>DD</sub> |     |                          | V     |

| WDI, CLR Leakage<br>Current             |                                                |                                                                                                                                 |                                                     | -1                       |     | +1                       | μA    |

| OUTPUT VOLTAGE ( RS                     | $\overline{T}, \overline{WDO}, \overline{OV})$ |                                                                                                                                 |                                                     |                          |     |                          |       |

| Output Voltage Low V <sub>OL</sub> RST, |                                                | RST, OV, WDO                                                                                                                    | V <sub>DD</sub> = 5V, I <sub>SINK</sub> = 3mA       |                          | 0.1 | 0.3                      |       |

|                                         | V <sub>OL</sub>                                | KS1, UV, WUU                                                                                                                    | V <sub>DD</sub> = 1.71V, I <sub>SINK</sub><br>= 8μA |                          | 0.1 | 0.3                      | V     |

|                                         | RST                                            | V <sub>DD</sub> = 1.1V, I <sub>SINK</sub><br>= 8μA                                                                              |                                                     | 0.1                      | 0.3 |                          |       |

**Note 1:** Minimum pulse required to clear  $\overline{OV}$  latched state. No overvoltage fault present and  $\overline{RST}$  = high.

Note 2: Pulling  $\overline{\text{CLR}}$  low for a pulse width duration  $t_{\text{CLR}} > 5 \mu \text{s}$  asserts  $\overline{\text{RST}}$ . A consecutive series of pulses on  $\overline{\text{CLR}}$  with low pulse width duration of  $t_{\text{CLR}} > 5 \mu \text{s}$  must be separated by high pulse width duration  $> t_{\text{RP}}$  for valid reset operation.

Note 3: The margin for error will be an additional ±30µs due to the internal synchronization logic.

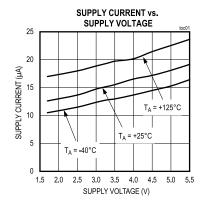

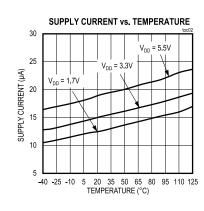

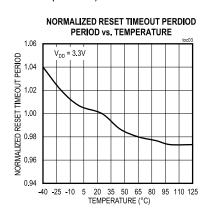

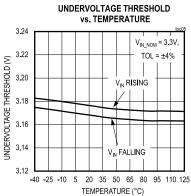

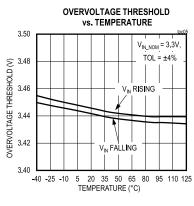

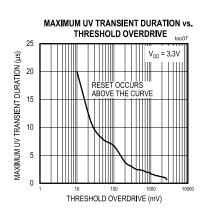

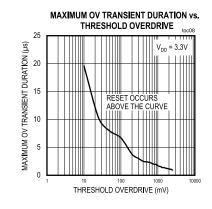

## **Typical Operating Characteristics**

$(V_{DD}$  = 1.71V to 5.5V,  $T_A$  = -40°C to +125°C, Typical values are at  $V_{DD}$  = 3.3V, unless otherwise specified.)

## **Typical Operating Characteristics (continued)**

$(V_{DD} = 1.71 \text{V to } 5.5 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{Typical values are at } V_{DD} = 3.3 \text{V}, \text{ unless otherwise specified.})$

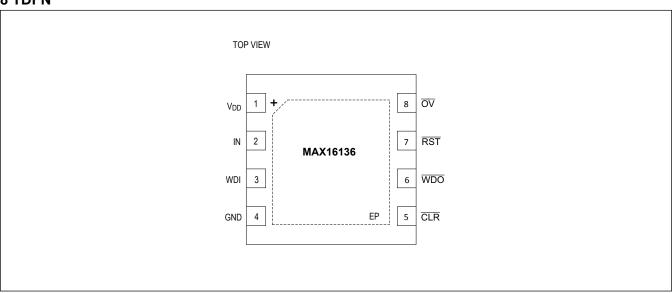

## **Pin Configuration**

#### 8 TDFN

## **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>DD</sub> | Supply Input. Bypass V <sub>DD</sub> to ground with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                               |

| 2   | IN              | Monitoring Input. IN monitors for undervoltage/overvoltage faults with respect to nominal input threshold. When $V_{\text{IN}}$ falls outside the the undervoltage/overvoltage thresholds window, $\overline{\text{RST}}$ asserts and stays asserted for reset timeout period after $V_{\text{IN}}$ falls within undervoltage/overvoltage thresholds window.                                                                                                         |

| 3   | WDI             | Watchdog Input. The internal watchdog timer clears to zero on the falling edge of WDI or when RST goes high. If WDI sees another falling edge within the factory-trimmed watchdog window, WDO will remain de-asserted. Transitions outside this window, either faster or slower, will cause WDO to pulse low. WDI must not be left floating. Connect to ground with 100kΩ resistor to ensure proper device operation. See Window Watchdog Operation for more detail. |

| 4   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | CLR             | Clear Input. Pull $\overline{\text{CLR}}$ low for a pulse duration of $t_{\text{CLR}}$ to clear the overvoltage fault output at $(\overline{\text{OV}})$ after the overvoltage condition is removed. $\overline{\text{CLR}}$ has a 50k $\Omega$ internal pull up to $V_{DD}$ .                                                                                                                                                                                       |

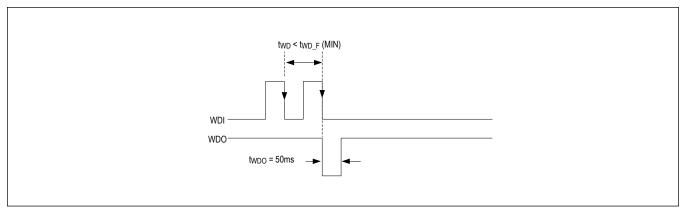

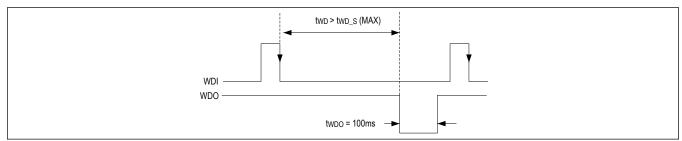

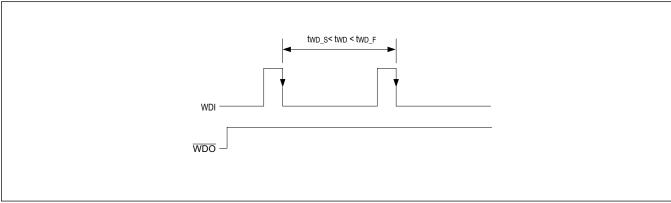

| 6   | WDO             | Open-Drain Watchdog Output. $\overline{\text{WDO}}$ asserts low for 50ms when two consecutive falling transitions on WDI are shorter than $t_{\text{WD}\_F}$ . $\overline{\text{WDO}}$ asserts low for 100ms when two consecutive falling transitions on WDI is longer than $t_{\text{WD}\_S}$ . See $\underline{\text{Window Watchdog Operation}}$ for more detail.                                                                                                 |

| 7   | RST             | Open-Drain Reset Output. $\overline{RST}$ asserts low when $V_{IN}$ falls outside of the undervoltage/overvoltage threshold's window. The reset output deasserts after the reset timeout period when $V_{IN}$ enters the undervoltage/overvoltage threshold's window.                                                                                                                                                                                                |

| 8   | ŌV              | Overvoltage Fault Output. $\overline{\text{OV}}$ latches low when the voltage at IN exceeds the overvoltage threshold setting. To clear the latch, pull $\overline{\text{CLR}}$ low for t <sub>CLR</sub> pulse width duration.                                                                                                                                                                                                                                       |

| -   | EP              | Exposed pad. Connect EP to GND to improve heat dissipation capability. Add thermal vias below the exposed pad.                                                                                                                                                                                                                                                                                                                                                       |

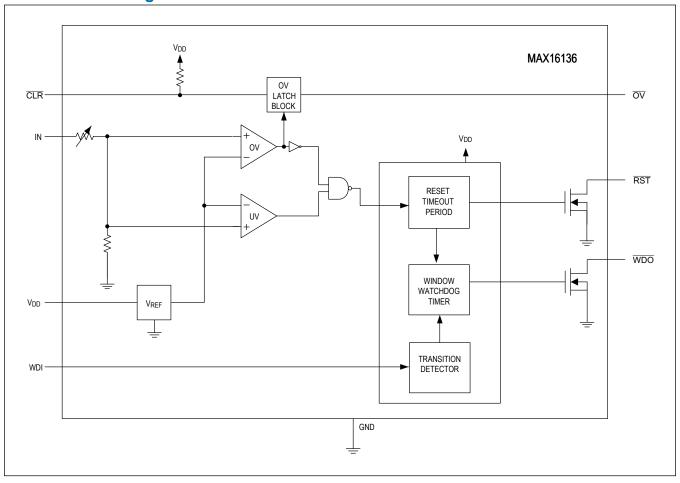

## **Internal Block Diagram**

#### **Detailed Description**

The MAX16136 is a high-accuracy supervisory circuit that monitors a single system-supply voltage for factory-trimmed undervoltage/overvoltage window-threshold settings between  $\pm 4\%$  to  $\pm 11\%$  input tolerance. A reset output ( $\overline{RST}$ ) asserts when the input voltage exceeds the selected tolerance levels and stays asserted for the reset timeout period after the supply voltage falls back within the selected undervoltage/overvoltage window threshold. An overvoltage fault output ( $\overline{OV}$ ) latches low when the supply voltage exceeds the overvoltage threshold level. The latched output can be cleared by pulling the clear input ( $\overline{CLR}$ ) low for  $t_{CLR}$  pulse duration. See the *Electrical Characteristics* for more detail.

The MAX16136 includes a window-watchdog timer circuit that monitors microprocessor or microcontroller activity (Figure 1). During normal operation, the microprocessor or microcontroller toggles the watchdog input (WDI) low within the factory-set window of operation. If the watchdog input is strobed faster than the fast watchdog timeout period, the watchdog output (WDO) pulses low for 50ms (typ). If the watchdog input is strobed slower than the slow watchdog timeout period, the watchdog output pulses low for 100ms (typ).

Figure 1. MAX16136 Detailed Watchdog Input Timing Relationship

#### Nominal Input Threshold Range

The MAX16136 offers a wide range of thresholds for monitoring system voltages from 0.5V to 5V in approximately 20mV increments. Each threshold is factory-trimmed for undervoltage/overvoltage threshold-window between ±4% to ±11% symmetrically with respect to nominal input threshold voltage. Contact Maxim sales for options not listed in the <u>Ordering Information</u> table.

#### **Undervoltage/Overvoltage Thresholds**

The MAX16136 monitors supply voltage for undervoltage/overvoltge faults with respect to nominal input voltage with ±1% accuracy over the operating temperature and supply ranges. The undervoltage and overvoltage thresholds are factory-trimmed from ±4% to ±11% in ±1% increments. Contact Maxim for threshold not listed in the *Ordering Information* table.

#### **Undervoltage/Overvoltage Threshold Hysteresis**

The MAX16136's monitoring input (IN) features undervoltage/overvoltage threshold hysteresis that provides immunity to short input transients. The input hysteresis is factory-set to either 0.25% or 0.5% and is applicable to both undervoltage and overvoltage thresholds. Contact Maxim for hysteresis option not listed in the <u>Ordering Information</u> table.

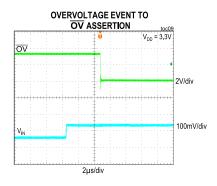

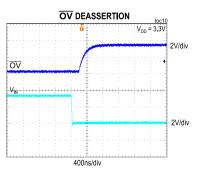

## Overvoltage Fault Output(OV)

The MAX16136 features an open-drain, active-low overvoltage fault output  $(\overline{OV})$  that asserts low  $5\mu s$  after input voltage exceeds the overvoltage threshold level.  $\overline{OV}$  is a latched output and can be cleared by pulling  $\overline{CLR}$  input low for  $t_{CLR}$  pulse width duration. See Figure 2 for more detail.

### Clear Input (CLR)

The MAX16136 provides an active-low input  $(\overline{CLR})$  to clear the latched overvoltage fault output  $(\overline{OV})$ . Pulling  $\overline{CLR}$  low for  $t_{CLR}$  pulse duration clears the overvoltage fault after the overvoltage condition is removed. See the <u>Electrical Characteristics</u> for more detail. The MAX16136 ignores any activity on  $\overline{CLR}$  input while the device is in an overvoltage condition. See <u>Figure 2</u> for the timing diagram.

Figure 2. Clear Input Timing Diagram

**Note:** Pulling  $\overline{\text{CLR}}$  low for a pulse width duration ( $t_{\text{CLR}}$ ) > 5µs asserts  $\overline{\text{RST}}$ . A consecutive series of pulses on  $\overline{\text{CLR}}$  with a low pulse width duration of  $t_{\text{CLR}}$  > 5µs must be separated by a high pulse width duration >  $t_{\text{RP}}$  for a valid reset output.

#### **Window Watchdog Operation**

The MAX16136 offers a window-watchdog circuit for monitoring the microprocessor or microcontroller activity. During normal operation the microprocessor or microcontroller repeatedly toggles the watchdog input WDI <u>low</u>. If the signal on WDI has two consecutive falling edges too close to each other ( $t_{WD} < t_{WD}_F$ ), the watchdog output, WDO pulses low for 50ms. If the signal on WDI has two consecutive falling edges too far apart ( $t_{WD} > t_{WD}_S$ ) the watchdog output pulses low 100ms. Two falling transitions within fast watchdog timeout and slow watchdog timeout window clears the watchdog timer and keeps the watchdog output deasserted. See <u>Figure 3</u>, <u>Figure 4</u>, <u>Figure 5</u>, and <u>Table 1</u> for more detail. Contact Maxim for a watchdog timeout not listed in <u>Table 1</u>.

Figure 3. Fast Watchdog Fault Timing Characteristics

Figure 4. Slow Watchdog Timing Characteristics

Figure 5. Normal Watchdog Operation (No Watchdog Output Pulse)

**Table 1. Window Watchdog Available Options**

| OPTIONS | FAST WD TIMEOUT PERIOD (ms) | SLOW WD TIMEOUT PERIOD (ms) |

|---------|-----------------------------|-----------------------------|

| 1       | 1                           | 10                          |

| 2       | 2                           | 20                          |

| 3       | 4                           | 40                          |

| 4       | 8                           | 80                          |

| 5       | 16                          | 160                         |

| 6       | 32                          | 320                         |

| 7       | 64                          | 640                         |

| 8       | 128                         | 1280                        |

| 9       | 256                         | 2560                        |

| 10      | 512                         | 5120                        |

| 11      | 1024                        | 10240                       |

| 12      | 2048                        | 20480                       |

| 13      | 4096                        | 40960                       |

### **Reset Output**

The MAX16136 offers an active-low, open-drain reset output (RST) that asserts low when the supply voltage falls outside of the undervoltage/overvoltage window threshold. The reset output deasserts after the selected reset timeout period when the supply voltage falls back within the undervoltage/overvoltage window threshold. See <u>Table 2</u> for more details. Contact Maxim for reset timeout period options not listed in <u>Table 2</u>.

**Table 2. Reset Timeout Period Available Options**

| OPTIONS | RESET TIMEOUT PERIOD (ms) |

|---------|---------------------------|

| 1       | 1                         |

| 2       | 5                         |

| 3       | 10                        |

| 4       | 15                        |

| 5       | 20                        |

| 6       | 50                        |

| 7       | 100                       |

| 8       | 150                       |

| 9       | 200                       |

| 10      | 250                       |

| 11      | 300                       |

| 12      | 500                       |

| 13      | 750                       |

| 14      | 1000                      |

| 15      | 1500                      |

### **Applications Information**

#### **Setting Input Thresholds**

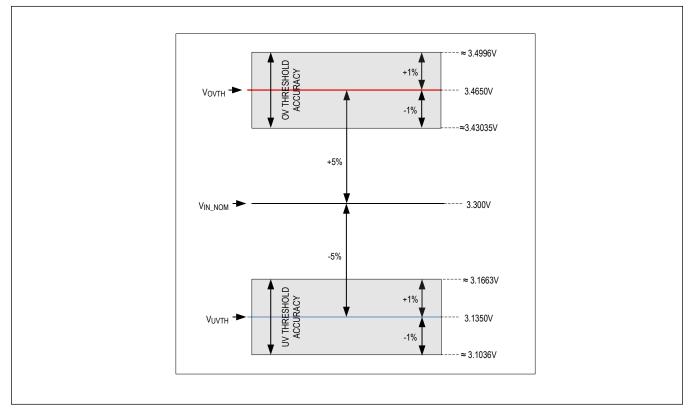

The MAX16136 monitors a system supply voltage for undervoltage/overvoltage window-threshold. Depending on the system supply tolerance requirement, the undervoltage/overvoltage thresholds can be factory-trimmed from  $\pm 4\%$  to  $\pm 11\%$ . The tolerance setting is symmetrical with respect to the selected nominal input threshold voltage ( $V_{IN\_NOM}$ ). A detailed calculation of how to determine the undervoltage/overvoltage threshold levels with  $\pm 1\%$  threshold accuracy for 3.3V  $\pm 5\%$  supply voltage is presented here:

$V_{IN NOM} = 3.3V$

$TOL = \pm 5\%$

$V_{UVTH} = V_{IN NOM} (1 - 5\%) = 3.3V (1 - 0.05) = 3.3V - 0.165V = 3.135V$

$V_{OVTH} = V_{IN NOM} (1 + 5\%) = 3.3V (1 + 0.05) = 3.3V + 0.165V = 3.465V$

Where  $V_{IN\_NOM}$  is the selected nominal input threshold voltage, TOL is the input tolerance,  $V_{UVTH}$  is undervottage threshold voltage, and  $V_{OVTH}$  is the overvoltage threshold voltage.

The MAX16136 monitors the supply voltage with ±1% accuracy over the operating temperature and supply range. The accuracy range for the 3.3V ±5% is shown below:

$V_{UVTH\ A} = V_{UVTH\ (1\pm1\%)} = 3.135V\ (1\pm0.03135V) = 3.135V\pm0.03135V$

$V_{OVTH\ A} = V_{OVTH\ (1\pm1\%)} = 3.465V\ (1\pm0.03465V) = 3.465V\pm0.03465V$

Where V<sub>UVTH\_A</sub> is the undervoltage threshold accuracy range and V<sub>OVTH\_A</sub> is the overvoltage threshold accuracy range. See <u>Figure 6</u> for details.

Figure 6. Undervoltage/Overvoltage Threshold Accuracy

#### **Power Supply Bypassing/Noise Immunity**

The MAX16136 operates from a 1.71V to 5.5V input supply range. An undervoltage lockout ensures that the outputs are in the correct states when the UVLO is exceeded. Bypass  $V_{DD}$  to ground with a 0.1 $\mu$ F capacitor as close to the device as possible. The additional capacitor improves transient immunity. For proper operation, limit  $V_{DD}$  noise within 200mV peak-to-peak.

#### **Selector Guide Table**

**Table 3. Selector Guide**

| PART<br>NUMBER      | THRESHOLD<br>VOLTAGE (V) | TOLERANCE<br>(%) | HYSTERESIS (%) | RESET TIMEOUT (ms) | WINDOW WATCHDOG<br>TIMEOUT (ms/ms) |

|---------------------|--------------------------|------------------|----------------|--------------------|------------------------------------|

| MAX1613600/<br>VY+T | 3.3                      | ±4               | ±0.25          | 10                 | 8/80                               |

| MAX1613601/<br>VY+T | 1.0                      | ±4               | ±0.25          | 20                 | 32/320                             |

| MAX1613602/<br>VY+T | 3.3                      | ±4               | ±0.25          | 1                  | 16/160                             |

| MAX1613603/<br>VY+T | 5.0                      | ±4               | ±0.25          | 10                 | 8/80                               |

## **Typical Application Circuit**

## **Ordering Information**

| PART NUMBER      | TEMP RANGE      | PIN-PACKAGE |

|------------------|-----------------|-------------|

| MAX1613600/VY+T  | -40°C to +125°C | 8 TDFN      |

| MAX1613601/VY+T* | -40°C to +125°C | 8 TDFN      |

| MAX1613602/VY+T* | -40°C to +125°C | 8 TDFN      |

| MAX1613603/VY+T  | -40°C to +125°C | 8 TDFN      |

N Denotes automotive grade.

Y Denotes side-wettable package.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

<sup>\*</sup>Future product—contact factory for availability.

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                    | PAGES<br>CHANGED |

|--------------------|---------------|------------------------------------------------------------------------------------------------|------------------|

| 0                  | 6/19          | Initial release                                                                                | _                |

| 1                  | 6/21          | Updated General Description, Pin Configuration, and Pin Description; added Table 1 and Table 2 | 1, 6, 7, 10–14   |

| 2                  | 12/21         | Updated Table 3 and Ordering Information table                                                 | 14, 15           |