#### MAX16550

# Integrated Protection IC on 12V Bus with an Integrated MOSFET, Lossless Current Sensing, and PMBus Interface

### **General Description**

The MAX16550 is a protection IC with an integrated low-resistance MOSFET and lossless current-sense circuitry featuring SMBus/PMBus™ control and reporting. This IC is designed to provide the optimum solution for distribution, control, monitoring and protection of the system's 12V power supply. An internal LDO provides the supply voltage for the protection IC.

If no fault is detected, the IC initiates the startup and has been designed to provide controlled, monotonic startup. Programmable soft-start ramp and delay is implemented to limit the in-rush current during startup.

The IC monitors the current and voltage of the 12V system power rail and provides multiple levels of protection with fast turn-off if a fault is detected.

Maxim's patented, lossless current sense provides high accuracy current sensing over load and temperature, improving overall system-energy efficiency, and reducing dissipation.

Output voltage is monitored at all times. If at any time the output voltage falls below the programmable output undervoltage-lockout threshold, the PWRGD signal is asserted low. If at any time the input voltage falls below the programmable input undervoltage-lockout threshold, the PWRGD signal is asserted low. The IC can be programmed through PMBus to provide input overvoltage protection. Input overvoltage protection is disabled by default. When enabled through PMBus, if the input voltage exceeds a programmable overvoltage threshold, the MOSFET is latched off and a fault indicated.

PMBus is a trademark of SMIF, Inc.

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- MAX16550—30A Protection ICn

- High-Density (4mm x 4.5mm for 30A): Less than 25% of the Board Area of Conventional Solutions

- · Monolithic Integration of Power, Control, and Monitoring

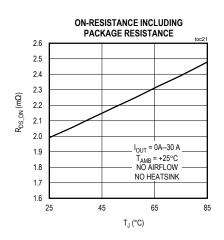

- Integrated Power MOSFET with 1.9mΩ Total Resistance in 12V Power Path (R<sub>DS(ON)</sub> Including Package)

- Integrated Lossless, Precise Current Sensing

- Integrated LDO Provides V<sub>DD</sub> Supply (1.8V Bias Suppy)

- Enables Advanced System Power Management— PMBus/SMBus Telemetry with Extensive Status Monitoring and Reporting

- Load Current Indicator (ILOAD) Pin Provides Analog Output Current Reporting with High Accuracy

- Programmable Soft-Start for Inrush Current Limiting

- Increases Power-Supply Reliability with IC Self-Protection Features

- · Very Fast Fault Detection and Isolation

- V<sub>IN</sub> to V<sub>OUT</sub> Short Protection During Startup

- · Overtemperature Protection

- · Three Levels of Overcurrent Protection

- Programmable Moderate OCP

- Programmable Severe OCP Provides Isolation < 5µs.</li>

- Fail-Safe Safe OCP Provides Isolation < 250ns.</li>

#### **Additional Features**

- Programmable Soft-Start and Delay

- Programmable Input Undervoltage-Lockout Threshold (UVLO)

- Programmable Power-Good Threshold

- PWRGD Pin for Output UVLO/Input UVLO Reporting

- FAULT Pin for Fault Reporting

### **Systems and Applications**

Servers, Networking, Storage, Communication Equipment and AC/DC Power Supplies

- Integrated Protection IC on 12V

- Circuit Breaker/E-Fuse, Hot Swap

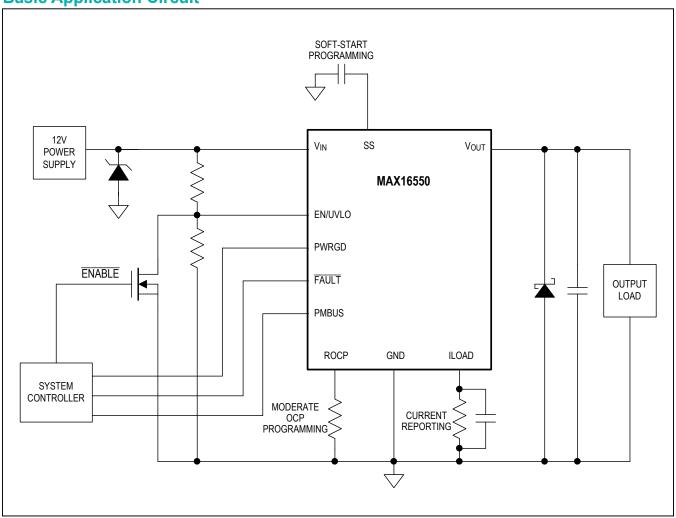

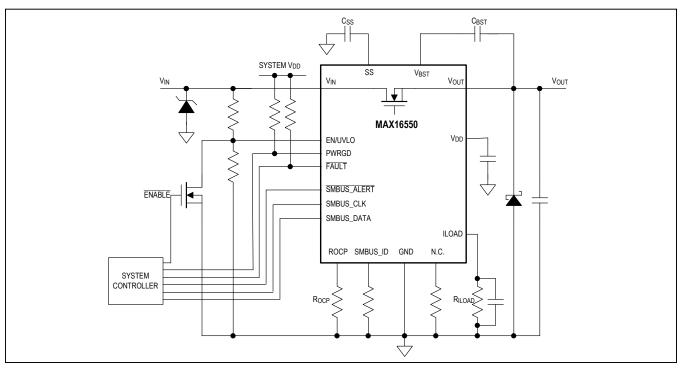

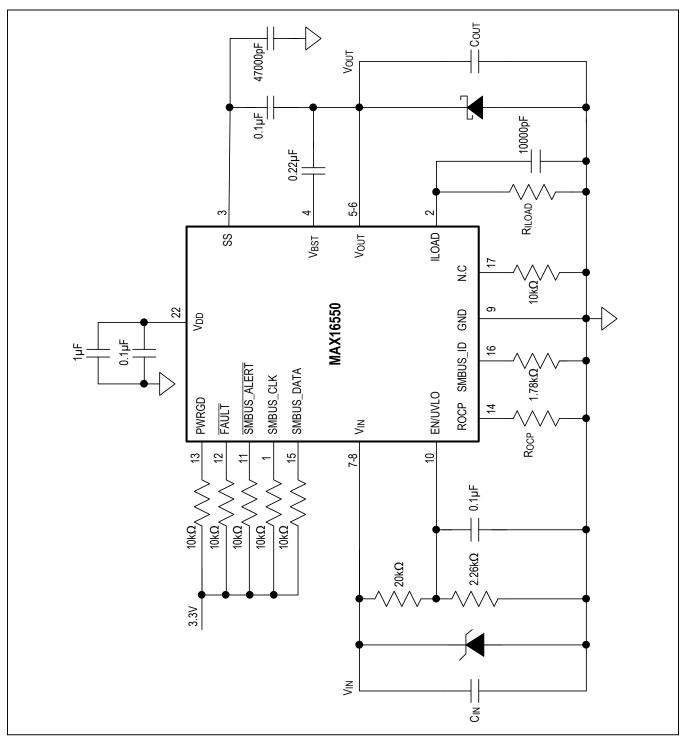

## **Basic Application Circuit**

### MAX16550

# Integrated Protection IC on 12V Bus with an Integrated MOSFET, Lossless Current Sensing, and PMBus Interface

## **Absolute Maximum Ratings (Note 1)**

| Supply Voltage (V <sub>IN</sub> ) DC                                        | 0.3V to +16V  | ILOAD                                  | 0.3V to +2.5V  |

|-----------------------------------------------------------------------------|---------------|----------------------------------------|----------------|

| Supply Voltage (V <sub>IN</sub> ) 150µs                                     |               | Output Voltage (VOLT) DC               | 0.3V to +16V   |

| Bias Supply Voltage (V <sub>DD</sub> )                                      | 0.3V to +2.5V | BST (Relative to V <sub>OUT</sub> )    | 0.3V to +2.5V  |

| PWRGD, FAULT                                                                | 0.3V to +5.5V | SS                                     | 0.3V to +16V   |

| EN/UVLO, R <sub>OCP</sub>                                                   | 0.3V to +2.5V | Junction Temperature (T <sub>J</sub> ) | 150°C          |

| SMBUS_CLK, SMBUS_DATA,                                                      |               | Storage Temperature Range              | 65°C to +165°C |

| SMBUS_ALERT                                                                 | 6V            | Peak Reflow Temperature                | 260°C          |

| SMBUS_ID                                                                    | 0.3V to +2.5V |                                        |                |

| Operating Ratings                                                           |               |                                        |                |

| Supply Voltage (V <sub>IN</sub> )<br>Bias Supply Voltage (V <sub>DD</sub> ) |               | Junction Temperature (T <sub>J</sub> ) | 0°C to +125°C  |

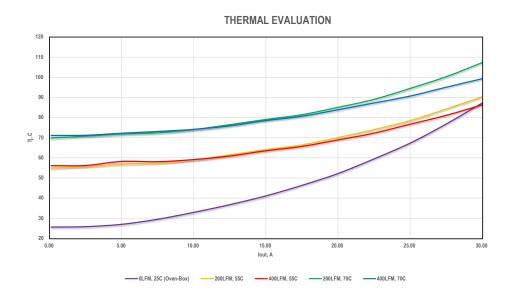

### **Package Thermal Characteristics**

Junction-to-Case Thermal Resistance (θ<sub>JC</sub>, max)......0.31°C/W

Note 1: These products are completely Halogen-free and Pb-free, employing special materials sets: molding compounds/die attach materials and 100% matte tin plate including anneal. These products are RoHS compliant with an -e3 termination finish and are compatible with both SnPb and Pb-free soldering operations. These products are MSL classified at peak reflow temperatures that meet JEDEC JSTD-020.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

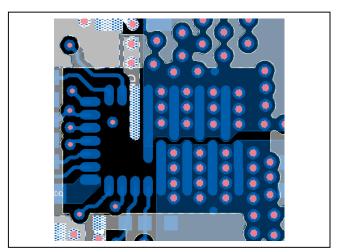

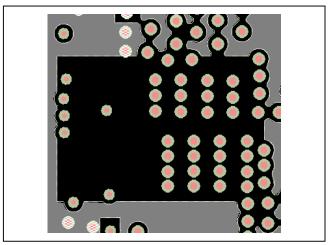

### **Package Information**

| PACKAGE TYPE: 18 FCQFN           |                |  |  |

|----------------------------------|----------------|--|--|

| Package Code                     | P184A4F+1      |  |  |

| Outline Number                   | <u>21-1080</u> |  |  |

| Land Pattern Number              | 90-0529        |  |  |

| THERMAL RESISTANCE               |                |  |  |

| Junction to Case $(\theta_{JC})$ | 0.31°C/W       |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

### **Electrical Characteristics**

$(V_{IN} = 12V \pm 10\%$ , unless otherwise noted.  $T_J = 0^{\circ}C$  to +125°C, unless otherwise noted. Specifications are 100% production tested at  $T_A = +32^{\circ}C$ . Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                                | SYMBOL                    | CONDITIONS                                                             | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------|------|------|------|-------|

| 12V SUPPLY (V <sub>IN</sub> )                                            |                           |                                                                        |      |      |      |       |

| Supply Voltage Range                                                     | V <sub>IN</sub>           |                                                                        | 10.8 | 12   | 13.2 | V     |

|                                                                          |                           | FET off                                                                | 3.0  |      | 6.25 |       |

| Device Supply Current                                                    | I <sub>IN</sub>           | FET on: I <sub>OUT</sub> = 0 (Note 2)                                  | 3.7  |      | 6.75 | mA    |

|                                                                          |                           | FET on: I <sub>OUT</sub> = 30A (Note 2)                                |      |      | 10   | ]     |

| INTEGRATED 1.8V LINEAR REGUI                                             | LATOR                     |                                                                        |      |      |      |       |

| LDO Output Voltage Range                                                 |                           |                                                                        | 1.76 | 1.85 | 1.94 |       |

| V <sub>DD</sub> Falling                                                  |                           | (Note 2)                                                               | 1.55 | 1.6  | 1.7  | V     |

| V <sub>DD</sub> Rising                                                   | $V_{DD}$                  | (Note 2)                                                               | 1.62 | 1.67 | 1.73 | ]     |

| Hysteresis                                                               |                           | (Note 2)                                                               | 30   | 60   | 80   | mV    |

| V <sub>DD</sub> UVLO Response Time                                       |                           | (Note 2)                                                               |      | 2    |      | μs    |

| UNDERVOLTAGE LOCKOUT: 12V                                                | SUPPLY (V <sub>IN</sub> ) |                                                                        |      |      |      |       |

| V <sub>IN</sub> _UVLO Rising Threshold                                   | .,                        |                                                                        | 0.95 | 1    | 1.05 | V     |

| V <sub>IN</sub> _UVLO Hysteresis                                         | $V_{IN\_UVLO}$            | At EN/UVLO pin                                                         |      | 50   |      | mV    |

| Programmable 12V V <sub>IN</sub> Undervoltage Threshold for Rising Input | V <sub>IN_UVLO</sub>      | Programmable through resistor-<br>divider, measured at V <sub>IN</sub> | 8    |      |      | V     |

| Response Time                                                            | t <sub>D</sub>            | From EN/UVLO = 0V to FET off                                           |      | 2    |      | μs    |

| EN_UVLO PIN INTERNAL PARAM                                               | ETERS                     |                                                                        |      |      |      |       |

| EN_UVLO Pin Leakage                                                      |                           | EN_UVLO = 1.8V                                                         | 5    | 6.7  | 11   | μA    |

| EN_UVLO Internal Pulldown Resistor                                       |                           |                                                                        | 110  | 250  | 450  | kΩ    |

| BOOST VOLTAGE (V <sub>BST</sub> )                                        |                           |                                                                        |      |      |      |       |

| V <sub>BST</sub> Charging Time to 1.6V Above V <sub>OUT</sub>            | <sup>t</sup> CHARGE       | C <sub>BST</sub> = 100nF                                               |      | 150  |      | μs    |

| BST Voltage Above V <sub>OUT</sub>                                       | V <sub>BST</sub>          |                                                                        |      | 1.8  |      | V     |

| Rising UVLO Threshold Above V <sub>OUT</sub>                             |                           | (Note 2)                                                               | 0.8  | 1.2  | 1.6  | ,,    |

| Falling UVLO Threshold Above V <sub>OUT</sub>                            | BOOST UVLO                | (Note 2)                                                               | 0.74 | 1.1  | 1.5  | V     |

| UVLO Hysteresis                                                          |                           | (Note 2)                                                               | 60   | 130  | 400  | mV    |

| Falling Lockout Response Time                                            | t <sub>D</sub>            |                                                                        |      | 1.5  |      | μs    |

| INTEGRATED MOSFET CHARACT                                                |                           |                                                                        |      |      |      |       |

| On-Resistance                                                            | R <sub>DS(ON)</sub>       | (Note 2)                                                               |      | 1.9  |      | mΩ    |

## **Electrical Characteristics (continued)**

$(V_{IN} = 12V \pm 10\%$ , unless otherwise noted.  $T_J = 0$ °C to +125°C, unless otherwise noted. Specifications are 100% production tested at  $T_A = +32$ °C. Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                     | SYMBOL                    | CONDITIONS                                                                                                                          | MIN | TYP                       | MAX | UNITS                |

|---------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|-----|----------------------|

| COMMON OVERCURRENT PROT                                       | ECTION                    |                                                                                                                                     |     |                           |     |                      |

| Severe OCP Threshold,<br>% Above Moderate OCP                 | I <sub>OCP</sub> (SEVERE) | Digitally programmable                                                                                                              |     | 130<br>170                |     | %                    |

| Severe OCP Threshold Accuracy                                 | J GOI (GEVEILE)           |                                                                                                                                     |     | ±20                       |     | -                    |

| Severe OCP Delay                                              | t <sub>D</sub> (SEVERE)   | From fault threshold exceeded to FET off (Note 3)                                                                                   |     | 5                         |     | μs                   |

| Gain from ROCP Pin Current                                    | G <sub>OCP</sub>          | (Note 2)                                                                                                                            |     | 4                         |     | A/µA                 |

| Allowed Range for No-Fault Detection                          | ROCP                      |                                                                                                                                     | 28  |                           | 360 | kΩ                   |

| Startup OCP Threshold                                         | locp_startup              | Programmed through PMBus default setting = 8A (Note 2)                                                                              |     | 4<br>8<br>12<br>16        |     | A                    |

| Startup OCP Threshold Accuracy                                |                           | I <sub>OUT</sub> = 4A<br>I <sub>OUT</sub> = 8A, 12A, 16A                                                                            |     | ±30<br>±20                |     | %                    |

| Safe OCP Threshold                                            | 1                         | (Note 2)                                                                                                                            |     | 60                        |     | Α                    |

| Safe OCP Threshold Accuracy                                   | OCP_SAFE                  | V <sub>IN</sub> = 12V, T = +125°C                                                                                                   |     | ±20                       |     | %                    |

| Safe OCP Delay                                                | <sup>t</sup> D_SAFE       | From fault threshold exceeded to FET off                                                                                            |     | 250                       |     | ns                   |

| OVERCURRENT PROTECTION (M                                     | MAX16550)                 |                                                                                                                                     |     |                           |     |                      |

| Gain from ROCP Pin Current                                    | G <sub>OCP</sub>          | Gain from ROCP pin current to I <sub>OUT</sub> (Note 2)                                                                             |     | 4                         |     | Α/μΑ                 |

| Moderate OCP Voltage Threshold                                | .,                        | Referred to voltage over ROCP (Note 2)                                                                                              |     | 0.8                       |     | V                    |

| Moderate OCP Voltage Threshold Accuracy                       | VOCPM                     | Referred to I <sub>OUT</sub> using Equation 1                                                                                       |     | ±12                       |     | %                    |

| Moderate OCP Threshold Range                                  | IOCP(MODERATE)            | Analog programmable through ROCP                                                                                                    | 15  |                           | 35  | А                    |

| Allowable ROCP Range for ROCP_<br>Fault Detection at Power-Up | ROCP                      |                                                                                                                                     | 28  |                           | 360 | kΩ                   |

| Moderate OCP Timeout                                          | <sup>t</sup> OCPM         | I <sub>OUT</sub> > moderate OCP,<br>I <sub>OUT</sub> < severe OCP, programmable<br>default moderate OCP timeout =<br>100μs (Note 3) |     | 12.5<br>100<br>100<br>250 |     | μs<br>μs<br>ms<br>ms |

| Moderate OCP Fault-Detect Delay<br>Timeout Accuracy           |                           | (Note 3)                                                                                                                            |     | ±10                       |     | %                    |

| SOFT-START AND C <sub>OUT</sub>                               | -                         |                                                                                                                                     |     |                           |     | •                    |

| Soft-Start Discharge Resistance                               | SS                        |                                                                                                                                     |     | 1                         | 2   | kΩ                   |

|                                                               |                           |                                                                                                                                     |     |                           |     |                      |

## **Electrical Characteristics (continued)**

$(V_{IN} = 12V \pm 10\%$ , unless otherwise noted.  $T_J = 0$ °C to +125°C, unless otherwise noted. Specifications are 100% production tested at  $T_A = +32$ °C. Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                                                        | SYMBOL                          | CONDITIONS                                            | MIN                      | TYP                | MAX                      | UNITS |

|--------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------|--------------------------|--------------------|--------------------------|-------|

| Soft-Start Charging Current                                                                      | I <sub>SS</sub>                 |                                                       | 20                       |                    | 39                       | μΑ    |

| Soft-Start Capacitor Value Range                                                                 | C <sub>SS</sub>                 | Linear startup ramp                                   | 0                        |                    | 75                       | nF    |

| Soft-Start Time                                                                                  | t <sub>SS</sub>                 | C <sub>SS</sub> = 0nF, I <sub>OUT</sub> = 0A (Note 3) |                          | 1                  |                          | ms    |

| Soft-Start Capacitor Discharge<br>Threshold                                                      |                                 |                                                       | 0.17                     | 0.2                | 0.25                     | V     |

| CSS Discharge Check Duration During Startup                                                      |                                 | (Note 3)                                              |                          | 2.2                |                          | s     |

| Recommended Output Capacitance Range                                                             | C <sub>OUT</sub>                | (Note 2)                                              | 10                       |                    | 10000                    | μF    |

| FET V <sub>GS</sub> UNDERVOLTAGE LOCKO                                                           | DUT                             |                                                       |                          |                    |                          | ,     |

| V <sub>GS</sub> Rising UVLO Threshold                                                            |                                 |                                                       | 0.87                     | 1.3                | 1.61                     | .,    |

| V <sub>GS</sub> Falling UVLO Threshold                                                           |                                 |                                                       | 0.74                     | 1.17               | 1.50                     | V     |

| V <sub>GS</sub> UVLO Hysteresis                                                                  | $V_{GS\_UVLO}$                  |                                                       | 87                       | 100                | 466                      | mV    |

| V <sub>GS</sub> UVLO Masking Time                                                                | _                               | During startup (Note 3)                               |                          | 100                |                          | ms    |

| V <sub>GS</sub> UVLO Deglitching                                                                 |                                 | (Note 3)                                              |                          | 10                 |                          | μs    |

| PASS FET SHORT DETECTION DU                                                                      | IRING STARTUP                   |                                                       |                          |                    |                          | ı     |

| Duration of V <sub>OUT</sub> Discharge Check                                                     | <sup>t</sup> DISCHARGE          | (Note 3)                                              |                          | 2.2                |                          | s     |

| Pulldown Resistance on V <sub>OUT</sub><br>During Self-Check                                     | R <sub>DISCHARGE</sub>          |                                                       | 400                      | 455                | 560                      | Ω     |

| Threshold for Self-Check Procedure                                                               | V <sub>OUT_</sub> SELF<br>CHECK | SMBus/PMBus programmable,<br>default 9V (Note 2)      | 5.8<br>6.8<br>7.7<br>8.8 | 6<br>7<br>8<br>9   | 6.2<br>7.2<br>8.2<br>9.4 | V     |

| Delay from Self-Check Pass to Start<br>V <sub>OUT</sub> Ramp                                     | t <sub>D</sub>                  | Programmable (Note 3)                                 |                          | 0<br>10<br>20      |                          | μs    |

| PWRGD PIN                                                                                        |                                 |                                                       |                          |                    |                          |       |

| Max Allowable PWRGD Output High Voltage                                                          | V <sub>OH</sub>                 | External pullup leakage below 1µA                     |                          | 5.5                |                          | V     |

| PWRGD Output Low Voltage                                                                         | $V_{OL}$                        | Sinking 4mA                                           |                          |                    | 0.4                      | V     |

| Propagation Delay from V <sub>OUT_UVLO</sub><br>Detect to PWRGD Pin Asserted Low                 | t <sub>D</sub>                  | (Note 3)                                              |                          | 3.2                |                          | μs    |

| Threshold for PWRGD Asserted High                                                                |                                 | SMBus/PMBus programmable, default 11V (Note 2)        |                          | 8<br>9<br>10<br>11 |                          | V     |

| PWRGD Clear Timing Time Needed to Clear PWRGD after V <sub>OUT</sub> Has Reached V <sub>IN</sub> | VTH(PWRGD)                      | (Note 3)                                              |                          | 5                  |                          | ms    |

| PWRGD Hysteresis                                                                                 |                                 | (Note 2)                                              | 0.35                     | 0.5                | 0.63                     | V     |

## **Electrical Characteristics (continued)**

$(V_{IN} = 12V \pm 10\%$ , unless otherwise noted.  $T_J = 0$ °C to +125°C, unless otherwise noted. Specifications are 100% production tested at  $T_A = +32$ °C. Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                 | SYMBOL                  | CONDITIONS                                           | MIN | TYP      | MAX  | UNITS |

|-----------------------------------------------------------|-------------------------|------------------------------------------------------|-----|----------|------|-------|

| PWRGD Accuracy                                            |                         |                                                      | -5  |          | +5   | %     |

| OVERTEMPERATURE PROTECTION                                | N                       |                                                      |     |          |      |       |

| Overtemperature-Protection<br>Threshold                   | $T_{OTP}$               | PMBus programmable (Note 2)                          |     | 140      |      | °C    |

| SMBus DATA (SMBUS_DATA) AND                               | CLOCK (SMBUS            | _CLOCK) PINS                                         |     |          |      |       |

| Leakage Current                                           |                         | For pullup = 5.5V (Note 2)                           |     | 5.3      |      | μA    |

| Input Low Voltage                                         | V <sub>IL</sub>         |                                                      |     |          | 0.8  | V     |

| Input High Voltage                                        | V <sub>IH</sub>         |                                                      | 2.1 |          |      | V     |

| Output Low Voltage                                        | V <sub>OL</sub>         | SMBUS_DATA, sinking 4mA                              |     |          | 0.4  | V     |

| Max Allowable External Pullup Voltage                     | V <sub>OH</sub> MAX     |                                                      |     | 5.5      | ,    | V     |

| SMBus ALERT PIN                                           |                         |                                                      |     |          |      |       |

| Output Low Voltage                                        | V <sub>OL</sub>         | Sinking 4mA                                          |     |          | 0.4  | V     |

| Leakage Current                                           |                         | For pullup = 5.5V (Note 2)                           |     |          | 1    | μA    |

| Max Allowable External Pullup<br>Voltage                  | V <sub>OH</sub> MAX     |                                                      |     | 5.5      |      | V     |

| FAULT-ISOLATION DELAY                                     |                         |                                                      |     |          |      |       |

| Fault-Detection Time                                      | t <sub>D</sub>          | Fault detection to start of gate pulldown (Note 3)   |     | 60       |      | ns    |

| Pass FET Turn-Off Time                                    | t <sub>F</sub>          | From start of gate pulldown to pass FET off (Note 3) |     | 50       |      | ns    |

| FAULT PIN                                                 |                         |                                                      |     |          |      |       |

| Input High Voltage                                        | $V_{IH}$                | (Note 2)                                             | 1   |          |      | V     |

| Input Low Voltage                                         | $V_{IL}$                | (Note 2)                                             |     |          | 0.66 | V     |

| Max Allowable FAULT Output High<br>Voltage                | $V_{OH}$                | External pullup, leakage below 1μΑ                   |     | 5.5      |      | V     |

| FAULT Output Low Voltage                                  | $V_{OL}$                | Sinking 4mA                                          |     |          | 0.4  | V     |

| Propagation Delay from Fault Detect to FAULT Asserted Low | t <sub>D</sub>          | (Note 3)                                             |     | 100      |      | ns    |

| V <sub>IN</sub> OVERVOLTAGE PROTECTION                    |                         |                                                      |     |          |      |       |

| Programmable Threshold for OVP                            | V <sub>IN_OVP</sub>     | Measured at V <sub>IN</sub> , programmable (Note 2)  |     | 14<br>16 |      | V     |

| V <sub>IN</sub> Overvoltage Accuracy                      | V <sub>IN_OVP</sub>     |                                                      | -5  |          | +5   | %     |

| Deglitching Time                                          | t <sub>FILTER_OVP</sub> | (Note 3)                                             |     | 20       |      | μs    |

| CURRENT REPORTING (ILOAD) P                               |                         |                                                      |     |          |      | 1     |

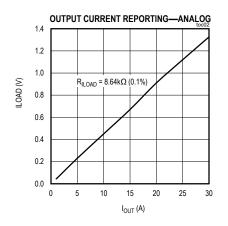

| Linear I <sub>OUT</sub> Reporting Range                   |                         | Current-reporting range                              | 0   |          | 30   | А     |

| Max Allowable Linear Voltage Range                        |                         |                                                      |     | 1.35     |      | V     |

| Offset Current                                            |                         | I <sub>OUT</sub> = 0A                                |     | 0.32     |      | μA    |

## **Electrical Characteristics (continued)**

$(V_{IN} = 12V \pm 10\%$ , unless otherwise noted.  $T_J = 0^{\circ}C$  to +125°C, unless otherwise noted. Specifications are 100% production tested at  $T_A = +32^{\circ}C$ . Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                 | SYMBOL                            | CONDITIONS                                                                       | MIN  | TYP  | MAX  | UNITS |  |

|-------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------|------|------|------|-------|--|

| Current-Reporting Gain                    | G <sub>ILOAD</sub>                | ILOAD current divided by I <sub>OUT</sub> current (Note 2)                       |      | 5    |      | μΑ/Α  |  |

| Bandwidth                                 |                                   | No capacitor in parallel with R <sub>LOAD</sub> resistor                         | 100  |      |      | kHz   |  |

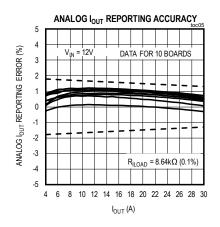

| ANALOG CURRENT-REPORTING                  | ACCURACY                          |                                                                                  |      |      |      | •     |  |

| Current-Reporting Accuracy                | lour                              | I <sub>OUT</sub> = 4A                                                            | -2.5 |      | +2.5 | - %   |  |

| (Notes 3, 4, 5)                           | lout                              | I <sub>OUT</sub> = 30A                                                           | -1.8 |      | +1.8 | 70    |  |

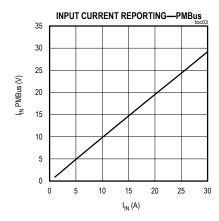

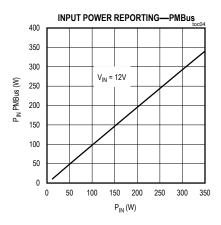

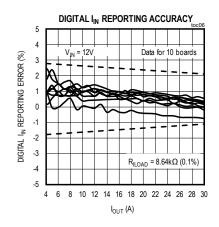

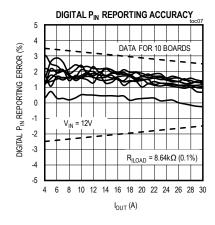

| SMBus/PMBus TELEMETRY                     |                                   |                                                                                  |      |      |      |       |  |

| Digital Current Benerting Accuracy        | READ_IOUT                         | I <sub>OUT</sub> = 4A                                                            |      | ±3   |      | %     |  |

| Digital Current-Reporting Accuracy        | (8Ch),<br>READ IIN (89h)          | I <sub>OUT</sub> = 30A                                                           |      | ±2   |      | 70    |  |

| Digital Power-Reporting Accuracy          | READ_PIN (97h)                    | Digital, $I_{OUT} = 4A$ , $V_{IN} = 12V$ , $R_{LOAD} = 9k\Omega$ (MAX16550)      |      | ±5   |      | - %   |  |

|                                           |                                   | Digital, $I_{OUT}$ = 30A, $V_{IN}$ = 12V,<br>$R_{LOAD}$ = 9k $\Omega$ (MAX16550) |      | ±3.5 |      |       |  |

| Digital Input-Voltage Reporting Accuracy  | READ_VIN (88h)                    |                                                                                  |      | ±1.2 |      | %     |  |

| Digital Output-Voltage Reporting Accuracy | READ_VOUT<br>(8Bh)                |                                                                                  |      | ±1.2 |      | %     |  |

| Digital Temperature-Reporting<br>Accuracy | READ_<br>TEMPERA-<br>TURE_1 (8Dh) |                                                                                  |      | ±8   |      | °C    |  |

| Digital Energy Reporting Assures:         | DEAD FIN (965)                    | I <sub>OUT</sub> = 4A                                                            |      | ±5   |      | - %   |  |

| Digital Energy-Reporting Accuracy         | READ_EIN (86h)                    | I <sub>OUT</sub> = 30A                                                           |      | ±3   |      | 70    |  |

**Note 2:** Denotes specificaltion that apply for typical operating junction temperature ( $T_J = +25^{\circ}C$ ).

Note 3: Guaranteed by design, not production tested.

Note 4: Reporting accuracy presented includes 0.1% external resistor tolerance contribution.

**Note 5:** Min/max limits are  $\geq 4\sigma$  about the mean.

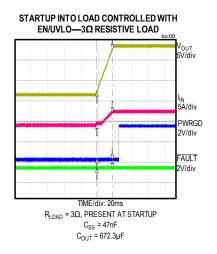

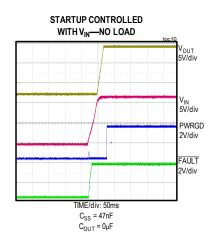

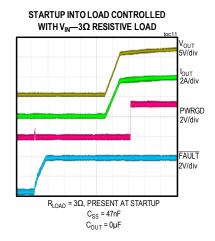

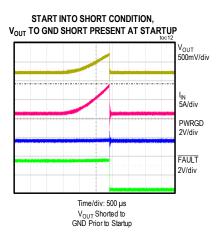

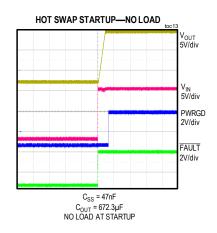

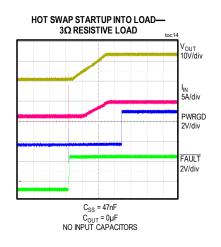

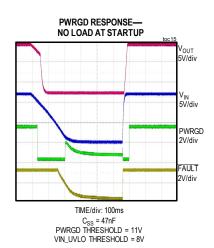

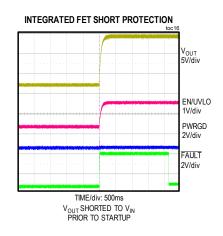

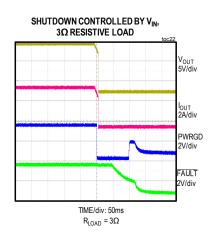

## **Typical Operating Characteristics**

## **Typical Operating Characteristics (continued)**

## **Typical Operating Characteristics (continued)**

## **Typical Operating Characteristics (continued)**

## **Typical Operating Characteristics (continued)**

## **Typical Operating Characteristics (continued)**

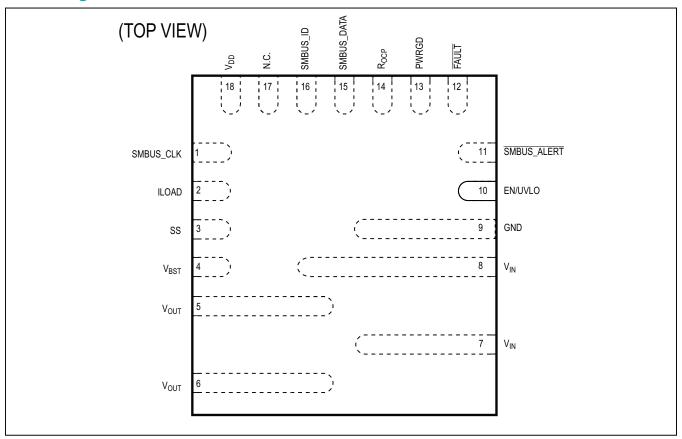

## **Pin Configuration**

## **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SMBUS_CLK        | SMBus Clock Pin.                                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | ILOAD            | Analog Current Representation of the Load Current. Connect the pin to ground through a properly sized resistor for proper voltage representation. Always keep this pin connected to ground through a resistor. A capacitor parallel to the R <sub>ILOAD</sub> resistor is required; see Table 16 for the recommended value.                                                                               |

| 3   | SS               | Soft-Start Pin. A capacitor is connected from SS to GND to program soft-start. The soft-start program capacitor should not exceed 75nF. If a fast load transient (di/dt > 2.5A/ms) resulting in fast and large transient output-voltage deviation is possible in the application, an additional capacitor between SS and $V_{OUT}$ is recommended to keep the pass FET $V_{GS}$ above its UVLO threshold. |

| 4   | V <sub>BST</sub> | Charge-Pump Supply for Pass FET Gate Drive. Connect this node to $V_{OUT}$ through a 220nF bypass capacitor. This supply is designed to be used by the MAX16550 only. No additional load or external components other than a bypass capacitor are allowed on the $V_{\rm BST}$ pin.                                                                                                                       |

| 5-6 | V <sub>OUT</sub> | 12V Output Power Pins (Load Side).                                                                                                                                                                                                                                                                                                                                                                        |

## **MAX16550/MAX16551 Connection Information (continued)**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-8 | V <sub>IN</sub> | 12V Input Power Pins (Power Supply Side).                                                                                                                                                                                                                                                                                                                      |

| 9   | GND             | IC Ground. Connect this node to GND plane through vias for proper operation.                                                                                                                                                                                                                                                                                   |

| 10  | EN/UVLO         | 12V Input Voltage and UVLO Pin. Normally connected to the center node of a resistor-divider connected from V <sub>IN</sub> to ground. A properly sized capacitor can be placed in parallel to the bottom resistor of the resistor-divider for additional filtering. In addition to 12V UVLO programming, this node can be used to enable/disable the MAX16550. |

| 11  | SMBUS_ALERT     | SMBus Alert, Open-Drain, Active-Low Pin.                                                                                                                                                                                                                                                                                                                       |

| 12  | FAULT           | Fault Communication, Bidirectional Pin. It is used to indicate/receive detection of latching fault. See the $\overline{\textit{FAULT}}$ Reporting section for more details. Connect this pin to the system bias supply rail through a $10\text{k}\Omega$ resistor. 5V compliant, active-low pin.                                                               |

| 13  | PWRGD           | Power Good Pin. Used to report $V_{\text{IN}}$ and $V_{\text{OUT}}$ status. See the <i>Power Good (PWRGD) Output</i> section for more details. Connect this pin to system bias supply rail through a $10 \text{k}\Omega$ resistor. This pin is 5V compliant.                                                                                                   |

| 14  | ROCP            | Moderate OCP Threshold Programming Input. Connect this pin to GND using an appropriate programming resistor. See the <i>Moderate OCP Threshold</i> section for additional details. No other components are allowed on this pin.                                                                                                                                |

| 15  | SMBUS_DATA      | SMBus Data Pin.                                                                                                                                                                                                                                                                                                                                                |

| 16  | SMBUS_ID        | SMBus Address Programming and Current Hysteresis Flag Pin. Connect this pin to GND through a properly sized resistor to select desired address setting.                                                                                                                                                                                                        |

| 17  | N.C.            | Not Connected. Connect to GND through a 10kΩ resistor.                                                                                                                                                                                                                                                                                                         |

| 18  | V <sub>DD</sub> | Internal 1.8V Linear Regulator (LDO) Output. Connect this pin to GND through a $1\mu F$ (or higher) capacitor. See Figure 6 for the correct value. No additional loads or components other than external properly sized capacitor are allowed on the $V_{DD}$ pin.                                                                                             |

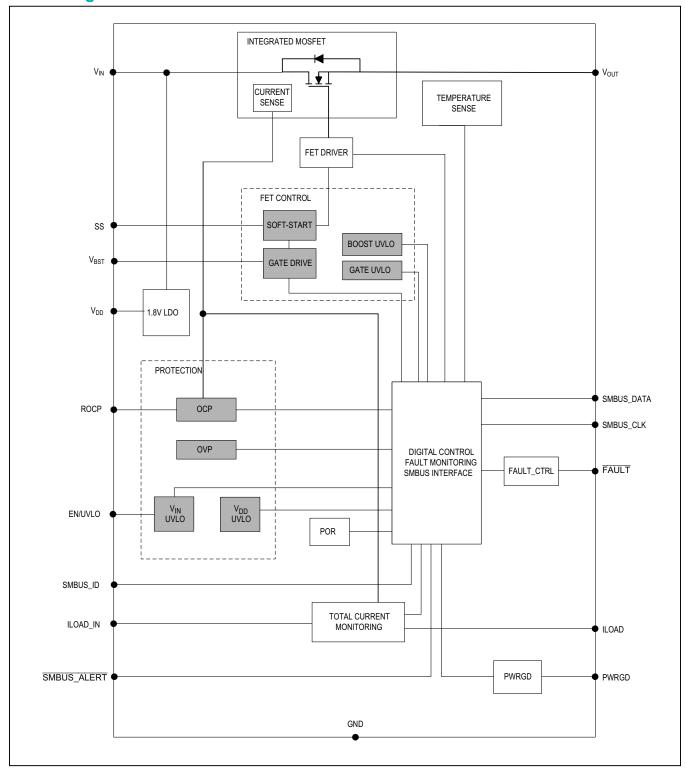

### **Block Diagram**

### **Detailed Description**

The MAX16550 integrated power-protection IC is designed to provide a complete, single-chip circuit-breaker protection solution for the 12V power bus. It combines power monitoring and control functions with a low on-resistance pass FET device that acts as a disconnect switch to limit maximum power distributed to the load. The IC implements Maxim's proprietary integrated lossless current sensing techniques to provide a highly accurate and compact protection solution. The ICs integrate PMBus/SMBus interface for digital control and monitoring.

Refer to the IC *Block Diagram*. An integrated N-channel power MOSFET is driven by the FET control circuit that includes a boost circuit to provide gate drive. An internal LDO provides V<sub>DD</sub> IC bias supply, eliminating the need for external bias supply, enabling effective use of the device in hot-swap applications.

#### **Startup**

The IC enables the integrated 1.8V  $V_{DD}$  LDO once the 12V supply voltage is high enough to guarantee LDO operation. Once  $V_{DD}$  is valid, the ICs read the SMBus\_ID programming resistor value to set the PMBus address and initiate. During this period, the gate-drive supply capacitor becomes fully charged. Once these two func-

tions are complete, the ICs can be controlled through the enable input.

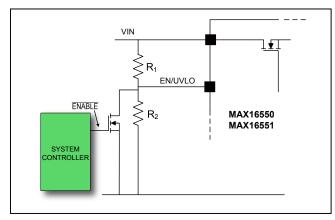

The enable input (EN/UVLO) has a precise threshold and provides a  $V_{\rm IN}$ \_UVLO function, where the enable voltage is derived from  $V_{\rm IN}$  through a resistor-divider, with an optional control signal used in conjunction with the divider, as shown in Figure 5. The EN/UVLO pin must not be pulled high externally other than to pull the EN/UVLO pin high through a propely sized resistor-divider from the input supply. Though the enable signal can be pulled low to disable the part, this should only be allowed to occur when the input-voltage supply is within operating range, as specified in the *Electrical Characteristics* table.

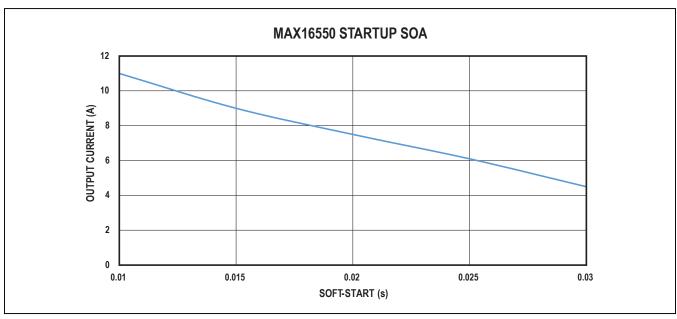

#### **Startup Safe Operating Area (SOA)**

During soft-start, it is important to keep the FET within its safe operating area. The peak current allowed during startup is shown in <a href="Figure 1">Figure 1</a>. In case resistive short is possible in the application, it is required to use startup OCP feature to protect the device. The startup OCP threshold must be programmed to a value lower than safe peak current. <a href="Figure 1">Figure 1</a> assumes pure capacitive or RC load on the output.

Figure 1. MAX16550 Startup SOA

#### Self-Check

Once  $V_{\mbox{\footnotesize{BST UVLO}}}$  has been cleared, the internal V<sub>DD LDO</sub> is fully enabled and the EN/UVLO pin is above the enable threshold, the ICs initiate a timed output discharge as a self-check procedure. By default, the ICs initiate this procedure immediately after V<sub>BST</sub> UVLO has been cleared and the internal V<sub>DD</sub> LDO is fully enabled. Delay to start this procedure can be reprogrammed through PMBus. If the output does not fall below the programmed VOLIT UVLO threshold after a fixed period, the pass FET could potentially be shorted, with the ICs asserting both FAULT and PWRGD pins low. The latched fault condition remains until restart (EN/UVLO or VIN toggling, restarting through the OPERATIONS command). The threshold (VOUT UVLO) for the self-check procedure can be programmed to one of three different values through the PMBus. These values are programmed with the corresponding values for the PWRGD threshold. If the output voltage is below the programmed VOLIT UVLO, the self-check is considered passed and the ICs proceed with startup.

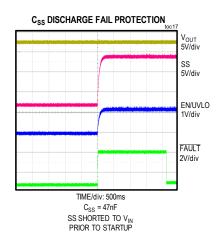

In addition, a soft-start capacitor discharge procedure is performed during every restart. The ICs utilize an integrated resistive element, with resistance approximately  $1.2k\Omega$ , to discharge the CSS capacitor. The ICs check if the voltage across the CSS capacitor is below the soft-start threshold shown in the *Electrical Characteristics* table after a fixed period of time. If the voltage across the CSS capacitor is not below the softstart threshold, the ICs latch the pass FET off and assert the FAULT pin low. The latched fault condition is kept until reset (EN/UVLO or  $V_{IN}$  toggling).

The ICs check the ROCP value at all times, including startup (after the bias supply is valid). This check ensures proper reference OCP threshold selection, which determines startup and severe OCP thresholds. If the wrong ROCP value is detected, the ICs report the fault by asserting the  $\overline{\text{FAULT}}$  signal low. The latched fault condition is kept until restart (EN/UVLO or  $V_{\text{IN}}$  toggling/restarting through the OPERATIONS command).

Figure 2. MAX16550 Configuration Example

#### Soft-Start

Once the self-check procedure is complete, the output-voltage soft-start ramp is initiated. During startup, the  $C_{SS}$  capacitor is charged using a constant-current source. Since the integrated FET is configured as a source follower, the output voltage is ramped monotonically at a rate determined by the external soft-start capacitor.

### **VDD UVLO**

The ICs implement  $V_{DD}$  UVLO fault monitor and protection.  $V_{DD}$  is monitored at all times. Startup

procedures are not initiated until  $V_{DD}$  UVLO is cleared. If  $V_{DD}$  falls below  $V_{DD}$  UVLO during normal operation, this fault is latched and  $V_{IN}$  power cycle/toggle is required to reset this latching fault.

#### **Current Hysteresis**

The SMBUS\_ID pin is used as a current-hysteresis flag after SMBUS\_ID decoding is completed. If the output current is greater than the MFR\_SPECIFIC\_HYSTH level, the current-hysteresis flag is set to high. If output current is less than the MFR\_SPECIFIC\_HYSTL level, then the current-hysteresis flag is set to low.

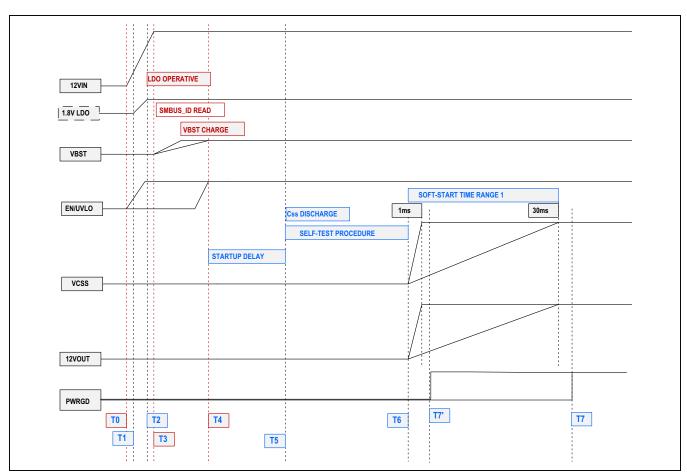

Figure 3. Startup Timing Diagram

**Table 1. Timing Diagram Example Shown** in Figure 5

| POINT/<br>PERIOD | DESCRIPTION                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tO               | 12V V <sub>IN</sub> applied.                                                                                                                                                |

| t1               | The LDO has enough headroom to start up. V <sub>IN</sub> > 2V (typ).                                                                                                        |

| t2               | The internal 1.8V LDO is ready and the MAX16550 logic is fully operational. External bypass capacitors connected to the V <sub>DD</sub> pin are fully charged. 700µs (typ). |

| t3, t4           | SMBus ID resistor reading and V <sub>BST</sub> charging.<br>EN/UVLO signal status is ignored from t3 to t4.<br>150µs (typ).                                                 |

| t4               | EN/UVLO is active. Startup check-up procedures can be started after the EN/UVLO is cleared.                                                                                 |

| t4, t5           | User-programmable startup delay (0 to 20µs).                                                                                                                                |

| t5, t6           | Self-test procedure. C <sub>SS</sub> discharge.                                                                                                                             |

| t6, t7           | V <sub>OUT</sub> ramp (1ms–30ms).                                                                                                                                           |

| t7               | Power-good (PWRGD) output asserted. 6ms (typ).                                                                                                                              |

| t7+              | PWRGD is high, normal operation starts.                                                                                                                                     |

#### SMBus ID Resistor Out of Range

After  $V_{DD}$  UVLO is cleared, the SMBus ID programming resistor is read. If it is out of range, a latching fault is tripped. This fault can be cleared by EN/UVLO or  $V_{IN}$  toggling or restarting through the OPERATIONS command. The latter may mean pulling EN/UVLO above the threshold and then low after the fault is detected to reset the fault latch. The value is read again when EN/UVLO goes high for the second time.

#### V<sub>BOOST</sub>, V<sub>GS</sub> UVLO

$V_{BOOST}$  UVLO is checked when EN/UVLO is above the enable threshold and remains active while the device is enabled. If  $V_{BOOST}$  UVLO is tripped before the FET is turned on, the latching fault can still be reset by EN/UVLO or  $V_{IN}$  toggling or restarting through the OPERATIONS command. The gate-drive ( $V_{GS}$ ) UVLO protection has 10 $\mu$ s internal deglitching filtering, which prevents false tripping due to output-voltage overshoot if a large, fast unloading transient is present. An external capacitance can be placed between the  $V_{OUT}$  and  $V_{SS}$  pins for filtering.  $V_{BOOST}$  and  $V_{GS}$  UVLO are latching faults, which result in the pass FET being latched off and FAULT asserted

low. V<sub>GS</sub> UVLO is masked for 100ms during startup to avoid tripping a latching fault.

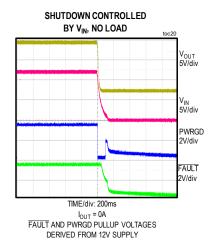

### VIN UVLO

The  $V_{\text{IN}}$  UVLO is fed through a resistor-divider to the EN/UVLO pin and therefore provides a programmable threshold on the 12V input rail. The EN/UVLO pin includes hysteresis and if the pin falls below the programmed value during operation, the device turns the integrated FET off and PWRGD is deasserted. The integrated FET is turned on again if the positive threshold is exceeded and performs self-test and soft-start for each cycle.  $V_{\text{IN}}$  UVLO warning is also provided through the PMBus.

#### **Overcurrent Detection**

The MAX16550 actively monitors load current on the 12V power bus load at all times, including startup. Startup OCP is active during startup until the power-good (PWRGD) flag is set. Startup OCP threshold is 8A by default and has much faster reaction time. If, at any time during startup, load current rises above the startup threshold, the integrated pass FET turns off within 10µs and the FAULT pin is asserted low. This is a latching fault.

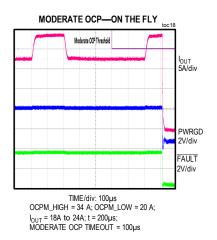

The MAX16550 provides three levels of overcurrent protection during normal operation (after the startup procedure is complete and the PWRGD flag is set high). The "moderate" OCP threshold is set using an analog external resistor and is therefore programmable over a wide continuous range. This OCP allows a higher current to be sustained for a period less than a programmable timeout period without shutting down the device to allow for short surges that pose no threat to the device and are normal operating conditions. If the load current on the 12V power bus exceeds the moderate OCP threshold for the entire timeout period, but its magnitude is less than a programmable severe overcurrent threshold (Table 3), the integrated pass FET switches off at the end of the timeout period and the FAULT pin is asserted low to indicate a moderate OCP fault condition. Restarting the system requires EN/UVLO or V<sub>IN</sub> toggling or restarting through the OPERATIONS command. Moderate OCP timeout is user programmable through SMBus, with four different values.

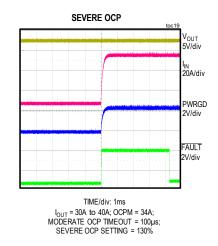

The second level of OCP protection is a "severe OCP." Severe OCP threshold is programmed relative to moderate OCP threshold using PMBus. If at any time the load current exceeds the severe OCP threshold, the MAX16550 turns the integrated pass FET off in less than  $5\mu$ s, and asserts the FAULT pin low. Severe overcurrent protection is a latching fault.

The MAX16550 features a third level of protection against severe overload faults, called "safe OCP," with 60A internally fixed threshold. It assures that the integrated pass FET is protected from exceeding its safe operating condition at all times. If at any time the load current on the 12V power bus exceeds the safe OCP threshold, the MAX16550 turns the pass FET off within 250ns and asserts the FAULT pin low. The severe OCP threshold should be set to a value less than the safe OCP threshold.

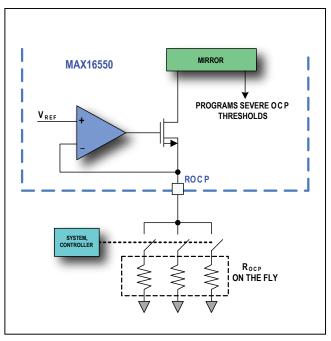

The MAX16550 supports on-the-fly moderate OCP threshold changes. The concept is shown in <u>Figure 4</u>. If the resistance seen by the ROCP pin is changed during the MAX16550 operation, the MAX16550 adjusts the moderate OCP threshold to match the value selected by the external resistive network.

#### **Overvoltage Protection**

The ICs includes  $V_{\text{IN}}$  overvoltage protection to protect the system from an overvoltage event that could harm the downstream circuitry. Overvoltage protection is disabled by default and can be enabled and programmed through PMBus. The input voltage is constantly monitored, and if at any time it rises above the PMBus programmed threshold, the pass FET is latched off,  $\overline{\text{FAULT}}$  asserted low, and a fault reported. This is a latching fault.

### **Wrong ROCP Protection**

The ICs are protected against out-of-range ROCP values. Protection is enabled at all operating conditions, including startup. Wrong ROCP is considered a severe, latching fault, so if at any time the ROCP value is detected out of the permitted range, the ICs latch the integrated FET off, and assert the  $\overline{\text{FAULT}}$  pin low. An EN/UVLO or  $V_{\text{IN}}$  toggling or a restart through the OPERATIONS command must be performed to clear the fault and restart the ICs. If ROCP is changed during operation by the system (see  $\overline{\text{Figure 4}}$ ), the design must be such that ROCP is within range at all times.

#### **Overtemperature Protection**

The ICs include protection against overtemperature conditions. If the junction temperature exceeds the programmable threshold, the IC latches the integrated FET off and asserts the FAULT output low. To re-enable the IC, the following options are available:

- Toggling EN/UVLO or V<sub>IN</sub>

- Restarting through the OPERATIONS command

The overtemperature threshold is user programmable through the PMBus.

Figure 4. On-The-Fly Analog Programmable Moderate OCP Threshold (MAX16550)

### **FAULT** Fault Reporting

The ICs provide a dedicated pin ( $\overline{\text{FAULT}}$ ) for fault reporting. If at any time a latching fault is detected, the  $\overline{\text{FAULT}}$  pin is immediately latched low. An EN/UVLO or V<sub>IN</sub> toggling or restart through the OPERATIONS command is required to reset the ICs after a latching-fault detection.

### Fault Input and FAULT Pullup

The FAULT pin is a bidirectional open-drain pin that can be used for fault communication from external circuitry to the ICs. To communicate a fault to the ICs, the external circuitry must pull the FAULT pin low. If FAULT is externally pulled low, the ICs treat it as a latching fault; therefore, the pullup voltage source must be considered to ensure the rail is operational and pulled high before the ICs' startup cycle.

These are the options for the pullup rail:

- MAX16550 V<sub>DD</sub>: 1.8V internal LDO rail. This rail is limited to 1.8V, so the external system has to be compliant with that rail.

- System 3.3V or 5V Rail: FAULT is 5V compliant; therefore, an external higher voltage rail can be used for pullup. This rail has to be stable when the ICs are initiating their startup procedure. If it is not, a potential false-fault communication may occur.

### Power-Good (PWRGD) Output

The ICs provide a dedicated pin for power-good reporting (PWRGD). PWRGD is asserted high after startup, when the output node is charged above the programmed PWRGD threshold and the FET is fully enhanced and operating in its resistive region. In all the other conditions, the PWRGD pin is deasserted low.

PWRGD is an open-drain pin; thus, an external pullup resistor connected to the pullup supply rail is needed. Different options are available for the pullup rail:

- MAX16550 V<sub>DD</sub>: 1.8V internal LDO rail. This rail is limited to1.8V, so the external system has to be compliant with that rail.

- System 3.3V or 5V Rail:. PWRGD is 5V compliant; therefore, an external higher voltage rail can be used for pullup.

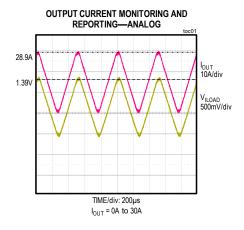

#### **Analog Load Current Signal Output**

The ICs include an output pin (ILOAD) that allows the user to monitor the load current through the ICs. The current sourced by the ILOAD pin is proportional to the current through the device with the ratio shown in the *Electrical Characteristics* table. A properly sized resistor between the ILOAD pin and GND should be added. The ICs report zero current on the ILOAD pin during soft-start, and start reporting load current once the pass FET VGS is above its UVLO threshold (i.e., the pass FET is in its resistive region).

### PMBus/SMBus Reporting and Warning

The ICs provide PMBus-compliant digital telemetry through the PMBus, as shown in <u>Table 4</u>. The ICs include a digital multiply function that provides a reading for input power and input energy. For average values, the sample size is programmable. Peak values for input/output

**Table 2. Faults Detected and Actions**

| PARAMETER                 | DESCRIPTION                                           | FAULT<br>ASSERTED | LATCHING |

|---------------------------|-------------------------------------------------------|-------------------|----------|

| V <sub>DD</sub> UVLO      | Internal V <sub>DD</sub> LDO UVLO                     | N/A*              | N/A*     |

| V <sub>BOOST</sub> UVLO   | UVLO for V <sub>BOOST</sub> voltage                   | Yes               | Yes      |

| V <sub>GS</sub> UVLO      | UVLO for V <sub>GS</sub> voltage                      | Yes               | Yes      |

| V <sub>IN</sub> UVLO      | EN/UVLO pin below threshold                           | No                | No       |

| R <sub>OCP</sub>          | R <sub>OCP</sub> detected as being out of valid range | Yes               | Yes      |

| R_SMBus_ID                | SMBus_ID resistor detected as being out of range      | Yes               | Yes      |

| C <sub>SS</sub> Discharge | Soft-start capacitor discharge failed                 | Yes               | Yes      |

| FET Short                 | Pass FET short detected during startup self-check     | Yes               | Yes      |

| Startup OCP               | Startup overcurrent fault detected                    | Yes               | Yes      |

| Severe OCP                | Severe overcurrent fault detected                     | Yes               | Yes      |

| Safe OCP                  | Safe overcurrent fault detected                       | Yes               | Yes      |

| Power Fault               | Power fault detected                                  | Yes               | Yes      |

| OTP                       | Overtemperature-fault threshold exceeded              | Yes               | Yes      |

| V <sub>IN</sub> OVP       | V <sub>IN</sub> overvoltage detected                  | Yes               | Yes      |

**Note 1:** If  $V_{BST}$ \_UVLO fault occurs before startup,  $\overline{FAULT}$  is not reported and status registers are not updated.

**Note 2:** V<sub>IN</sub> \_UVLO clears FAULT and the latching event.

Table 3. Requirements for PWRGD Assertion

| PARAMETER        | CONDITION                                                                                  |

|------------------|--------------------------------------------------------------------------------------------|

| V <sub>OUT</sub> | V <sub>OUT</sub> > PWRGD Threshold                                                         |

| V <sub>IN</sub>  | V <sub>IN</sub> > V <sub>IN_UVLO</sub>                                                     |

| Self-Check       | MOSFET (V <sub>IN</sub> to V <sub>OUT</sub> ) short not detected during startup.           |

| V <sub>GS</sub>  | FET on and in triode region. 5ms delay before PWRGD assertion after this condition is met. |

### Table 4. PMBus/SMBus Reporting

| PARAMETER             | CONDITION                                     |

|-----------------------|-----------------------------------------------|

| V <sub>IN</sub>       | Input voltage (PMBus compliant)               |

| lout                  | Output current (PMBus compliant)              |

| P <sub>IN</sub>       | Input power (PMBus compliant)                 |

| E <sub>IN</sub>       | Input energy (PMBus compliant)                |

| Temperature           | MAX16550 chip temperature (PMBus compliant)   |

| Peak V <sub>IN</sub>  | Peak value of input voltage (direct reading)  |

| Peak I <sub>OUT</sub> | Peak value of output current (direct reading) |

| Peak P <sub>IN</sub>  | Peak value of input power (direct reading)    |

| Peak Temperature      | Peak value of IC temperature (direct reading) |

| Peak V <sub>OUT</sub> | Peak value of output voltage (direct reading) |

voltage, output current, input power, and temperature are stored in dedicated manufacturer-specific registers. The ICs also provide warning functions based on programmable warning thresholds, as specified in the PMBus specification. The sample size for warning flags is also programmable.

### Configuration

The ICs are configured using both analog programming resistors and also through the PMBus. See  $\underline{\text{Table 5}}$  for programmable parameters.

#### Reference OCP Threshold

The reference OCP threshold is externally programmable through a resistor connected to the ROCP pin. This threshold is used as reference for startup and severe OCP thresholds. The reference OCP threshold is programmed as shown in Equations 1 and 2 (see the *Electrical Characteristics* table for  $V_{OCPM}$  and  $G_{OCP}$ ).

#### Equation 1:

$$I_{OCP\_REF} = \frac{V_{OCPM}}{ROCP} \times GOCP$$

where:

I<sub>OCP\_REF</sub> = Reference overcurrent-protection threshold (A) V<sub>OCPM</sub> = Overcurrent-protection reference voltage shown in the *Electrical Characteristics* table (V)

GOCP = Overcurrent-protection gain shown in the *Electrical Characteristics* table ( $\mu$ A/A)

$R_{OCP}$  = Value of overcurrent-protection programming resistor ( $\Omega$ )

#### **Equation 2:**

$$R_{OCP} = \frac{V_{OCPM}}{I_{OCP REF}} \times GOCP$$

where:

I<sub>OCP\_REF</sub> = Reference overcurrent-protection threshold (A)

V<sub>OCPM</sub> = Overcurrent-protection reference voltage shown

in the *Electrical Characteristics* table (V)

GOCP = Overcurrent-protection gain shown in the *Electrical Characteristics* table (A/A).

$R_{OCP}$  = Value of overcurrent-protection programming resistor ( $\Omega$ )

#### Design Example (MAX16550):

To set moderate OCP to 35A nominal, using Equation 2:

$$R_{OCP} = \frac{0.8 \text{ V}}{35 \text{ A}} \times (4 \times 10^6)$$

$$= 91.5 \text{ k}\Omega$$

#### Startup OCP Threshold

PMBus register DDh is used to set startup OCP threshold. See Table 14 for Reg DDh settings.

### **Design Example:**

To set Startup OCP to 4A, write 10b to bits Reg\_DDh[5:4].

**Table 5. MAX16550 Programmability**

| PARAMETER                                                                    | PROGRAMMABILITY<br>TYPE | COMPONENT                                 | CONDITION |

|------------------------------------------------------------------------------|-------------------------|-------------------------------------------|-----------|

| Moderate (MAX16550) OCP Threshold (sets moderate and severe OCP)             | Analog                  | ROCP                                      | R_OCP     |

| Soft-Start Ramp Rate                                                         | Analog                  | C <sub>SS</sub>                           | SS        |

| Input UVLO Threshold                                                         | Analog                  | Divider                                   | EN/UVLO   |

| PMBus Address                                                                | Programming Resistor    | SMBus_ID Resistor                         | SMBus_ID  |

| Power Fault Timeout                                                          | Digital                 | PMBus_Reg D0h[6:5]                        | SMB_DATA  |

| Severe OCP Threshold                                                         | Digital                 | PMBus_Reg D0h[7]                          | SMB_DATA  |

| Startup Delay                                                                | Digital                 | PMBus_Reg D0h[12:11]                      | SMB_DATA  |

| Input OVP Threshold (OVP feature can be enabled/disabled)                    | Digital                 | PMBus_Reg D0h[3:2]                        | SMB_DATA  |

| Output PWRGD Threshold (sets V <sub>OUT</sub> UVLO and self-test thresholds) | Digital                 | PMBus_Reg D0h[9:8]                        | SMB_DATA  |

| Self-Check Threshold                                                         | Digital                 | PMBus_Reg D0h[9:8]                        | SMB_DATA  |

| Overtemperature Warning and Fault Thresholds                                 | Digital                 | PMBus_Reg 51h,<br>PMBus_Reg 4Fh           | SMB_DATA  |

| Input Overpower Warning Threshold and Fault Thresholds                       | Digital                 | PMBus_Reg 6Bh,<br>PMBus_Reg F5h           | SMB_DATA  |

| Reporting and Warning Averaging Sample Size                                  | Digital                 | PMBus_Reg DDh[3:0],<br>PMBus_Reg D0h[1:0] | SMB_DATA  |

| V <sub>IN</sub> Undervoltage Warning and Fault Thresholds                    | Digital                 | PMBus_Reg 58h,<br>PMBus_Reg 59h           | SMB_DATA  |

| Overcurrent Warning                                                          | Digital                 | PMBus_Reg 4Ah                             | SMB_DATA  |

| V <sub>OUT</sub> Undervoltage Warning Threshold                              | Digital                 | PMBus_Reg 43h                             | SMB_DATA  |

| ILOAD Voltage Gain                                                           | Analog                  | ILOAD Resistor                            | ILOAD     |

### MAX16550

## Integrated Protection IC on 12V Bus with an Integrated MOSFET, Lossless Current Sensing, and PMBus Interface

### Soft-Start Capacitor (CSS)

During startup. the pass FET device is operated as a source follower. Soft-start capacitor CSS is connected between the MOSFET's gate and ground and is charged from a fixed current source. The external C<sub>SS</sub> capacitor therefore charges linearly and this produces a linear monotonic ramp for V<sub>OUT</sub>. The ramp rate is programmable by selecting the appropriate value for CSS.

The ramp rate for the voltage across C<sub>SS</sub> and V<sub>OUT</sub> is given by Equation 5.

#### Equation 5:

$$\frac{dV}{dt} = \frac{i_{SS}}{C_{SS}}$$

where:

dV/dt = Voltage ramp rate of V<sub>OUT</sub> (V/µs)

i<sub>SS</sub> = Soft-start current source (mA)

C<sub>SS</sub> = External C<sub>SS</sub> capacitor value (nF)

Assuming V<sub>IN</sub> = 12V, Equation 5 can be used to derive the soft-start time given by Equation 6.

#### Equation 6:

$$t_{SS} = \frac{12 \, V \times C_{SS}}{i_{SS}}$$

where:

$t_{SS}$  = Ramp duration ( $\mu$ s)

iss = Soft-start current (mA)

C<sub>SS</sub> = External soft-start capacitor value (nF)

Assuming the load inrush current is due to the input capacitance only, the load current is given by Equations 7 and 8.

#### Equation 7:

$$I_{IN} = I_{OUT} = C_{OUT} \times \frac{dV}{dt}$$

where:

I<sub>OUT</sub> = Load inrush current (A)

$C_{OUT}$  = Load capacitance ( $\mu F$ )

#### **Equation 8:**

$$I_{IN} = I_{OUT} = \frac{C_{OUT} \times i_{SS}}{C_{SS}}$$

where:

I<sub>OUT</sub> = Load inrush current(A)

$C_{OUT}$  = Load capacitance ( $\mu F$ )

C<sub>SS</sub> = External soft-start capacitor value (nF)

iss = Soft-start current (mA)

Therefore, the soft-start capacitor can be selected based on the design value of inrush current using Equation 9.

#### Equation 9:

$$C_{SS} = \frac{C_{OUT} \times i_{SS}}{I_{INRUSH}}$$

where:

I<sub>INRUSH</sub> = Desired maximum inrush current due to C<sub>LOAD</sub> (A)

C<sub>OUT</sub> = Load capacitance (mF)

C<sub>SS</sub> = External soft-start capacitor value (nF)

i<sub>SS</sub> = MAX16550 soft-start current (μA)

In order to achieve optimal low-loss operation of the pass FET, the ICs monitor the value of the pass FET V<sub>GS</sub>. The V<sub>GS</sub> UVLO is enabled approximately 100ms (according to the *Electrical Characteristics* table) after startup initiation. This places an upper limit on C<sub>SS</sub> and t<sub>SS</sub>.

Note that if load unloading transients with di/dt > 2.5A/ ms large enough to cause output-voltage transients > ~100mV, an additional capacitor between SS and VOUT is recommended to ensure the pass FET VGS remains above its UVLO threshold. This capacitor has no noticeable effect on soft-start ramp time as the differential voltage from VOLIT to SS remains approximately constant in soft-start.

#### **Design Example:**

Assume a maximum design value for inrush current of 10A, and a load capacitance of 2mF.

$$C_{SS} = \frac{(2mF) x (30 \mu A)}{10 A}$$

= 6nF minimum (to meet inrush maximum)

Use Equation 6 to show that corresponding tss in this example is 2.4ms, which is well below the 100ms limit.

### Input UVLO

The input UVLO is set using a resistor-divider circuit, as shown in Figure 5. The enable threshold,  $V_{\mbox{\footnotesize{IN}}}$  UVLO is given in the Electrical Characteristics table. The corresponding value for the V<sub>IN</sub> rail is given by Equation 10.

#### Equation 10:

$$V_{IN} = \frac{V_{IN\_UVLO}}{K}$$

or

#### **Equation 11:**

$$K = \frac{\left(V_{IN\_UVLO}\right)}{V_{IN}}$$

where:

V<sub>IN</sub> = 12V rail input voltage to enable device (V)

V<sub>IN UVLO</sub> = EN/UVLO threshold (V)

K = Resistor-divider rato, R2/(R1 + R2)

#### **Design Example:**

To guarantee system startup at 10.8V using Equation 11.

$$K = \frac{1.0V}{10.8V}$$

$$= 0.926$$

$$set R2 = 10k\Omega$$

$$R1 = 98k\Omega$$

#### **PMBus Address Programming**

The PMBus address is programmed to one of 16 values using the external resistor, as shown in Table 6.

Figure 5. Programming Resistors for Input UVLO

Table 6. PMBus Address Programming **Resistor Values**

| VALUE | R_SMBUS_ID (kΩ) | SMBus ID |  |  |

|-------|-----------------|----------|--|--|

| 0     | 1.78            | 40h      |  |  |

| 1     | 2.37            | 41h      |  |  |

| 2     | 3.16            | 42h      |  |  |

| 3     | 4.22            | 43h      |  |  |

| 4     | 5.62            | 44h      |  |  |

| 5     | 7.5             | 45h      |  |  |

| 6     | 9.76            | 46h      |  |  |

| 7     | 13              | 47h      |  |  |

| 8     | 17.4            | 10h      |  |  |