#### MAX17105

## 8-String WLED Driver with Integrated Step-Up Regulator and SMBus/PWM Dimming Capability

### **General Description**

The MAX17105 is a high-efficiency driver for white-light-emitting diodes (WLEDs). It is designed for large liquid-crystal displays (LCDs) that employ an array of LEDs as the light source. An internal switch-current mode step-up controller drives the LED array, which can be configured for up to 8 strings in parallel and 10 LEDs per string. Each string is terminated with ballast that achieves ±2% current regulation accuracy, ensuring even LED brightness. The MAX17105 has a wide input voltage range from 6V to 28V, and provides adjustable 0 to 30mA full-scale LED current.

The MAX17105 can internally generate a digitally adjusted pulse-width modulation (DPWM) signal for accurate WLED dimming control. The DPWM frequency is resistor programmable, while DPWM duty cycle is controlled directly from an external PWM signal or through a control word through the MAX17105's SMBus interface. This DPWM control provides a dimming range with 8-bit resolution and supports Intel display power-saving technology (DPST) to maximize battery life. The MAX17105 also has direct PWM control mode, in which the PWMI directly controls the LED current turn on/off and the SMBus interface is disabled.

The MAX17105 has multiple features to protect the controller from fault conditions. Separate feedback loops limit the output voltage under any circumstance, ensuring safe operation. Once an open string is detected, the string is disabled while other strings operate normally. The MAX17105 also features short LED detection. The shorted strings are also disabled. The controller features cycle-by-cycle current limit to provide constant operation and soft-start capability. If the MAX17105 is in currentlimit condition, the step-up regulator is latched off after an internal timer expires. A thermal-shutdown circuit provides another level of protection. When the input overcurrentlimit fault, thermal shutdown, or output-voltage short condition happens, the input p-channel MOSFET is turned off and the step-up regulator output is isolated from the input supply.

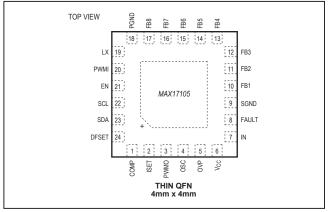

The MAX17105 is available in a thermally enhanced, 24-pin, 4mm x 4mm, thin QFN package with exposed pad.

#### **Applications**

- Notebook, Subnotebook, and Tablet Computer Displays

- Handy Terminals

#### **Features**

- 6V to 28V Input Supply Voltage

- Up to Eight Parallel-String Multiple Series Connected LFDs

- 500kHz-to-2MHz Adjustable Switching Frequency

- 0.15Ω Internal HV Power MOSFET (45V max)

- Low-String Feedback Voltage: 500mV at 20mA LED current

- Full-Scale LED Current Adjustable from 0mA to 30mA

- ±2% Current Regulation Accuracy Between Strings

- 100:1 Dimming Ratio at 25kHz Direct PWM Frequency

- 100Hz to 30kHz PWMI Input Range for DPWM Mode and 10kHz ±5% for SMBus Mode

- 100Hz to 5kHz Adjustable DPWM Frequency

- Full-Range Dimming with 8-Bit Resolution

- Open and Short LED Protection

- Output Overvoltage Protection

- Thermal Shutdown

- FAULT Output to Drive p-Channel MOSFET

- Small 24-Pin, 4mm x 4mm, Thin QFN Package

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX17105ETG+ | -40°C to +85°C | 24 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **Pin Configuration**

Simplified Operating Circuit appears at end of data sheet.

<sup>\*</sup>EP = Exposed pad.

Lead Temperature (soldering, 10s) .....+300°C

### **Absolute Maximum Ratings**

| FAULT, IN to SGND0.3V to +30V                           | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|---------------------------------------------------------|-------------------------------------------------------|

| FB_, LX to PGND0.3V to +45V                             | Thin QFN (derate 20.8mW/°C above +70°C)1667mW         |

| PGND to SGND0.3V to +0.3V                               | (single-layer board)                                  |

| V <sub>CC</sub> , EN, PWMI, SDA, SCL to SGND0.3V to +6V | Thin QFN (derate 27.8mW/°C above +70°C)2222mW         |

| COMP, ISET, OSC, OVP,                                   | (multilayer board)                                    |

| PWMO, DFSET to SGND0.3V to (V <sub>CC</sub> + 0.3V)     | Operating Temperature Range40°C to +85°C              |

| LX Switch Maximum Continuous RMS Current1.6A            | Junction Temperature+150°C                            |

|                                                         | Storage Temperature Range65°C to +150°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $C_{COMP}$  = 33nF,  $R_{COMP}$  = 1k $\Omega$ ,  $R_{ISET}$  = 50k $\Omega$ ,  $R_{OSC}$  = 100k $\Omega$ ,  $R_{DFSET}$  = 250k $\Omega$ , PWMI = SGND,  $C_{PWMO}$  = 1 $\mu$ F,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                       | CONDITIONS                                                                     |                                               | MIN         | TYP          | MAX  | UNITS |

|---------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------|-------------|--------------|------|-------|

| SUPPLY                          |                                                                                |                                               |             |              |      |       |

|                                 | V <sub>CC</sub> = open, EN = high                                              |                                               | 5.5         |              | 28   |       |

| IN Input Voltage Range (Note 1) | EN = SGND, SMBus mode                                                          | All functions available                       | 6.3         |              | 28   | \ \ \ |

|                                 | (Note 5)                                                                       | SMBus interface only                          | 3.9         | 4.0          |      |       |

| IN Input Voltage UVLO Threshold | Rising edge, hysteresis = 150                                                  | )mV                                           | 5.9         | 6.05         | 6.2  | V     |

| (SMBus Mode Only) (Note 4)      | Falling edge, hysteresis = 15                                                  | 0mV                                           | 5.75        | 5.9          | 6.05 | v     |

|                                 | MAX17105 is enabled at min SMBus mode and no-load, V                           | _                                             |             | 2.0          | 3.0  | mA    |

| IN Quiescent Current            | MAX17105 is enabled in SMBus mode and is under IN UVLO, V <sub>IN</sub> = 5.5V |                                               |             | 0.7          | 1.1  | mA    |

|                                 | MAX17105 is disabled                                                           |                                               |             | 30           | 60   | μA    |

| V <sub>CC</sub> Output Voltage  | MAX17105 is enabled, 6V < 10mA                                                 | V <sub>IN</sub> < 28V, 0 < I <sub>VCC</sub> < | 4.7 5.0 5.3 |              | V    |       |

|                                 | MAX17105 is disabled, V <sub>IN</sub> =                                        | 12V                                           | 3.7         | 3.7 4.6 4.95 |      |       |

| V <sub>CC</sub> Current Limit   | V <sub>CC</sub> is forced to 4.5V                                              |                                               | 15          | 40           | 70   | mA    |

| V <sub>CC</sub> UVLO Threshold  | Rising edge, typical hysteresis = 85mV                                         |                                               | 4.00        | 4.3          | 4.45 | V     |

| STEP-UP REGULATOR               |                                                                                |                                               |             |              |      |       |

| LX On-Resistance                | 100mA from LX to PGND                                                          |                                               |             | 0.15         | 0.3  | Ω     |

| LX Leakage Current              | 40V on LX, T <sub>A</sub> = +25°C                                              |                                               |             |              | 1    | μA    |

|                                 | $R_{OSC} = 50k\Omega$                                                          |                                               | 1.7         | 2.0          | 2.3  |       |

| Operating Frequency             | $R_{OSC} = 100k\Omega$                                                         |                                               | 0.9         | 1.0          | 1.1  | MHz   |

|                                 | $R_{OSC}$ = 200k $\Omega$                                                      |                                               | 0.4         | 0.5          | 0.6  |       |

| Minimum On-Time                 | (Note 1)                                                                       |                                               |             | 50           |      | ns    |

| Maximum Duty Cycle              | At f <sub>SW</sub> = 1MHz                                                      | _                                             | 93          | 95           | 97   | %     |

| Minimum Off-Time                |                                                                                |                                               |             | 50           |      | ns    |

## **Electrical Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $C_{COMP}$  = 33nF,  $R_{COMP}$  = 1k $\Omega$ ,  $R_{ISET}$  = 50k $\Omega$ ,  $R_{OSC}$  = 100k $\Omega$ ,  $R_{DFSET}$  = 250k $\Omega$ , PWMI = SGND,  $C_{PWMO}$  = 1 $\mu$ F,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                          | CONDITIONS                                      | MIN   | TYP  | MAX   | UNITS |

|------------------------------------|-------------------------------------------------|-------|------|-------|-------|

| LX Current Limit                   | Duty cycle = 75% (Note 1)                       | 2.4   | 2.9  | 3.4   | Α     |

| CONTROL INPUT                      |                                                 |       |      |       |       |

| Logic-Input High Level             | SDA, SCL, PWMI, EN                              | 2.1   |      |       | V     |

| Logic-Input Low Level              | SDA, SCL, PWMI, EN                              |       |      | 0.8   | V     |

| INPUT LEAKAGE                      |                                                 |       |      |       |       |

| PWMI Leakage Current               | T <sub>A</sub> = +25°C                          | -0.1  |      | +0.1  | μA    |

| Logic Input Bias Current           | T <sub>A</sub> = +25°C, EN, SDA, SCL            | -1    |      | +1    | μA    |

| OVP Leakage Current                | TA = +25°C                                      | -0.1  |      | +0.1  | μA    |

| SDA Output-Low Sink Current        | V <sub>SDA</sub> = 0.4V                         | 4     |      |       | mA    |

| LED CURRENT                        |                                                 | ·     |      |       |       |

| Full-Scale FB_ Output Current-     | PWM-only dimming mode                           | 15    |      | 30    | A     |

| Adjustable Range (Note 4)          | SMBus-enabled dimming modes                     | 15    |      | 25    | mA mA |

|                                    | R <sub>ISET</sub> = 33.3kΩ                      | 29.1  | 30.0 | 30.9  |       |

| Full Cools ED. Outsut Comment      | R <sub>ISET</sub> = 50.0kΩ                      | 19.4  | 20.0 | 20.6  | - mA  |

| Full-Scale FB_ Output Current      | R <sub>ISET</sub> = 66.6kΩ                      | 14.45 | 15.0 | 15.55 |       |

|                                    | V <sub>ISET</sub> < 0.4V                        | 0.2   | 0.3  | 0.4   |       |

| ISET Output Voltage                |                                                 | 1.1   | 1.2  | 1.3   | V     |

|                                    | I <sub>FB</sub> _ = 30mA                        | -2.0  |      | +2.0  | %     |

| Current Regulation Between Strings | I <sub>FB</sub> _ = 20mA                        | -2.0  |      | +2.0  |       |

| Striigs                            | I <sub>FB</sub> _ = 15mA                        | -2.0  |      | +2.0  |       |

|                                    | I <sub>FB</sub> _ = 30mA                        |       |      | 770   |       |

| Minimum FB_ Regulation Voltage     | I <sub>FB</sub> _ = 20mA                        |       | 480  |       | mV    |

| Voltage                            | I <sub>FB</sub> _ = 15mA                        |       | 450  |       |       |

| FB_ On-Resistance                  | V <sub>FB</sub> _ = 50mV                        |       | 15   | 26    | Ω     |

| FB_ Leakage Current                | V <sub>FB</sub> _ = 40V, T <sub>A</sub> = +25°C |       | 0.1  | 5     | μA    |

| FB_ On-Time                        |                                                 | 400   |      |       | ns    |

| FAULT PROTECTION                   |                                                 |       |      |       |       |

| OVP Threshold Voltage              | Rising edge, hysteresis = 60mV                  | 1.15  | 1.25 | 1.35  | V     |

| OVP Shutdown Voltage               | Rising edge                                     |       | 1.35 |       | V     |

| OVP Global Fail                    |                                                 | 48    |      | 120   | mV    |

| FB_ UVLO Threshold                 | FB open                                         | 140   | 220  | 300   | mV    |

| FB_ Overvoltage Threshold          |                                                 | 7.4   | 8    | 8.6   | V     |

| FB_ Check LED Source Current       |                                                 | 0.4   |      |       | mA    |

| FB_ Check LED Time                 |                                                 |       | 1    |       | ms    |

## **Electrical Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $C_{COMP}$  = 33nF,  $R_{COMP}$  = 1k $\Omega$ ,  $R_{ISET}$  = 50k $\Omega$ ,  $R_{OSC}$  = 100k $\Omega$ ,  $R_{DFSET}$  = 250k $\Omega$ , PWMI = SGND,  $C_{PWMO}$  = 1 $\mu$ F,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                  | CONDITIONS                                                         | MIN                   | TYP                    | MAX                      | UNITS |

|--------------------------------------------|--------------------------------------------------------------------|-----------------------|------------------------|--------------------------|-------|

| FB_ Overvoltage Fault Timer                |                                                                    | 88                    | 128                    | 168                      | μs    |

| Thermal-Shutdown Threshold                 | (Note 1)                                                           |                       | +150                   |                          | °C    |

| Overcurrent FAULT Shutdown Timer           | I <sub>PEAK</sub> > 2.9A at duty = 75%                             | 72                    | 128                    | 168                      | μs    |

| FAULT High-Level Leakage Current           | V <sub>FAULT</sub> = V <sub>IN</sub> = 28V, T <sub>A</sub> = +25°C |                       |                        | 1                        | μA    |

| FAULT Low-Level Clamp Voltage              |                                                                    | V <sub>IN</sub> – 5.5 | V <sub>IN</sub> -<br>5 | V <sub>IN</sub> –<br>4.5 | V     |

| FAULT Charge Current                       |                                                                    | 45                    |                        | 65                       | μΑ    |

| PWM FILTER                                 |                                                                    |                       |                        |                          |       |

| PWM Output Impedance                       |                                                                    | 20                    | 40                     | 60                       | kΩ    |

|                                            | $R_{DFSET} = 500k\Omega$                                           |                       | 100                    |                          | 1.1-  |

| DDWM Ossillator Fraguescy                  | $R_{DFSET} = 250k\Omega$                                           | 190                   | 200                    | 210                      | Hz    |

| DPWM Oscillator Frequency                  | $R_{DFSET} = 25k\Omega$                                            |                       | 2                      |                          |       |

|                                            | $R_{DFSET} = 10k\Omega$                                            | 4.4                   | 5.0                    | 5.5                      | kHz   |

| DFSET Short-Detection<br>Threshold Voltage |                                                                    |                       | 210                    | 300                      | mV    |

|                                            | $R_{DFSET} = 500k\Omega$                                           |                       | 4.15                   |                          | μΑ    |

| DECET Comment                              | $R_{DFSET} = 250k\Omega$                                           |                       | 7.85                   |                          |       |

| DFSET Source Current                       | $R_{DFSET} = 25k\Omega$                                            |                       | 40                     |                          |       |

|                                            | $R_{DFSET} = 10k\Omega$                                            |                       | 55                     |                          |       |

| DWM Input Fraguency Dange                  | DPST/SMBus mode                                                    | 9.5                   | 10.0                   | 10.5                     | kHz   |

| PWMI Input Frequency Range                 | Direct-PWM mode                                                    | 0.1                   |                        | 30.0                     |       |

|                                            | SMBus mode, PWMI duty cycle = 98%                                  | 97.5                  | 98                     | 98.5                     |       |

| PWMI Brightness Setting                    | SMBus mode, PWMI duty cycle = 50%                                  | 48                    | 50                     | 52                       | %     |

|                                            | SMBus mode, PWMI duty cycle = 0%                                   | 0.2                   | 0.4                    | 0.6                      |       |

| SMBus TIMING SPECIFICATION                 |                                                                    |                       |                        |                          |       |

| SMBus Frequency                            | f <sub>SMB</sub>                                                   | 10                    |                        | 100                      | kHz   |

| Bus Free Time                              | t <sub>BUF</sub>                                                   | 4.7                   |                        |                          | μs    |

| START Condition Hold Time from SCL         | t <sub>HD:STA</sub>                                                | 4                     |                        |                          | μs    |

| START Condition Setup Time from SCL        | tsu:sta                                                            | 4.7                   |                        |                          | μs    |

| STOP Condition Setup Time from SCL         | t <sub>SU:STO</sub>                                                | 4                     |                        |                          | μs    |

| SDA Hold Time from SCL                     | t <sub>HD:DAT</sub>                                                | 300                   |                        |                          | ns    |

| SDA Setup Time from SCL                    | tsu:dat                                                            | 250                   |                        |                          | ns    |

| SCL Low Period                             | t <sub>LOW</sub>                                                   | 4.7                   |                        |                          | μs    |

| SCL High Period                            | thigh                                                              | 4                     |                        |                          | μs    |

#### **Electrical Characteristics**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $C_{COMP}$  = 33nF,  $R_{COMP}$  = 1k $\Omega$ ,  $R_{ISET}$  = 50k $\Omega$ ,  $R_{OSC}$  = 100k $\Omega$ ,  $R_{DFSET}$  = 250k $\Omega$ , PWMI = SGND,  $C_{PWMO}$  = 1 $\mu$ F,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                         | CONDITIONS                                                    |                                      | MIN   | TYP | MAX   | UNITS |  |

|---------------------------------------------------|---------------------------------------------------------------|--------------------------------------|-------|-----|-------|-------|--|

| SUPPLY                                            |                                                               |                                      |       |     |       |       |  |

|                                                   | V <sub>CC</sub> = open, EN = high (Note                       | : 5)                                 | 5.5   |     | 28    |       |  |

| IN Input Voltage Range (Note 1)                   | EN - COND CMD                                                 | All functions available              | 6.3   |     | 28    | V     |  |

|                                                   | EN = SGND, SMBus mode                                         | SMBus interface only                 | 3.9   | 4.0 |       |       |  |

| IN Input Voltage UVLO Threshold (SMBus Mode Only) | Rising edge, hysteresis = 150                                 | )mV                                  | 5.9   |     | 6.2   | V     |  |

| (Note 2)                                          | Falling edge, hysteresis = 150                                | DmV                                  | 5.75  |     | 6.05  | V     |  |

|                                                   | MAX17105 is enabled at mini in SMBus mode and no load,        | •                                    |       |     | 3.0   | mΛ    |  |

| IN Quiescent Current                              | MAX17105 is enabled in SME<br>IN UVLO, V <sub>IN</sub> = 5.5V | Bus mode, and is under               |       |     | 1.1   | mA    |  |

|                                                   | MAX17105 is disabled                                          |                                      |       |     | 60    | μA    |  |

|                                                   | MAX17105 is enabled, 6V < V <sub>IN</sub>                     | N < 28V, 0 < I <sub>VCC</sub> < 10mA | 4.7   |     | 5.3   | .,    |  |

| V <sub>CC</sub> Output Voltage                    | MAX17105 is disabled, V <sub>IN</sub> =                       |                                      | 3.7   |     | 4.95  | V     |  |

| V <sub>CC</sub> Current Limit                     | V <sub>CC</sub> is forced to 4.5V                             |                                      | 15    |     | 70    | mA    |  |

| V <sub>CC</sub> UVLO Threshold                    | Rising edge, typical hysteresi                                | s = 85mV                             | 4.00  |     | 4.45  | V     |  |

| STEP-UP REGULATOR                                 |                                                               |                                      |       |     |       |       |  |

| LX On-Resistance                                  | 100mA from LX to PGND                                         |                                      |       |     | 0.3   | Ω     |  |

|                                                   | $R_{OSC} = 50k\Omega$                                         |                                      | 1.7   |     | 2.3   |       |  |

| Operating Frequency                               | $R_{OSC} = 100k\Omega$                                        |                                      | 0.9   |     | 1.1   | MHz   |  |

|                                                   | $R_{OSC} = 200k\Omega$                                        |                                      | 0.45  |     | 0.6   |       |  |

| Maximum Duty Cycle                                | At f <sub>SW</sub> = 1MHz                                     |                                      | 93    |     | 98    | %     |  |

| LX Current Limit                                  | Duty cycle = 75%                                              |                                      | 2.4   |     | 3.4   | Α     |  |

| CONTROL INPUT                                     |                                                               |                                      |       |     |       |       |  |

| Logic-Input High Level                            | SDA, SCL, PWMI, EN                                            |                                      | 2.1   |     |       | V     |  |

| Logic-Input Low Level                             | SDA, SCL, PWMI, EN                                            |                                      |       |     | 8.0   | V     |  |

| SDA Output-Low Sink Current                       | V <sub>SDA</sub> = 0.4V                                       |                                      | 4     |     |       | mA    |  |

| SDA, SCL Input Bias Current                       | T <sub>A</sub> = +25NC                                        |                                      | -1    |     | +1    | μΑ    |  |

| LED CURRENT                                       |                                                               |                                      |       |     |       |       |  |

| Full-Scale FB_ Output Current                     | PWM only dimming mode                                         |                                      | 15    |     | 30    | mΛ    |  |

| Adjustable Range (Note 3)                         | SMBus-enabled dimming mod                                     | des                                  | 15    |     | 25    | mA    |  |

|                                                   | $R_{ISET}$ = 33.3k $\Omega$                                   |                                      | 28.8  |     | 31.2  |       |  |

| Full Scale ED Output Current                      | $R_{ISET}$ = 50.0k $\Omega$                                   |                                      | 18.9  |     | 21    | mΛ    |  |

| Full-Scale FB_ Output Current                     | $R_{ISET}$ = 66.6k $\Omega$                                   |                                      | 14.25 |     | 15.75 | mA    |  |

|                                                   | V <sub>ISET</sub> < 0.4V                                      |                                      | 0.2   |     | 0.4   |       |  |

| Current Degulation Detuces                        | I <sub>FB</sub> _ = 30mA                                      |                                      | -2.5  |     | +2.5  |       |  |

| Current Regulation Between Strings                | I <sub>FB</sub> _ = 20mA                                      |                                      | -2.5  |     | +2.5  | %     |  |

| Guniga                                            | I <sub>FB</sub> _ = 15mA                                      |                                      | -2.5  |     | +2.5  |       |  |

| Minimum FB_ Regulation Voltage                    | I <sub>FB</sub> _ = 30mA                                      |                                      |       |     | 770   | mV    |  |

| FB_ On-Resistance                                 | V <sub>FB</sub> _ = 50mV                                      |                                      |       |     | 26    | Ω     |  |

| FB_ On-Time                                       |                                                               |                                      | 400   |     |       | ns    |  |

### **Electrical Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $C_{COMP}$  = 33nF,  $R_{COMP}$  = 1k $\Omega$ ,  $R_{ISET}$  = 50k $\Omega$ ,  $R_{OSC}$  = 100k $\Omega$ ,  $R_{DFSET}$  = 250k $\Omega$ , PWMI = SGND,  $C_{PWMO}$  = 1 $\mu$ F,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                  | CONDITIONS                                       | MIN                   | TYP | MAX                      | UNITS |  |

|--------------------------------------------|--------------------------------------------------|-----------------------|-----|--------------------------|-------|--|

| FAULT PROTECTION                           | ,                                                | -1                    |     | ,                        |       |  |

| OVP Threshold Voltage                      | Rising edge, hysteresis = 60mV                   | 1.15                  |     | 1.35                     | V     |  |

| OVP Shutdown Voltage                       | Rising edge (tracks with OVP threshold voltage)  | 1.25                  |     | 1.45                     | V     |  |

| OVP Global Fail                            |                                                  | 48                    |     | 120                      | mV    |  |

| FB_ UVLO Threshold                         | FB open                                          | 140                   |     | 300                      | mV    |  |

| FB_ Overvoltage Threshold                  |                                                  | 7.4                   |     | 8.6                      | V     |  |

| FB_ Check LED Source Current               |                                                  | 0.4                   |     |                          | mA    |  |

| FB_ Overvoltage Fault Timer                |                                                  | 88                    |     | 168                      | μs    |  |

| Overcurrent FAULT Shutdown Timer           | I <sub>PEAK</sub> > 2.9A at duty = 75% (typical) | 72                    |     | 168                      | μs    |  |

| FAULT High-Level Leakage Current           | V <sub>FAULT</sub> = V <sub>IN</sub> = 28V       |                       |     | 1                        | μΑ    |  |

| FAULT Low-Level<br>Clamp Voltage           |                                                  | V <sub>IN</sub> – 5.5 |     | V <sub>IN</sub> –<br>4.5 | V     |  |

| FAULT Charge Current                       |                                                  | 45                    |     | 65                       | μΑ    |  |

| PWM FILTER                                 |                                                  |                       |     |                          |       |  |

| PWM Output Impedance                       |                                                  | 20                    |     | 60                       | kl    |  |

| DDIA/AA Oo cilleter Frequency              | $R_{DFSET} = 250k\Omega$                         | 190                   |     | 210                      | Hz    |  |

| DPWM Oscillator Frequency                  | $R_{DFSET} = 10k\Omega$                          | 4.4                   |     | 5.5                      | kHz   |  |

| DFSET Short-Detection<br>Threshold Voltage |                                                  |                       |     | 300                      | mV    |  |

| DIA/A41 Inc. of Francisco Dance            | DPST/SMBus mode                                  | 9.5                   |     | 10.5                     | Id I= |  |

| PWMI Input Frequency Range                 | Direct-PWM mode                                  | 0.1                   |     | 30.0                     | kHz   |  |

|                                            | SMBus mode, PWMI duty cycle = 98%                | 97.5                  |     | 98.5                     |       |  |

| PWMI Brightness Setting                    | SMBus mode, PWMI duty cycle = 50%                | 48                    |     | 52                       | %     |  |

|                                            | SMBus mode, PWMI duty cycle = 0%                 | 0.2                   |     | 0.6                      |       |  |

| SMBus TIMING SPECIFICATION                 |                                                  |                       |     |                          |       |  |

| SMBus Frequency                            | f <sub>SMB</sub>                                 | 10                    |     | 100                      | kHz   |  |

| Bus Free Time                              | t <sub>BUF</sub>                                 | 4.7                   |     |                          | μs    |  |

| START Condition Hold Time from SCL         | t <sub>HD:STA</sub>                              | 4                     |     |                          | μs    |  |

| START Condition Setup Time from SCL        | t <sub>SU:STA</sub>                              | 4.7                   |     |                          | μs    |  |

| STOP Condition Setup Time from SCL         | tsu:sto                                          | 4                     |     |                          | μs    |  |

| SDA Hold Time from SCL                     | t <sub>HD:DAT</sub>                              | 300                   |     |                          | ns    |  |

| SDA Setup Time from SCL                    | t <sub>SU:DAT</sub>                              | 250                   |     |                          | ns    |  |

| SCL Low Period                             | t <sub>LOW</sub>                                 | 4.7                   |     |                          | μs    |  |

| SCL High Period                            | thigh                                            | 4                     |     |                          | μs    |  |

#### **Electrical Characteristics (continued)**

Circuit of Figure 1.  $V_{IN}$  = 12V,  $C_{COMP}$  = 33nF,  $R_{COMP}$  = 1k $\Omega$ ,  $R_{ISET}$  = 50k $\Omega$ , ROSC = 100k $\Omega$ ,  $R_{DFSET}$  = 250k $\Omega$ , PWMI = SGND,  $C_{PWMO}$  = 1 $\mu$ F,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

- Note 1: Specifications are guaranteed by design, not production tested.

- **Note 2:** Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design, not production tested.

- Note 3: LED full-scale current maximum value is subjected to string number, LED number per string, and LX current limit. In SMBus modes, if the total load is heavier than 8 strings with 10 WLEDs per string at 25mA LED current, upon step-up regulator input V<sub>S</sub> removal, an OC fault may occur, resulting in SMBus status register OV\_CURR and FAULT bits being set to 1 and violating SMBus specifications.

- Note 4: Minimum voltage drop from V<sub>S</sub> to IN pin, including the forward voltage drop of diode DIN1 used in Figure 1, should be no less than 0.8V. If lower forward voltage drop diode is used, upon step-up regulator input VS removal, an OC fault may occur, resulting in SMBus status register OV\_CURR and FAULT bits being set to 1 and violating SMBus specifications.

- Note 5: Dimming modes not to be done after the driver starts up or on-the-fly.

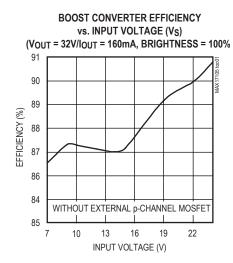

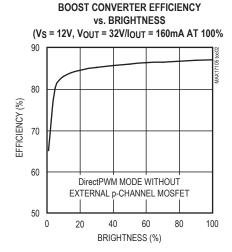

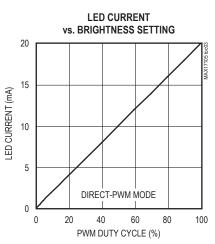

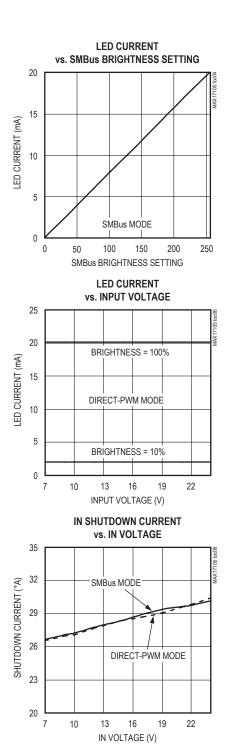

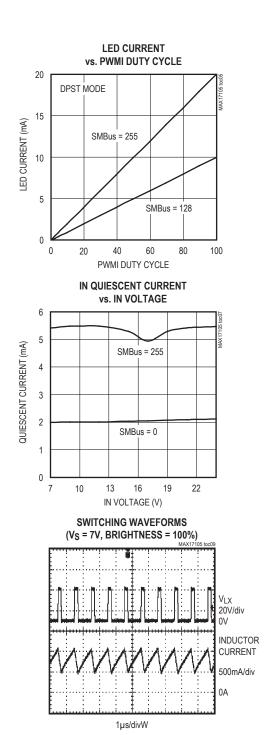

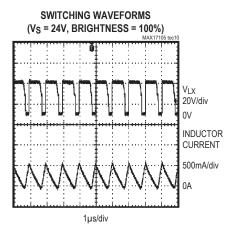

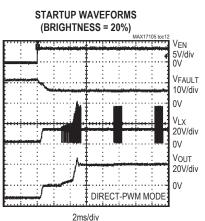

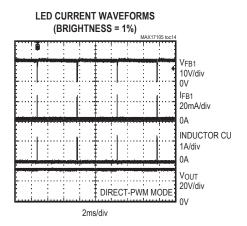

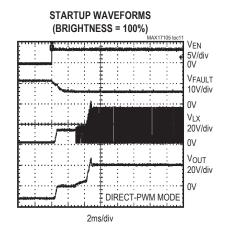

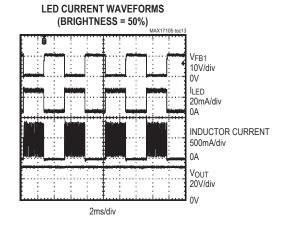

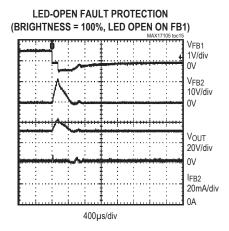

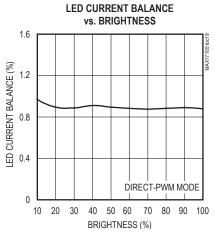

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

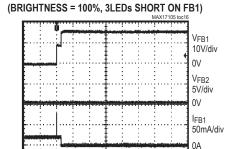

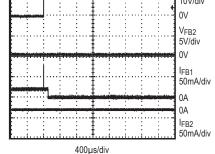

LED-SHORT FAULT PROTECTION

Maxim Integrated | 10 www.maximintegrated.com

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                      |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | COMP  | Step-Up Regulator Compensation Pin. Connect a $0.033\mu F$ ceramic capacitor and $1k\Omega$ resistor from COMP to SGND and an additional 220pF capacitor from COMP to SGND. When the MAX17105 shuts down, COMP is discharged to 0V through an internal $20k\Omega$ resistor.                                  |

| 2   | ISET  | Full-Scale LED Current Adjustment Pin. The resistance from ISET to SGND controls the full-scale current in each LED string:                                                                                                                                                                                   |

| 3   | PWMO  | Filtered PWM Signal Output. Connect a capacitor between PWMO and SGND. The capacitor forms a lowpass filter with an internal $40 \text{k}\Omega$ (typ) resistor to filter the PWM signal into an analog signal whose level represents the duty cycle information of the input PWM signal.                     |

| 4   | OSC   | Oscillator Frequency Adjustment Pin. The resistance from OSC to SGND sets the step-up regulator's oscillator frequency: $fSW = 1 MHz \times 100 k\Omega/ROSC$ The acceptable resistance range is $50 k\Omega < ROSC < 200 k\Omega$ , which corresponds to the switching frequency of $2MHz > fSW > 500 kHz$ . |

| 5   | OVP   | Overvoltage Sense. Connect OVP to the center tap of a resistive voltage-divider from the output of the step-up regulator to ground.                                                                                                                                                                           |

| 6   | Vcc   | 5V Linear-Regulator Output. VCC provides power to the MAX17105. Bypass VCC to SGND with a ceramic capacitor of 1μF or greater.                                                                                                                                                                                |

| 7   | IN    | Power-Supply Input. VIN biases the internal 5V linear regulator that powers the device. Bypass IN to SGND directly at the pin with a 0.1µF ceramic capacitor or greater.                                                                                                                                      |

| 8   | FAULT | External p-Channel MOSFET Gate Drive-Output. External pullup resistor is connected between FAULT and IN when p-channel MOSFET is used. If the p-channel MOSFET is not used, leave FAULT unconnected.                                                                                                          |

| 9   | SGND  | Analog Ground                                                                                                                                                                                                                                                                                                 |

| 10  | FB1   | LED String 1 Cathode Connection. FB1 is the open-drain output of an internal regulator, which controls current through FB1. FB1 can sink up to 30mA. If unused, connect FB1 to SGND.                                                                                                                          |

| 11  | FB2   | LED String 2 Cathode Connection. FB2 is the open-drain output of an internal regulator, which controls current through FB2. FB2 can sink up to 30mA. If unused, connect FB2 to SGND.                                                                                                                          |

| 12  | FB3   | LED String 3 Cathode Connection. FB3 is the open-drain output of an internal regulator, which controls current through FB3. FB3 can sink up to 30mA. If unused, connect FB3 to SGND.                                                                                                                          |

| 13  | FB4   | LED String 4 Cathode Connection. FB4 is the open-drain output of an internal regulator, which controls current through FB4. FB4 can sink up to 30mA. If unused, connect FB4 to SGND.                                                                                                                          |

| 14  | FB5   | LED String 5 Cathode Connection. FB5 is the open-drain output of an internal regulator, which controls current through FB5. FB5 can sink up to 30mA. If unused, connect FB5 to SGND.                                                                                                                          |

| 15  | FB6   | LED String 6 Cathode Connection. FB6 is the open-drain output of an internal regulator, which controls current through FB6. FB6 can sink up to 30mA. If unused, connect FB6 to SGND.                                                                                                                          |

| 16  | FB7   | LED String 7 Cathode Connection. FB7 is the open-drain output of an internal regulator, which controls current through FB7. FB7 can sink up to 30mA. If unused, connect FB7 to SGND.                                                                                                                          |

| 17  | FB8   | LED String 8 Cathode Connection. FB8 is the open-drain output of an internal regulator, which controls current through FB8. FB8 can sink up to 30mA. If unused, connect FB8 to SGND.                                                                                                                          |

## **Pin Description (continued)**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | PGND  | Step-Up Regulator Power Ground                                                                                                                                                                                                                                                                                                                                                      |

| 19  | LX    | Step-Up Regulator Switching Node. Drain of the internal n-channel MOSFET between LX and PGND. Connect the inductor and catch diode here and minimize trace area for lowest EMI.                                                                                                                                                                                                     |

| 20  | PWMI  | PWM Signal Input. This PWM signal is used for brightness control in direct-PWM mode or DPST mode of SMBus mode. In direct-PWM mode, the DPWM duty cycle is equal to the input PWM duty cycle. In DPST mode, the DPWM duty cycle is the input PWM duty cycle multiplied by the SMBus brightness command. PWMI directly controls the LED current source on or off in direct-PWM mode. |

| 21  | EN    | Direct-PWM Mode Enable Pin. When direct-PWM mode is selected through the DFSET pin, the MAX17105 can start up with direct-PWM mode by EN = high.                                                                                                                                                                                                                                    |

| 22  | SCL   | SMBus Serial Clock Input                                                                                                                                                                                                                                                                                                                                                            |

| 23  | SDA   | SMBus Serial Data Input                                                                                                                                                                                                                                                                                                                                                             |

| 24  | DFSET | DPWM Frequency Adjustment Pin. Connect a resistor from DFSET to SGND to set the internal DPWM frequency in SMBus mode. In direct-PWM mode, DFSET pin is connected to SGND:                                                                                                                                                                                                          |

| _   | EP    | Exposed Backside Pad. Solder to the circuit board ground plane with sufficient copper connection to ensure low thermal resistance. See the <i>PCB Layout Guidelines</i> section.                                                                                                                                                                                                    |

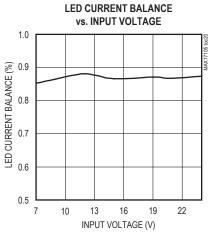

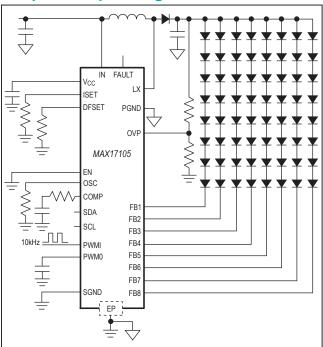

Figure 1. Typical Operating Circuit

### **Table 1. Component List**

| DESIGNATION     | DESCRIPTION                                                               |

|-----------------|---------------------------------------------------------------------------|

| White LED       | Nichia NSSW008C 3.2V (typ), 3.5V (max) at 20mA                            |

| L1              | 10µH, 1.5A, H = 1.2mm<br>TDK VLP6812T-100M1R5                             |

| Q1 (Optional)   | 30V, $65m\Omega$ p-channel MOSFET Si3481DV FDC658AP                       |

| C <sub>IN</sub> | 4.7μF ±10%, 25V X5R ceramic capacitor (1206)<br>Murata GRM319R61E475KA12D |

| C1, C2          | 2.2µF ±20%, 50V X7R ceramic capacitors (1206) Murata GRM31CR71H225K       |

| D1              | 2A, 40V Schottky diode (M-flat)<br>Toshiba CMS11                          |

**Table 2. Component Suppliers**

| SUPPLIER                                                | PHONE        | WEBSITE                     |

|---------------------------------------------------------|--------------|-----------------------------|

| Fairchild<br>Semiconductor                              | 888-522-5372 | www.fairchildsemi.com       |

| Murata                                                  | 770-436-1300 | www.murata-northamerica.com |

| Nichia Corp.                                            | 248-352-6575 | www.nichia.com              |

| TDK Corp.                                               | 847-803-6100 | www.component.tdk.com       |

| Toshiba<br>America<br>Electronic<br>Components,<br>Inc. | 949-623-2900 | www.toshiba.com/taec        |

| Vishay                                                  | 402-563-6866 | www.vishay.com              |

### **Detailed Description**

The MAX17105 typical operating circuit is shown in Figure 1. Table 1 lists some recommended components, and Table 2 lists the contact information of component suppliers.

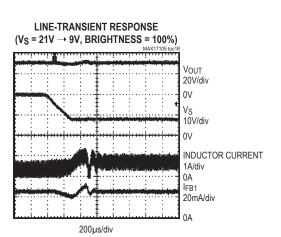

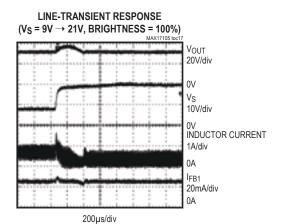

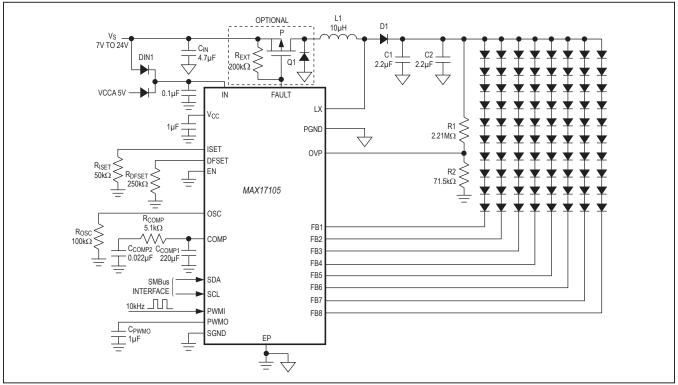

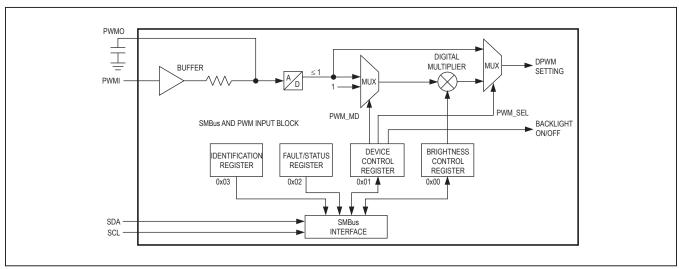

The MAX17105 is a high-efficiency driver for arrays of white LEDs. It contains a fixed-frequency, current-mode PWM step-up controller, a 5V linear regulator, dimming control circuit, SMBus interface, internal power MOSFET, eight regulated current sources, and an external p-channel MOSFET drive circuit. Figure 2 shows the MAX17105 functional

diagram. When enabled, the step-up controller boosts the output voltage to provide sufficient headroom for the current sources to regulate their respective string currents. The MAX17105 features a resistor-adjustable switching frequency (500kHz to 2MHz), which allows trade-offs between external component size and operating efficiency.

Figure 2. Functional Diagram

WLED brightness is controlled by turning the WLEDs on and off with a DPWM signal. The DPWM frequency can be accurately adjusted with a resistor or directly controlled by the PWMI signal. The brightness of the LEDs is proportional to the duty cycle of the DPWM signal, which is controlled externally through either a PWM or 2-wire SMBus-compatible interface, or both. When both interfaces are used at the same time, the product of the PWM duty cycle and SMBus command value is used for the dimming control. This DPWM control provides a dimming range with 8-bit resolution.

The MAX17105 has multiple features to protect the controller from fault conditions. Separate feedback loops limit the output voltage in all circumstances. The MAX17105 checks each FB voltage during the operation. If one or more strings are open, the corresponding FB voltages are pulled below 220mV (typ), and an open-circuit fault is detected. As a result, the respective current sources are disabled. When one or more LEDs are shorted and the FB\_ voltage exceeds 8V, a short fault is detected and the respective current source is disabled. In either LED open or short conditions, the fault strings are disabled while other strings can still operate normally. The controller features cycle-by-cycle current limit to provide consistent operation and soft-start protection. In a current-limit condition, the controller shuts down after a 128µs overcurrent fault timer expires. A thermal-shutdown circuit provides yet another level of protection.

The MAX17105 includes a 5V linear regulator that provides the internal bias and gate driver for the step-up controller.

#### **Fixed-Frequency Step-Up Controller**

The MAX17105's fixed-frequency, current mode, step-up controller automatically chooses the lowest active FB\_ voltage to regulate the feedback voltage. Specifically, the difference between the lowest FB\_ voltage and the current source control signal plus an offset (VSAT) is integrated at the COMP output. The resulting error signal is compared to the external switch current plus slope compensation to determine the switch on-time. As the load changes, the error amplifier sources or sinks current to the COMP output to deliver the required peak inductor current. The slope-compensation signal is added to the current-sense signal in order to improve stability at high duty cycles.

#### Internal 5V Linear Regulator and UVLO

The MAX17105 includes an internal low-dropout (LDO) linear regulator (V $_{CC}$ ). When V $_{IN}$  is higher than 5.5V, this linear regulator generates a 5V supply to power the internal PWM controller, control logic, and MOSFET driver. The V $_{CC}$  voltage drops to 4.5V in standby. If V $_{IN}$  is less than or equal to 5.5V, V $_{CC}$  and IN can be connected together and powered from an external 5V supply. There is a body diode from V $_{CC}$  to IN, so V $_{IN}$  must be greater than V $_{CC}$ . (See Figure 2.)

The MAX17105 includes power-on reset (POR) and undervoltage lockout (UVLO) features. POR resets the fault latch and sets all the SMBus resisters to their POR values. POR occurs when  $V_{CC}$  rises above 2.8V (typ). The controller is disabled until  $V_{CC}$  exceeds the UVLO threshold of 4.3V (typ). The hysteresis on  $V_{CC}$  UVLO is approximately 85mV.

In standby mode, the internal LDO is low-power mode with  $60\mu\text{A}$  (max) input current and regulated at 4.5V (typ). When EN is high in direct-PWM mode or an ENABLE command through the SMBus interface, the internal LDO is enabled and regulated at 5.0V (typ). In addition to  $V_{CC}$  UVLO, the MAX17105 has also implemented an IN UVLO function. This IN UVLO function is not activated in direct-PWM mode. However, when the controller is enabled with SMBus, the IN UVLO feature is enabled. If the IN voltage is below its UVLO threshold, the step-up converter is shut off

The  $V_{CC}$  pin should be bypassed to SGND with a minimum  $1\mu F$  ceramic capacitor.

#### Startup

The MAX17105 has two operating modes: direct-PWM mode and SMBus mode. The two modes are identified by the DFSET pin. At the first enable signal, either EN = high or an SMBus ENABLE command, the DFSET pin sources a current to check whether the DFSET pin is connected to SGND. When the DFSET voltage is lower than 210mV (typ), the MAX17105 is set for direct-PWM mode. Otherwise, the MAX17105 is set for SMBus mode. Once the mode is set, the mode is not cleared until the VCC is lower than the POR voltage. When the MAX17105 is set for SMBus mode, the EN pin signal is ignored and the MAX17105 is woken by the SMBus ENABLE command. When the MAX17105 is set for direct-PWM mode, the SMBus command is ignored and the MAX17105is woken by the EN signal. Table 3 summarizes the operating mode.

**Table 3. Operating Mode**

|                         | EN   | DFSET              | SCL, SDA          |

|-------------------------|------|--------------------|-------------------|

| Direct PWM<br>(Standby) | Low  | SGND               | X                 |

| Direct PWM<br>(Startup) | High | SGND               | ×                 |

| SMBus<br>(Standby)      | Х    | R <sub>DFSET</sub> | CLOCK             |

| SMBus<br>(Startup)      | Х    | R <sub>DFSET</sub> | ENABLE<br>Command |

X = Don't Care

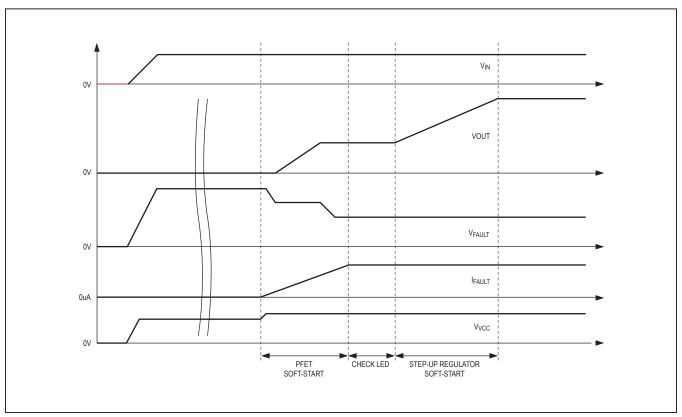

At startup, there are three phases. The first phase is p-channel MOSFET soft-start time, the second is check LED time (1ms), and the last phase is boost soft-start time (4ms). In the first phase, FAULT sink current is increased from  $0\mu A$  to  $50\mu A$  to avoid high inrush current caused by the p-channel MOSFET turn-on. In check LED time, the MAX17105 performs a diagnostic test of the LED array. In the test phase, all FB are pulled up by

0.8mA (typ, 0.4mA min) current source during 1ms (typ). If some FB\_ voltage is lower than 1.2V (max), the string is considered to be unused. Therefore, when a string is not in use, it should be connected to SGND. All other strings with FB\_ higher than 1.2V (max) are detected as in use. After the LED string diagnostic phases are finished, the step-up regulator starts. The total startup time is less than 10ms. Figure 3 shows the sequence.

#### Standby and FAULT Shutdown

The MAX17105 can be placed into standby by EN = low in direct-PWM mode or clearing bit 0 of the device control register (0x01) in SMBus mode. When a critical failure is detected, the IC enters fault shutdown mode. In standby or fault shutdown mode, all functions of the IC are turned off, including the 5V linear regulator. Only a crude linear regulator remains on providing a 4.5V (typ) output voltage to  $V_{CC}$ , with 1µA current sourcing capability. The Fault/ Status register is not reset in fault shutdown. When bit 0 of the device control register (0x01) is set to 1 in SMBus mode or cycling the EN pin, the MAX17105 exits fault shutdown mode and starts. The Fault/Status register is reset at startup.

Figure 3. Startup Timing Sequence

In standby or fault shutdown, the FAULT pin is pulled up to IN with an internal resistor of 1M $\Omega$  (typ), and the p-channel MOSFET is turned off. An external resistor could be used as well (R<sub>FXT</sub> > 200k $\Omega$ ).

#### **Frequency Selection**

The step-up regulator switching frequency can be adjusted through the external resistor-connected OSC pin. The switching frequency adjustable range is 500kHz to 2MHz. High-frequency (2MHz) operation optimizes the regulator for the smallest component size, at the expense of efficiency due to increased switching losses. Low-frequency (500kHz) operation offers the best overall efficiency, but requires larger components and PCB area. The maximum step-up regulator duty is limited by the 50ns (typ) minimum on-time.

#### **Overvoltage Protection**

To protect the step-up regulator when the load is open, or the output voltage becomes excessive for any reason, the MAX17105 features a dedicated overvoltage feedback input (OVP). The OVP pin is connected to the center tap of a resistive voltage-divider from the high-voltage output. The OVP pin has two levels of threshold. When the OVP pin voltage,  $V_{\rm OVP}$ , exceeds 1.25V (typ), a comparator turns off the internal power MOSFET and prevents excessive voltage from damage. This step-up regulator switch is reenabled after the  $V_{\rm OVP}$  drops 60mV (typ) hysteresis below the protection threshold. This overvoltage-protection feature ensures the step-up regulator fail-safe operation when the LED strings are disconnected from the output. When the OVP pin voltage exceeds 1.35V (typ), the IC is in fault shutdown.

#### **LED Current Sources**

Maintaining uniform LED brightness and dimming capability are critical for backlight applications. The MAX17105 is equipped with a bank of eight matched current sources. These specialized current sources are accurate to within  $\pm 2\%$ , and can be switched on- and off-PWM frequencies of up to 30kHz in direct-PWM mode and 5kHz in SMBus mode. All LED full-scale currents are identical and are set through the ISET pin (0mA <  $I_{LED}$  < 30mA). The LED current source has high-speed capability and allows 400ns minimum on-time within 400ns rise and fall time.

The minimum voltage drop across each current source is 500mV (max) when the LED current is 20mA. The low voltage drop helps reduce dissipation while maintaining sufficient compliance to control the LED current within the required tolerances.

The LED current sources can be disabled by connecting the respective FB\_ pin to SGND at startup. When the IC is enabled, the controller scans settings for all FB\_ pins. If a FB\_ pin is not connected to SGND, an internal circuit pulls this pin high, and the controller enables the corresponding current source to regulate the string current. If the FB\_ pin is connected to SGND, the controller disables the corresponding current regulator. The current regulator cannot be disabled by connecting the respective FB\_ pin to SGND after the IC is enabled.

All FB\_ pins in use are combined to extract a lowest FB\_ voltage (LVC) (see Figure 2). LVC is fed into the step-up regulator's error amplifier and is used to set the output voltage.

#### **Current Source Fault Protection**

LED fault open/short is detected after startup. When one or more strings fail after startup, the corresponding current source is disabled. The remaining LED strings are still operated normally. When a fault is detected, bit 4 or/ and bit 5 of the Fault/Status resister are set in SMBus mode. (See the Fault Status Register description in the Dimming Control Register Descriptions section.)

#### **LED Short and String Mismatch Protection**

The MAX17105 can tolerate slight mismatch between LED strings. When severe mismatches or WLED shorts occur, the FB\_ voltages are uneven because of mismatched voltage drops across strings. At each LED turnon, the FB\_ voltage is brought down to the regulation voltage quickly. When FB\_ voltage is higher than 8V (typ) after the LED turns on, the LED short is detected. When the LED short condition is continued for 2ms, the strings are disabled. The remaining LED strings can still operate normally. If only one string is used, the output voltage decreases and regulates the needed current during the operation of LED short. The LED short protection is not triggered since FB\_ voltage is never higher than the threshold. The LED short protection is disabled during the soft-start phase of the step-up regulator.

#### **Open-Current Source Protection**

The MAX17105 step-up regulator output voltage is regulated according to the minimum FB\_ voltages on all of the strings in use. If one or more strings are open, the respective FB\_ pins are pulled to ground. For any FB\_ lower than 220mV, the corresponding current source is disabled. The remaining LED strings can still operate normally. If all strings in use are open, the MAX17105 shuts the step-up regulator down.

#### **Dimming Control**

The MAX17105 has two dimming modes that are selected by the DFSET pin as shown in Table 3. The LED on/off DPWM frequency is generated by the internal oscillator for SMBus mode, while LED is directly on/off by the PWMI pin in direct-PWM mode. The DPWM frequency is adjustable through an external setting resistor and has 3% accuracy over the 200Hz to 2kHz range. In SMBus mode, the duty cycle of this DPWM signal can be controlled externally through two interfaces: PWM and SMBus. The ISET pin sets the amplitude of the current sources for each LED string (Figure 2). The internal DPWM signal directly controls the duty cycle of these current sources. The resulting current is chopped and synchronized to the DPWM signal. When filtered by the slow response time of the human eye, the overall brightness is modulated in a consistent flicker-free manner.

#### Full-Scale LED and Low-Level LED Current

The full-scale LED current IISET is determined by the resistors connected from ISET to SGND:

$$I_{LED\_MAX} = \frac{20mA \times 50k\Omega}{R_{ISET}}$$

The acceptable resistance range is  $33.3k\Omega < R_{ISET} < open$ , which corresponds to full-scale LED current of  $30mA > I_{LED\_MAX} > 0mA$ . Connect ISET to SGND sets the test mode for 0.3mA (typ) full-scale LED current.

#### **DPWM Frequency Setting**

The MAX17105 uses an internal DPWM signal to perform dimming control while operating at SMBus mode. The

DPWM frequency is specified by an external resistor connected from the DFSET pin to SGND:

$$f_{\text{DPWM}} = \frac{200 \text{Hz} \times 250 \text{k}\Omega}{R_{\text{DFSET}}}$$

The adjustable range for the DFSET resistor, R<sub>DFSET</sub>, is from  $10k\Omega$  to  $500k\Omega$ , corresponding to the DPWM frequency of  $5kHz > f_{DPWM} > 100Hz$ .

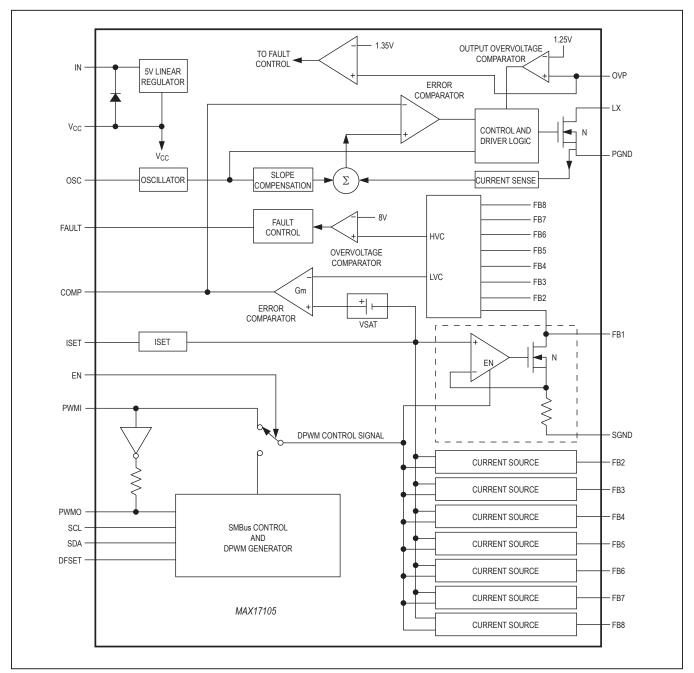

#### **Dimming Control Interfaces for SMBus Mode**

The MAX17105's dimming control circuit consists of two interfaces: PWM and SMBus. The block diagram of these two input interfaces is shown in Figure 4. The dimming can be performed in three modes: PWM, SMBus, or DPST. In PWM mode, the brightness is adjusted by the PWM signal applied to the PWMI pin. In SMBus mode, the brightness is adjusted by an I<sup>2</sup>C command from an uplink processor through a 2-wire SMBus. In DPST mode, the brightness is adjusted by the product of the PWM duty cycle and SMBus command value. This DPWM control provides a dimming range with 8-bit resolution down to 0% and supports Intel DPST to maximize battery life.

The SMBus interface can be used to adjust the dimming, as well as shut down the MAX17105. Before the MAX17105 receives a turn-on command from the SMBus, it automatically remains off. In this low-power state, most of the control circuits are turned off, and only part of the LDO is active to provide a loosely regulated output of approximately 4.5V on the  $V_{\rm CC}$  pin to power the SMBus interface.

Figure 4. PWM and SMBus Interface Circuit

#### **Dimming Control Register Descriptions**

The MAX17105 includes four registers to monitor and control brightness, fault status, driver ID, and operating mode.

**Brightness Control Register:** Address is 0x00. This register is both readable and writeable for all 8 bits, and for BRT0, and BRT7, which are used to control the LED brightness level. In SMBus dimming mode, an SMBus write byte cycle to register 0x00 sets the output brightness level. The SMBus setting of 0xFF for this register sets the backlight controller to the maximum brightness output, and 0x00 sets 0.4% backlight brightness. The default value for register 0x00 is 0xFF. A write byte cycle to register 0x00 has no effect when the backlight controller is in PWM mode. The SMBus read byte cycle to register 0x00 returns the current brightness level regardless of the dimming mode.

| REGISTER 0x00 BRIGHTNESS |             | ESS CONTROL I | REGISTER    | DEF         | AULT VALUE 0 | xFF         |                |

|--------------------------|-------------|---------------|-------------|-------------|--------------|-------------|----------------|

| BRT7                     | BRT6        | BRT5          | BRT4        | BRT3        | BRT2         | BRT1        | BRT0           |

| Bit 7 (R/W)              | Bit 6 (R/W) | Bit 5 (R/W)   | Bit 4 (R/W) | Bit 3 (R/W) | Bit 2 (R/W)  | Bit 1 (R/W) | Bit 0<br>(R/W) |

#### Bit Field Definitions:

| BIT FIELD | DEFINITION | DESCRIPTION                                                                                |

|-----------|------------|--------------------------------------------------------------------------------------------|

| Bit [7:0] | BRT [7:0]  | 8-bit brightness setting, adjusting brightness levels in 256 steps, default value is 0xFF. |

**Device Control Register:** Address is 0x01. This register is both readable and writeable for Bit 0 to Bit 2. Bit 0, also named BL\_CTL, is used as on/off control for the output LEDs. Bit 1 and Bit 2, named PWM\_SEL and PWM\_MD respec tively, control the operating mode of the backlight controller. Bit 3 to Bit 7 are reserved bits. All reserved bits, return 0 when read, and are ignored by the controller when written. A value of 1 written to BL\_CTL turns on the backlight in 10ms or less after the write cycle completes. A value of 0 written to BL\_CTL immediately turns off the backlight.

| REGISTER 0x01 DEVICE CONTROL REGISTER |          | GISTER   | DEFAULT VALUE 0X00 |          |             |             |             |

|---------------------------------------|----------|----------|--------------------|----------|-------------|-------------|-------------|

| Reserved                              | Reserved | Reserved | Reserved           | Reserved | PWM_MD      | PWM_SEL     | BL_CTL      |

| Bit 7                                 | Bit 6    | Bit 5    | Bit 4              | Bit 3    | Bit 2 (R/W) | Bit 1 (R/W) | Bit 0 (R/W) |

#### Bit Field Definitions:

| BIT FIELD | DEFINITION | DESCRIPTION                                                         |  |  |

|-----------|------------|---------------------------------------------------------------------|--|--|

| Bit 2     | PWM_MD     | PWM mode select (1 = absolute brightness, 0 = % change) default = 0 |  |  |

| Bit 1     | PWM_SEL    | Brightness MUX select (1 = PWMI pin, 0 = SMBus value) default = 0   |  |  |

| Bit 0     | BL_CTL     | BL on/off (1 = On, 0 = Off) default = 0                             |  |  |

The MAX17105 uses two multiplexers internally to direct the dimming signal processing (Figure 4). These two multiplexers are controlled by 2 bits of the device control register, PWM\_SEL and PWM\_MD, respectively. The PWM\_SEL bit selects either the SMBus or the PWMI input to control the brightness. The PWM\_MD bit selects the mode in which the PWMI input is to be interpreted. Table 4 provides a complete setting of the three dimming modes.

Table 4. Operating Modes Selected by Device Control Register Bits 1 and 2

| PWM_MD | PWM_SEL | MODE       | DPWM DUTY-CYCLE SETTING                            |

|--------|---------|------------|----------------------------------------------------|

| X      | 1       | PWM mode   | PWMI input duty cycle                              |

| 1      | 0       | SMBus mode | SMBus command                                      |

| 0      | 0       | DPST mode  | Product of PWMI input duty cycle and SMBus command |

X = Don't Care

In PWM mode, the output LED brightness is solely controlled by the percentage duty cycle of the input signal to PWMI. In SMBus mode, the input of PWMI has no effect on the dimming control, and only the SMBus command to the brightness control register adjusts the output brightness. In DPST mode, the overall brightness level is the normalized product of the SMBus command setting and PWM input duty cycle. The PWM signal starts from 100% when operating in DPST mode. The default value for register 0x01 is 0x00.

**Fault/Status Register:** Address is 0x02. This register has 6 status bits that allow monitoring the backlight controller's operating state. Bit 6 and Bit 7 are reserved bits, and Bit 3 is the status indicator or backlight. The other 5 bits are fault indicators. Bit 0 is a logical OR of all fault codes to simplify error detection (GLOBAL FAIL, OVCURR FAIL, 1CH SHORT/OPEN, 2 CH SHORT/OPEN, THRM\_SHDN). All the bits in this register are read only. The reserved bits return a 0 when read.

| REGIST    | ER 0x02   | x02 FAULT/STATUS REGISTER |           | DEFAULT VALUE 0X00 |           |           |           |

|-----------|-----------|---------------------------|-----------|--------------------|-----------|-----------|-----------|

| Reserved  | Reserved  | 2_CH_SD                   | 1_CH_SD   | BL_STAT            | OVCURR    | THRM_SHDN | FAULT     |

| Bit 7 (R) | Bit 6 (R) | Bit 5 (R)                 | Bit 4 (R) | Bit 3 (R)          | Bit 2 (R) | Bit 1 (R) | Bit 0 (R) |

#### Bit Field Definitions:

| BIT FIELD | DEFINITION | DESCRIPTION                                                            |  |  |

|-----------|------------|------------------------------------------------------------------------|--|--|

| Bit 5     | 2_CH_SD    | Two or more LED output channels are shut down (1 = shutdown, 0 = okay) |  |  |

| Bit 4     | 1_CH_SD    | One LED output channel is shut down (1 = shutdown, 0 = okay)           |  |  |

| Bit 3     | BL_STAT    | Backlight status (1 = BL on, 0 = BL off)                               |  |  |

| Bit 2     | OV_CURR    | Input overcurrent (1 = overcurrent condition, 0 = current okay)        |  |  |

| Bit 1     | THRM_SHDN  | Thermal shutdown (1 = thermal fault, 0 = thermal okay)                 |  |  |

| Bit 0     | FAULT      | Fault occurred (logic OR of all the fault conditions)                  |  |  |

**Identification Register:** Address is 0x03. The ID register contains two bit fields to denote the manufacturer and the silicon revision of the controller IC. The bit field widths were chosen to allow up to 32 vendors with up to eight silicon revisions each. This register is read only.

| REGISTER 0x03 ID REGISTER |           |           | ID REGISTER |           | DEF       | AULT VALUE 0 | X80       |

|---------------------------|-----------|-----------|-------------|-----------|-----------|--------------|-----------|

| LED Panel                 | MFG3      | MFG2      | MFG1        | MFG0      | REV2      | REV1         | REV0      |

| Bit 7 = 1                 | Bit 6 (R) | Bit 5 (R) | Bit 4 (R)   | Bit 3 (R) | Bit 2 (R) | Bit 1 (R)    | Bit 0 (R) |

#### Bit Field Definitions:

| BIT FIELD | DEFINITION | DESCRIPTION                                                      |  |  |

|-----------|------------|------------------------------------------------------------------|--|--|

| Bit 7     | LED Panel  | Display panel using LED backlight, Bit 7 = 1                     |  |  |

| Bit [6:3] | MFG[3:0]   | Manufacturer ID, see Table 5, default = 0                        |  |  |

| Bit [2:0] | REV[2:0]   | Silicon rev (revs 0 to 7 allowed for silicon spins), default = 0 |  |  |

The list of ID values for vendors is shown below, based on the current backlight controller vendor list and is not sorted in any particular order.

#### Table 5. Vendor IDs

| ID | VENDOR     |  |  |

|----|------------|--|--|

| 0  | Maxim      |  |  |

| 1  | Micro Semi |  |  |

| 2  | MPS        |  |  |

| 3  | O2 Micro   |  |  |

| 4  | TI         |  |  |

| ID   | VENDOR                             |  |  |

|------|------------------------------------|--|--|

| 5    | ST                                 |  |  |

| 6    | Analog Devices                     |  |  |

| 7-14 | Reserved                           |  |  |

| 15   | Vendor ID register not implemented |  |  |

#### Thermal Shutdown

The MAX17105 includes a thermal-protection circuit. When the local IC temperature exceeds +150°C (typ), the controller and current sources shut down and do not restart until the next enable signal is sent.

### **Design Procedure**

All MAX17105 designs should be prototyped and tested prior to production.

External component value choice is primarily dictated by the output voltage and the maximum load current, as well as maximum and minimum input voltages. Begin by selecting an inductor value. Once the inductor is known, choose the diode and capacitors.

#### **Step-Up Converter Current Calculation**

To ensure stable operation, the MAX17105 includes slope compensation, which sets the minimum inductor value. In continuous-conduction mode (CCM), the minimum inductor value is calculated with the following equation:

$$L_{CCM(MIN)} = \frac{\left(V_{OUT(MAX)} + V_{DIODE} - 2 \times V_{S(MIN)}\right) \times R_{S}}{2 \times 25.5 mV \times f_{SW(MIN)}}$$

where 25.5mV is a scale factor from the slope compensation,  $L_{CCM(MIN)}$  is the minimum inductor value for stable operation in CCM, and  $R_S$  =13.7m $\Omega$  (typ) is the equivalent sensing-scale factor from the controller's internal current-sense circuit.

The controller can also operate in discontinuous-conduction mode (DCM). In this mode, the inductor value can be lower, but the peak inductor current is higher than in CCM. In DCM, the maximum inductor value is calculated with the following equation:

$$\begin{split} L_{DCM(MAX)} = & \left(1 - \frac{V_{S(MIN)}}{V_{OUT(MAX)} + V_{DIODE}}\right) \\ \times & \frac{V_{S(MIN)}^2 \times \eta}{2 \times f_{SW(MAX)} \times V_{OUT(MAX)} \times I_{OUT(MAX)}} \end{split}$$

where  $L_{DCM(MAX)}$  is the maximum inductor value for DCM,  $\eta$  is the nominal regulator efficiency (85%), and  $I_{OUT(MAX)}$  is the maximum output current.

The output current capability of the step-up regulator is a function of current limit, input voltage, operating frequency, and inductor value. Because the slope compensation is used to stabilize the feedback loop, the inductor current limit depends on the duty cycle, and is determined with the following equation:

$$I_{LIM} = 2A + \frac{25.5mV \times (0.75 - D)}{R_S}$$

where 25.5 mV is the scale factor from the slope compensation, 2A is the current limit specified at 75% duty cycle, and D is the duty cycle.

The output current capability depends on the current-limit value and operating mode. The maximum output current in CCM is governed by the following equation:

$$I_{OUT\_CCM(MAX)} = \left(I_{LIM} - \frac{0.5 \times D \times V_{S}}{f_{SW} \times L}\right) \times \frac{V_{S}}{V_{OUT}} \times \eta$$

where  $I_{LIM}$  is the current limit calculated above,  $\eta$  is the nominal regulator efficiency (85%), and D is the duty cycle. The corresponding duty cycle for this current is:

$$D = \frac{V_{OUT} - V_{S} + V_{DIODE}}{V_{OUT} - I_{LIM} \times R_{ON} + V_{DIODE}}$$

where  $V_{DIODE}$  is the forward voltage of the rectifier diode and  $R_{ON}$  is the internal MOSFET's on-resistance (0.15 $\Omega$  (typ)).