# **Automotive Hi-Speed USB 2.0 Protectors**

### **General Description**

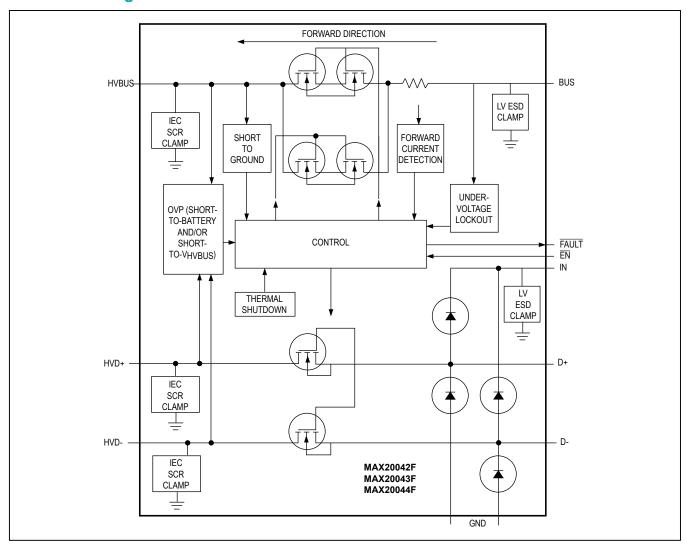

The MAX20042F, MAX20043F, and MAX20044F devices provide high ESD and short-circuit protection for the low-voltage internal USB data and USB power line in automotive radio, navigation, connectivity, and USB hub applications. The devices support USB Hi-Speed (480Mbps), USB full-speed (12Mbps), and USB low-speed (1.5Mbps) operation, as well as USB on-the-go (OTG) functionality.

The short-circuit protection features include short-to-battery on the protected HVBUS, HVD+, and HVD-outputs, as well as short-to-HVBUS on the protected HVD+ and HVD- outputs. The devices are capable of a short-to-battery condition of up to +18V. Short-to-GND protection and overcurrent protection are also provided on the protected HVBUS output to protect the internal BUS power rail from an overcurrent fault.

The devices feature high ESD protection to ±15kV Air Gap and ±8kV Contact on the protected HVBUS, HVD+, and HVD- outputs.

The devices feature a low on-resistance (R<sub>ON</sub>), 90m $\Omega$  (max) USB power switch, and two low on-resistance (R<sub>ON</sub>), 4 $\Omega$  (typ) USB 2.0 data switches. These devices also feature an enable input, a fault output, a 10ms fault-recovery time, a 1ms overcurrent blanking time, and an integrated overcurrent autoretry.

The MAX20042F, MAX20043F, and MAX20044F are available in a lead-free, 16-pin QSOP package and operate over the -40 $^{\circ}$ C to +105 $^{\circ}$ C temperature range.

#### **Benefits and Features**

- Accurate Bus Current Limiting with Minimal Voltage Drop

- Low  $R_{ON}$  90m $\Omega$  (max) USB Power Switch

- 0.65A (typ), MAX20042F

- 1.0A (typ), MAX20043F

- 1.3A (typ), MAX20044F

- Targeted Features for Optimized USB Performance

- Two R<sub>ON</sub> 4Ω (typ) USB 2.0 Data Switches

- 480Mbps or 12Mbps USB 2.0 Operation

- · 10ms Fault-Recovery Time

- · 1ms Overcurrent Blanking Time

- 5.67V (typ) Fixed HVBUS Protection Trip Threshold

- Robust for the Automotive Environment

- Short-to-Battery and Short-to-GND Protection on Protected HVBUS Output

- Short-to-Battery and Short-to-BUS Protection on Protected HVD+ and HVD- Outputs

- Tested to ISO 10605 and IEC 61000-4-2 ESD Standards

- 16-Pin (3.90mm x 4.94mm) QSOP Package

- -40°C to +105°C Operating Temperature Range

- AEC-Q100 Qualified

## **Applications**

Automotive USB Protection

Ordering Information appears at end of data sheet. Functional Diagram appears at end of data sheet.

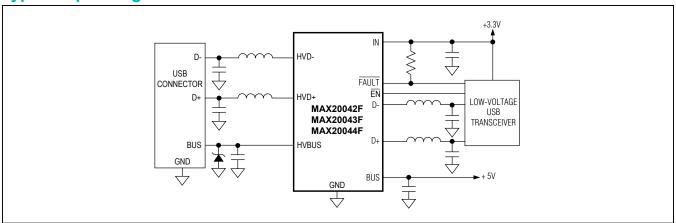

# **Typical Operating Circuit**

## **Absolute Maximum Ratings**

| (All voltages referenced to GND.) |              | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-----------------------------------|--------------|-------------------------------------------------------|

| BUS, IN                           | 0.3V to +6V  | 16-Pin QSOP (derate 9.6mW/°C above +70°C)771.5mW      |

| FAULT, EN, D+, D                  | 0.3V to +6V  | Operating Temperature Range40°C to +105°C             |

| D+, D- to IN                      | +0.3V        | Storage Temperature Range65°C to +150°C               |

| HVD+, HVD-, HVBUS                 | 0.3V to +18V | Junction Temperature+150°C                            |

|                                   |              | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

**QSOP**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....103.7°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......37°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{BUS} = 5.0 \text{V V}_{IN} = +3.3 \text{V}, T_J = T_A = -40 ^{\circ}\text{C} \text{ to } +105 ^{\circ}\text{C}. R_L = \infty, \text{ unless otherwise noted.}$  Typical values are at  $V_{\overline{EN}} = 0 \text{V}$  or  $V_{\overline{EN}} = 3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Note 2)

| PARAMETER                          | SYMBOL                   | CONDITIONS                                               | MIN  | TYP  | MAX  | UNITS |

|------------------------------------|--------------------------|----------------------------------------------------------|------|------|------|-------|

| POWER SUPPLY                       |                          |                                                          |      |      |      |       |

| Power-Supply Range (BUS)           | V <sub>BUS</sub>         |                                                          | 4.75 |      | 5.5  | V     |

| Power-Supply Range (IN)            | V <sub>IN</sub>          |                                                          | 3.0  |      | 3.6  | V     |

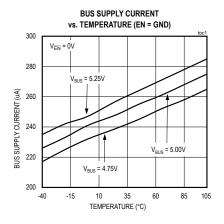

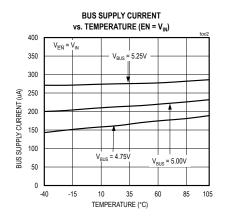

| Input Current (BUS)                | I <sub>BUS</sub>         | V <sub>EN</sub> = 0V, I <sub>L</sub> = 0A, no fault      |      |      | 400  | μA    |

| Input Current (IN)                 | I <sub>IN</sub>          | V <sub>EN</sub> = 0V, I <sub>L</sub> = 0A, no fault      |      |      | 10   | μA    |

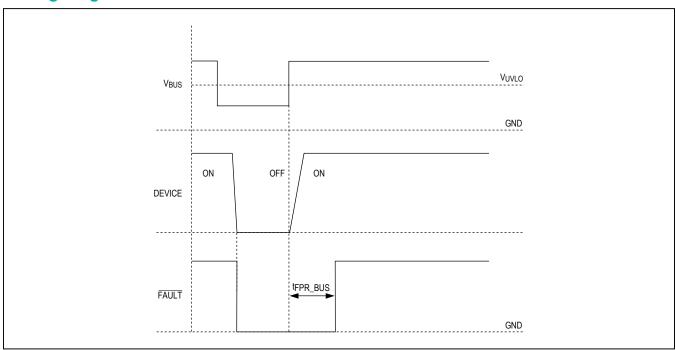

| BUS Undervoltage Lockout           | V <sub>UVLO</sub>        | V <sub>BUS</sub> falling, Figure 1                       | 3.85 | 4.2  | 4.55 | V     |

| BUS ANALOG SWITCH                  |                          |                                                          |      |      |      |       |

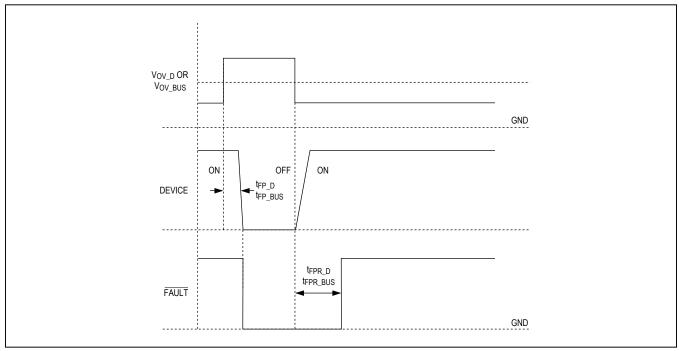

| HVBUS Protection Trip Threshold    | V <sub>OV_BUS</sub>      | HVBUS rising, Figure 2                                   | 5.55 | 5.67 | 5.8  | V     |

| Voltage Protection Response Time   | t <sub>FP_BUS</sub>      | HVBUS rising, Figure 2                                   |      | 0.3  | 3.0  | μs    |

| Protection Recovery Time           | t <sub>FPR_BUS</sub>     | HVBUS falling to below V <sub>OV_BUS</sub> , Figure 2    | 4.5  | 10   | 22   | ms    |

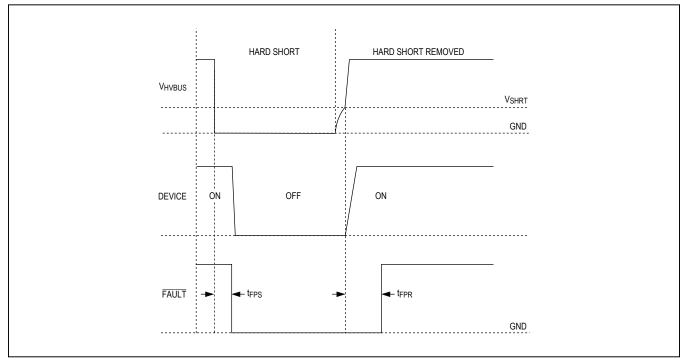

| HVBUS Short-to-Ground<br>Threshold | V <sub>SHRT</sub>        | Figure 3                                                 | 0.7  |      | 2.2  | V     |

| Short-to-Ground Response Time      | t <sub>FPS</sub>         | HVBUS falling to GND, Figure 3                           |      | 0.3  | 1    | μs    |

| Short Detection Time               | tshrt det                | Enabled into short-to-ground                             | 1    | 2    | 4    | ms    |

| On-Resistance                      | R <sub>ON</sub>          | V <sub>BUS</sub> = 5V, I <sub>BUS</sub> = 500mA (Note 2) |      | 51   | 90   | mΩ    |

|                                    |                          | MAX20042F, Figure 4                                      | 0.57 | 0.65 | 0.73 |       |

| Forward-Current Threshold (Note 3) | I <sub>THR</sub>         | MAX20043F, Figure 4                                      | 0.88 | 1.00 | 1.12 | Α     |

| (1.10.10 0)                        |                          | MAX20044F, Figure 4                                      | 1.14 | 1.30 | 1.46 |       |

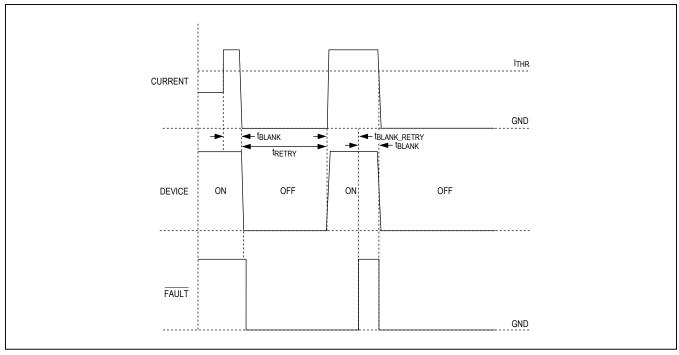

| Overcurrent Blanking Time          | t <sub>BLANK</sub>       | Figure 4 (Note 4)                                        | 0.35 | 1.2  | 2.8  | ms    |

| Overcurrent-Retry Blanking Time    | t <sub>BLANK_RETRY</sub> | Figure 4                                                 |      | 12   |      | ms    |

| Overcurrent Autoretry Time         | t <sub>RETRY</sub>       | Figure 4                                                 |      | 128  |      | ms    |

# **Electrical Characteristics (continued)**

$(V_{BUS} = 5.0 \text{V V}_{IN} = +3.3 \text{V}, T_J = T_A = -40 ^{\circ}\text{C} \text{ to } +105 ^{\circ}\text{C}. R_L = \infty, \text{ unless otherwise noted}. Typical values are at <math>V_{\overline{EN}} = 0 \text{V or } V_{\overline{EN}} = 3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Note 2)

| PARAMETER                            | SYMBOL                              | CONDITIONS                                                                                                                          | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| LIV/DLIC Off Lagles as Comment       |                                     | V <sub>HVBUS</sub> = 18V, V <sub>BUS</sub> = 4.75V                                                                                  |      |      | 750  |       |

| HVBUS Off-Leakage Current            | I <sub>LKGOFF</sub>                 | V <sub>HVBUS</sub> = 18V, V <sub>BUS</sub> = 0V, V <sub>IN</sub> = 0V                                                               |      | 560  |      | μA    |

| Thermal Shutdown                     |                                     |                                                                                                                                     |      | +175 |      | °C    |

| Thermal-Shutdown Hysteresis          |                                     |                                                                                                                                     |      | 15   |      | °C    |

| D+, D- ANALOG USB SWITCHES           |                                     |                                                                                                                                     |      |      |      |       |

| Analog Signal Range                  |                                     |                                                                                                                                     | 0    |      | 3.6  | V     |

| Protection Trip Threshold            | V <sub>OV_D</sub>                   | HVD+, HVD- rises from $V_{IN}$ to > $V_{IN}$ + 1, Figure 2                                                                          |      |      | 3.9  | V     |

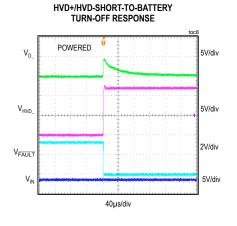

| Protection Response Time             | t <sub>FP_D</sub>                   | HVD+, HVD- rises from $V_{IN}$ to > $V_{IN}$ + 1, Figure 2                                                                          |      | 3.0  | 8.0  | μs    |

| Protection Recovery Time             | t <sub>FPR_D</sub>                  | HVD+, HVD- falling to below V <sub>OV_D</sub> , Figure 2                                                                            | 4.5  | 10   | 22   | ms    |

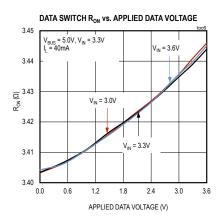

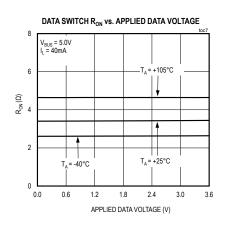

| On-Resistance                        | R <sub>ON</sub>                     | $V_{BUS} = 5V$ , $I_{L} = 40$ mA, $0 \le V_{D_{L}} \le 3.6$ V                                                                       |      | 4    |      | Ω     |

| On-Resistance Match Between Channels | ΔR <sub>ON</sub>                    | V <sub>BUS</sub> = 5V; I <sub>L</sub> = 40mA; V <sub>D</sub> _ = 1.5V, 3.0V                                                         |      | 0.7  | 1.5  | Ω     |

| On-Resistance Flatness               | R <sub>FLAT(ON)</sub>               | I <sub>L</sub> = 40mA, V <sub>D</sub> = 0V or 0.4V                                                                                  |      | 1.0  |      | Ω     |

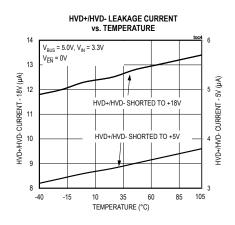

|                                      |                                     | V <sub>HVD+</sub> , V <sub>HVD-</sub> = 18V; V <sub>D+</sub> , V <sub>D-</sub> = 0V                                                 | -200 | +100 | +200 |       |

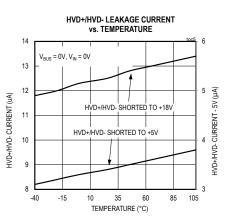

| HVD+, HVD- Off-Leakage Current       | I <sub>HVD_OFF</sub>                | V <sub>HVD+</sub> , V <sub>HVD-</sub> = 18V; V <sub>D+</sub> , V <sub>D-</sub> = 0V;<br>V <sub>IN</sub> = 0V; V <sub>BUS</sub> = 0V |      | 45   |      | μA    |

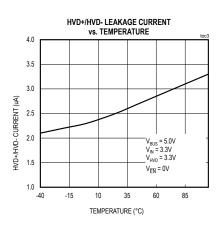

| HVD+, HVD- On-Leakage Current        | I <sub>HVD_ON</sub>                 | $V_{HVD+}$ , $V_{HVD-} = V_{IN}$ or 0V; $V_{\overline{EN}} = 0V$                                                                    |      | +2.2 |      | μΑ    |

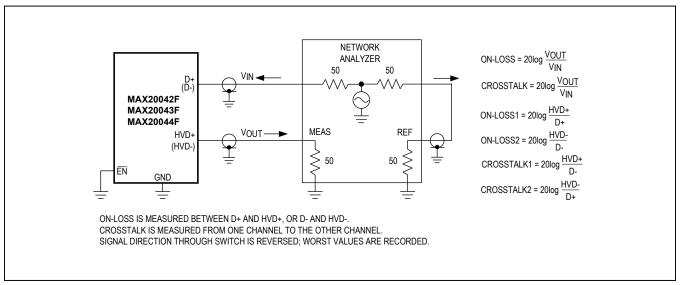

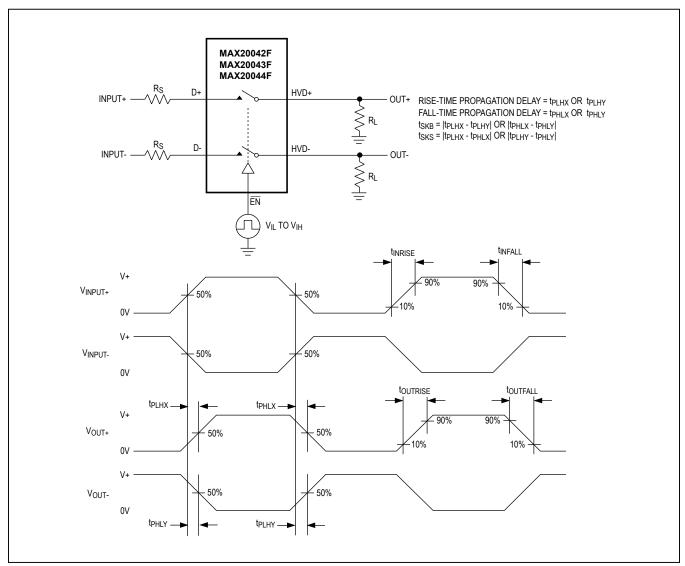

| Propagation Delay                    | t <sub>PLH</sub> , t <sub>PHL</sub> | $R_L = R_S = 50\Omega$ , Figure 7                                                                                                   |      | 200  |      | ps    |

| Output Skew Between Switches         | t <sub>SKB</sub>                    | Skew between D+ and D- switch, Figure 7                                                                                             |      | 40   |      | ps    |

| Output Skew Same Switch              | tsks                                | Skew between opposite transitions in same switch, Figure 7                                                                          |      | 40   |      | ps    |

| FAULT OUTPUT                         |                                     | 1                                                                                                                                   | l .  |      | ,    |       |

| FAULT Output Low Voltage             | V <sub>OL</sub>                     | I <sub>SINK</sub> = 500μA                                                                                                           |      |      | 0.5  | V     |

| FAULT Output High-Leakage<br>Current |                                     |                                                                                                                                     |      |      | 1    | μА    |

| FAULT-Recovery Time                  | t <sub>FPR</sub>                    | V <sub>FAULT</sub> = V <sub>IN</sub> , Figure 3 (Note 3)                                                                            | 4.5  | 10   | 22   | ms    |

| EN INPUT                             |                                     |                                                                                                                                     |      |      |      |       |

| Input Logic-High                     | V <sub>IH</sub>                     |                                                                                                                                     | 1.65 |      |      | V     |

| Input Logic-Low                      | V <sub>IL</sub>                     |                                                                                                                                     |      |      | 0.5  | V     |

| Input Leakage Current                | IEN                                 | V <sub>EN</sub> = 0V or V <sub>IN</sub>                                                                                             |      |      | 1    | μΑ    |

| Enable Delay Time                    | t <sub>D_EN</sub>                   |                                                                                                                                     |      | 40   |      | μs    |

## **Electrical Characteristics (continued)**

$(V_{BUS} = 5.0 \text{V V}_{IN} = +3.3 \text{V}, T_J = T_A = -40 ^{\circ}\text{C}$  to  $+105 ^{\circ}\text{C}$ .  $R_L = \infty$ , unless otherwise noted. Typical values are at  $V_{\overline{EN}} = 0 \text{V}$  or  $V_{\overline{EN}} = 3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Note 2)

| PARAMETER                        | SYMBOL | CONDITIONS                          | MIN | TYP | MAX | UNITS |

|----------------------------------|--------|-------------------------------------|-----|-----|-----|-------|

| ESD PROTECTION HVD+, HVD-, HVBUS |        |                                     |     |     |     |       |

|                                  |        | ISO 10605 Air Gap (330pF, 2kΩ)      |     | ±25 |     |       |

|                                  |        | ISO 10605 Contact (330pF, 2kΩ)      |     | ±8  |     |       |

| CCD Protection Level (Note 5)    | \/     | IEC 61000-4-2 Air Gap (150pF, 330Ω) |     | ±15 |     | 107   |

| ESD Protection Level (Note 5)    | VESD   | IEC 61000-4-2 Contact (150pF, 330Ω) |     | ±8  |     | kV    |

|                                  |        | IEC 61000-4-2 Air Gap (330pF, 330Ω) |     | ±15 |     |       |

|                                  |        | IEC 61000-4-2 Contact (330pF, 330Ω) |     | ±8  |     |       |

- **Note 2:** Specifications with minimum and maximum limits are 100% production tested at  $T_A = +25$ °C and are guaranteed over the operating temperature range by design and characterization. Actual typical values may vary and are not guaranteed.

- Note 3: Forward current is defined as current into BUS and out of HVBUS. See the Functional Diagram.

- Note 4: Guaranteed by design. Limits are not production tested.

- Note 5: Tested in the Typical Application Circuit, as shown on the MAX20044 evaluation kit.

## **Timing Diagrams/Test Circuits**

Figure 1. Timing Diagram for Undervoltage Lockout on BUS

# **Timing Diagrams/Test Circuits (continued)**

Figure 2. Timing Diagram for Overvoltage Protection on HVBUS, HVD+, and HVD-

Figure 3. Timing Diagram for Short-to-Ground Protection

# **Timing Diagrams/Test Circuits (continued)**

Figure 4. Timing Diagram for Overcurrent Protection

Figure 5. On-Channel -3dB Bandwidth and Crosstalk

# **Timing Diagrams/Test Circuits (continued)**

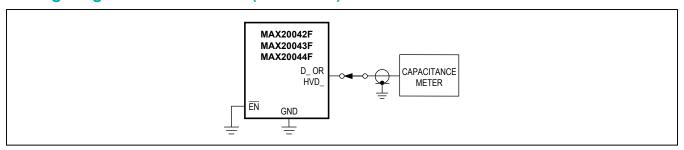

Figure 6. On-Capacitance

Figure 7. Propagation Delay and Output Skew

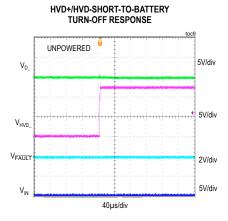

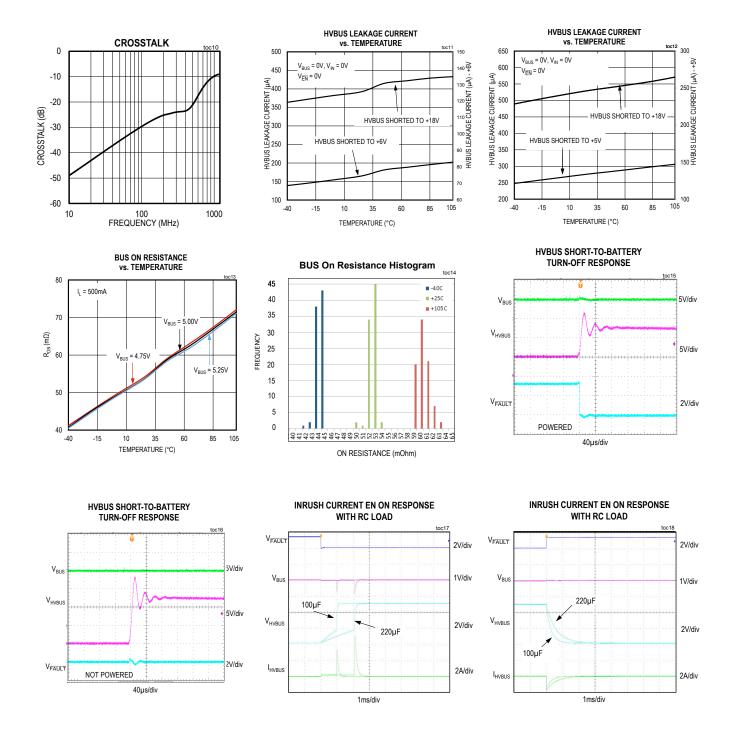

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

(T<sub>A</sub> = +25°C, unless otherwise noted.)

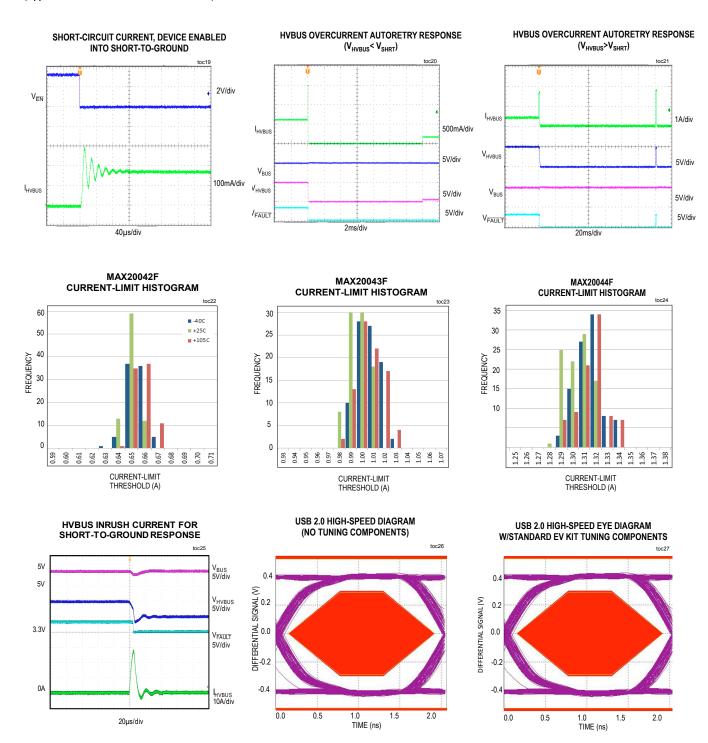

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

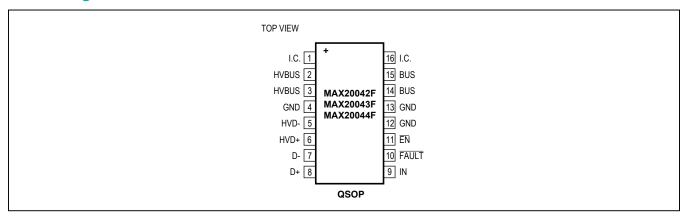

# **Pin Configuration**

# **Pin Description**

| PIN       | NAME                                                             | FUNCTION                                                                                                                                                                                                                                   |

|-----------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 16     | I.C.                                                             | Internal Connection. Must be left unconnected.                                                                                                                                                                                             |

| 2, 3      | HVBUS                                                            | Protected BUS Output. Connect HVBUS directly to the USB connector. Connect both HVBUS outputs together for proper operation. Connect a 20V zener diode and a 0.1µF and 10µF capacitor from HVBUS to GND.                                   |

| 4, 12, 13 | GND                                                              | Ground                                                                                                                                                                                                                                     |

| 5         | HVD-                                                             | High-Voltage-Protected USB Differential Data D- Output. Connect HVD- directly to USB connector D                                                                                                                                           |

| 6         | HVD+                                                             | High-Voltage-Protected USB Differential Data D+ Output. Connect HVD+ directly to USB connector D+.                                                                                                                                         |

| 7         | D-                                                               | USB Differential Data D- Input. Connect D- to low-voltage USB transceiver D                                                                                                                                                                |

| 8         | D+                                                               | USB Differential Data D+ Input. Connect D+ to low-voltage USB transceiver D+.                                                                                                                                                              |

| 9         | IN                                                               | Logic Power-Supply Input. The supply voltage range is from +3.0V to +3.6V. Connect a 0.1µF and 10µF capacitor from IN to GND. Place these components on the same plane as the IC, close to the IN and GND pins.                            |

| 10        | FAULT                                                            | Open-Drain Fault Indicator Output. Used to indicate if an overvoltage condition exists on HVD-, HVD+, or HVBUS, if an overcurrent condition exists on HVBUS, if a short-to-GND exists on HVBUS, or if an overtemperature condition occurs. |

| 11        | 1 EN Active-Low Enable Input. Drive EN low to enable the device. |                                                                                                                                                                                                                                            |

| 14, 15    | BUS                                                              | USB Power Supply. Connect BUS to USB +5V supply. Connect both BUS inputs together for proper operation. Connect a 0.1μF and a 100μF, low-ESR ceramic capacitor from BUS to GND.                                                            |

### **Detailed Description**

The MAX20042F, MAX20043F, and MAX20044F devices provide high ESD and short-circuit protection for the low-voltage internal USB data and USB power line in automotive radio, navigation, connectivity, and USB hub applications. The devices support both USB Hi-Speed (480Mbps) and USB full-speed (12Mbps) operation.

The short-circuit protection features include short-to-battery on the protected HVBUS, HVD+, and HVD- outputs, as well as short-to-HVBUS on the protected HVD+ and HVD- outputs. These devices are capable of a short-to-battery condition of up to +18V. Short-to-GND protection and overcurrent protection are also provided on the protected HVBUS output to protect the internal BUS power rail from overcurrent faults.

The devices feature high ESD protection to ±15kV Air Gap Discharge and ±8kV Contact Discharge on all protected HVBUS, HVD+, and HVD- outputs.

The devices feature a low on-resistance ( $R_{ON}\rangle$  0.14 $\Omega$  (max) USB power switch and two low on-resistance ( $R_{ON}\rangle$  of  $4\Omega$  (typ) USB 2.0 switches. These devices also feature an enable input, a fault output, a 10ms fault-recovery time, a 1ms overcurrent blanking time, and an integrated overcurrent autoretry.

#### **BUS Undervoltage Lockout (Power-On Reset)**

The devices have a 4.2V (typ) undervoltage-lockout threshold ( $V_{UVLO}$ ). When  $V_{BUS}$  is less than  $V_{UVLO}$ , FAULT is enabled and all the device switches are high impedance.

#### **HVBUS Overvoltage Protection**

The devices have a fixed 5.57V (typ) HVBUS protection trip threshold; when HVBUS rises from  $V_{BUS}$  to > 5.57V, the device is turned off. Connect a 20V zener diode or RC snubber network from HVBUS to GND to limit positive inductive voltage spikes that are caused by the inductance from long wires at turn-off.

#### **HVBUS Short-to-Ground**

The devices have a 0.7V (min) HVBUS short-to-ground threshold ( $V_{SHRT}$ ). When HVBUS falls below the  $V_{SHRT}$  threshold, the main power switch is turned off. During continuous short-to-ground conditions, an approximately 250mA autoreset current remains active to detect removal of the short circuit.

#### **HVBUS Overcurrent Protection**

The devices have a 0.65A/1.0A/1.3A (typ) forward current threshold ITHR. When the HVBUS forward current exceeds the ITHR threshold, the device is turned off. Forward current is defined as current into BUS and out of HVBUS. See the *Functional Diagram*.

### **HVD+ and HVD- Overvoltage Protection**

The devices have a 4.1V (typ) overvoltage threshold (VOV\_D). When HVD+, or HVD- is greater than VOV\_D, FAULT is enabled and all the device switches are high impedance. Note that HVD+ and HVD- do not have short-to-ground protection. Forward current is limited by the upstream transceiver.

#### **FAULT** Output

$\overline{\text{FAULT}}$  goes low when a fault is detected on HVD+, HVD-, or HVBUS. The  $\overline{\text{FAULT}}$  output is asserted low when the device is enabled and the switches are disabled due to a fault. Fault detection includes short-to-battery, short-to-GND or overcurrent on HVBUS, and short-to-battery or short-to-HVBUS on HVD+ or HVD-. Connect a 100kΩ pullup resistor from  $\overline{\text{FAULT}}$  to IN.

#### **EN** Input

$\overline{\text{EN}}$  is an active-low enable input. Drive  $\overline{\text{EN}}$  low for normal operation and enable the protection switches. This allows BUS power, D+, and D- USB signaling to pass through the device if a fault is not present. Drive  $\overline{\text{EN}}$  high to disable the device.

The MAX20042F, MAX20043F, and MAX20044F devices support USB OTG. With these units, disabling the device through the  $\overline{\text{EN}}$  pin disables the +5V BUS power switch, but leaves the D+ and D- data switches closed. This allows for a downstream device to assume the role of host when negotiated per the USB Host Negotiation Protocol. In this mode, the HVBUS, HVD+, and HVD-outputs continue to be protected and  $\overline{\text{FAULT}}$  continues to assert normally in response to overvoltage conditions on these pins.

## **Applications Information**

#### **Power-Supply Bypass Capacitor**

Bypass HVBUS to GND with a  $10\mu F$  and a  $0.1\mu F$  ceramic capacitor as close to the device as possible to provide  $\pm 15 kV$  (HBM) ESD protection on the pin. If the power source has significant inductance due to long lead length, take care to prevent overshoots due to the LC tank circuit and provide protection if necessary to prevent violation of the +6V absolute maximum rating on BUS. Connect a  $100\mu F$  low-ESR ceramic capacitor from BUS to GND. Connect a  $0.1\mu F$  and  $10\mu F$  ceramic capacitor from both BUS and IN to GND. Place these components on the same plane as the IC, close to the IN and GND pins.

#### **Layout of USB Data Line Traces**

USB Hi-Speed requires careful PCB layout with  $90\Omega$  controlled-impedance matched traces of equal lengths. Use LC tuning components on the data lines as shown in the <u>Typical Operating Circuit</u>. The values of these components are layout and captive-cable dependent. Contact Maxim technical support for more detailed information.

#### ±15kV ESD Protection

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The devices have extra protection against static electricity. Maxim's engineers have developed state-of-theart structures to protect against ESD of ±15kV at the HVD+, HVD-, and HVBUS ports without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, the devices keep working without latchup, whereas other solutions can latch and must be powered down to remove latchup. ESD protection can be tested in various ways; this product is characterized for protection to the following limits:

- ±15kV using the Human Body Model

- ±15kV using IEC 61000-4-2's Air-Gap Discharge method, EN = GND

- ±8kV using the Contact Discharge method specified in IEC 61000-4-2, EN = GND

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### **Human Body Model**

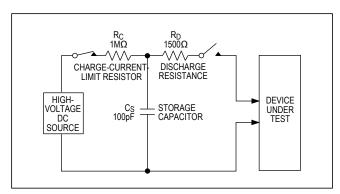

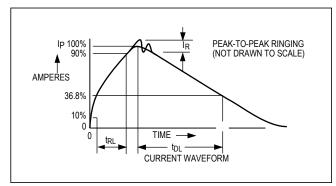

<u>Figure 8</u> shows the Human Body Model, and <u>Figure 9</u> shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$  resistor.

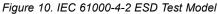

#### IEC 61000-4-2

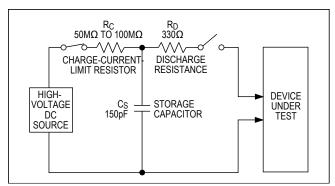

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. The MAX20042F, MAX20043F, and MAX20044F devices help users design equipment that meets Level 4 of IEC 61000-4-2. The main difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2. Because series resistance is lower in the IEC 61000-4-2 ESD test model (Figure 10), the ESD withstand voltage measured to this standard is generally lower than that measured using the Human Body Model. Figure 11 shows the current waveform for the ±8kV, IEC 61000-4-2 Level 4, ESD Contact Discharge test. The Air-Gap Discharge test involves approaching the device with a charged probe. The Contact Discharge method connects the probe to the device before the probe is energized.

## **Functional Diagram**

Figure 8. Human Body ESD Test Model

Figure 9. Human Body Current Waveform

Figure 11. IEC 61000-4-2 ESD Generator Current Waveform

## **Ordering Information**

| PART             | CURRENT RATING (A) (typ) | OTG SUPPORT | PIN-PACKAGE |

|------------------|--------------------------|-------------|-------------|

| MAX20042FGEEA/V+ | 0.65                     | No          | 16 QSOP     |

| MAX20042FGEEB/V+ | 0.65                     | Yes         | 16 QSOP     |

| MAX20043FGEEA/V+ | 1.0                      | No          | 16 QSOP     |

| MAX20043FGEEB/V+ | 1.0                      | Yes         | 16 QSOP     |

| MAX20044FGEEA/V+ | 1.3                      | No          | 16 QSOP     |

| MAX20044FGEEB/V+ | 1.3                      | Yes         | 16 QSOP     |

Note: All devices are specified over the -40°C to +105°C operating temperature range.

# **Chip Information**

PROCESS: BiCMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND        |

|---------|---------|---------|-------------|

| TYPE    | CODE    | NO.     | PATTERN NO. |

| 16 QSOP | E16+12C | 21-0055 |             |

<sup>/</sup>V denotes an automotive qualified part.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## MAX20042F-MAX20044F

# Automotive Hi-Speed USB 2.0 Protectors

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 1/17          | Initial release |                  |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.