#### Click here to ask an associate for production status of specific part numbers.

### Industrial Configurable Analog I/O

### **General Description**

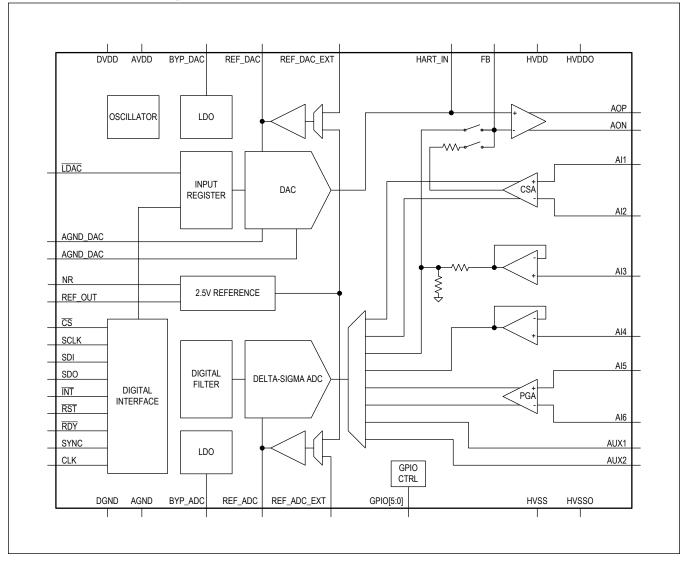

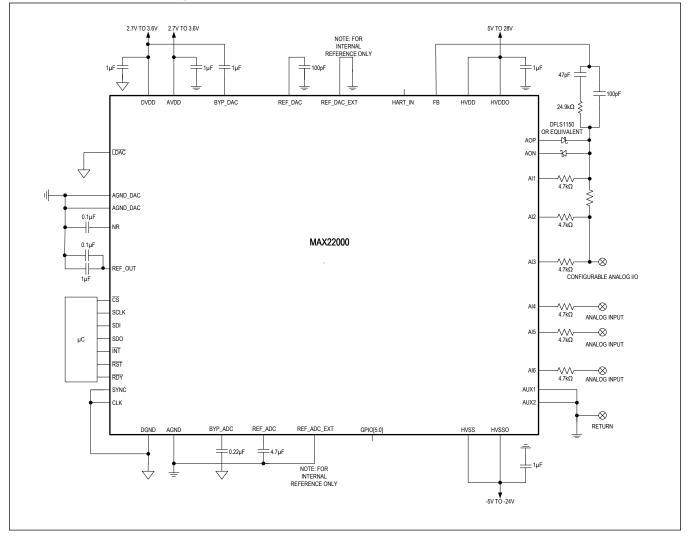

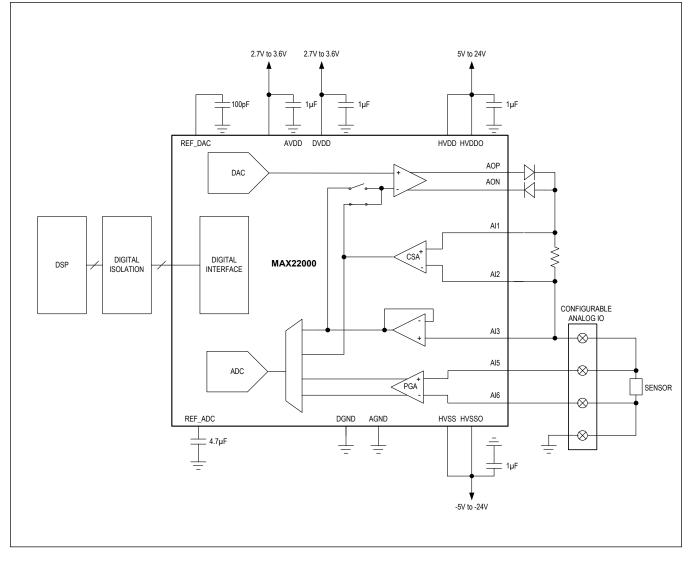

The MAX22000 is an industrial-grade configurable analog input/output device that can be configured on-the-fly in software as a voltage input or output, or current input or output. Additional inputs are available to measure other analog signals.

The device offers an 18-bit DAC with fast settling time, as well as a 24-bit delta-sigma ADC. The ADC and DAC can individually choose between an internal or an external reference.

The MAX22000 supports the ADC with a low-noise programmable gain amplifier (PGA), with high-voltage and low-voltage input ranges to support RTD and thermocouple measurements. Additional auxiliary inputs are provided to measure cold junction temperatures on-board.

The MAX22000 communicates through a high speed 20MHz SPI bus for all configuration and management information, as well as for conversion results. An optional 8-bit CRC enhances the reliability of the SPI interface, protecting against all 8-bit bursts and double-bit errors.

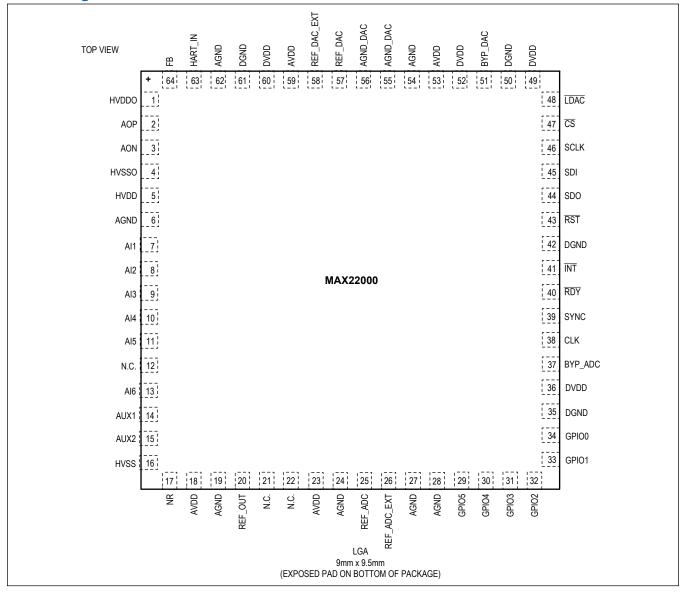

The MAX22000 operates from 2.7V to 3.6V analog and digital supplies and up to  $\pm$ 24V high-voltage supplies. The device is available in a 64-pin LGA package and operates over the -40°C to +125°C industrial temperature range.

### **Applications**

- Distributed Control Systems

- Process Control

- Programmable Logic Controllers (PLC)

- Programmable Automation Controllers (PAC)

### **Benefits and Features**

- Accuracy

- Analog Output Voltage or Current Mode:

- 0.02% FSR Accuracy, Room Temp

- 0.1% FSR Accuracy, ±50°C Temp Variation

- 5ppm/°C Internal Reference

- Flexibility

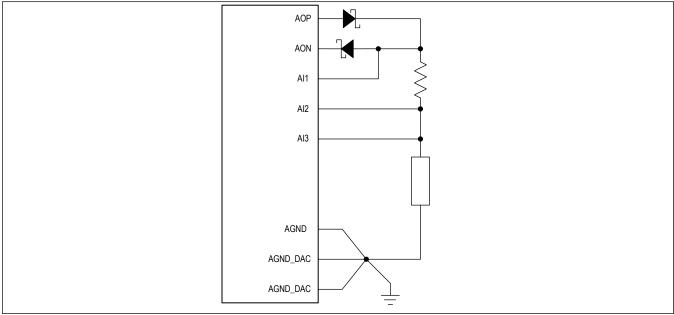

- 6 Analog Inputs/1 Analog Output, Software Configurable for Voltage and Current Mode

- Two Auxiliary ADC Inputs for Cold Junction Measurements

- RTD Input Mode in 2, 3, or 4-Wire Configurations

- Thermocouple Input Mode

- ±12.5V Input/Output Voltage Range

- ±25mA or ±2.5mA Output Current Range

- ±25V, ±2.5V, ±500mV, ±250mV, and ±125mV PGA

- Input Voltage Ranges

- +24V Field Supply for Current Loop

- Optional External Reference for ADC and/or DAC

- Six GPIOs

- 20MHz SPI Interface

- Robustness

- ±36V Protection on All Analog I/O Ports

- Overcurrrent Protection

- Thermal Shutdown

- Undervoltage Interrupt on All High Voltage Supplies

- CRC Detection

- · Open Detection on All Analog Inputs

- 1kV HBM Protection on All Pins

- -40°C to +125°C Operating Temperature Range

- 9mm x 9.5mm 64-Pin LGA Package

<u>Ordering Information</u> and <u>Application Block Diagram</u> appear at end of datasheet.

© 2022 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

## Industrial Configurable Analog I/O

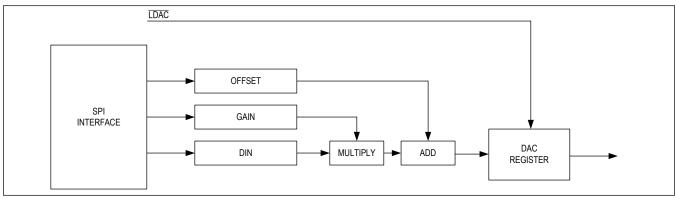

### Functional Block Diagram

# Industrial Configurable Analog I/O

### **Absolute Maximum Ratings**

| AVDD to AGND         | -0.3V to +3.9V                                   |

|----------------------|--------------------------------------------------|

| DVDD to DGND         | -0.3V to +3.9V                                   |

| AGND to DGND         | -0.3V to +0.3V                                   |

| AGND_DAC to AGND     | -0.3V to +0.3V                                   |

| AGND_DAC to DGND     |                                                  |

| AVDD to REF_DAC_EXT  | -0.3V to +3.9V                                   |

| BYP_ADC to DGND      | 0.3V to +2.1V                                    |

| HVDD to HVSS         |                                                  |

| HVDDO to HVSSO       | 0.3V to +52V                                     |

| HVDD to AGND         | 0.3V to +40V                                     |

| HVDDO to AGND        |                                                  |

| AGND to HVSS         |                                                  |

| AGND to HVSSO        | 0.3V to +40V                                     |

| HVSSO to HVSS        |                                                  |

| AI_ to HVSS          | 0.3V to the lower of +52V or                     |

|                      | ((V <sub>HVDD</sub> -V <sub>HVSS</sub> )+0.3V)   |

| HART_IN, FB to HVSSO | 0.3 to the lower of +52V or                      |

|                      | ((V <sub>HVDDO</sub> -V <sub>HVSSO</sub> )+0.3V) |

| INT to DGND<br>CS, SCLK, SDI, SDO, RDY, RST, SYNC, CLH<br>DGND0.3 to the lower of +3.9V<br>REF_ADC, REF_DAC, AUX1, AUX2,<br>REF_DAC_EXT, NR, REF_OUT, BYP_DAC to<br>the lower of +3.9V | <pre>K, LDAC, GPIO_ to / or (V<sub>DVDD</sub>+0.3V) REF_ADC_EXT,</pre> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| AON to HVSS                                                                                                                                                                            |                                                                        |

|                                                                                                                                                                                        |                                                                        |

| AOP to HVDDO                                                                                                                                                                           |                                                                        |

| AON to HVSSO                                                                                                                                                                           | 0.3V to +70V                                                           |

| Maximum Current into AOP, AON                                                                                                                                                          | ±100mA                                                                 |

| Maximum Current into Any Other Pin                                                                                                                                                     | ± 50mA                                                                 |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                                                                                                  |                                                                        |

| 64-Pin LGA (derate 42.8mW/°C over $T_{\Delta} = +$                                                                                                                                     | -70°C)3418.8mW                                                         |

| Operating Temperature Range                                                                                                                                                            | ,                                                                      |

|                                                                                                                                                                                        |                                                                        |

| Junction Temperature                                                                                                                                                                   |                                                                        |

| Storage Temperature Range                                                                                                                                                              | 65°C to +150°C                                                         |

| Soldering Temperature (reflow)                                                                                                                                                         | +260°C                                                                 |

|                                                                                                                                                                                        |                                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 64 LGA

| Package Code                          | L649A9M+1        |

|---------------------------------------|------------------|

| Outline Number                        | <u>21-100274</u> |

| Land Pattern Number                   | <u>90-100096</u> |

| Thermal Resistance, Four-Layer Board: |                  |

| Junction to Ambient ( $\theta_{JA}$ ) | 23.4°C/W         |

| Junction to Case $(\theta_{JC})$      | 7.0°C/W          |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "." in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

## Industrial Configurable Analog I/O

### **Electrical Characteristics**

| PARAMETER                                     | SYMBOL                                                                                               | CONDITIONS                                                                                                                                                   | MIN   | TYP      | MAX   | UNITS             |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-------|-------------------|

| ANALOG OUTPUT VOLT                            | AGE MODE                                                                                             | -                                                                                                                                                            |       |          |       |                   |

|                                               |                                                                                                      | 12.5V setting, DAC full-scale range ( <u>Note</u><br><u>2</u> )                                                                                              |       | ±12.5    |       |                   |

| Output Voltage Range                          | V <sub>OUT</sub>                                                                                     | 12.5V setting, linear range ( <u>Note 2</u> , <u>Note</u><br><u>3</u> )                                                                                      | -10.5 |          | +10.5 | V                 |

|                                               |                                                                                                      | 25V setting ( <u>Note 2</u> )                                                                                                                                |       | +25      |       |                   |

| Dropout Voltage                               | V <sub>HVDDO</sub> = +13V, sourcing 25mA,<br>measured between HVDDO and AOP,<br>gain compression <1% |                                                                                                                                                              |       | 0.85     | - v   |                   |

| Diopout voltage                               |                                                                                                      | V <sub>HVDDO</sub> = -13V, sinking 25mA,<br>measured between AON and HVSSO,<br>gain compression <1%                                                          |       |          | 0.85  | v                 |

| Output Current                                |                                                                                                      | Output shorted to HVDDO or HVSSO, threshold current ( <u>Note 4</u> )                                                                                        |       | 50       |       | - mA              |

| Protection                                    |                                                                                                      | Output shorted to HVDDO or HVSSO, average current ( <u>Note 4</u> )                                                                                          |       | 13       |       | IIIA              |

| AOP, AON High<br>Impedance Leakage<br>Current |                                                                                                      | Measured at the combined output after the external diodes                                                                                                    |       |          | ±0.5  | μΑ                |

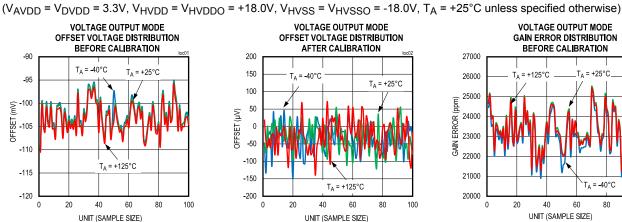

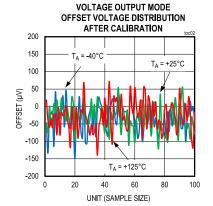

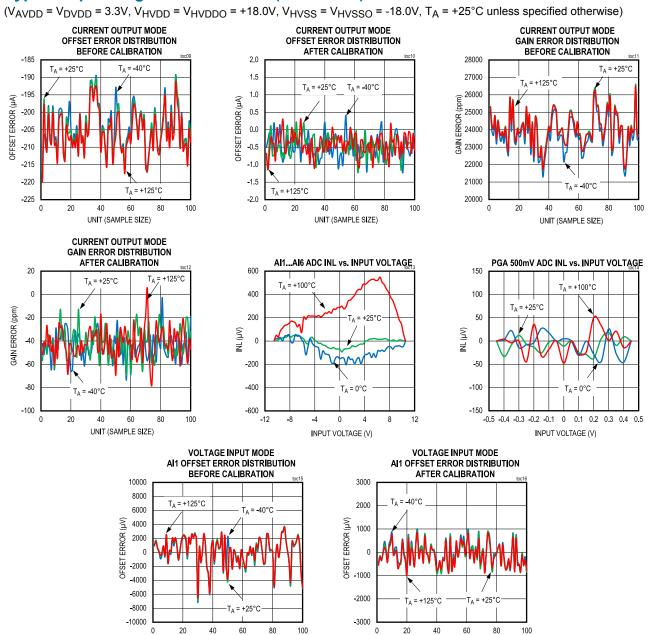

| Offset Error                                  | V <sub>OFF</sub>                                                                                     | $T_A$ = +25°C before calibration                                                                                                                             |       |          | ±150  | mV                |

| Offset Calibration Range                      |                                                                                                      |                                                                                                                                                              |       | ±12.5    |       | V                 |

| Offset Calibration<br>Resolution              |                                                                                                      |                                                                                                                                                              |       | 95       |       | μV                |

| Offset Drift                                  |                                                                                                      | $T_A = +50^{\circ}C \pm 50^{\circ}C$ with internal reference ( <u>Note 5</u> )                                                                               |       | ±18      |       | µV/°C             |

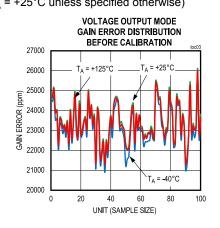

| Gain Error                                    |                                                                                                      | $T_A$ = +25°C before calibration                                                                                                                             | 0     |          | 4     | %                 |

| Gain Calibration Range                        |                                                                                                      |                                                                                                                                                              |       | 0 to 100 |       | %                 |

| Gain Calibration<br>Resolution                |                                                                                                      |                                                                                                                                                              |       | 4        |       | ppm               |

| Gain Drift                                    |                                                                                                      | $T_A = +50^{\circ}C \pm 50^{\circ}C$ with internal reference ( <u>Note 5</u> )                                                                               |       | ±3.3     |       | ppm/°C            |

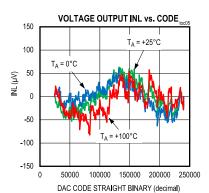

| INL Error                                     | INL                                                                                                  | T <sub>A</sub> = +25°C                                                                                                                                       |       |          | ±300  | μV                |

| INL Drift                                     |                                                                                                      | T <sub>A</sub> = +50°C ± 50°C ( <u>Note 5</u> )                                                                                                              |       | ±3       |       | μV/°C             |

| Output Noise                                  | V <sub>N</sub>                                                                                       | 10kHz bandwidth                                                                                                                                              |       | 85       |       | μV <sub>RMS</sub> |

| Supply Rejection Ratio                        | PSRR                                                                                                 | DC, 12.5V setting, $V_{OUT}$ = 0V, $V_{HVDD}$ = $V_{HVDDO}$ = +5V to +24V                                                                                    |       | 120      |       | - dB              |

|                                               |                                                                                                      | DC, 12.5V setting, $V_{OUT}$ = 0V, $V_{HVSS}$ = $V_{HVSSO}$ = -24V to -5V                                                                                    |       | 115      |       |                   |

| Load Regulation                               |                                                                                                      | -10mA $\leq$ I <sub>LOAD</sub> $\leq$ +10mA, measured at V <sub>OUT</sub> = -10.5V and V <sub>OUT</sub> = +10.5V, output change due to self-heating excluded |       | ±0.1     |       | mV                |

| AI3 Headroom                                  |                                                                                                      | From V <sub>HVSS</sub> ( <u>Note 3</u> )                                                                                                                     | 2.5   |          |       | - V               |

|                                               |                                                                                                      | From V <sub>HVDD</sub> ( <u>Note 3</u> )                                                                                                                     | 2.5   |          |       |                   |

### **Electrical Characteristics (continued)**

| PARAMETER                      | SYMBOL | CONDITIONS                                                                                                                               | MIN TYP  | MAX  | UNITS   |

|--------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------|----------|------|---------|

| AI3 Input Current              |        | ( <u>Note 5</u> )                                                                                                                        |          | ±20  | nA      |

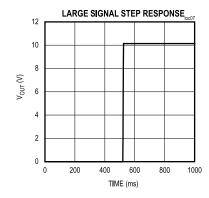

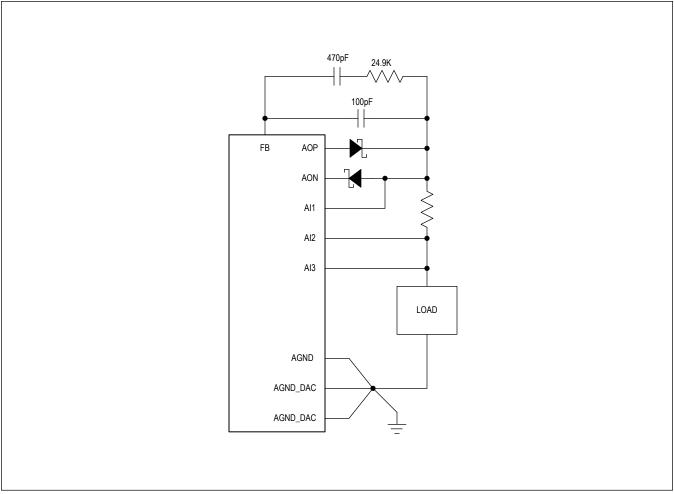

| Settling Time                  |        | 12.5V setting, resistive load from $1k\Omega$ to<br>10M $\Omega$ ; settling to 1% for V <sub>OUT</sub> = 0V to<br>+10.5V or 0V to -10.5V | 0.2      |      | - ms    |

|                                |        | 12.5V setting, capacitive load up to 1µF; settling to 1% for V <sub>OUT</sub> = 0V to +10.5V or 0V to -10.5V                             | 1        |      | 1115    |

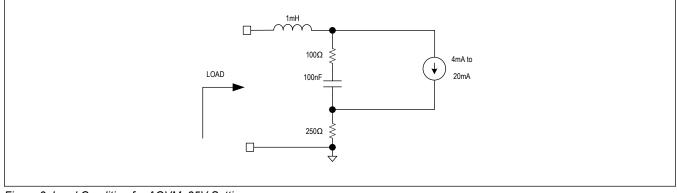

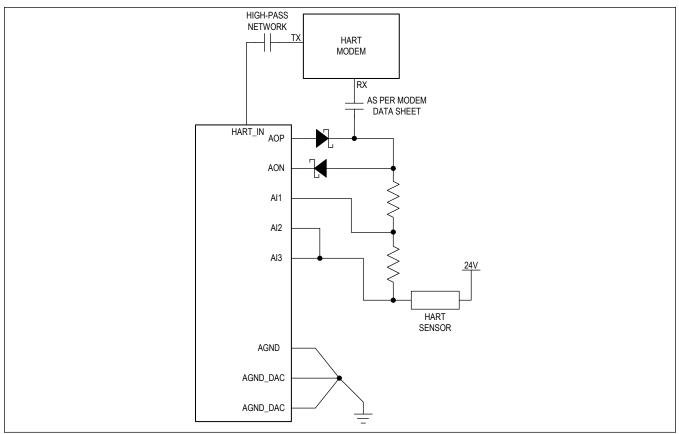

| Bandwidth of 25V<br>Setting    |        | -3dB bandwidth from HART_IN to output, 25V setting, load as depicted in Figure 3                                                         | 10       |      | kHz     |

| ANALOG OUTPUT CURF             |        |                                                                                                                                          |          |      |         |

|                                |        | 25mA setting, $R_{SENSE}$ = 50Ω, DAC full-<br>scale range ( <u>Note 6</u> )                                                              | ±25      |      |         |

| Output Current Range           | lour   | 25mA setting, $R_{SENSE}$ = 50Ω, linear range ( <u>Note 3</u> , <u>Note 6</u> )                                                          | -21      | +21  | - mA    |

| Output Current Range           | IOUT   | 2.5mA setting, $R_{SENSE} = 50\Omega$ , DAC full-<br>scale range ( <u>Note 6</u> )                                                       | ±2.5     |      |         |

|                                |        | 2.5mA setting, $R_{SENSE} = 50\Omega$ , linear range ( <u>Note 3</u> , <u>Note 6</u> )                                                   | -2.1     | +2.1 |         |

| Dropout Voltage                |        | Sourcing 25mA, measured between<br>HVDDO and AOP, gain compression<br><1%                                                                |          | 0.85 | v       |

|                                |        | Sinking 25mA, measured between AON and HVSSO, gain compression <1%                                                                       |          | 0.85 |         |

| Offset Error                   | loss   | 25mA setting, $T_A$ = +25°C before calibration                                                                                           |          | ±300 | - μΑ    |

|                                | IOFF   | 2.5mA setting, T <sub>A</sub> = +25°C before calibration                                                                                 |          | ±30  | μΛ      |

| Offset Calibration Range       |        | 25mA setting                                                                                                                             | ±25      |      | - mA    |

| Chock Guilbration Hange        |        | 2.5mA setting                                                                                                                            | ±2.5     |      | 110 (   |

| Offset Calibration             |        | 25mA setting                                                                                                                             | 200      |      | - nA    |

| Resolution                     |        | 2.5mA setting                                                                                                                            | 20       |      |         |

| Offset Drift                   |        | 25mA setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ with<br>internal reference ( <u>Note 5</u> )                                          | ±36      |      | - nA/°C |

|                                |        | 2.5mA setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ , with internal reference ( <u>Note 5</u> )                                          | ±4       |      |         |

| Gain Error                     |        | 25mA setting, $T_A$ = +25°C before calibration                                                                                           | 0        | 4    | %       |

| Gain Calibration Range         |        | All settings                                                                                                                             | 0 to 100 |      | %       |

| Gain Calibration<br>Resolution |        | All settings                                                                                                                             | 4        |      | ppm     |

| Gain Drift                     |        | 25mA setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ , with internal reference ( <u>Note 5</u> )                                           | ±3.2     |      | ppm/°C  |

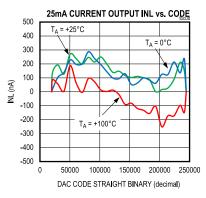

| INL Error                      | INL    | 25mA setting, T <sub>A</sub> = +25°C                                                                                                     |          | ±600 | nA      |

### **Electrical Characteristics (continued)**

| PARAMETER                                | SYMBOL           | CONDITIONS                                                                                            | MIN   | TYP      | MAX   | UNITS             |

|------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|-------|----------|-------|-------------------|

| INL Drift                                |                  | 25mA setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ ( <u>Note</u><br><u>5</u> )                        |       | ±6       |       | nA/°C             |

| Outrast Nation                           |                  | 25mA setting, 10kHz bandwidth                                                                         |       | 270      |       | nA <sub>RMS</sub> |

| Output Noise                             | ۱ <sub>N</sub>   | 2.5mA setting, 10Hz bandwidth                                                                         |       | 25       |       | nA <sub>p-p</sub> |

| Cumulu Dejection                         | DCD              | DC, 25mA setting, V <sub>HVDD</sub> = V <sub>HVDDO</sub> =<br>+5V to +24V                             |       | 10       |       |                   |

| Supply Rejection                         | PSR              | DC, 25mA setting, V <sub>HVSS</sub> = V <sub>HVSSO</sub> =<br>-24V to -5V                             |       | 10       |       | - nA/V            |

| AI1, AI2 Headroom                        |                  | From V <sub>HVSS</sub> ( <u>Note 3</u> )                                                              | 2.5   |          |       | - v               |

| AIT, AIZ Headroom                        |                  | From V <sub>HVDD</sub> ( <u>Note 3</u> )                                                              | 2.5   |          |       | ] <b>v</b>        |

| AI1, AI2 Input Current                   |                  | ( <u>Note 5</u> )                                                                                     |       |          | ±20   | nA                |

| Common-Mode<br>Rejection                 | CMR              | AI1, AI2 in CSA mode, $V_{AI1} = V_{AI2} = V_{CM}$ , $V_{CM} = -16V$ to +16V                          |       |          | 0.5   | μA/V              |

| AI1 and AI2 Differential Input Range     |                  | AI1, AI2 in CSA mode                                                                                  |       | ±1.25    |       | V                 |

| AI1 and AI2 Differential Input Impedance |                  | AI1, AI2 in CSA mode                                                                                  |       | 100      |       | MΩ                |

|                                          |                  | Resistive load up to $250\Omega$ ; settling to 1% for $I_{OUT}$ = 0mA to +21mA or 0mA to -21mA        |       | 0.5      |       |                   |

| Settling Time                            |                  | Resistive load up to $750\Omega$ ; settling to 1% for I <sub>OUT</sub> = 0mA to +21mA or 0mA to -21mA |       | 1.0      |       | ms                |

|                                          |                  | Inductive load up to 1mH; settling to 1% for I <sub>OUT</sub> = 0mA to +21mA or 0mA to -21mA          |       | 0.5      |       |                   |

| ANALOG INPUT VOLTAG                      | GE MODE (AI1     | TO AI4)                                                                                               |       |          |       | 1                 |

|                                          |                  | From V <sub>HVSS</sub> ( <u>Note 3</u> )                                                              | 2.5   |          |       |                   |

| Headroom                                 |                  | From V <sub>HVDD</sub> ( <u>Note 3</u> )                                                              | 2.5   |          |       |                   |

|                                          |                  | ADC full-scale range                                                                                  |       | ±12.5    |       |                   |

| Input Voltage Range                      | V <sub>IN</sub>  | Linear range ( <u>Note 3</u> )                                                                        | -10.5 |          | +10.5 |                   |

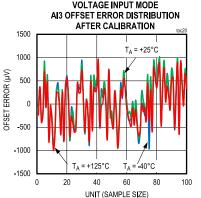

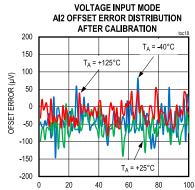

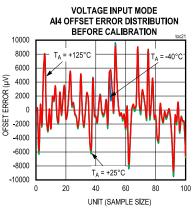

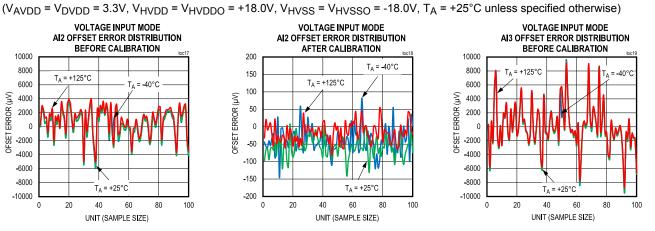

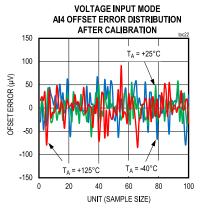

| Offset Error                             | V <sub>OFF</sub> | $T_A$ = +25°C before calibration                                                                      |       |          | ±25   | mV                |

| Offset Calibration Range                 |                  |                                                                                                       |       | ±12.5    |       | V                 |

| Offset Calibration<br>Resolution         |                  |                                                                                                       |       | 3        |       | μV                |

| Offset Drift                             |                  | $T_A = +50^{\circ}C \pm 50^{\circ}C$ with internal reference ( <i>Note 5</i> )                        |       | ±12      |       | µV/°C             |

| Gain Error                               |                  | $T_A = +25^{\circ}C$ before calibration                                                               |       |          | ±4    | %                 |

| Gain Calibration Range                   |                  |                                                                                                       |       | 0 to 200 |       | %                 |

| Gain Calibration<br>Resolution           |                  |                                                                                                       |       | 0.1      |       | ppm               |

| Gain Drift                               |                  | $T_A = +50^{\circ}C \pm 50^{\circ}C$ with internal<br>reference ( <u>Note 5</u> )                     |       | ±2.2     |       | ppm/°C            |

### **Electrical Characteristics (continued)**

| PARAMETER              | SYMBOL           | CONDITIONS                                                                                                                                                        | MIN  | TYP  | MAX  | UNITS             |  |

|------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------------|--|

| INL Error              | INL              | T <sub>A</sub> = +25°C                                                                                                                                            |      |      | ±600 | μV                |  |

| INL Drift              |                  | T <sub>A</sub> = +50°C ± 50°C ( <u>Note 5</u> )                                                                                                                   |      | ±2.4 |      | μV/°C             |  |

| Input Voltage Noise    | V <sub>N</sub>   | ADC sample rate is 57.6ksps, ADC mode is Continuous                                                                                                               |      | 85   |      | μV <sub>RMS</sub> |  |

| Input Current          |                  | ( <u>Note 5</u> )                                                                                                                                                 |      |      | ±20  | nA                |  |

| Cumply Dejection Datio |                  | DC, $V_{HVDD}$ = +5V to +24V                                                                                                                                      |      | 100  |      | dD                |  |

| Supply Rejection Ratio | PSRR             | DC, V <sub>HVSS</sub> = -24V to -5V                                                                                                                               |      | 100  |      | - dB              |  |

| 50/60Hz Normal Mode    |                  | DCHNL_RATE[3:0] = 0b0010, 0b0011,<br>0b0100, 0b0101                                                                                                               | 87   |      |      | dB                |  |

| Rejection              |                  | DCHNL_RATE[3:0] = 0b0000, 0b0001                                                                                                                                  | 75   |      |      | ]                 |  |

| Open/Short Detector    |                  | From any AI1 through AI6 to HVDD                                                                                                                                  |      | 2    |      | ΜΩ                |  |

| Resistance             |                  | From any AI1 through AI6 to AGND                                                                                                                                  |      | 2    |      |                   |  |

| Settling Time          |                  | V <sub>IN</sub> changes from 0V to +10.5V or 0V to<br>-10.5V, digital output reaches 1% of final<br>value, ADC sample rate is 57.6ksps, ADC<br>mode is Continuous |      | 100  |      | μs                |  |

| ANALOG INPUT VOLTA     | GE MODE – PG/    | A (AI5, AI6)                                                                                                                                                      |      |      |      |                   |  |

| Headroom               |                  | From V <sub>HVSS</sub> ( <u>Note 3</u> )                                                                                                                          | 2.5  |      |      | v                 |  |

| Headloom               |                  | From V <sub>HVDD</sub> ( <u>Note 3</u> )                                                                                                                          | 2.5  |      |      |                   |  |

|                        |                  | 25V setting, ADC full-scale range                                                                                                                                 |      | ±25  |      |                   |  |

|                        |                  | 25V setting, linear range ( <u>Note 3</u> )                                                                                                                       | -21  |      | 21   | - v               |  |

|                        |                  | 2.5V setting, ADC full-scale range                                                                                                                                |      | ±2.5 |      | v                 |  |

|                        |                  | 2.5V setting, linear range ( <u>Note 3</u> )                                                                                                                      | -2.1 |      | +2.1 |                   |  |

| Input Voltage Range    | VIN              | 500mV setting, ADC full-scale range                                                                                                                               |      | ±500 |      |                   |  |

| input voltage italige  | Y IN             | 500mV setting, linear range ( <u>Note 3</u> )                                                                                                                     | -420 |      | +420 |                   |  |

|                        |                  | 250mV setting, ADC full-scale range                                                                                                                               |      | ±250 |      | mV                |  |

|                        |                  | 250mV setting, linear range ( <u>Note 3</u> )                                                                                                                     | -210 |      | +210 |                   |  |

|                        |                  | 125mV setting, ADC full-scale range                                                                                                                               |      | ±125 |      |                   |  |

|                        |                  | 125mV setting, linear range ( <u>Note 3</u> )                                                                                                                     | -105 |      | +105 | 1                 |  |

|                        |                  | 25V setting, T <sub>A</sub> = +25°C before calibration                                                                                                            |      |      | ±25  | mV                |  |

|                        |                  | 2.5V setting, $T_A = +25^{\circ}C$ before calibration                                                                                                             |      | ±300 |      |                   |  |

| Offset Error           | V <sub>OFF</sub> | 500mV setting, $T_A = +25^{\circ}C$ before calibration                                                                                                            |      |      | ±500 | 1                 |  |

|                        |                  | 250mV setting, $T_A = +25^{\circ}C$ before calibration                                                                                                            |      | ±30  |      | - μV              |  |

|                        |                  | 125mV setting, $T_A$ = +25°C before calibration                                                                                                                   |      | ±15  |      | 1                 |  |

### **Electrical Characteristics (continued)**

| PARAMETER                        | SYMBOL         | CONDITIONS                                                                                                 | MIN TYP  | MAX   | UNITS             |  |

|----------------------------------|----------------|------------------------------------------------------------------------------------------------------------|----------|-------|-------------------|--|

|                                  |                | 25V setting                                                                                                | ±25      |       | V                 |  |

|                                  |                | 2.5V setting                                                                                               | ±2500    |       |                   |  |

| Offset Calibration Range         |                | 500mV setting                                                                                              | ±500     |       |                   |  |

|                                  |                | 250mV setting                                                                                              | ±250     |       | - mV              |  |

|                                  |                | 125mV setting                                                                                              | ±125     |       | 1                 |  |

|                                  |                | 25V setting                                                                                                | 6        |       |                   |  |

|                                  |                | 2.5V setting                                                                                               | 0.6      |       | 1                 |  |

| Offset Calibration<br>Resolution |                | 500mV setting                                                                                              | 0.12     |       | μV                |  |

|                                  |                | 250mV setting                                                                                              | 0.06     |       | 1                 |  |

|                                  |                | 125mV setting                                                                                              | 0.03     |       | 1                 |  |

| Offect Drift                     |                | 25V setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ with<br>internal reference ( <i>Note 5</i> )             | ±12      |       | µV/°C             |  |

| Offset Drift                     |                | 500mV setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ with<br>internal reference ( <i>Note 5</i> )           | ±600     |       | nV/°C             |  |

| Gain Error                       |                | All voltage settings, $T_A = +25^{\circ}C$ before calibration                                              |          | ±4    | %                 |  |

| Gain Calibration Range           |                |                                                                                                            | 0 to 200 |       | %                 |  |

| Gain Calibration<br>Resolution   |                |                                                                                                            | 0.1      |       | ppm               |  |

|                                  |                | 25V setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ with<br>internal reference ( <i>Note 5</i> )             | ±2.2     | 200   | nnm/°C            |  |

| Gain Drift                       |                | All other voltage settings, $T_A = +50^{\circ}C \pm 50^{\circ}C$ with internal reference ( <i>Note 5</i> ) | ±1.1     |       | – ppm/°C          |  |

|                                  | 15.11          | 25V setting, T <sub>A</sub> = +25°C                                                                        |          | ±600  | μV                |  |

| INL Error                        | INL            | 500mV setting, T <sub>A</sub> = +25°C                                                                      |          | ±170  | μV                |  |

|                                  |                | 25V setting, $T_A = 25^{\circ}C \pm 50^{\circ}C (Note 5)$                                                  | ±35      |       | µV/°C             |  |

| INL Drift                        |                | 500mV setting, $T_A = +50^{\circ}C \pm 50^{\circ}C$ ( <u>Note</u><br><u>5</u> )                            | ±3.5     |       | µV/°C             |  |

|                                  |                | 25V setting, ADC sample rate is<br>57.6ksps, ADC mode is Continuous                                        | 85       |       | μV <sub>RMS</sub> |  |

| Input Voltage Noise              | V <sub>N</sub> | 500mV setting, ADC sample rate is 900sps, ADC mode is Continuous                                           | 4        |       | μV <sub>P-P</sub> |  |

| Input Common Mode                |                | 25V setting, guaranteed by CMRR ( <u>Note</u><br><u>Z</u> )                                                | -6.25    | +6.25 |                   |  |

| Range                            |                | All other voltage settings, guaranteed by CMRR ( <u>Note 7</u> )                                           | -1.25    | +1.25 | - V               |  |

|                                  |                | 25V setting, V <sub>CM</sub> = -6.25V to +6.25V                                                            | 60       |       |                   |  |

| Common Mode                      | CMRR           | 2.5V setting, V <sub>CM</sub> = -1.25V to +1.25V                                                           | 80       | 80    |                   |  |

| Rejection Ratio                  | Ratio          | All other voltage settings, $V_{CM}$ = -1.25V to +1.25V                                                    | 92       |       | dB                |  |

| Supply Dojoction Datis           | חחסח           | DC, $V_{HVDD}$ = +5V to +24V                                                                               | 100      | 100   |                   |  |

| Supply Rejection Ratio           | PSRR           | DC, V <sub>HVSS</sub> = -24V to -5V                                                                        | 100      |       | - dB              |  |

### **Electrical Characteristics (continued)**

| PARAMETER                        | SYMBOL           | CONDITIONS                                                                                                                                                                          | MIN | TYP             | MAX  | UNITS             |

|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|------|-------------------|

| 50/60Hz Normal Mode              |                  | DCHNL_RATE[3:0] = 0b0010, 0b0011,<br>0b0100, 0b0101                                                                                                                                 | 87  |                 |      | dB                |

| Rejection                        |                  | DCHNL_RATE[3:0] = 0b0000, 0b0001                                                                                                                                                    | 75  |                 |      | 1                 |

| Input Current                    |                  | ( <u>Note 5</u> )                                                                                                                                                                   |     |                 | ±20  | nA                |

|                                  |                  | 25V setting, V <sub>IN</sub> changes from 0V to<br>+21V or 0V to -21V, digital output<br>reaches 1% of final value, ADC sample<br>rate is 57.6ksps, ADC mode is<br>Continuous       |     | 100             |      |                   |

| Settling Time                    |                  | 500mV setting, V <sub>IN</sub> changes from 0V to<br>+420mV or 0V to -420mV, digital output<br>reaches 1% of final value, ADC sample<br>rate is 57.6ksps, ADC mode is<br>Continuous |     | 100             |      | - µs              |

| AMPLIFIER INPUTS (HAI            | RT_IN, FB)       |                                                                                                                                                                                     |     |                 |      |                   |

| Input Bias Voltage               |                  |                                                                                                                                                                                     |     | ±2.5            |      | V                 |

| AUX INPUTS (AUX1, AUX            | (2)              |                                                                                                                                                                                     |     |                 |      |                   |

|                                  |                  | From V <sub>HVSS</sub> ( <u>Note 3</u> )                                                                                                                                            | 2.5 |                 |      | v                 |

| Headroom                         |                  | From V <sub>HVDD</sub> ( <u>Note 3</u> )                                                                                                                                            | 2.5 |                 |      | 7 V               |

|                                  | N/               | ADC linear range, single-ended ( <u>Note 3</u> )                                                                                                                                    |     | +0.1 to<br>+2.4 |      | - v               |

| Input Voltage Range              | V <sub>IN</sub>  | ADC linear range, differential ( <u>Note 3</u> )                                                                                                                                    |     | -2.3 to<br>+2.3 |      | V                 |

| Offset Error                     | V <sub>OFF</sub> | $T_A$ = +25°C before calibration                                                                                                                                                    |     | ±0.5            | ±2.5 | mV                |

| Offset Calibration Range         |                  | Single-ended                                                                                                                                                                        |     | 0 to 2.5        |      | - v               |

| Unset Calibration Range          |                  | Differential                                                                                                                                                                        |     | ±2.5            |      |                   |

| Offset Calibration<br>Resolution |                  |                                                                                                                                                                                     |     | 0.3             |      | μV                |

| Offset Drift                     |                  | $T_A = +50^{\circ}C \pm 50^{\circ}C$ with internal<br>reference ( <u>Note 5</u> )                                                                                                   |     | ±1              |      | µV/°C             |

| Gain Error                       |                  | $T_A$ = +25°C before calibration                                                                                                                                                    |     |                 | ±4   | %                 |

| Gain Calibration Range           |                  |                                                                                                                                                                                     |     | 0 to 200        |      | %                 |

| Gain Calibration<br>Resolution   |                  |                                                                                                                                                                                     |     | 0.1             |      | ppm               |

| Gain Drift                       |                  | $T_A = +50^{\circ}C \pm 50^{\circ}C$ , with internal reference ( <i>Note 5</i> )                                                                                                    |     | ±1              |      | ppm/°C            |

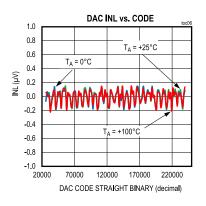

| INL Error                        | INL              | T <sub>A</sub> = +25°C                                                                                                                                                              |     | ±15             | ±60  | μV                |

| INL Drift                        |                  | T <sub>A</sub> = +50°C ± 50°C ( <u>Note 5</u> )                                                                                                                                     |     | ±50             |      | nV/°C             |

| Input Voltage Noise              | V <sub>N</sub>   | ADC sample rate is 57.6ksps, ADC mode is Continuous                                                                                                                                 |     | 8               |      | μV <sub>RMS</sub> |

| Supply Dejection Dati-           |                  | DC, $V_{HVDD}$ = +5V to +24V                                                                                                                                                        | 100 |                 |      |                   |

| Supply Rejection Ratio           | PSRR             | DC, V <sub>HVSS</sub> = -24V to -5V                                                                                                                                                 |     | 100             |      | dB                |

### **Electrical Characteristics (continued)**

| PARAMETER                                 | SYMBOL               | CONDITIONS                                                                                                                                         | MIN                       | TYP | MAX                       | UNITS  |

|-------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|--------|

| 50/60Hz Normal Mode                       |                      | DCHNL_RATE[3:0] = 0b0010, 0b0011,<br>0b0100, 0b0101                                                                                                | 87                        |     |                           | dB     |

| Rejection                                 |                      | DCHNL_RATE[3:0] = 0b0000, 0b0001                                                                                                                   | 75                        |     |                           |        |

| Input Current                             | I <sub>IN</sub>      | ( <u>Note 5</u> )                                                                                                                                  |                           |     | ±20                       | nA     |

| Settling Time                             |                      | V <sub>IN</sub> changes from 0.1V to +2.4V, digital<br>output reaches 1% of final value, ADC<br>sample rate is 57.6ksps, ADC mode is<br>Continuous |                           | 100 |                           | μs     |

| DAC REFERENCE (REF_                       | DAC)                 |                                                                                                                                                    |                           |     |                           |        |

| REF_DAC Output<br>Voltage                 | V <sub>REF_DAC</sub> | Internal reference                                                                                                                                 |                           | 2.5 |                           | V      |

| Output Voltage<br>Accuracy                |                      | Referred to $V_{REF_{DAC}}$ , $T_{A} = +25^{\circ}C$                                                                                               | -0.2                      |     | +0.2                      | %      |

| Output Voltage<br>Temperature Coefficient |                      | T <sub>A</sub> = -40°C to +125°C ( <u>Note 5</u> )                                                                                                 |                           | 5   |                           | ppm/°C |

| Line Regulation                           |                      | $2.7V \le V_{AVDD} \le 3.6V$                                                                                                                       |                           |     | 50                        | μV/V   |

| REF_DAC Bypass<br>Capacitor               |                      |                                                                                                                                                    |                           | 100 |                           | pF     |

| REF_DAC_EXT Input<br>Range                |                      | External reference                                                                                                                                 |                           | 2.5 |                           | V      |

| ADC REFERENCE (REF_                       | _ADC)                |                                                                                                                                                    |                           |     |                           |        |

| REF_ADC Output<br>Voltage                 | V <sub>REF_ADC</sub> | Internal reference                                                                                                                                 |                           | 2.5 |                           | V      |

| Output Voltage<br>Accuracy                |                      | Referred to $V_{REF_ADC}$ , $T_A = +25^{\circ}C$                                                                                                   | -0.2                      |     | +0.2                      | %      |

| Output Voltage<br>Temperature Coefficient |                      | T <sub>A</sub> = -40°C to +125°C ( <u>Note 5</u> )                                                                                                 |                           | 5   |                           | ppm/°C |

| Line Regulation                           |                      | $2.7V \le V_{AVDD} \le 3.6V$                                                                                                                       |                           |     | 250                       | μV/V   |

| REF_ADC Bypass<br>Capacitor               |                      |                                                                                                                                                    |                           | 4.7 |                           | μF     |

| REF_ADC_EXT Input<br>Range                |                      | External reference                                                                                                                                 |                           | 2.5 |                           | V      |

| DIGITAL INPUTS (CS, SC                    | CLK, SDI, RST,       | SYNC, CLK, LDAC, GPIO0 THROUGH GP                                                                                                                  | IO5)                      |     |                           |        |

| Input Logic Low Voltage                   | VIL                  |                                                                                                                                                    |                           |     | 0.3×V <sub>DV</sub><br>DD | V      |

| Input Logic High Voltage                  | V <sub>IH</sub>      |                                                                                                                                                    | 0.7×V <sub>DV</sub><br>DD |     |                           | V      |

| Input Hysteresis                          | V <sub>HYS</sub>     |                                                                                                                                                    |                           | 200 |                           | mV     |

| Input Leakage Current                     | I <sub>IN</sub>      |                                                                                                                                                    | -1                        |     | +1                        | μA     |

| Input Capacitance                         | C <sub>IN</sub>      |                                                                                                                                                    |                           | 10  |                           | pF     |

| DIGITAL OUTPUTS (SDC                      | , RDY, INT, GP       | 100 THROUGH GPIO5)                                                                                                                                 |                           |     |                           |        |

| Output Logic Low<br>Voltage               | V <sub>OL</sub>      | I <sub>SINK</sub> = 4mA                                                                                                                            |                           |     | 0.4                       | V      |

### **Electrical Characteristics (continued)**

| PARAMETER                              | SYMBOL              | CONDITIONS                                                 | MIN                       | TYP | MAX | UNITS |

|----------------------------------------|---------------------|------------------------------------------------------------|---------------------------|-----|-----|-------|

| Output Logic High<br>Voltage           | V <sub>OH</sub>     | I <sub>SOURCE</sub> = 4mA, except INT                      | 0.9×V <sub>DV</sub><br>DD |     |     | V     |

| Three-State Leakage<br>Current         |                     |                                                            | -10                       |     | +10 | μA    |

| Three-State Output<br>Capacitance      |                     |                                                            |                           | 10  |     | pF    |

| POWER SUPPLIES                         |                     |                                                            |                           |     |     |       |

| Analog Supply Voltage                  | V <sub>AVDD</sub>   |                                                            | 2.7                       | 3.3 | 3.6 | V     |

| Digital Supply Voltage                 | V <sub>DVDD</sub>   |                                                            | 2.7                       | 3.3 | 3.6 | V     |

| Positive High Voltage<br>Supply        | V <sub>HVDD</sub>   |                                                            | 5                         |     | 28  | V     |

| Negative High Voltage<br>Supply        | V <sub>HVSS</sub>   |                                                            | -24                       |     | -5  | V     |

| High Voltage Supply                    | V <sub>HV</sub>     | V <sub>HVDD</sub> - V <sub>HVSS</sub>                      | 10                        |     | 48  | V     |

| Positive High Voltage<br>Output Supply | V <sub>HVDDO</sub>  |                                                            | 5                         |     | 28  | V     |

| Negative High Voltage<br>Output Supply | V <sub>HVSSO</sub>  |                                                            | -24                       |     | -5  | V     |

| High Voltage Output<br>Supply          | V <sub>HVO</sub>    | V <sub>HVDDO</sub> - V <sub>HVSSO</sub>                    | 10                        |     | 48  | V     |

| DVDD POR Threshold                     |                     | Voltage rising                                             |                           | 1.6 |     | V     |

| HVDD Undervoltage<br>Threshold         |                     | Voltage rising                                             |                           | 1.5 |     | V     |

|                                        |                     | Analog output voltage mode                                 |                           | 5.5 |     |       |

| Analog Supply                          |                     | Analog output current mode                                 |                           | 5.5 |     |       |

| Quiescent Current                      | I <sub>AVDD_Q</sub> | Analog inputs AI1-AI6                                      |                           | 5.2 |     | - mA  |

|                                        |                     | Analog inputs and output                                   |                           | 8   |     |       |

|                                        |                     | Analog output voltage mode                                 |                           | 1.4 |     |       |

| Digital Supply Quiescent               | IDVDD_Q             | Analog output current mode                                 |                           | 1.4 |     | mA    |

| Current                                | עַעעיטי             | Analog inputs AI1-AI6                                      |                           | 2.4 |     |       |

|                                        |                     | Analog inputs and output                                   |                           | 2.4 |     |       |

|                                        |                     | Analog output voltage mode, no load current                |                           | 2.3 |     |       |

| High-Voltage Quiescent<br>Current      | I <sub>HV_Q</sub>   | Analog output current mode, no load current                |                           | 3.3 |     | mA    |

| Current                                |                     | Analog inputs AI1-AI6, AI1-AI6 at AGND                     |                           | 2.8 |     | ]     |

|                                        |                     | Analog inputs and output, AI1-AI6 at AGND, no load current |                           | 3.5 |     |       |

### **Electrical Characteristics (continued)**

| PARAMETER                     | SYMBOL                | CONDITIONS                                                                                                                                                        | MIN | TYP  | MAX | UNITS |

|-------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

|                               |                       | Analog output voltage mode, no load<br>current, V <sub>HVDD</sub> = V <sub>HVDDO</sub> = +15V,<br>V <sub>HVSS</sub> = V <sub>HVSSO</sub> = -15V                   |     | 90   |     |       |

|                               |                       | Analog output current mode, no load<br>current, $V_{HVDD} = V_{HVDDO} = +15V$ ,<br>$V_{HVSS} = V_{HVSSO} = -15V$                                                  |     | 120  |     |       |

| Total Quiescent Power         | PQ                    | Analog inputs AI1-AI6, AI1-AI6 at AGND,<br>V <sub>HVDD</sub> = V <sub>HVDDO</sub> = +15V, V <sub>HVSS</sub> =<br>V <sub>HVSSO</sub> = -15V                        |     | 110  |     | mW    |

|                               |                       | Analog inputs and output, AI1-AI6 at<br>AGND, no load current, V <sub>HVDD</sub> =<br>V <sub>HVDDO</sub> = +15V, V <sub>HVSS</sub> = V <sub>HVSSO</sub> =<br>-15V |     | 140  |     |       |

| PROTECTION                    |                       |                                                                                                                                                                   |     |      |     |       |

| Thermal Shutdown<br>Threshold | T <sub>SHDN</sub>     | Temperature rising until the analog I/O configuration resets                                                                                                      |     | +165 |     | °C    |

| Thermal Warning<br>Threshold  | T <sub>WARN</sub>     | Temperature rising until interrupt assertion                                                                                                                      |     | +145 |     | °C    |

| Thermal Warning<br>Hysteresis | T <sub>WARN_HYS</sub> |                                                                                                                                                                   |     | 10   |     | °C    |

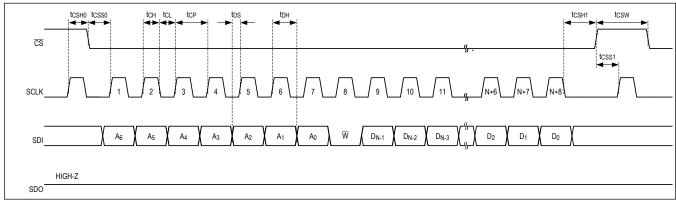

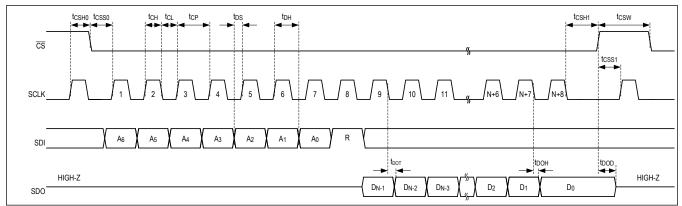

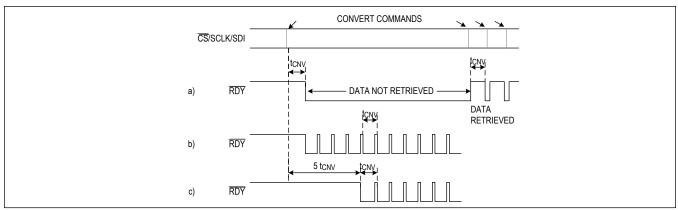

| TIMING CHARACTERIS            | TICS                  |                                                                                                                                                                   |     |      |     |       |

| SCLK Frequency                | foor                  | All SPI transactions except analog output<br>DAC register read-back                                                                                               |     |      | 20  | - MHz |

| SOLKTIEquency                 | fsclk                 | Analog output DAC register read-back, registers 0x44 through 0x47                                                                                                 |     |      | 10  |       |

| SCLK Clock Period             | top                   | All SPI transactions except analog output DAC register read-back                                                                                                  | 50  |      |     | - ns  |

| SOLK CIUCK FEIIOU             | t <sub>CP</sub>       | Analog output DAC register read-back, registers 0x44 through 0x47                                                                                                 | 100 |      |     | 115   |

| SCLK Pulse Width High         | t                     | All SPI transactions except analog output DAC register read-back                                                                                                  | 13  |      |     | - ns  |

|                               | tсн                   | Analog output DAC register read-back for registers 0x44 through 0x47                                                                                              | 40  |      |     | 115   |

| SCLK Pulse Width Low          | <b>4</b>              | All SPI transactions except analog output DAC register read-back                                                                                                  | 20  |      |     | 20    |

| SCLK Pulse Width Low          | t <sub>CL</sub>       | Analog output DAC register read-back, registers 0x44 through 0x47                                                                                                 | 40  |      |     | - ns  |

| CS Fall Setup Time            | t <sub>CSS0</sub>     | CS falling edge to first SCLK rising edge setup time                                                                                                              | 7   |      |     | ns    |

| CS Rise Setup Time            | t <sub>CSS1</sub>     | $\overline{\text{CS}}$ rising edge to SCLK rising edge setup time                                                                                                 | 5   |      |     | ns    |

| CS Fall Hold Time             | tCSH0                 | SCLK rising edge to $\overline{CS}$ falling edge hold time                                                                                                        | 0   |      |     | ns    |

| CS Rise Hold Time             | tCSH1                 | SCLK falling edge to $\overline{\text{CS}}$ rising edge hold time                                                                                                 | 3   |      |     | ns    |

### **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{DVDD} = +2.7V \text{ to } +3.6V, V_{HVDD} = V_{HVDDO} = +18.0V; V_{HVSS} = V_{HVSSO} = -18.0V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{AVDD} = V_{DVDD} = 3.3V, V_{HVDD} = V_{HVDDO} = +18.0V, V_{HVSS} = V_{HVSSO} = -18.0V, T_A = +25^{\circ}C.) (Note 1)$

| PARAMETER           | SYMBOL                   | CONDITIONS                                                                             | MIN | TYP | MAX | UNITS |

|---------------------|--------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|-------|

| CS Pulse Width High | t <sub>CSW</sub>         | Minimum CS pulse width high                                                            | 150 |     |     | ns    |

| SDI Setup Time      | t <sub>DS</sub>          | SDI setup time to SCLK rising edge                                                     | 10  |     |     | ns    |

| SDI Hold Time       | t <sub>DH</sub>          | SDI hold time after SCLK rising edge                                                   | 5   |     |     | ns    |

| SDO Transition Time | <sup>t</sup> DOT         | SDO transition valid after SCLK falling<br>edge                                        |     |     | 20  | ns    |

| SDO Hold Time       | tdoh                     | Output remains valid after falling edge of SCLK                                        | 1   |     |     | ns    |

| SDO Disable Time    | tDOD                     | $\overline{\text{CS}}$ rising edge to SDO disable, C <sub>LOAD</sub> = 20pF            |     |     | 80  | ns    |

| ESD AND SURGE PROT  | ESD AND SURGE PROTECTION |                                                                                        |     |     |     |       |

| ESD                 |                          | Human Body Model, all pins                                                             |     | ±1  |     | kV    |

| IEC Surge           | V <sub>SURGE</sub>       | IEC 61000-4-5, 1.2/50 $\mu$ s pulse, pins Al1-Al6, 4.75k $\Omega$ series MELF resistor | ±1  |     | kV  |       |

**Note 1:** Maximum and minimum limits are 100% tested with typical supply voltage levels at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and device characterization.

- **Note 2:** The output voltage is measured at the sense voltage input (Al3). The supply voltage must fulfill the input headroom requirements, as well as the output amplifier requirements. Assuming that Al1, Al2, and Al3 are connected to the output, Al1 dictates the headroom requirement. Assuming a 25mA load current, a  $\pm 12.5V$  output, and a 50 $\Omega$  sense resistor, the minimum supply voltage to fulfill the Al1 headroom requirement is the output voltage (V<sub>OUT</sub>) plus the voltage drop across the sense resistor plus 2.5V, resulting in a supply voltage requirement of  $\pm 16.25V$ . The minimum supply voltage required for the output amplifier is the sum of the V<sub>OUT</sub>, the voltage across the sense resistor, the diode forward voltage, and the dropout voltage. For a 25mA load current, a  $\pm 12.5V$  output, a 50 $\Omega$  sense resistor, and a diode forward voltage of 750mV, the minimum supply voltage required by the output amplifier is  $\pm 15.35V$ . Overall, the minimum supply voltage is  $\pm 16.25V$ .

- Note 3: Offset error, gain error, INL error, and settling times are only guaranteed in the linear range. The minimum and maximum specification of the linear range and input headroom are guaranteed through offset, gain, and INL error.

- Note 4: The threshold current specifies the typical current that triggers the short circuit protection. The average current that accounts for self heating of the device is significantly smaller due to the duty cycle when OVC\_CTRL is set to logic low.

- Note 5: Not production tested. Guaranteed by design and device characterization.